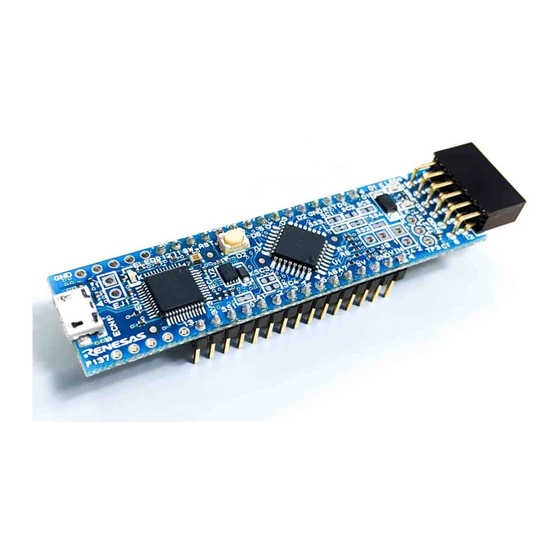

Renesas RL78/G1P Hardware User Manual

16-bit single-chip microcontroller

Hide thumbs

Also See for RL78/G1P:

- User manual (59 pages) ,

- User manual (27 pages) ,

- User manual (58 pages)

Table of Contents

Advertisement

Quick Links

RL78/G1P

16

16-Bit Single-Chip Microcontrollers

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Electronics Corp. without notice. Please review the latest information published by

Renesas Electronics Corp. through various means, including the Renesas Electronics Corp.

website (http://www.renesas.com).

www.renesas.com

User's Manual: Hardware

Rev.1.00 Nov 2019

Advertisement

Table of Contents

Summary of Contents for Renesas RL78/G1P

- Page 1 All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp.

- Page 2 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Page 3 Unit Products The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- Page 4 This manual is intended to give users an understanding of the functions described in the Organization below. Organization The RL78/G1P manual is separated into two parts: this manual and the software edition (common to the RL78 Family). RL78/G1P RL78 Family User’s Manual...

- Page 5 E2 Emulator User’s Manual R20UT3538E E2 Lite Emulator User’s Manual R20UT3240E Renesas Flash Programmer Flash Memory Programming Software User’s Manual R20UT4066E Renesas Flash Development Toolkit User’s Manual R20UT0508E Caution The related documents listed above are subject to change without notice. Be sure to use the latest...

- Page 6 All trademarks and registered trademarks are the property of their respective owners. EEPROM is a trademark of Renesas Electronics Corporation. SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

-

Page 7: Table Of Contents

CONTENTS CHAPTER 1 OUTLINE..........................1 1.1 Features ............................1 1.2 List of Part Numbers ........................3 1.3 Pin Configuration (Top View) ......................4 1.3.1 24-pin products ........................... 4 1.3.2 32-pin products ........................... 5 1.4 Pin Identification ..........................6 1.5 Block Diagram ..........................7 1.5.1 24-pin products ........................... - Page 8 3.1.4 Special function register (SFR) area ....................33 3.1.5 Extended special function register (2nd SFR: 2nd Special Function Register) area ......33 3.1.6 Data memory addressing ......................... 34 3.2 Processor Registers ........................35 3.2.1 Control registers ..........................35 3.2.2 General-purpose registers ........................ 37 3.2.3 ES and CS registers .........................

- Page 9 4.4 Port Function Operations ......................90 4.4.1 Writing to I/O port ..........................90 4.4.2 Reading from I/O port ........................90 4.4.3 Operations on I/O port ........................90 4.5 Settings of Port Related Register When Using Alternate Function ........91 4.6 Cautions When Using Port Function ..................94 4.6.1 Cautions on 1-bit manipulation instruction for port register n (Pn) ............

- Page 10 6.2.1 Timer count register mn (TCRmn) ....................135 6.2.2 Timer data register mn (TDRmn) ....................136 6.3 Registers Controlling Timer Array Unit ..................137 6.3.1 Peripheral enable register 0 (PER0) ....................138 6.3.2 Timer clock select register m (TPSm) .................... 139 6.3.3 Timer mode register mn (TMRmn) ....................

- Page 11 6.9.1 Operation as one-shot pulse output function .................. 204 6.9.2 Operation as PWM function ......................211 6.9.3 Operation as multiple PWM output function ................... 218 6.10 Cautions When Using Timer Array Unit ................. 226 6.10.1 Cautions when using timer output ....................226 CHAPTER 7 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER ..........

- Page 12 9.3.10 A/D test register (ADTES) ......................266 9.3.11 Registers controlling port function of analog input pins ..............267 9.4 A/D Converter Conversion Operations ..................268 9.5 Input Voltage and Conversion Results ..................270 9.6 A/D Converter Operation Modes ....................271 9.6.1 Software trigger mode (select mode, sequential conversion mode) ..........

- Page 13 CHAPTER 11 SERIAL ARRAY UNIT ....................308 11.1 Functions of Serial Array Unit ....................309 11.1.1 3-wire serial I/O (CSI00) ....................... 309 11.1.2 UART (UART0) ..........................310 11.2 Configuration of Serial Array Unit ..................311 11.2.1 Shift register ..........................313 11.2.2 Lower 8/9 bits of the serial data register mn (SDRmn) ..............

- Page 14 11.6.2 Slave reception ..........................412 11.6.3 Slave transmission/reception ......................419 11.6.4 Calculating transfer clock frequency ..................... 429 11.6.5 Procedure for processing errors that occurred during slave select input function communication ..........................431 11.7 Operation of UART (UART0) Communication ............... 432 11.7.1 UART transmission ........................

- Page 15 12.5.14 Communication reservation ......................501 12.5.15 Cautions ............................. 505 12.5.16 Communication operations ......................506 12.5.17 Timing of I C interrupt request (INTIICAn) occurrence ............... 513 12.6 Timing Charts ........................... 534 CHAPTER 13 DMA CONTROLLER ..................... 549 13.1 Functions of DMA Controller ....................549 13.2 Configuration of DMA Controller ....................

- Page 16 15.3.3 Priority specification flag registers (PR00L, PR00H, PR01L, PR10L, PR10H, PR11L) ....581 15.3.4 External interrupt rising edge enable register (EGP0), external interrupt falling edge enable register (EGN0) ..............582 15.3.5 Program status word (PSW) ......................583 15.4 Interrupt Servicing Operations ....................584 15.4.1 Maskable interrupt request acknowledgment ................

- Page 17 19.4.3 When used as interrupt and reset mode ..................635 19.5 Cautions for Voltage Detector ....................641 CHAPTER 20 SAFETY FUNCTIONS ....................643 20.1 Overview of Safety Functions ....................643 20.2 Registers Used by Safety Functions ..................644 20.3 Operation of Flash memory CRC operation function (high-speed CRC) ......644 20.3.1 Flash memory CRC control register (CRC0CTL) .................

- Page 18 23.8 Processing Time for Each Command When PG-FP6 Is in Use (Reference Value) .... 690 CHAPTER 24 ON-CHIP DEBUG FUNCTION ..................691 24.1 Connecting E1, E2, E2 Lite, E20 On-chip Debugging Emulator to RL78/G1P ....691 24.2 On-chip Debug Security ID ...................... 692 24.3 Securing of User Resources ....................

- Page 19 CHAPTER 26 INSTRUCTION SET ....................... 697 26.1 Conventions Used in Operation List ..................698 26.1.1 Operand identifiers and specification methods ................698 26.1.2 Description of operation column ....................699 26.1.3 Description of flag operation column .................... 700 26.1.4 PREFIX instruction ........................700 26.2 Operation List ...........................

-

Page 20: Chapter 1 Outline

R01UH0895EJ0100 RL78/G1P Rev.1.00 RENESAS MCU Nov 29, 2019 CHAPTER 1 OUTLINE 1.1 Features Minimum instruction execution time can be changed from high speed (0.03125 s: @ 32 MHz operation with high- speed on-chip oscillator) to low-speed (1 s: @ 1 MHz operation with high-speed on-chip oscillator) ... - Page 21 RL78/G1P CHAPTER 1 OUTLINE ROM, RAM capacities Note Flash ROM Data Flash 24-pin 32-pin 16 KB 2 KB 1.5 KB R5F11Z7AANA, R5F11Z7ADNA R5F11ZBAAFP, R5F11ZBADFP Note The flash libraries use the on-chip RAM area from FFE20H to FFEFFH and the parts of the RAM area referred to as self RAM (RAM for use in self-programming), which are listed in the table below, for self-programming or rewriting of the data flash memory.

-

Page 22: List Of Part Numbers

= -40 to +85°C D: Industrial applications, T = -40 to +85°C ROM capacity: A: 16 KB Pin count: 7: 24-pin B: 32-pin RL78/G1P group Memory type: F: Flash memory Renesas MCU Renesas semiconductor product Pin Count Package Data Flash... -

Page 23: Pin Configuration (Top View)

RL78/G1P CHAPTER 1 OUTLINE 1.3 Pin Configuration (Top View) 1.3.1 24-pin products 24-pin plastic HWQFN (4 × 4 mm, 0.5 mm pitch) exposed die pad 18 17 16 15 14 13 P30/INTP2/TxD0/TOOLTxD/SO00 P21/ANI1/AV REFM P31/INTP1/RxD0/TOOLRxD/SI00 P20/ANI0/AV REFP P32/INTP3/SCK00 P22/ANI2/ANO0... -

Page 24: 32-Pin Products

RL78/G1P CHAPTER 1 OUTLINE 1.3.2 32-pin products 32-pin plastic LQFP (7 × 7 mm, 0.8 mm pitch) 24 23 22 21 20 19 18 17 P27/ANI7 P30/INTP2/TxD0/TOOLTxD/SO00 P26/ANI6 P31/INTP1/RxD0/TOOLRxD/SI00 P25/ANI5 P32/INTP3/SCK00 P21/ANI1/AV P33/TI02/TO02/SSI00 REFM P20/ANI0/AV REFP P22/ANI2/ANO0 P23/ANI3/ANO1 P61/SDAA0/SDAA1... -

Page 25: Pin Identification

RL78/G1P CHAPTER 1 OUTLINE 1.4 Pin Identification ANI0 to ANI7, ANI16: Analog input RxD0: Receive data ANO0, ANO1: Analog output SCK00: Serial clock input/output Analog reference voltage SCLA0, SCLA1: Serial clock input/output REFM minus SDAA0, SDAA1: Serial data input/output Analog reference voltage... -

Page 26: Block Diagram

RL78/G1P CHAPTER 1 OUTLINE 1.5 Block Diagram 1.5.1 24-pin products TIMER ARRAY UNIT (4ch) P10, P12, P13, PORT 1 TI00/TO00/P13 P15, P16 P20 to P23, TI01/TO01/P16 PORT 2 TI02/TO02/P33 PORT 3 P30 to P33 TI03/TO03/P12 PORT 4 WINDOW PORT 6... -

Page 27: 32-Pin Products

RL78/G1P CHAPTER 1 OUTLINE 1.5.2 32-pin products TIMER ARRAY UNIT (4ch) TI00/TO00/P13 PORT 1 P10 to P17 TI01/TO01/P16 PORT 2 P20 to P27 TI02/TO02/P33 PORT 3 P30 to P35 TI03/TO03/P12 PORT 4 WINDOW PORT 6 P60, P61 WATCHDOG TIMER PORT 12... -

Page 28: Outline Of Functions

RL78/G1P CHAPTER 1 OUTLINE 1.6 Outline of Functions (1/2) Item 24-pin 32-pin R5F11Z7AANA, R5F11Z7ADNA R5F11ZBAAFP, R5F11ZBADFP Code flash memory 16 KB Data flash memory 2 KB Note 1.5 KB Memory space 1 MB Main system High-speed X1 (crystal/ceramic) oscillation, external main system clock input (EXCLK) - Page 29 RL78/G1P CHAPTER 1 OUTLINE (2/2) Item 24-pin 32-pin R5F11Z7AANA, R5F11Z7ADNA R5F11ZBAAFP, R5F11ZBADFP Reset by RESET pin Reset Internal reset by watchdog timer Internal reset by power-on-reset Internal reset by voltage detector Internal reset by illegal instruction execution Note ...

-

Page 30: Chapter 2 Pin Functions

RL78/G1P CHAPTER 2 PIN FUNCTIONS CHAPTER 2 PIN FUNCTIONS 2.1 Pin Function List Pin I/O buffer power supplies are unique for all products. The relationship between these power supplies and the pins is shown below. The input and output, buffer, and pull-up resistor settings for each port are also valid for the alternate function. -

Page 31: 24-Pin Products

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.1.1 24-pin products Function Name Function After Reset Alternate Function Port 1. Input port ANI16 5-bit I/O port. TI03/TO03/INTP4/P Input/output can be specified in 1-bit units. CLBUZ0 Use of an on-chip pull-up resistor can be specified by a software TI00/TO00 setting at input port. -

Page 32: 32-Pin Products

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.1.2 32-pin products Function Name Function After Reset Alternate Function Port 1. Input port 8-bit I/O port. Input/output can be specified in 1-bit units. TI03/TO03/INTP4/ Use of an on-chip pull-up resistor can be specified by a software PCLBUZ0 setting at input port. -

Page 33: Functions Other Than Port Pins

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.2 Functions Other Than Port Pins 2.2.1 With functions for each product Function Name 32-pin 24-pin Function Name 32-pin 24-pin ANI0 TO03 ANI1 TxD0 ... -

Page 34: Function Descriptions

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.2.2 Function descriptions (1/2) Function Name Function ANI0 Input A/D converter analog input ANI1 ANI2 ANI3 ANI4 ANI5 ANI6 ANI7 ANI16 ANO0 Output D/A converter output ANO1 Input Negative reference voltage input of the A/D converter... - Page 35 RL78/G1P CHAPTER 2 PIN FUNCTIONS (2/2) Function Name Function Resonator connection for main system clock EXCLK Input External clock input for main system clock Positive power supply for all pins Ground potential for all pins TOOLRxD...

-

Page 36: Description Of Pin Functions

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.3 Description of Pin Functions Remark The pins mounted depend on the product. See 1.3 Pin Configuration (Top View) and 2.1 Pin Function List. 2.3.1 P10 to P17 (port 1) P10 to P17 function as an I/O port. These pins also function as timer I/O, external interrupt request input, and clock/buzzer output. -

Page 37: P30 To P35 (Port 3)

RL78/G1P CHAPTER 2 PIN FUNCTIONS (a) ANI0 to ANI7 These are the analog input pins (ANI0 to ANI7) of A/D converter. See 9.10 (5) Analog input (ANIn) pins. (b) AV REFP This is a pin that inputs the A/D converter reference potential (+ side). -

Page 38: P40 (Port 4)

RL78/G1P CHAPTER 2 PIN FUNCTIONS (h) TI02 This is a pin for inputting an external count clock/capture trigger to 16-bit timer 02. TO02 This is a timer output pin from 16-bit timer 02. TOOLTxD This is the UART serial data output pin for the external device connection used during flash memory programming. -

Page 39: P60, P61 (Port 6)

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.3.5 P60, P61 (port 6) P60 and P61 function as an I/O port. These pins also function as serial interface data I/O and clock I/O. Output of P60 and P61 is N-ch open-drain output (6 V tolerance). -

Page 40: P137 (Port 13)

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.3.7 P137 (port 13) P137 functions as an input port. P137 pin also functions as external interrupt request input. (1) Port mode P137 functions as an input port. (2) Control mode P137 functions as external interrupt request input. -

Page 41: Connection Of Unused Pins

RL78/G1P CHAPTER 2 PIN FUNCTIONS 2.4 Connection of Unused Pins Table 2-3 shows the connection of unused pins. Table 2-3. Connection of Unused Pins Recommended Connection of Unused Pins Pin Name I/O Circuit Type P10/ANI16 Note 1 11-U Input: Independently connect to V or V via a resistor. - Page 42 RL78/G1P CHAPTER 2 PIN FUNCTIONS Figure 2-1. Pin I/O Circuit List (1/2) Type 2 Type 8-R pullup P-ch enable data P-ch IN/OUT Schmitt-triggered input with hysteresis characteristics output N-ch disable Type 11-G Type 11-T data P-ch IN/OUT data P-ch output...

- Page 43 RL78/G1P CHAPTER 2 PIN FUNCTIONS Figure 2-1. Pin I/O Circuit List (2/2) Type 11-U Type 13-R pull-up P-ch enable data P-ch IN/OUT IN/OUT output N-ch data disable N-ch output disable input enable P-ch Comparator N-ch Series resistor string voltage Type 37-C...

-

Page 44: Chapter 3 Cpu Architecture

RL78/G1P CHAPTER 3 CPU ARCHITECTURE CHAPTER 3 CPU ARCHITECTURE 3.1 Memory Space Products in the RL78/G1P can access a 1 MB address space. Figure 3-1 shows the memory map. R01UH0895EJ0100 Rev.1.00 Nov 29, 2019... - Page 45 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-1. Memory Map FFFFF H 0 3 F F F H Special function registers (SFR) 256 bytes FFF00 H FFEFFH General-purpose registers 32 bytes FFEE0H FFEDFH Notes 1, 2, 4 1.5 KB FF9 00 H...

- Page 46 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Remark The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see Table 3-1 Correspondence Between Address Values and Block Numbers in Flash Memory. 03FFFH Block 0FH...

- Page 47 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Correspondence between the address values and block numbers in the flash memory are shown below. Table 3-1. Correspondence Between Address Values and Block Numbers in Flash Memory Address Value Block Number 00000H to 003FFH 00400H to 007FFH...

-

Page 48: Internal Program Memory Space

CHAPTER 3 CPU ARCHITECTURE 3.1.1 Internal program memory space The internal program memory space stores the program and table data. The RL78/G1P products incorporate internal ROM (flash memory), as shown below. Table 3-2. Internal ROM Capacity Part Number Internal ROM... - Page 49 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-3. Vector Table Vector Table Address Interrupt Source 00000H RESET, POR, LVD, WDT, TRAP, IAW, RPE 00004H INTWDTI 00006H INTLVI 00008H INTP0 0000AH INTP1 0000CH INTP2 0000EH INTP3 00010H INTP4 00012H INTP5 00014H INTAD...

-

Page 50: Mirror Area

CHAPTER 3 CPU ARCHITECTURE 3.1.2 Mirror area The RL78/G1P mirrors the code flash area of 02000H to 03FFFH, F2000H to F3FFFH. By reading data from F2000H to F3FFFH, an instruction that does not have the ES register as an operand can be used, and thus the contents of the code flash can be read with the shorter code. - Page 51 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Processor mode control register (PMC) This register sets the flash memory space for mirroring to area from F2000H to F3FFFH. The PMC register can be set by a 1-bit or 8-bit memory manipulation instruction.

-

Page 52: Internal Data Memory Space

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.1.3 Internal data memory space The RL78/G1P products incorporate the following RAMs. Table 3-4. Internal RAM Capacity Part Number Internal RAM 1536 8 bits (FF900H to FFEFFH) RL78/G1P The internal RAM can be used as a data area and a program area where instructions are fetched (it is prohibited to use the general-purpose register area for fetching instructions). -

Page 53: Data Memory Addressing

Several addressing modes are provided for addressing the memory relevant to the execution of instructions for the RL78/G1P, based on operability and other considerations. In particular, special addressing methods designed for the functions of the special function registers (SFR) and general-purpose registers are available for use. Figures 3-3 shows correspondence between data memory and addressing. -

Page 54: Processor Registers

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.2 Processor Registers The RL78/G1P products incorporate the following processor registers. 3.2.1 Control registers The control registers control the program sequence, statuses and stack memory. The control registers consist of a program counter (PC), a program status word (PSW) and a stack pointer (SP). - Page 55 Programming Library Type 01 User’s Manual and RL78 Family Data Flash Library Type 04 User’s Manual. RL78/G1P: FFE20H to FFEFFH 4. The flash libraries use the parts of the RAM area referred to as self RAM in self-programming or rewriting of the data flash memory. For the sizes of the RAM areas used by the flash libraries, see “ROM, RAM capacities”...

-

Page 56: General-Purpose Registers

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.2.2 General-purpose registers General-purpose registers are mapped at particular addresses (FFEE0H to FFEFFH) of the data memory. The general- purpose registers consists of 4 banks, each bank consisting of eight 8-bit registers (X, A, C, B, E, D, L, and H). -

Page 57: And Cs Registers

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.2.3 ES and CS registers The ES register and CS register are used to specify the higher address for data access and when a branch instruction is executed (register indirect addressing), respectively. The default value of the ES register after reset is 0FH, and that of the CS register is 00H. -

Page 58: Special Function Registers (Sfrs)

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.2.4 Special function registers (SFRs) Unlike a general-purpose register, each SFR has a special function. SFRs are allocated to the FFF00H to FFFFFH area. SFRs can be manipulated like general-purpose registers, using operation, transfer, and bit manipulation instructions. - Page 59 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-5. Special Function Register (SFR) List (1/3) Manipulable Bit Range Address Special Function Register (SFR) Name Symbol After Reset 1-bit 8-bit 16-bit FFF01H Port register 1 FFF02H Port register 2 ...

- Page 60 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-5. Special Function Register (SFR) (2/3) Manipulable Bit Range Address Special Function Register (SFR) Name Symbol After Reset 1-bit 8-bit 16-bit FFF64H Timer data register 02 TDR02 0000H FFF65H ...

- Page 61 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-5. Special Function Register (SFR) List (3/3) Manipulable Bit Range Address Special Function Register (SFR) Name Symbol After Reset 1-bit 8-bit 16-bit FFFE0H Interrupt request flag register 0L IF0L ...

-

Page 62: Extended Special Function Registers (2Nd Sfrs: 2Nd Special Function Registers)

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.2.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers) Unlike a general-purpose register, each extended SFR (2nd SFR) has a special function. Extended SFRs are allocated to the F0000H to F07FFH area. SFRs other than those in the SFR area (FFF00H to FFFFFH) are allocated to this area. - Page 63 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-6. Extended Special Function Register (2nd SFR) List (1/4) Manipulable Bit Range Address Extended Special Function Register Symbol After Reset (2nd SFR) Name 1-bit 8-bit 16-bit F0010H A/D converter mode register 2 ADM2 ...

- Page 64 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-6. Extended Special Function Register (2nd SFR) List (2/4) Manipulable Bit Range Address Extended Special Function Register Symbol After Reset (2nd SFR) Name 1-bit 8-bit 16-bit F0110H Serial mode register 00...

- Page 65 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-6. Extended Special Function Register (2nd SFR) List (3/4) Manipulable Bit Range Address Extended Special Function Register Symbol After Reset (2nd SFR) Name 1-bit 8-bit 16-bit F01A0H Timer status register 00...

- Page 66 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Table 3-6. Extended Special Function Register (2nd SFR) List (4/4) Manipulable Bit Range Address Extended Special Function Register Symbol After Reset (2nd SFR) Name 1-bit 8-bit 16-bit F0300H Event output destination select register 00 ELSELR00 ...

-

Page 67: Instruction Address Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.3 Instruction Address Addressing 3.3.1 Relative addressing [Function] Relative addressing stores in the program counter (PC) the result of adding a displacement value included in the instruction word (signed complement data: 128 to +127 or 32768 to +32767) to the program counter (PC)’s value (the start address of the next instruction), and specifies the program address to be used as the branch destination. -

Page 68: Register Indirect Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.3.3 Table indirect addressing [Function] Table indirect addressing specifies a table address in the CALLT table area (0080H to 00BFH) with the 5-bit immediate data in the instruction word, stores the contents at that table address and the next address in the program counter (PC) as 16-bit data, and specifies the program address. -

Page 69: Addressing For Processing Data Addresses

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4 Addressing for Processing Data Addresses 3.4.1 Implied addressing [Function] Instructions for accessing registers (such as accumulators) that have special functions are directly specified with the instruction word, without using any register specification field in the instruction word. -

Page 70: Direct Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.3 Direct addressing [Function] Direct addressing uses immediate data in the instruction word as an operand address to directly specify the target address. [Operand format] Identifier Description !addr16 Label or 16-bit immediate data (only the space from F0000H to FFFFFH is specifiable) -

Page 71: Short Direct Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.4 Short direct addressing [Function] Short direct addressing directly specifies the target addresses using 8-bit data in the instruction word. This type of addressing is applied only to the space from FFE20H to FFF1FH. [Operand format]... -

Page 72: Sfr Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.5 SFR addressing [Function] SFR addressing directly specifies the target SFR addresses using 8-bit data in the instruction word. This type of addressing is applied only to the space from FFF00H to FFFFFH. [Operand format]... -

Page 73: Register Indirect Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.6 Register indirect addressing [Function] Register indirect addressing directly specifies the target addresses using the contents of the register pair specified with the instruction word as an operand address. [Operand format] Identifier Description [DE], [HL] (only the space from F0000H to FFFFFH is specifiable) ... -

Page 74: Based Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.7 Based addressing [Function] Based addressing uses the contents of a register pair specified with the instruction word or 16-bit immediate data as a base address, and 8-bit immediate data or 16-bit immediate data as offset data. The sum of these values is used to specify the target address. - Page 75 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-24. Example of [HL+byte], [DE+byte] [HL + byte], [DE + byte] <1> <2> <1> <2> FFFFFH Instruction code Target OP-code Target memory array <2> Offset of data <2> byte <1> Address of Other data in...

- Page 76 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-27. Example of ES:[HL+byte], ES:[DE+byte] ES: [HL + byte], ES: [DE + byte] <1> <2> <3> <1> <2> <3> XFFFFH Instruction code <2> <3> Target memory Target OP-code array Offset byte of data <3>...

- Page 77 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-29. Example of ES:word[BC] ES: word [BC] XFFFFH <1> <2> <3> Array of Instruction code Target memory <3> word-sized <3> Offset data OP-code rp(BC) <2> Low Addr. Address of a word within an array <2>...

-

Page 78: Based Indexed Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.8 Based indexed addressing [Function] Based indexed addressing uses the contents of a register pair specified with the instruction word as the base address, and the content of the B register or C register similarly specified with the instruction word as offset address. -

Page 79: Stack Addressing

RL78/G1P CHAPTER 3 CPU ARCHITECTURE 3.4.9 Stack addressing [Function] The stack area is indirectly addressed with the stack pointer (SP) values. This addressing is automatically employed when the PUSH, POP, subroutine call, and return instructions are executed or the register is saved/restored upon generation of an interrupt request. - Page 80 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-33. Example of POP POP rp <1> <2> SP+2 <1> SP+1 Stack (SP+1) Instruction code area (SP) <2> OP-code F0000H Stack addressing is specified <1>. The contents of addresses SP and SP + 1 are stored in the lower-order and higher-order bytes of the pair of registers indicated by rp <2>, respectively.

- Page 81 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-35. Example of RET <1> SP+4 <1> SP+3 (SP+3) Instruction code Stack SP+2 (SP+2) area OP-code SP+1 (SP+1) <3> (SP) <2> F0000H Stack addressing is specified <1>. The contents of addresses SP, SP + 1, and SP + 2 are stored in PC bits 7 to 0, 15 to 8, and 19 to 16, respectively <2>.

- Page 82 RL78/G1P CHAPTER 3 CPU ARCHITECTURE Figure 3-37. Example of RETI, RETB RETI, RETB <1> SP+4 <1> SP+3 (SP+3) Instruction code SP+2 (SP+2) Stack OP-code area SP+1 (SP+1) <3> (SP) <2> F0000H Stack addressing is specified <1>. Memory The contents of addresses SP, SP + 1, SP + 2, and SP + 3 are stored in PC bits 7 to 0, 15 to 8, 19 to 16, and the PSW, respectively <2>.

-

Page 83: Chapter 4 Port Functions

CHAPTER 4 PORT FUNCTIONS 4.1 Port Functions The RL78/G1P microcontrollers are provided with digital I/O ports, which enable variety of control operations. In addition to the function as digital I/O ports, these ports have several alternate functions. For details of the alternate functions, see CHAPTER 2 PIN FUNCTIONS. -

Page 84: Port 1

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.1 Port 1 Port 1 is an I/O port with an output latch. Port 1 can be set to the input mode or output mode in 1-bit units using port mode register 1 (PM1). When the P10 to P17 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 1 (PU1). - Page 85 RL78/G1P CHAPTER 4 PORT FUNCTIONS For example, figures 4-1 to 4-4 show block diagrams of port 1. Figure 4-1. Block Diagrams of P10 (24-pin products) PU10 P-ch PMC1 PMC10 PORT Output latch P10/ANI16 (P10) PM10 A/D converter Port register 1...

- Page 86 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-2. Block Diagram of P10, P11, P14, and P17 (32-pin products) PU10, PU11, PU14, PU17 P-ch PORT Output latch P10, P11, P14, P17 (P10, P11, P14, P17) PM10, PM11, PM14, PM17 Port register 1...

- Page 87 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-3. Block Diagram of P12, P13, and P16 PU12, PU13, PU16 P-ch Alternate function PORT Output latch P12/TI03/TO03/INTP4/ (P12, P13, P16) PCLBUZ0, P13/TI00/TO00, P16/TI01/TO01/INTP5 PM12, PM13, PM16 Alternate function Port register 1 PU1: Pull-up resistor option register 1...

- Page 88 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-4. Block Diagrams of P15 PU15 P-ch PORT Output latch P15/PCLBUZ1 (P15) PM15 Alternate function Port register 1 PU1: Pull-up resistor option register 1 PM1: Port mode register 1 Read signal WR: Write signal R01UH0895EJ0100 Rev.1.00...

-

Page 89: Port 2

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.2 Port 2 Port 2 is an I/O port with an output latch. Port 2 can be set to the input mode or output mode in 1-bit units using port mode register 2 (PM2). This port can also be used for A/D converter analog input, (+ side and – side) reference voltage input, and D/A converter output. - Page 90 RL78/G1P CHAPTER 4 PORT FUNCTIONS Table 4-5. Setting Functions of P22/ANI2/ANO0, P23/ANI3/ANO1 Pins ADPC Register PM2 Register DAM Register ADS Register P22/ANI2/ANO0, P23/ANI3/ANO1 Pins Digital I/O selection Input mode Digital input Output mode Digital output Analog input selection...

- Page 91 RL78/G1P CHAPTER 4 PORT FUNCTIONS For example, figures 4-5 and 4-6 show block diagrams of port 2 for 32-pin products. Figure 4-5. Block Diagram of P20, P21, P24 to P27 ADPC ADPC 0: Analog input 1: Digital I/O ADPC0, ADPC1,...

-

Page 92: Port 3

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.3 Port 3 Port 3 is an I/O port with an output latch. Port 3 can be set to the input mode or output mode in 1-bit units using port mode register 3 (PM3). When the P30 to P35 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 3 (PU3). - Page 93 RL78/G1P CHAPTER 4 PORT FUNCTIONS For example, figures 4-7 to 4-11 show block diagrams of port 3 for 32-pin products. Figure 4-7. Block Diagram of P30 PU30 P-ch Alternate function PORT Output latch P30/INTP2/TxD0/ (P30) TOOLTxD/SO00 PM30 Alternate function Port register 3...

- Page 94 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-8. Block Diagram of P31 PU31 P-ch Alternate function PORT Output latch P31/INTP1/RxD0/ (P31) TOOLRxD/SI00 PM31 Port register 3 PU3: Pull-up resistor option register 3 PM3: Port mode register 3 Read signal WR: Write signal R01UH0895EJ0100 Rev.1.00...

- Page 95 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-9. Block Diagram of P32 PU32 P-ch Alternate function PORT Output latch P32/INTP3/SCK00 (P32) PM32 Alternate function Port register 3 PU3: Pull-up resistor option register 3 PM3: Port mode register 3 Read signal WR: Write signal R01UH0895EJ0100 Rev.1.00...

- Page 96 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-10. Block Diagram of P33 PU33 P-ch Alternate function PORT Output latch P33/TI02/TO02/ (P33) SSI00 PM33 Alternate function Port register 3 PU3: Pull-up resistor option register 3 PM3: Port mode register 3 Read signal WR: Write signal...

- Page 97 RL78/G1P CHAPTER 4 PORT FUNCTIONS Figure 4-11. Block Diagram of P34 and P35 PU34, PU35 P-ch PORT Output latch P34, P35 (P34, P35) PM34, PM35 Port register 3 PU3: Pull-up resistor option register 3 PM3: Port mode register 3 Read signal WR: Write signal...

-

Page 98: Port 4

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.4 Port 4 Port 4 is an I/O port with an output latch. Port 4 can be set to the input mode or output mode using port mode register 4 (PM4). When the P40 pin is used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 4 (PU4). -

Page 99: Port 6

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.5 Port 6 Port 6 is an I/O port with an output latch. Port 6 can be set to the input mode or output mode in 1-bit units using port mode register 6 (PM6). The output of the P60 and P61 pins is N-ch open-drain output (6 V tolerance). - Page 100 RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.6 Port 12 P121 and P122 are 2-bit input only ports. This port can also be used for connecting resonator for main system clock and external clock input for main system clock. Reset signal generation sets port 12 to input mode.

-

Page 101: Port 13

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.2.7 Port 13 P137 is a 1-bit input-only port. P137 is fixed to an input ports. This port can also be used for external interrupt request input. Table 4-10. Settings of Registers When Using Port 13... -

Page 102: Registers Controlling Port Function

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3 Registers Controlling Port Function Port functions are controlled by the following registers. Port mode registers (PMxx) Port registers (Pxx) Pull-up resistor option registers (PUxx) Port mode control register 1 (PMC1) ... - Page 103 RL78/G1P CHAPTER 4 PORT FUNCTIONS Table 4-11. PMxx, Pxx, PUxx, PMC1 Registers and Bits Mounted on Each Product (2/2) Bit Name Port PMxx PUxx PMC1 Register Register Register Register Port 4 PM40 PU40 ...

-

Page 104: Port Mode Registers (Pmxx)

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3.1 Port mode registers (PMxx) These registers specify input or output mode for the port in 1-bit units. These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets these registers to FFH. -

Page 105: Port Registers (Pxx)

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3.2 Port registers (Pxx) These registers set the output latch value of a port. If the data is read in the input mode, the pin level is read. If it is read in the output mode, the output latch value is... -

Page 106: Pull-Up Resistor Option Registers (Puxx)

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3.3 Pull-up resistor option registers (PUxx) These registers specify whether the on-chip pull-up resistors are to be used or not. On-chip pull-up resistors can be used in 1-bit units only for the bits set to input mode (PMmn = 1) for the pins to which the use of an on-chip pull-up resistor has been specified in these registers. -

Page 107: Port Mode Control Register 1 (Pmc1) (24-Pin Products Only)

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3.4 Port mode control register 1 (PMC1) (24-pin products only) This register sets the digital I/O/analog input in 1-bit units. This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to FFH. -

Page 108: A/D Port Configuration Register (Adpc)

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.3.5 A/D port configuration register (ADPC) This register switches the ANI0/P20to ANI7/P27 pins to digital I/O of port or analog input of A/D converter. The ADPC register can be set by an 8-bit memory manipulation instruction. -

Page 109: Port Function Operations

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.4 Port Function Operations Port operations differ depending on whether the input or output mode is set, as shown below. 4.4.1 Writing to I/O port (1) Output mode A value is written to the output latch by a transfer instruction, and the output latch contents are output from the pin. -

Page 110: Settings Of Port Related Register When Using Alternate Function

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.5 Settings of Port Related Register When Using Alternate Function To use the alternate function of a port pin, set the port mode register, and output latch as shown in Table 4-12. Caution If the output function of an alternate function is assigned to a pin that is also used as an output pin, the output of the unused alternate function must be set to its initial state. - Page 111 RL78/G1P CHAPTER 4 PORT FUNCTIONS Table 4-12. Settings of Port Related Register When Using Alternate Function (2/2) Pin Name Alternate Function PM P Name INTP2 Input TxD0 Output TOOLTxD Output SO00 Output INTP1 Input RxD0 Input ...

- Page 112 RL78/G1P CHAPTER 4 PORT FUNCTIONS Table 4-14. Setting Functions of P22/ANI2/ANO0 and P23/ANI3/ANO1 Pins ADPC Register PM2 Register P22/ANI2/ANO0, DAM Register ADS Register P23/ANI3/ANO1 Pins Input mode Digital input Digital I/O selection Output mode Digital output Selects ANI.

-

Page 113: Cautions When Using Port Function

The targets of writing to and reading from the Pn register of a port whose PMnm bit is 1 are the output latch and pin status, respectively. A 1-bit manipulation instruction is executed in the following order in the RL78/G1P. <1> The Pn register is read in 8-bit units. -

Page 114: Cautions On Specifying The Pin Settings

RL78/G1P CHAPTER 4 PORT FUNCTIONS 4.6.2 Cautions on specifying the pin settings If the output function of an alternate function is assigned to a pin that is also used as an output pin, the output of the unused alternate function must be set to its initial state so as to prevent conflicting outputs. For details about the alternate output function, see 4.5 Settings of Port Related Register When Using Alternate Function. -

Page 115: Chapter 5 Clock Generator

RL78/G1P CHAPTER 5 CLOCK GENERATOR CHAPTER 5 CLOCK GENERATOR 5.1 Functions of Clock Generator The clock generator generates the clock to be supplied to the CPU and peripheral hardware. The following three kinds of system clocks and clock oscillators are selectable. -

Page 116: Configuration Of Clock Generator

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.2 Configuration of Clock Generator The clock generator includes the following hardware. Table 5-1. Configuration of Clock Generator Item Configuration Control registers Clock operation mode control register (CMC) System clock control register (CKC) Clock operation status control register (CSC) - Page 117 RL78/G1P CHAPTER 5 CLOCK GENERATOR R01UH0895EJ0100 Rev.1.00 Nov 29, 2019...

-

Page 118: Registers Controlling Clock Generator

RL78/G1P CHAPTER 5 CLOCK GENERATOR Remark f X1 clock oscillation frequency High-speed on-chip oscillator clock frequency External main system clock frequency High-speed system clock frequency : Main system clock frequency MAIN CPU/peripheral hardware clock frequency Low-speed on-chip oscillator clock frequency 5.3 Registers Controlling Clock Generator... - Page 119 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-2. Format of Clock Operation Mode Control Register (CMC) Address: FFFA0H After reset: 00H Symbol EXCLK OSCSEL AMPH EXCLK OSCSEL High-speed system clock X1/P121 pin X2/EXCLK/P122 pin pin operation mode Input port mode Input port...

-

Page 120: System Clock Control Register (Ckc)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.2 System clock control register (CKC) This register is used to select a CPU/peripheral hardware clock and a main system clock. The CKC register can be set by a 1-bit or 8-bit memory manipulation instruction. -

Page 121: Clock Operation Status Control Register (Csc)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.3 Clock operation status control register (CSC) This register is used to control the operations of the high-speed system clock and high-speed on-chip oscillator clock (except the low-speed on-chip oscillator clock). The CSC register can be set by a 1-bit or 8-bit memory manipulation instruction. -

Page 122: Oscillation Stabilization Time Counter Status Register (Ostc)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.4 Oscillation stabilization time counter status register (OSTC) This is the register that indicates the count status of the X1 clock oscillation stabilization time counter. The X1 clock oscillation stabilization time can be checked in the following case, ... - Page 123 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-5. Format of Oscillation Stabilization Time Counter Status Register (OSTC) Address: FFFA2H After reset: 00H Symbol OSTC MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST MOST Oscillation stabilization time status...

-

Page 124: Oscillation Stabilization Time Select Register (Osts)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.5 Oscillation stabilization time select register (OSTS) This register is used to select the X1 clock oscillation stabilization wait time when the STOP mode is released. When the X1 clock is selected as the CPU clock, the operation automatically waits for the time set using the OSTS register after the STOP mode is released. - Page 125 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-6. Format of Oscillation Stabilization Time Select Register (OSTS) Address: FFFA3H After reset: 07H Symbol OSTS OSTS2 OSTS1 OSTS0 OSTS2 OSTS1 OSTS0 Oscillation stabilization time selection = 10 MHz = 20 MHz ...

-

Page 126: Peripheral Enable Registers 0, 1 (Per0, Per1)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.6 Peripheral enable registers 0, 1 (PER0, PER1) These registers are used to enable or disable supply of the clock signal to peripheral hardware. Clock supply to a hardware that is not in use is stopped in order to reduce power consumption and noise. - Page 127 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-7. Format of Peripheral Enable Register 0 (PER0) (2/2) Address: F00F0H After reset: 00H Symbol <6> <5> <4> <2> <0> PER0 IICA1EN ADCEN IICA0EN SAU0EN TAU0EN SAU0EN Control of serial array unit 0 input clock supply Stops input clock supply.

-

Page 128: High-Speed On-Chip Oscillator Frequency Select Register (Hocodiv)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.7 High-speed on-chip oscillator frequency select register (HOCODIV) The frequency of the high-speed on-chip oscillator which is set by an option byte (000C2H) can be changed by using high-speed on-chip oscillator frequency select register (HOCODIV). However, the selectable frequency depends on the FRQSEL3 bit of the option byte (000C2H). -

Page 129: High-Speed On-Chip Oscillator Trimming Register (Hiotrm)

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.3.8 High-speed on-chip oscillator trimming register (HIOTRM) This register is used to adjust the accuracy of the high-speed on-chip oscillator. With self-measurement of the high-speed on-chip oscillator frequency via a timer using high-accuracy external clock input (timer array unit), and so on, the accuracy can be adjusted. -

Page 130: System Clock Oscillator

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.4 System Clock Oscillator 5.4.1 X1 oscillator The X1 oscillator oscillates with a crystal resonator or ceramic resonator (1 to 20 MHz) connected to the X1 and X2 pins. An external clock can also be input. In this case, input the clock signal to the EXCLK pin. - Page 131 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-12 shows examples of incorrect resonator connection. Figure 5-12. Examples of Incorrect Resonator Connection (1/2) (a) Too long wiring (b) Crossed signal line PORT (c) The X1 and X2 signal line wires cross. (d) A power supply/GND pattern exists under the X1 and X2 wires.

- Page 132 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-12. Examples of Incorrect Resonator Connection (2/2) (e) Wiring near high alternating current (f) Current flowing through ground line of oscillator (potential at points A, B, and C fluctuates) High current (g) Signals are fetched R01UH0895EJ0100 Rev.1.00...

-

Page 133: High-Speed On-Chip Oscillator

5.4.2 High-speed on-chip oscillator The high-speed on-chip oscillator is incorporated in the RL78/G1P. The frequency can be selected from among 32, 24, 16, 12, 8, 6, 4, 3, 2, or 1 MHz by using the option byte (000C2H). Oscillation can be controlled by bit 0 (HIOSTOP) of the clock operation status control register (CSC). -

Page 134: Clock Generator Operation

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.5 Clock Generator Operation The clock generator generates the following clocks and controls the operation modes of the CPU, such as standby mode (see Figure 5-1). Main system clock f MAIN High-speed system clock f... - Page 135 RL78/G1P CHAPTER 5 CLOCK GENERATOR Figure 5-13. Clock Generator Operation When Power Supply Voltage Is Turned On 10 μs or more Lower limit of the operating voltage range Power supply voltage (V <1> Power-on-reset RESET pin Switched by software Reset processing...

-

Page 136: Controlling Clock

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.6 Controlling Clock 5.6.1 Example of setting high-speed on-chip oscillator After a reset release, the CPU/peripheral hardware clock (f ) always starts operating with the high-speed on-chip oscillator clock. The frequency of the high-speed on-chip oscillator can be selected from 32, 24, 16, 12, 8, 6, 4, 3, 2, and 1 MHz by using FRQSEL0 to FRQSEL3 of the option byte (000C2H). -

Page 137: Example Of Setting X1 Oscillation Clock

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.6.2 Example of setting X1 oscillation clock After a reset release, the CPU/peripheral hardware clock (f ) always starts operating with the high-speed on-chip oscillator clock. To subsequently change the clock to the X1 oscillation clock, set the oscillator and start oscillation by... -

Page 138: Cpu Clock Status Transition Diagram

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.6.3 CPU clock status transition diagram Figure 5-14 shows the CPU clock status transition diagram of this product. Figure 5-14. CPU Clock Status Transition Diagram Power ON High-speed on-chip oscillator: Woken up X1 oscillation/EXCLK input: Stops (input port mode) ≥... - Page 139 RL78/G1P CHAPTER 5 CLOCK GENERATOR Table 5-3 shows transition of the CPU clock and examples of setting the SFR registers. Table 5-3. CPU Clock Transition and SFR Register Setting Examples (1/3) (1) CPU operating with high-speed on-chip oscillator clock (B) after reset release (A)

- Page 140 RL78/G1P CHAPTER 5 CLOCK GENERATOR Table 5-3. CPU Clock Transition and SFR Register Setting Examples (2/3) (3) CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed system clock (C) (Setting sequence of SFR registers) Setting Flag of SFR Register...

- Page 141 RL78/G1P CHAPTER 5 CLOCK GENERATOR Table 5-3. CPU Clock Transition and SFR Register Setting Examples (3/3) (5) HALT mode (D) set while CPU is operating with high-speed on-chip oscillator clock (B) HALT mode (E) set while CPU is operating with high-speed system clock (C)

-

Page 142: Condition Before Changing Cpu Clock And Processing After Changing Cpu Clock

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.6.4 Condition before changing CPU clock and processing after changing CPU clock Condition before changing the CPU clock and processing after changing the CPU clock are shown below. Table 5-4. Changing CPU Clock CPU Clock... -

Page 143: Time Required For Switchover Of Cpu Clock And System Clock

RL78/G1P CHAPTER 5 CLOCK GENERATOR 5.6.5 Time required for switchover of CPU clock and system clock By setting bit 4 (MCM0) of the system clock control register (CKC), the main system clock can be switched (between the high-speed on-chip oscillator clock and the high-speed system clock). -

Page 144: Resonator And Oscillator Constants

A list of the resonators for which the operation has most recently been verified and their oscillation constants (for reference) is provided on the page for the corresponding product at the Renesas Web site (http://www.renesas.com). Cautions 1. The constants for these oscillator circuits are reference values based on specific environments set up for evaluation by the manufacturers. -

Page 145: Chapter 6 Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT CHAPTER 6 TIMER ARRAY UNIT The number of units or channels of the timer array unit differs, depending on the product. Units Channels 24, 32-pin Unit 0 Channel 0 √ Channel 1 √ Channel 2 √... - Page 146 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT The timer array unit has four 16-bit timers. Each 16-bit timer is called a channel and can be used as an independent timer. In addition, two or more “channels” can be used to create a high-accuracy timer.

-

Page 147: Functions Of Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.1 Functions of Timer Array Unit Timer array unit has the following functions. 6.1.1 Independent channel operation function By operating a channel independently, it can be used for the following purposes without being affected by the operation mode of other channels. -

Page 148: Simultaneous Channel Operation Function

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (6) Delay counter Counting is started at the valid edge of the signal input to the timer input pin (TImn), and an interrupt is generated after any delay period. Compare operation Timer input Interrupt signal... -

Page 149: 8-Bit Timer Operation Function (Channels 1 And 3 Only)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (3) Multiple PWM (Pulse Width Modulation) output By extending the PWM function and using one master channel and two or more slave channels, up to three types of PWM signals that have a specific period and a specified duty factor can be generated. -

Page 150: Configuration Of Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.2 Configuration of Timer Array Unit Timer array unit includes the following hardware. Table 6-1. Configuration of Timer Array Unit Item Configuration Timer/counter Timer count register mn (TCRmn) Register Timer data register mn (TDRmn) - Page 151 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-1. Entire Configuration of Timer Array Unit 0 Timer clock select register 0 (TPS0) PRS031 PRS030 PRS021 PRS020 PRS013 PRS012 PRS011 PRS010 PRS003 PRS002 PRS001 PRS000 Prescaler to f Peripheral enable Selector Selector...

- Page 152 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-2. Internal Block Diagram of Channel 0 of Timer Array Unit 0 Timer CK00 TCLK Output controller controller TO00 Mode CK01 Output latch selection (Pxx) PMxx Interrupt controller INTTM00 (Timer interrupt) Edge Timer counter register 00 (TCR00)

- Page 153 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-4. Internal Block Diagram of Channel 2 of Timer Array Unit 0 Interrupt signal from master channel Timer CK00 Output controller controller TCLK TO02 CK01 Mode Output latch selection PMxx (Pxx) Interrupt controller...

-

Page 154: Timer Count Register Mn (Tcrmn)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.2.1 Timer count register mn (TCRmn) The TCRmn register is a 16-bit read-only register and is used to count clocks. The value of this counter is incremented or decremented in synchronization with the rising edge of a count clock. -

Page 155: Timer Data Register Mn (Tdrmn)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.2.2 Timer data register mn (TDRmn) This is a 16-bit register from which a capture function and a compare function can be selected. The capture or compare function can be switched by selecting an operation mode by using the MDmn3 to MDmn0 bits of timer mode register mn (TMRmn). -

Page 156: Registers Controlling Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3 Registers Controlling Timer Array Unit Timer array unit is controlled by the following registers. Peripheral enable register 0 (PER0) Timer clock select register m (TPSm) Timer mode register mn (TMRmn) ... -

Page 157: Peripheral Enable Register 0 (Per0)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.1 Peripheral enable register 0 (PER0) The PER0 register is used to enable or disable supply of the clock signal to peripheral hardware. Clock supply to a hardware that is not in use is stopped in order to reduce power consumption and noise. -

Page 158: Timer Clock Select Register M (Tpsm)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.2 Timer clock select register m (TPSm) The TPSm register is a 16-bit register that is used to select two types or four types of operation clocks (CKm0, CKm1 , CKm2, CKm3) that are commonly supplied to each channel from external prescaler. CKm1 is selected by using bits 7 to 4 of the TPSm register, and CKm0 is selected by using bits 3 to 0. - Page 159 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-10. Format of Timer Clock Select register m (TPSm) (1/2) Address: F01B6H, F01B7H (TPS0) After reset: 0000H Symbol TPSm Selection of operation clock (CKmk) (k = 0, 1) Note = 2 MHz = 5 MHz f...

- Page 160 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-10. Format of Timer Clock Select register m (TPSm) (2/2) Address: F01B6H, F01B7H (TPS0) After reset: 0000H Symbol TPSm Selection of operation clock (CKm2) Note = 2 MHz = 5 MHz f = 10 MHz f...

-

Page 161: Timer Mode Register Mn (Tmrmn)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.3 Timer mode register mn (TMRmn) The TMRmn register sets an operation mode of channel n. This register is used to select the operation clock (f select the count clock, select the master/slave, select the 16 or 8-bit timer (only for channels 1 and 3), specify the start trigger and capture trigger, select the valid edge of the timer input, and specify the operation mode (interval, capture, event counter, one-count, or capture and one-count). - Page 162 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-11. Format of Timer Mode Register mn (TMRmn) (1/4) Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03) After reset: 0000H Symbol MAST TMRmn ERmn (n = 2) Symbol TMRmn SPLIT (n = 1, 3)

- Page 163 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-11. Format of Timer Mode Register mn (TMRmn) (2/4) Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03) After reset: 0000H Symbol MAST TMRmn ERmn (n = 2) Symbol TMRmn SPLIT (n = 1, 3)

- Page 164 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-11. Format of Timer Mode Register mn (TMRmn) (3/4) Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03) After reset: 0000H Symbol MAST TMRmn ERmn (n = 2) Symbol TMRmn SPLIT (n = 1, 3)

- Page 165 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-11. Format of Timer Mode Register mn (TMRmn) (4/4) Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03) After reset: 0000H Symbol MAST TMRmn ERmn (n = 2) Symbol TMRmn SPLIT (n = 1, 3)

-

Page 166: Timer Status Register Mn (Tsrmn)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.4 Timer status register mn (TSRmn) The TSRmn register indicates the overflow status of the counter of channel n. The TSRmn register is valid only in the capture mode (MDmn3 to MDmn1 = 010B) and capture & one-count mode (MDmn3 to MDmn1 = 110B). -

Page 167: Timer Channel Enable Status Register M (Tem)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.5 Timer channel enable status register m (TEm) The TEm register is used to enable or stop the timer operation of each channel. Each bit of the TEm register corresponds to each bit of the timer channel start register m (TSm) and the timer channel stop register m (TTm). -

Page 168: Timer Channel Start Register M (Tsm)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.6 Timer channel start register m (TSm) The TSm register is a trigger register that is used to initialize timer count register mn (TCRmn) and start the counting operation of each channel. When a bit of this register is set to 1, the corresponding bit of timer channel enable status register m (TEm) is set to 1. -

Page 169: Timer Channel Stop Register M (Ttm)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.7 Timer channel stop register m (TTm) The TTm register is a trigger register that is used to stop the counting operation of each channel. When a bit of this register is set to 1, the corresponding bit of timer channel enable status register m (TEm) is cleared to 0. -

Page 170: Timer Input Select Register 0 (Tis0)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.8 Timer input select register 0 (TIS0) The TIS0 register is used to select the channel 1 of unit 0 timer input. The TIS0 register can be set by an 8-bit memory manipulation instruction. -

Page 171: Timer Output Enable Register M (Toem)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.9 Timer output enable register m (TOEm) The TOEm register is used to enable or disable timer output of each channel. Channel n for which timer output has been enabled becomes unable to rewrite the value of the TOmn bit of timer output register m (TOm) described later by software, and the value reflecting the setting of the timer output function through the count operation is output from the timer output pin (TOmn). -

Page 172: Timer Output Register M (Tom)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.10 Timer output register m (TOm) The TOm register is a buffer register of timer output of each channel. The value of each bit in this register is output from the timer output pin (TOmn) of each channel. -

Page 173: Timer Output Level Register M (Tolm)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.11 Timer output level register m (TOLm) The TOLm register is a register that controls the timer output level of each channel. The setting of the inverted output of channel n by this register is reflected at the timing of set or reset of the timer output signal while the timer output is enabled (TOEmn = 1) in the Slave channel output mode (TOMmn = 1). -

Page 174: Timer Output Mode Register M (Tomm)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.12 Timer output mode register m (TOMm) The TOMm register is used to control the timer output mode of each channel. When a channel is used for the independent channel operation function, set the corresponding bit of the channel to be used to 0. -

Page 175: Noise Filter Enable Register 1 (Nfen1)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.13 Noise filter enable register 1 (NFEN1) The NFEN1 register is used to set whether the noise filter can be used for the timer input signal to each channel. Enable the noise filter by setting the corresponding bits to 1 on the pins in need of noise removal. -

Page 176: Port Mode Registers 1, 3 ( Pm1, Pm3)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.3.14 Port mode registers 1, 3 ( PM1, PM3) These registers set input/output of ports 1 and 3 in 1-bit units. When using the ports (such as P13/TO00/TI00, and P33/TO02/TI02/SSI00) to be shared with the timer output pin for timer output, set the port mode register (PMxx) bit and port register (Pxx) bit corresponding to each port to 0. -

Page 177: Basic Rules Of Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.4 Basic Rules of Timer Array Unit 6.4.1 Basic rules of simultaneous channel operation function When simultaneously using multiple channels, namely, a combination of a master channel (a reference timer mainly counting the cycle) and slave channels (timers operating according to the master channel), the following rules apply. - Page 178 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Example 1 TAU0 Channel group (simultaneous channel CK00 Channel 0: Master operation function) CK01 Channel 1: Independent channel operation function * A channel that operates independent channel operation function may be between Channel 2: Slave a master and a slave of channel group.

-

Page 179: Basic Rules Of 8-Bit Timer Operation Function (Channels 1 And 3 Only)

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.4.2 Basic rules of 8-bit timer operation function (channels 1 and 3 only) The 8-bit timer operation function makes it possible to use a 16-bit timer channel in a configuration consisting of two 8- bit timer channels. -

Page 180: Operation Of Counter

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.5 Operation of Counter 6.5.1 Count clock (f TCLK The count clock (f ) of the timer array unit can be selected between following by CCSmn bit of timer mode register TCLK mn (TMRmn). - Page 181 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (2) When valid edge of input signal via the TImn pin is selected (CCSmn = 1) The count clock (f ) becomes the signal that detects valid edge of input signal via the TImn pin and...

-

Page 182: Start Timing Of Counter

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.5.2 Start timing of counter Timer count register mn (TCRmn) becomes enabled to operation by setting of TSmn bit of timer channel start register m (TSm). Operations from count operation enabled state to timer count Register mn (TCRmn) count start is shown in Table 6-5. -

Page 183: Operation Of Counter

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.5.3 Operation of counter Here, the counter operation in each mode is explained. (1) Operation of interval timer mode <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit. Timer count register mn (TCRmn) holds the initial value until count clock generation. - Page 184 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (2) Operation of event counter mode <1> Timer count register mn (TCRmn) holds its initial value while operation is stopped (TEmn = 0). <2> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

- Page 185 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (3) Operation of capture mode (input pulse interval measurement) <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit. <2> Timer count register mn (TCRmn) holds the initial value until count clock generation.

- Page 186 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (4) Operation of one-count mode <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit. <2> Timer count register mn (TCRmn) holds the initial value until start trigger generation. <3> Rising edge of the TImn input is detected.

- Page 187 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (5) Operation of capture & one-count mode (high-level width measurement) <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit of timer channel start register m (TSm). <2> Timer count register mn (TCRmn) holds the initial value until start trigger generation.

-

Page 188: Channel Output (Tomn Pin) Control

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.6 Channel Output (TOmn pin) Control 6.6.1 TOmn pin output circuit configuration Figure 6-30. Output Circuit Configuration <5> TOmn register Interrupt signal of the master channel (INTTMmn) TOmn pin Interrupt signal of the slave channel... -

Page 189: Tomn Pin Output Setting

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.6.2 TOmn pin output setting The following figure shows the procedure and status transition of the TOmn output pin from initial setting to timer operation start. Figure 6-31. Status Transition from Timer Output Setting to Operation Start... -

Page 190: Cautions On Channel Output Operation

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.6.3 Cautions on channel output operation (1) Changing values set in the registers TOm, TOEm, and TOLm during timer operation Since the timer operations (operations of timer count register mn (TCRmn) and timer data register mn (TDRmn)) - Page 191 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (2) Default level of TOmn pin and output level after timer operation start The change in the output level of the TOmn pin when timer output register m (TOm) is written while timer output is disabled (TOEmn = 0), the initial level is changed, and then timer output is enabled (TOEmn = 1) before port output is enabled, is shown below.

- Page 192 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (b) When operation starts with slave channel output mode (TOMmp = 1) setting (PWM output)) When slave channel output mode (TOMmp = 1), the active level is determined by timer output level register m (TOLm) setting.

- Page 193 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT (3) Operation of TOmn pin in slave channel output mode (TOMmn = 1) (a) When timer output level register m (TOLm) setting has been changed during timer operation When the TOLm register setting has been changed during timer operation, the setting becomes valid at the generation timing of the TOmn pin change condition.

- Page 194 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-35. Set/Reset Timing Operating Statuses (1) Basic operation timing TCLK INTTMmn Internal reset Master signal channel TOmn pin/ TOmn Toggle Toggle Internal set signal 1 clock delay INTTMmp Slave channel Internal reset signal...

-

Page 195: Collective Manipulation Of Tomn Bit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.6.4 Collective manipulation of TOmn bit In timer output register m (TOm), the setting bits for all the channels are located in one register in the same way as timer channel start register m (TSm). Therefore, the TOmn bit of all the channels can be manipulated collectively. -

Page 196: Timer Interrupt And Tomn Pin Output At Operation Start

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.6.5 Timer interrupt and TOmn pin output at operation start In the interval timer mode or capture mode, the MDmn0 bit in timer mode register mn (TMRmn) sets whether or not to generate a timer interrupt at count start. -

Page 197: Timer Input (Timn) Control

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.7 Timer Input (TImn) Control 6.7.1 TImn input circuit configuration A signal is input from a timer input pin, goes through a noise filter and an edge detector, and is sent to a timer controller. -

Page 198: Cautions On Channel Input Operation

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.7.3 Cautions on channel input operation When a timer input pin is set as unused, the operating clock is not supplied to the noise filter. Therefore, after settings are made to use the timer input pin, the following wait time is necessary before a trigger is specified to enable operation of the channel corresponding to the timer input pin. -

Page 199: Independent Channel Operation Function Of Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.8 Independent Channel Operation Function of Timer Array Unit 6.8.1 Operation as interval timer/square wave output (1) Interval timer The timer array unit can be used as a reference timer that generates INTTMmn (timer interrupt) at fixed intervals. - Page 200 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-41. Block Diagram of Operation as Interval Timer/Square Wave Output CKm1 Note Operation clock Timer counter Output CKm0 TOmn pin register mn (TCRmn) controller Interrupt Timer data Interrupt signal TSmn controller register mn(TDRmn) (INTTMmn) Note When channels 1 and 3, the clock can be selected from CKm0, CKm1, CKm2 and CKm3.

- Page 201 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-43. Example of Set Contents of Registers During Operation as Interval Timer/Square Wave Output (1/2) (a) Timer mode register mn (TMRmn) TMRmn Note CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2...

- Page 202 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-43. Example of Set Contents of Registers During Operation as Interval Timer/Square Wave Output (2/2) (d) Timer output level register m (TOLm) Bit n TOLm 0: Cleared to 0 when TOMmn = 0 (master channel output mode)

- Page 203 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-44. Operation Procedure of Interval Timer/Square Wave Output Function (1/2) Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

- Page 204 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-44. Operation Procedure of Interval Timer/Square Wave Output Function (2/2) Software Operation Hardware Status To hold the TOmn pin output level Clears the TOmn bit to 0 after the value to stop be held is set to the port register.

-

Page 205: Operation As External Event Counter

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.8.2 Operation as external event counter The timer array unit can be used as an external event counter that counts the number of times the valid input edge (external event) is detected in the TImn pin. When a specified count value is reached, the event counter generates an interrupt. - Page 206 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-46. Example of Basic Timing of Operation as External Event Counter TSmn TEmn TImn TCRmn 0000H TDRmn 0003H 0002H INTTMmn 4 events 4 events 3 events Remarks 1. m: Unit number (m = 0), n: Channel number (n = 0 to 3) 2.

- Page 207 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-47. Example of Set Contents of Registers in External Event Counter Mode (1/2) (a) Timer mode register mn (TMRmn) TMRmn Note CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2 MDmn1 MDmn0...

- Page 208 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-47. Example of Set Contents of Registers in External Event Counter Mode (2/2) (d) Timer output level register m (TOLm) Bit n TOLm 0: Cleared to 0 when TOMmn = 0 (master channel output mode).

- Page 209 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-48. Operation Procedure When External Event Counter Function Is Used Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

-

Page 210: Operation As Input Pulse Interval Measurement

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.8.3 Operation as input pulse interval measurement The count value can be captured at the TImn valid edge and the interval of the pulse input to TImn can be measured. In addition, the count value can be captured by using software operation (TSmn = 1) as a capture trigger while the TEmn bit is set to 1. - Page 211 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-50. Example of Basic Timing of Operation as Input Pulse Interval Measurement (MDmn0 = 0) TSmn TEmn TImn FFFFH TCRmn 0000H TDRmn 0000H INTTMmn Remarks 1. m: Unit number (m = 0)n: Channel number (n = 0 to 3) 2.

- Page 212 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-51. Example of Set Contents of Registers to Measure Input Pulse Interval (a) Timer mode register mn (TMRmn) TMRmn Note CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2 MDmn1 MDmn0 Operation mode of channel n...

- Page 213 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-52. Operation Procedure When Input Pulse Interval Measurement Function Is Used Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

-

Page 214: Operation As Input Signal High-/Low-Level Width Measurement

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.8.4 Operation as input signal high-/low-level width measurement By starting counting at one edge of the TImn pin input and capturing the number of counts at another edge, the signal width (high-level width/low-level width) of TImn can be measured. The signal width of TImn can be calculated by the following expression. - Page 215 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-53. Block Diagram of Operation as Input Signal High-/Low-Level Width Measurement CKm1 Operation clock Note Timer counter CKm0 register mn (TCRmn) TNFENmn Timer data Interrupt NFEN1 Noise Edge Interrupt signal TImn pin register mn (TDRmn)

- Page 216 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-55. Example of Set Contents of Registers to Measure Input Signal High-/Low-Level Width (a) Timer mode register mn (TMRmn) TMRmn Note CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2 MDmn1 MDmn0 Operation mode of channel n 110B: Capture &...

- Page 217 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-56. Operation Procedure When Input Signal High-/Low-Level Width Measurement Function Is Used Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

-

Page 218: Operation As Delay Counter

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.8.5 Operation as delay counter It is possible to start counting down when the valid edge of the TImn pin input is detected (an external event), and then generate INTTMmn (a timer interrupt) after any specified interval. - Page 219 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-58. Example of Basic Timing of Operation as Delay Counter TSmn TEmn TImn FFFFH TCRmn 0000H TDRmn INTTMmn Remarks 1. m: Unit number (m = 0), n: Channel number (n = 0 to 3) 2.

- Page 220 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-59. Example of Set Contents of Registers to Delay Counter (1/2) (a) Timer mode register mn (TMRmn) TMRmn Note CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2 MDmn1 MDmn0 Operation mode of channel n...

- Page 221 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-59. Example of Set Contents of Registers to Delay Counter (2/2) (d) Timer output level register m (TOLm) Bit n TOLm 0: Cleared to 0 when TOMmn = 0 (master channel output mode).

- Page 222 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-60. Operation Procedure When Delay Counter Function Is Used Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

-

Page 223: Simultaneous Channel Operation Function Of Timer Array Unit

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.9 Simultaneous Channel Operation Function of Timer Array Unit 6.9.1 Operation as one-shot pulse output function By using two channels as a set, a one-shot pulse having any delay pulse width can be generated from the signal input to the TImn pin. - Page 224 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-61. Block Diagram of Operation as One-Shot Pulse Output Function Master channel (one-count mode) CKm1 Operation clock Timer counter register mn (TCRmn) CKm0 TNFENmn TSmn Timer data Interrupt Interrupt signal register mn (TDRmn)

- Page 225 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-62. Example of Basic Timing of Operation as One-Shot Pulse Output Function TSmn TEmn TImn Master FFFFH channel TCRmn 0000H TDRmn TOmn INTTMmn TSmp TEmp FFFFH TCRmp Slave 0000H channel TDRmp TOmp INTTMmp Remarks 1.

- Page 226 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-63. Example of Set Contents of Registers When One-Shot Pulse Output Function Is Used (Master Channel) (a) Timer mode register mn (TMRmn) TMRmn CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2...

- Page 227 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-64. Example of Set Contents of Registers When One-Shot Pulse Output Function Is Used (Slave Channel) (a) Timer mode register mp (TMRmp) TMRmp Note CKSmp1 CKSmp0 CCSmp STSmp2 STSmp1 STSmp0 CISmp1 CISmp0 MDmp3...

- Page 228 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-65. Operation Procedure of One-Shot Pulse Output Function (1/2) Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

- Page 229 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-65. Operation Procedure of One-Shot Pulse Output Function (2/2) Software Operation Hardware Status Operation Sets the TOEmp bit (slave) to 1 (only when operation is start resumed). The TSmn (master) and TSmp (slave) bits of timer channel start register m (TSm) are set to 1 at the same time.

-

Page 230: Operation As Pwm Function

RL78/G1P CHAPTER 6 TIMER ARRAY UNIT 6.9.2 Operation as PWM function Two channels can be used as a set to generate a pulse of any period and duty factor. The period and duty factor of the output pulse can be calculated by the following expressions. - Page 231 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-66. Block Diagram of Operation as PWM Function Master channel (interval timer mode) CKm1 Operation clock Timer counter register mn (TCRmn) CKm0 Timer data Interrupt Interrupt signal TSmn register mn (TDRmn) controller (INTTMmn)

- Page 232 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-67. Example of Basic Timing of Operation as PWM Function TSmn TEmn FFFFH Master TCRmn channel 0000H TDRmn TOmn INTTMmn TSmp TEmp FFFFH TCRmp Slave 0000H channel TDRmp TOmp INTTMmp Remark 1. m: Unit number (m = 0), n: Master channel number (n = 0, 2) p: Slave channel number (n = 0: p = 1, 2, 3, n = 2: p = 3) 2.

- Page 233 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-68. Example of Set Contents of Registers When PWM Function (Master Channel) Is Used (a) Timer mode register mn (TMRmn) TMRmn CKSmn1 CKSmn0 CCSmn STSmn2 STSmn1 STSmn0 CISmn1 CISmn0 MDmn3 MDmn2 MDmn1 MDmn0...

- Page 234 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-69. Example of Set Contents of Registers When PWM Function (Slave Channel) Is Used (a) Timer mode register mp (TMRmp) TMRmp Note CKSmp1 CKSmp0 CCSmp STSmp2 STSmp1 STSmp0 CISmp1 CISmp0 MDmp3 MDmp2 MDmp1...

- Page 235 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-70. Operation Procedure When PWM Function Is Used (1/2) Software Operation Hardware Status Input clock supply for timer array unit 0 is stopped. default (Clock supply is stopped and writing to each register is setting disabled.)

- Page 236 RL78/G1P CHAPTER 6 TIMER ARRAY UNIT Figure 6-70. Operation Procedure When PWM Function Is Used (2/2) Software Operation Hardware Status Operation Sets the TOEmp bit (slave) to 1 (only when operation is start resumed). The TSmn (master) and TSmp (slave) bits of timer...

-

Page 237: Operation As Multiple Pwm Output Function