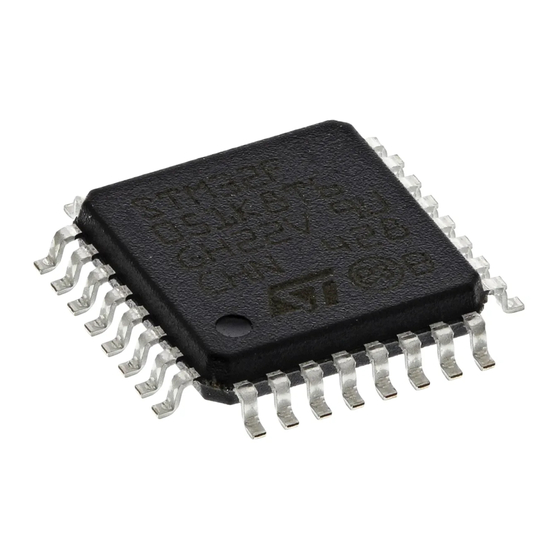

STMicroelectronics STM32F05 series Manuals

Manuals and User Guides for STMicroelectronics STM32F05 series. We have 1 STMicroelectronics STM32F05 series manual available for free PDF download: Reference Manual

STMicroelectronics STM32F05 series Reference Manual (742 pages)

advanced ARM-based 32-bit MCUs

Brand: STMicroelectronics

|

Category: Microcontrollers

|

Size: 10 MB

Table of Contents

-

-

-

-

Introduction62

-

-

-

-

-

-

GPIO Registers127

-

-

SYSCFG Registers135

-

-

(Syscfg_Exticr1)136

-

-

-

(Syscfg_Exticr2)138

-

(Syscfg_Exticr3)138

-

(Syscfg_Exticr4)139

-

-

-

-

DMA Introduction142

-

-

DMA Transactions143

-

Arbiter144

-

DMA Channels144

-

Error Management147

-

Interrupts147

-

-

DMA Registers150

-

DMA Register Map155

-

-

-

EXTI Registers163

-

-

Introduction168

-

-

-

Data Management183

-

ADC Interrupts191

-

ADC Registers192

-

-

-

-

DAC Data Format207

-

DAC Conversion207

-

DMA Request209

-

DAC Registers209

-

-

(Dac_Dhr12R1)211

-

-

-

(Dac_Dhr12L1)211

-

-

-

(Dac_Dhr8R1)212

-

-

DAC Register Map214

-

-

COMP Registers219

-

-

-

Time-Base Unit225

-

Counter Modes227

-

Clock Sources237

-

PWM Input Mode243

-

PWM Mode245

-

One-Pulse Mode255

-

Debug Mode264

-

-

TIM1 Registers265

-

-

-

Time-Base Unit293

-

Counter Modes295

-

Clock Sources304

-

PWM Input Mode310

-

PWM Mode312

-

One-Pulse Mode315

-

Debug Mode328

-

-

-

-

Tim3_Dier)335

-

-

-

Tim3_Ccmr1)339

-

-

-

Tim3_Ccmr2)342

-

-

-

Tim3_Ccr1)346

-

Tim3_Ccr2)346

-

-

-

Tim3_Ccr3)348

-

Tim3_Ccr4)348

-

-

-

Tim3_Dmar)349

-

-

-

-

Time-Base Unit354

-

Counter Modes356

-

Clock Source359

-

PWM Mode363

-

Debug Mode364

-

-

TIM14 Registers365

-

-

-

Time-Base Unit379

-

Counter Modes380

-

Clock Sources384

-

PWM Mode391

-

One-Pulse Mode397

-

Debug Mode401

-

-

TIM15 Registers402

-

-

-

Tim17_Dier)424

-

-

-

Tim17_Egr)426

-

-

-

Tim17_Ccmr1)427

-

-

-

Tim17_Ccer)430

-

-

-

Tim17_Rcr)433

-

-

-

Tim17_Ccr1)433

-

-

-

Tim17_Bdtr)434

-

-

-

Tim17_Dmar)436

-

-

-

-

Time-Base Unit441

-

Counter Modes443

-

Clock Source446

-

Debug Mode446

-

-

TIM6 Registers447

-

-

Introduction453

-

-

Window Option453

-

Debug Mode454

-

-

IWDG Registers455

-

-

-

Debug Mode464

-

WWDG Registers465

-

-

-

Mode Selection472

-

Software Reset476

-

Data Transfer477

-

I2C Slave Mode479

-

I2C Master Mode487

-

Table 70. Table503

-

Smbus Slave Mode506

-

Error Conditions514

-

DMA Requests516

-

I 2 C Interrupts517

-

I 2 C Debug Mode519

-

I 2 C Registers519

-

I2C Register Map534

-

-

Introduction535

-

-

Tamper Detection546

-

Alarm Output548

-

RTC Interrupts549

-

RTC Registers550

-

-

(Rtc_Tafcr)565

-

-

RTC Register Map569

-

-

-

-

Transmitter577

-

Receiver579

-

Parity Control591

-

Smartcard Mode597

-

USART Interrupts609

-

USART Registers611

-

-

Introduction634

-

I²S Features635

-

-

Initialize SPI642

-

SPI Status Flags646

-

SPI Error Flags647

-

SPI Interrupts652

-

-

Clock Generator660

-

I 2 S Slave Mode664

-

I 2 S Interrupts669

-

DMA Features669

-

-

-

-

Introduction681

-

-

Reset and Clocks684

-

Max Count Error686

-

Acquisition Mode688

-

TSC Interrupts689

-

TSC Registers690

-

TSC Register Map697

-

-

-

Introduction699

-

-

HDMI-CEC Pin700

-

Bit Timing701

-

-

Arbitration702

-

Error Handling704

-

Bit Error704

-

Message Error704

-

-

-

-

-

Overview718

-

SW Debug Port721

-

SW-DP Registers723

-

SW-AP Registers725

-

Core Debug725

-

-

DBG Register Map732

-

-

Revision History

741

Advertisement

Advertisement

Related Products

- STMicroelectronics STM32F050G6

- STMicroelectronics STM32F050K4

- STMicroelectronics STM32F050G4

- STMicroelectronics STM32F050F6

- STMicroelectronics STM32F050F4

- STMicroelectronics STM32F050K6

- STMicroelectronics STM32F050C4

- STMicroelectronics STM32F050C6

- STMicroelectronics STM32F038F6

- STMicroelectronics STM32F042C6