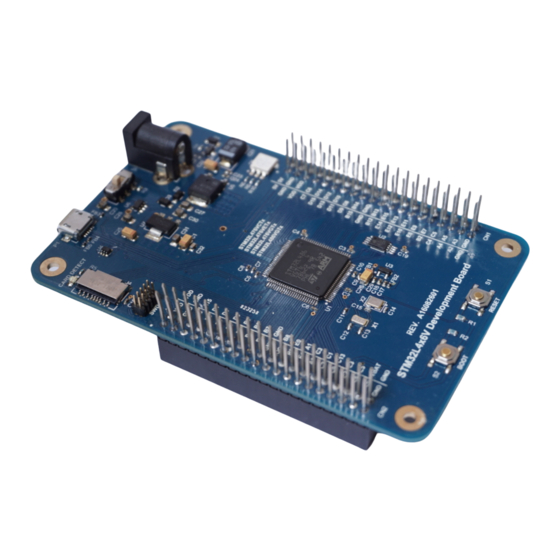

ST STM32L4x6 Manuals

Manuals and User Guides for ST STM32L4x6. We have 1 ST STM32L4x6 manual available for free PDF download: Reference Manual

ST STM32L4x6 Reference Manual (1693 pages)

Brand: ST

|

Category: Microcontrollers

|

Size: 31 MB

Table of Contents

-

-

-

Bit Banding71

-

-

-

-

Introduction78

-

FLASH Interrupts105

-

FLASH Registers106

-

-

Firewall (FW)

121-

Introduction121

-

-

Firewall States126

-

-

-

Power Supplies133

-

Low-Power Modes141

-

Run Mode147

-

Low Power Modes149

-

Sleep Mode150

-

Table 22. Sleep150

-

Stop 0 Mode151

-

Stop 1 Mode153

-

Stop 2 Mode154

-

Standby Mode157

-

Shutdown Mode159

-

PWR Registers161

-

Reset179

-

-

-

Clocks181

-

HSE Clock185

-

HSI16 Clock186

-

MSI Clock187

-

LSE Clock188

-

LSI Clock189

-

ADC Clock191

-

Low-Power Modes195

-

Introduction254

-

GPIO Registers264

-

-

Introduction286

-

-

Introduction295

-

-

DMA Channels298

-

Error Management301

-

-

DMA Registers307

-

Introduction324

-

-

-

AHB Interface345

-

-

Introduction400

-

-

Introduction426

-

-

-

Clocks431

-

-

Trigger Occurs458

-

Data Management463

-

Oversampler478

-

Dual ADC Modes483

-

-

-

Introduction541

-

-

DAC Conversion544

-

Noise Generation546

-

DAC Registers559

-

-

-

COMP Registers584

-

Introduction589

-

OPAMP Modes591

-

Calibration594

-

OPAMP Registers597

-

-

Integrator Unit620

-

-

-

-

-

Common Driver662

-

Segment Driver665

-

Flowchart678

-

LCD Registers681

-

-

-

Reset and Clocks694

-

Acquisition Mode698

-

TSC Registers700

-

Introduction710

-

Operation711

-

RNG Registers712

-

-

Data Type729

-

Operating Modes731

-

Error Flags735

-

AES Interrupts737

-

AES Registers738

-

Counter Modes756

-

Clock Selection771

-

-

PWM Mode781

-

Debug Mode811

-

-

Counter Modes861

-

Is Not Used867

-

Clock Selection871

-

PWM Mode881

-

DMA Burst Mode900

-

Debug Mode901

-

-

Counter Modes936

-

Preloaded)939

-

Clock Selection941

-

PWM Mode949

-

Debug Mode964

-

TIM15 Registers965

-

-

Counting Mode1013

-

Preloaded)1015

-

Preloaded)1016

-

UIF Bit Remapping1016

-

Debug Mode1017

-

Introduction1023

-

-

Prescaler1026

-

Operating Mode1027

-

Timeout Function1028

-

Waveform Generation1029

-

Register Update1030

-

Counter Mode1031

-

LPTIM Interrupts1034

-

LPTIM Registers1035

-

-

-

Introduction1047

-

Window Option1048

-

Low-Power Freeze1049

-

-

IWDG Registers1050

-

-

-

RTC Main Features1064

-

-

Clock and Prescalers1067

-

Programmable Alarms1069

-

Reading the Calendar1071

-

Resetting the RTC1072

-

RTC Synchronization1073

-

Time-Stamp Function1076

-

Tamper Detection1077

-

RTC Interrupts1080

-

RTC Registers1081

-

Introduction1107

-

I2C Initialization1112

-

Software Reset1116

-

Data Transfer1117

-

I2C Slave Mode1119

-

I2C Master Mode1128

-

(Max T IDLE = 50 Μs)1147

-

Smbus Slave Mode1147

-

DMA Requests1157

-

Debug Mode1158

-

I2C Registers1160

-

-

Transmitter (USART)

1178-

USART Implementation1180

-

USART Transmitter1185

-

USART Receiver1187

-

USART Parity Control1201

-

USART Registers1222

-

Transmitter (LPUART)

1245-

LPUART Main Features1246

-

-

LPUART Transmitter1251

-

LPUART Receiver1253

-

LPUART Interrupts1266

-

LPUART Registers1268

-

Introduction1283

-

-

Configuration of SPI1292

-

SPI Status Flags1303

-

SPI Error Flags1304

-

NSS Pulse Mode1305

-

CRC Calculation1306

-

SPI Interrupts1308

-

SPI Registers1309

-

SAI Main Features1319

-

-

Main SAI Modes1321

-

Audio Data Size1323

-

Slot Configuration1326

-

SAI Clock Generator1328

-

Internal Fifos1330

-

SPDIF Output1334

-

Specific Features1336

-

Error Flags1341

-

Disabling the SAI1344

-

-

SAI Interrupts1345

-

SAI Registers1346

-

Introduction1363

-

SWPMI Main Features1364

-

-

Reception Procedure1372

-

Error Management1377

-

Loopback Mode1379

-

SWPMI Registers1381

-

SDMMC Main Features1393

-

-

SDMMC APB2 Interface1408

-

-

Block Write1411

-

Block Read1412

-

Card Status Register1418

-

SD Status Register1420

-

Table 229. SD Status1421

-

SD I/O Mode1425

-

Table 241. Lock Card1428

-

Response Formats1429

-

R3 (OCR Register)1431

-

SDMMC Registers1435

-

Introduction1451

-

Test Mode1455

-

-

Identifier Filtering1460

-

Message Storage1464

-

Error Management1466

-

Bxcan Interrupts1469

-

CAN Registers1470

-

CAN Filter Registers1487

-

Introduction1495

-

Host-Mode Features1496

-

USB Host1505

-

Power Options1511

-

OTG_FS Interrupts1517

-

OTG_FS Registers1522

-

Host-Mode Registers1551

-

Core Initialization1594

-

Host Initialization1595

-

SW Debug Port1655

-

-

Advertisement

Advertisement