Table of Contents

Advertisement

Quick Links

Introduction

This reference manual targets application developers. It provides complete information on

how to use the STM32L4x6 microcontroller memory and peripherals.

The STM32L4x6 is a family of microcontrollers with different memory sizes, packages and

peripherals.

For ordering information, mechanical and electrical device characteristics please refer to the

corresponding datasheets.

For information on the ARM

Reference Manual.

Related documents

• Cortex

• STM32L476xx, STM32L486xx, STM32L476xx and STM32L486xx datasheet

• Cortex

December 2015

STM32L4x6 advanced ARM

®

Cortex

®

-M4 Technical Reference Manual, available from: http://infocenter.arm.com

®

-M4 programming manual (PM0214)

DocID024597 Rev 3

Reference manual

®

-M4 core, please refer to the Cortex

RM0351

®

-based 32-bit MCUs

®

-M4 Technical

1/1693

www.st.com

1

Advertisement

Table of Contents

Summary of Contents for ST STM32L4x6

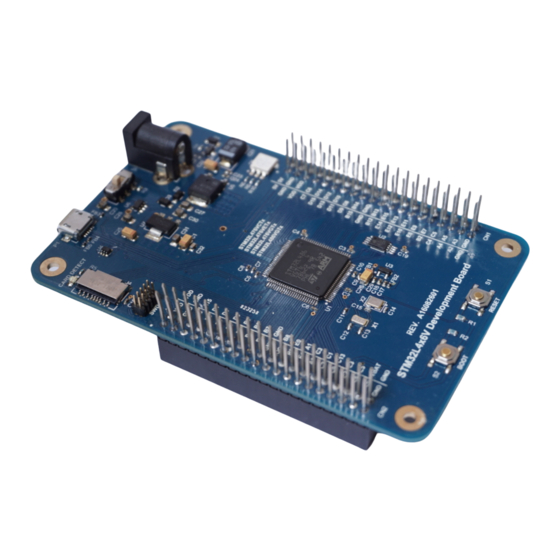

- Page 1 This reference manual targets application developers. It provides complete information on how to use the STM32L4x6 microcontroller memory and peripherals. The STM32L4x6 is a family of microcontrollers with different memory sizes, packages and peripherals. For ordering information, mechanical and electrical device characteristics please refer to the corresponding datasheets.

-

Page 2: Table Of Contents

Contents RM0351 Contents Documentation conventions ....... . . 61 List of abbreviations for registers ....... 61 Glossary . - Page 3 RM0351 Contents 3.3.6 Flash main memory erase sequences ......86 3.3.7 Flash main memory programming sequences ....87 3.3.8 Read-while-write (RWW) .

- Page 4 Contents RM0351 4.3.3 Firewall segments ........123 4.3.4 Segment accesses and properties .

- Page 5 RM0351 Contents 5.3.9 Standby mode ......... . . 157 5.3.10 Shutdown mode .

- Page 6 Contents RM0351 6.2.3 MSI clock ..........187 6.2.4 PLL .

- Page 7 RM0351 Contents 6.4.20 APB1 peripheral clock enable register 2 (RCC_APB1ENR2) ..230 6.4.21 APB2 peripheral clock enable register (RCC_APB2ENR) ..232 6.4.22 AHB1 peripheral clocks enable in Sleep and Stop modes register (RCC_AHB1SMENR) .

- Page 8 Contents RM0351 7.4.1 GPIO port mode register (GPIOx_MODER) (x =A..H) ... . . 264 7.4.2 GPIO port output type register (GPIOx_OTYPER) (x = A..H) ..264 7.4.3 GPIO port output speed register (GPIOx_OSPEEDR) (x = A..H) .

- Page 9 RM0351 Contents Connection summary ........286 Interconnection details .

- Page 10 Contents RM0351 10.5.1 DMA interrupt status register (DMA_ISR) ..... . 307 10.5.2 DMA interrupt flag clear register (DMA_IFCR) ....308 10.5.3 DMA channel x configuration register (DMA_CCRx) (x = 1..7 , where x = channel number) .

- Page 11 RM0351 Contents 12.5.7 Interrupt mask register 2 (EXTI_IMR2) ......332 12.5.8 Event mask register 2 (EXTI_EMR2) ......333 12.5.9 Rising trigger selection register 2 (EXTI_RTSR2) .

- Page 12 Contents RM0351 14.6.1 External memory interface signals ......386 14.6.2 NAND Flash supported memories and transactions ....388 14.6.3 Timing diagrams for NAND Flash memory .

- Page 13 RM0351 Contents 15.5.8 QUADSPI alternate bytes registers (QUADSPI_ABR) ... . 421 15.5.9 QUADSPI data register (QUADSPI_DR) ..... . . 422 15.5.10 QUADSPI polling status mask register (QUADSPI _PSMKR) .

- Page 14 Contents RM0351 16.3.24 End of conversion sequence (EOS, JEOS) ..... 461 16.3.25 Timing diagrams example (single/continuous modes, hardware/software triggers) ....... . . 462 16.3.26 Data management .

- Page 15 RM0351 Contents 16.6.1 ADC Common status register (ADCx_CSR) ....532 16.6.2 ADC common control register (ADCx_CCR) ....534 16.6.3 ADC common regular data register for dual mode (ADCx_CDR) .

- Page 16 Contents RM0351 17.5.9 Dual DAC 12-bit right-aligned data holding register (DAC_DHR12RD) ........564 17.5.10 DUAL DAC 12-bit left aligned data holding register (DAC_DHR12LD) .

- Page 17 RM0351 Contents 19.4 COMP low-power modes ........582 19.5 COMP interrupts .

- Page 18 Contents RM0351 21.3.6 Parallel data inputs ........616 21.3.7 Channel selection .

- Page 19 RM0351 Contents 21.7.11 DFSDM analog watchdog status register (DFSDMx_AWSR) ..645 21.7.12 DFSDM analog watchdog clear flag register (DFSDMx_AWCFR) . . . 645 21.7.13 DFSDM Extremes detector maximum register (DFSDMx_EXMAX) . . 646 21.7.14 DFSDM Extremes detector minimum register (DFSDMx_EXMIN) . . . 646 21.7.15 DFSDM conversion timer register (DFSDMx_CNVTIMR) .

- Page 20 Contents RM0351 23.3.4 Charge transfer acquisition sequence ......695 23.3.5 Spread spectrum feature ........696 23.3.6 Max count error .

- Page 21 RM0351 Contents 25.3 AES functional description ........716 25.4 Encryption and derivation keys .

- Page 22 Contents RM0351 25.14.18 AES register map ......... 749 Advanced-control timers (TIM1/TIM8) .

- Page 23 RM0351 Contents 26.4.2 TIM1/TIM8 control register 2 (TIMx_CR2) ..... . 813 26.4.3 TIM1/TIM8 slave mode control register (TIMx_SMCR) ... . 816 26.4.4 TIM1/TIM8 DMA/interrupt enable register (TIMx_DIER) .

- Page 24 Contents RM0351 27.3.3 Clock selection ......... . . 871 27.3.4 Capture/compare channels .

- Page 25 RM0351 Contents 27.4.18 TIMx DMA address for full transfer (TIMx_DMAR) ....924 27.4.19 TIM2 option register 1 (TIM2_OR1) ......925 27.4.20 TIM3 option register 1 (TIM3_OR1) .

- Page 26 Contents RM0351 28.5.5 TIM15 status register (TIM15_SR) ......970 28.5.6 TIM15 event generation register (TIM15_EGR) ....972 28.5.7 TIM15 capture/compare mode register 1 (TIM15_CCMR1) .

- Page 27 RM0351 Contents Basic timers (TIM6/TIM7) ........1010 29.1 TIM6/TIM7 introduction .

- Page 28 Contents RM0351 30.4.12 Encoder mode ......... . 1031 30.5 LPTIM low power modes .

- Page 29 RM0351 Contents System window watchdog (WWDG) ......1056 33.1 Introduction ..........1056 33.2 WWDG main features .

- Page 30 Contents RM0351 34.5 RTC interrupts ......... . . 1080 34.6 RTC registers .

- Page 31 RM0351 Contents 35.4.8 I2C master mode ........1128 35.4.9 I2C_TIMINGR register configuration examples .

- Page 32 Contents RM0351 36.5.4 USART baud rate generation ......1194 36.5.5 Tolerance of the USART receiver to clock deviation ... . . 1196 36.5.6 USART auto baud rate detection .

- Page 33 RM0351 Contents 37.4.1 LPUART character description ......1248 37.4.2 LPUART transmitter ........1251 37.4.3 LPUART receiver .

- Page 34 Contents RM0351 38.4.8 Procedure for enabling SPI ....... . 1293 38.4.9 Data transmission and reception procedures .

- Page 35 RM0351 Contents 39.4 SAI interrupts ..........1345 39.5 SAI registers .

- Page 36 Contents RM0351 40.6.7 SWPMI Transmit data register (SWPMI_TDR) ....1389 40.6.8 SWPMI Receive data register (SWPMI_RDR) ....1390 40.6.9 SWPMI Option register (SWPMI_OR) .

- Page 37 RM0351 Contents 41.6.1 SDIO I/O read wait operation by SDMMC_D2 signalling ..1433 41.6.2 SDIO read wait operation by stopping SDMMC_CK ... . . 1434 41.6.3 SDIO suspend/resume operation .

- Page 38 Contents RM0351 42.5.1 Silent mode ..........1455 42.5.2 Loop back mode .

- Page 39 RM0351 Contents 43.6.1 SRP-capable peripheral ........1502 43.6.2 Peripheral states .

- Page 40 Contents RM0351 43.15.12 OTG general core configuration register (OTG_GCCFG) ..1542 43.15.13 OTG core ID register (OTG_CID) ......1543 43.15.14 OTG core LPM configuration register (OTG_GLPMCFG) .

- Page 41 RM0351 Contents 43.15.39 OTG device V discharge time register (OTG_DVBUSDIS) ........1570 43.15.40 OTG device V pulsing time register (OTG_DVBUSPULSE) .

- Page 42 Using serial wire and releasing the unused debug pins as GPIOs . . 1650 44.5 STM32L4x6 JTAG TAP connection ......1650 44.6 ID codes and locking mechanism .

- Page 43 44.17.7 Asynchronous mode ........1675 44.17.8 TRACECLKIN connection inside the STM32L4x6 ....1675 44.17.9 TPIU registers .

- Page 44 Table 35. STM32L4x6 peripherals interconnect matrix ........286 Table 36.

- Page 45 RM0351 List of tables Table 49. NAND bank selection ........... . 348 Table 50.

- Page 46 List of tables RM0351 for master ADC, 0x100 for slave ADC) ........538 Table 101.

- Page 47 Table 190. I2C register map and reset values ......... 1176 Table 191. STM32L4x6 USART/UART/LPUART features ....... . 1180 Table 192.

- Page 48 Table 205. STM32L4x6 SPI implementation ........

- Page 49 RM0351 List of tables Table 250. Response type and SDMMC_RESPx registers ....... 1439 Table 251.

- Page 50 STM32L4x6 firewall connection schematics ........122...

- Page 51 RM0351 List of figures Figure 49. NAND Flash controller waveforms for common memory access ....389 Figure 50. Access to non ‘CE don’t care’ NAND-Flash ........390 Figure 51.

- Page 52 List of figures RM0351 (DISCEN=1, JDISCEN=1) ..........472 Figure 96.

- Page 53 RM0351 List of figures Figure 145. PGA mode, internal gain setting (x2/x4/x8/x16), inverting input used for filtering ............. . . 594 Figure 146.

- Page 54 List of figures RM0351 Figure 196. Counter timing diagram, update event when ARPE=1 (TIMx_ARR preloaded) ..759 Figure 197. Counter timing diagram, internal clock divided by 1 ......761 Figure 198.

- Page 55 RM0351 List of figures Figure 248. Control circuit in external clock mode 2 + trigger mode ......809 Figure 249.

- Page 56 List of figures RM0351 Figure 299. TIM16 and TIM17 block diagram ......... . . 933 Figure 300.

- Page 57 RM0351 List of figures Figure 346. Encoder mode counting sequence ......... 1033 Figure 347.

- Page 58 List of figures RM0351 Figure 398. ISO 7816-3 asynchronous protocol ........1208 Figure 399.

- Page 59 RM0351 List of figures Figure 448. Tristate strategy on SD output line on an inactive slot ......1340 Figure 449.

- Page 60 List of figures RM0351 Figure 500. Host-mode FIFO address mapping and AHB FIFO access mapping ....1514 Figure 501. Interrupt hierarchy............1517 Figure 502.

-

Page 61: Documentation Conventions

RM0351 Documentation conventions Documentation conventions List of abbreviations for registers The following abbreviations are used in register descriptions: read/write (rw) Software can read and write to these bits. read-only (r) Software can only read these bits. write-only (w) Software can only write to this bit. Reading the bit returns the reset value. read/clear Software can read as well as clear this bit by writing 1. -

Page 62: System And Memory Overview

System and memory overview RM0351 System and memory overview System architecture The main system consists of 32-bit multilayer AHB bus matrix that interconnects: • Five masters: ® – Cortex -M4 with FPU core I-bus ® – Cortex -M4 with FPU core D-bus ®... -

Page 63: S0: I-Bus

RM0351 System and memory overview Figure 1. System architecture 2.1.1 S0: I-bus ® This bus connects the instruction bus of the Cortex -M4 core to the BusMatrix. This bus is used by the core to fetch instructions. The targets of this bus are the internal Flash memory, SRAM1, SRAM2 and external memories through FMC or QUADSPI. -

Page 64: S2: S-Bus

System and memory overview RM0351 2.1.3 S2: S-bus ® This bus connects the system bus of the Cortex -M4 core to the BusMatrix. This bus is used by the core to access data located in a peripheral or SRAM area. The targets of this bus are the SRAM1, the AHB1 peripherals including the APB1 and APB2 peripherals, the AHB2 peripherals and the external memories through the FMC or QUADSPI. -

Page 65: Memory Organization

RM0351 Memory organization 2.2.1 Introduction Program memory, data memory, registers and I/O ports are organized within the same linear 4-Gbyte address space. The bytes are coded in memory in Little Endian format. The lowest numbered byte in a word is considered the word’s least significant byte and the highest numbered byte the most significant. -

Page 66: Figure 2. Memory Map

RM0351 Figure 2. Memory map It is forbidden to access QUADSPI Flash bank area before having properly configured and enabled the QUADSPI peripheral. 66/1693 DocID024597 Rev 3... -

Page 67: Memory Map And Register Boundary Addresses

See the datasheet corresponding to your device for a comprehensive diagram of the memory map. The following table gives the boundary addresses of the peripherals available in the devices. Table 1. STM32L4x6 memory map and peripheral register boundary addresses Boundary address Size (bytes) Peripheral Peripheral register map Section 24.4.4: RNG register... - Page 68 RM0351 Table 1. STM32L4x6 memory map and peripheral register boundary addresses (continued) Boundary address Size (bytes) Peripheral Peripheral register map Section 23.6.11: TSC register 0x4002 4000 - 0x4002 43FF 1 KB 0x4002 3400 - 0x4002 3FFF 1 KB Reserved Section 13.4.6: CRC register...

- Page 69 RM0351 Table 1. STM32L4x6 memory map and peripheral register boundary addresses (continued) Boundary address Size (bytes) Peripheral Peripheral register map Section 28.6.20: TIM16&TIM17 0x4001 4800 - 0x4001 4BFF 1 KB TIM17 register map Section 28.6.20: TIM16&TIM17 0x4001 4400 - 0x4001 47FF...

- Page 70 RM0351 Table 1. STM32L4x6 memory map and peripheral register boundary addresses (continued) Boundary address Size (bytes) Peripheral Peripheral register map 0x4000 9800 - 0x4000 FFFF 26 KB Reserved Section 30.7.11: LPTIM register 0x4000 9400 - 0x4000 97FF 1 KB LPTIM2...

-

Page 71: Bit Banding

RM0351 Table 1. STM32L4x6 memory map and peripheral register boundary addresses (continued) Boundary address Size (bytes) Peripheral Peripheral register map Section 36.8.12: USART 0x4000 5000 - 0x4000 53FF 1 KB UART5 register map Section 36.8.12: USART 0x4000 4C00 - 0x4000 4FFF... -

Page 72: Embedded Sram

In the STM32L4x6 devices both the peripheral registers and the SRAM1 are mapped to a bit-band region, so that single bit-band write and read operations are allowed. The ®... -

Page 73: Sram2 Parity Check

RM0351 2.4.1 SRAM2 Parity check The user can enable the SRAM2 parity check using the option bit SRAM2_PE in the user option byte (refer to Section 3.4.1: Option bytes description). The data bus width is 36 bits because 4 bits are available for parity check (1 bit per byte) in order to increase memory robustness, as required for instance by Class B or SIL norms. -

Page 74: Sram2 Read Protection

RM0351 Table 2. SRAM2 organization (continued) Page number Start address End address Page 20 0x1000 5000 0x1000 53FF Page 21 0x1000 5400 0x1000 57FF Page 22 0x1000 5800 0x1000 5BFF Page 23 0x1000 5C00 0x1000 5FFF Page 24 0x1000 6000 0x1000 63FF Page 25 0x1000 6400... -

Page 75: Boot Configuration

Embedded Flash memory (FLASH) for more details. Boot configuration In the STM32L4x6, three different boot modes can be selected through the BOOT0 pin and nBOOT1 bit in the User option byte, as shown in the following table. Table 3. Boot modes... -

Page 76: Table 4. Memory Mapping Versus Boot Mode/Physical Remap

RM0351 Note: When booting from bank 2, in the application initialization code, you have to relocate the vector table to bank 2 base address. (0x0808 0000) using the NVIC exception table and offset register. Physical remap Once the boot pins are selected, the application software can modify the memory accessible in the code area (in this way the code can be executed through the ICode bus in place of the System bus). - Page 77 2. Even when aliased in the boot memory space, the related memory is still accessible at its original memory space. Embedded boot loader The embedded boot loader is located in the System memory, programmed by ST during production. Refer to AN2606 STM32 microcontroller system memory boot mode. DocID024597 Rev 3...

-

Page 78: Embedded Flash Memory (Flash)

Embedded Flash memory (FLASH) RM0351 Embedded Flash memory (FLASH) Introduction The Flash memory interface manages CPU AHB ICode and DCode accesses to the Flash memory. It implements the erase and program Flash memory operations and the read and write protection mechanisms. The Flash memory interface accelerates code execution with a system of instruction prefetch and cache lines. -

Page 79: Table 5. Flash Module - 1 Mb Dual Bank Organization

USART1, USART2, USART3, USB (DFU), I2C1, I2C2, I2C3, SPI1, SPI2, SPI3. It is programmed by STMicroelectronics when the device is manufactured, and protected against spurious write/erase operations. For further details, please refer to the AN2606 available from www.st.com. – 1 KByte (128 double word) OTP (one-time programmable) bytes for user data. -

Page 80: Table 6. Flash Module - 512 Kb Dual Bank Organization

Embedded Flash memory (FLASH) RM0351 Table 5. Flash module - 1 MB dual bank organization (continued) Size Flash area Flash memory addresses Name (bytes) Bank 1 0x1FFF 0000 - 0x1FFF 6FFF 28 K System memory Bank 2 0x1FFF 8000 - 0x1FFF EFFF 28 K Information block Bank 1... -

Page 81: Error Code Correction (Ecc)

RM0351 Embedded Flash memory (FLASH) Table 7. Flash module - 256 KB dual bank organization Size Flash area Flash memory addresses Name (bytes) 0x0800 0000 - 0x0800 07FF Page 0 0x0800 0800 - 0x0800 0FFF Page 1 0x0800 1000 - 0x0800 17FF Page 2 0x0800 1800 - 0x0800 1FFF Page 3... -

Page 82: Read Access Latency

Embedded Flash memory (FLASH) RM0351 When ECCC or ECCD is set, ADDR_ECC and BK_ECC are not updated if a new ECC error occurs. FLASH_ECCR is updated only when ECC flags are cleared. Note: For a virgin data: 0xFF FFFF FFFF FFFF FFFF, one error is detected and corrected but 2 errors detection is not supported. -

Page 83: Adaptive Real-Time Memory Accelerator (Art Accelerator™)

RM0351 Embedded Flash memory (FLASH) Decreasing the CPU frequency: Modify the CPU clock source by writing the SW bits in the RCC_CFGR register If needed, modify the CPU clock prescaler by writing the HPRE bits in RCC_CFGR Check that the new CPU clock source or/and the new CPU clock prescaler value is/are taken into account by reading the clock source status (SWS bits) or/and the AHB prescaler value (HPRE bits), respectively, in the RCC_CFGR register Program the new number of wait states to the LATENCY bits in... -

Page 84: Figure 3. Sequential 16 Bits Instructions Execution

Embedded Flash memory (FLASH) RM0351 Figure 3. Sequential 16 bits instructions execution When the code is not sequential (branch), the instruction may not be present in the currently used instruction line or in the prefetched instruction line. In this case (miss), the penalty in terms of number of cycles is at least equal to the number of wait states. -

Page 85: Flash Program And Erase Operations

RM0351 Embedded Flash memory (FLASH) If a loop is present in the current buffer, no new flash access is performed. Instruction cache memory (I-Cache) To limit the time lost due to jumps, it is possible to retain 32 lines of 4*64 bits in an instruction cache memory.This feature can be enabled by setting the instruction cache enable (ICEN) bit in the Flash access control register... -

Page 86: Flash Main Memory Erase Sequences

Embedded Flash memory (FLASH) RM0351 write (RWW)). On the contrary, during a program/erase operation to the Flash memory, any attempt to read the same Flash memory bank will stall the bus. The read operation will proceed correctly once the program/erase operation has completed. Unlocking the Flash memory After reset, write is not allowed in the Flash control register (FLASH_CR) -

Page 87: Flash Main Memory Programming Sequences

RM0351 Embedded Flash memory (FLASH) Check that no Flash memory operation is ongoing by checking the BSY bit in the FLASH_SR register Check and clear all error programming flags due to a previous programming. If not, PGSERR is set. Set the MER1 bit or/and MER2 (depending on the bank) in the Flash control register (FLASH_CR). - Page 88 Embedded Flash memory (FLASH) RM0351 automatically when PG bit is set, and disabled automatically when PG bit is cleared, except if the HSI16 is previously enabled with HSION in RCC_CR register. If the user needs to program only one word, double word must be completed with the erase value 0xFFFF FFFF to launch automatically the programming.

- Page 89 RM0351 Embedded Flash memory (FLASH) Programming errors Several kind of errors can be detected. In case of error, the Flash operation (programming or erasing) is aborted. • PROGERR: Programming Error In standard programming: PROGERR is set if the word to write is not previously erased (except if the value to program is full zero).

-

Page 90: Read-While-Write (Rww)

Embedded Flash memory (FLASH) RM0351 In fast programming: FASTERR is set if one of the following conditions occurs: – When FSTPG bit is set for more than 7µs which generates a time-out detection. – When the row fast programming has been interrupted by a MISSERR, PGAERR, WRPERR or SIZERR. - Page 91 RM0351 Embedded Flash memory (FLASH) Check that no Flash memory operation is ongoing by checking the BSY bit in the Flash status register (FLASH_SR) (BSY is active when erase/program operation is on going in bank 1 or bank 2). Set MER1 or MER2 to in the Flash control register (FLASH_CR).

-

Page 92: Flash Option Bytes

Embedded Flash memory (FLASH) RM0351 FLASH option bytes 3.4.1 Option bytes description The option bytes are configured by the end user depending on the application requirements. As a configuration example, the watchdog may be selected in hardware or software mode (refer to Section 3.4.2: Option bytes programming). - Page 93 WRP2B WRP2B 1FFFF820 Unused Unused Unused Unused _END _STRT _END _STRT User and read protection option bytes Flash memory address: 0x1FFF 7800 ST production value: 0xFFEF F8AA SRAM2 SRAM2 DUAL WWDG IWGD_ IWDG_ IWDG_ Res. Res. Res. Res. Res. Res.

- Page 94 0xAA: Level 0, read protection not active 0xCC: Level 2, chip read protection active Others: Level 1, memories read protection active Bank 1 PCROP Start address option bytes Flash memory address: 0x1FFF 7808 ST production value: 0xFFFF FFFF Res. Res. Res. Res.

- Page 95 Bits 15:0 PCROP1_STRT: Bank 1 PCROP area start offset PCROP1_STRT contains the first double-word of the bank 1 PCROP area. Bank 1 PCROP End address option bytes Flash memory address: 0x1FFF 7810 ST production value: 0x0000 0000 PCROP Res. Res.

- Page 96 Embedded Flash memory (FLASH) RM0351 Bank 1 WRP Area B address option bytes Flash memory address: 0x1FFF 7820 ST production value: 0x0000 00FF Res. Res. Res. Res. Res. Res. Res. Res. WRP1B_END[15:0] Res. Res. Res. Res. Res. Res. Res. Res.

-

Page 97: Option Bytes Programming

Bits 15:0 PCROP2_END: Bank 2 PCROP area end offset PCROP2_END contains the last double-word of the bank 2 PCROP area. Bank 2 WRP Area A address option bytes Flash memory address: 0x1FFF F818 ST production value: 0x0000 00FF Res. Res. Res. - Page 98 Embedded Flash memory (FLASH) RM0351 unlock this register: Unlock the FLASH_CR with the LOCK clearing sequence (refer to Unlocking the Flash memory). Write OPTKEY1 = 0x08192A3B in the Flash option key register (FLASH_OPTKEYR). Write OPTKEY2 = 0x4C5D6E7F in the FLASH_OPTKEYR register. The user options can be protected against unwanted erase/program operations by setting the OPTLOCK bit by software.

- Page 99 RM0351 Embedded Flash memory (FLASH) During option byte loading, the options are read by double word with ECC. If the word and its complement are matching, the option word/byte is copied into the option register. If the comparison between the word and its complement fails, a status bit OPTVERR is set. Mismatch values are forced into the option registers: –...

-

Page 100: Flash Memory Protection

Embedded Flash memory (FLASH) RM0351 FLASH memory protection The Flash main memory can be protected against external accesses with the Read protection (RDP). The pages of the Flash memory can also be protected against unwanted write due to loss of program counter contexts. The write-protection (WRP) granularity is one page (2 KBytes). - Page 101 RM0351 Embedded Flash memory (FLASH) Level 1: Read protection This is the default protection level when RDP option byte is erased. It is defined as well when RDP value is at any value different from 0xAA and 0xCC, or even if the complement is not correct.

-

Page 102: Table 12. Access Status Versus Protection Level And Execution Modes

Embedded Flash memory (FLASH) RM0351 Figure 4. Changing the Read protection (RDP) level Table 12. Access status versus protection level and execution modes Debug/ BootFromRam/ User execution (BootFromFlash) Protection BootFromLoader Area level Read Write Erase Read Write Erase Flash main memory System memory... -

Page 103: Proprietary Code Readout Protection (Pcrop)

RM0351 Embedded Flash memory (FLASH) 3.5.2 Proprietary code readout protection (PCROP) Apart of the flash memory can be protected against read and write from third parties. The protected area is execute-only: it can only be reached by the STM32 CPU, as an instruction code, while all other accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited. -

Page 104: Write Protection (Wrp)

Embedded Flash memory (FLASH) RM0351 Changing the Read protection level). In this case, PCROP1/2_STRT and PCROP1/2_END are also not erased. Note: It is recommended to align PCROP area with page granularity when using PCROP_RDP, or to leave free the rest of the page where PCROP zone starts or ends. 3.5.3 Write protection (WRP) The user area in Flash memory can be protected against unwanted write operations. -

Page 105: Flash Interrupts

RM0351 Embedded Flash memory (FLASH) FLASH interrupts Table 13. Flash interrupt request Event flag/interrupt Interrupt enable control Interrupt event Event flag clearing method End of operation Write EOP=1 EOPIE Operation error OPERR Write OPERR=1 ERRIE Read error RDERR Write RDERR=1 RDERRIE ECC correction ECCC... -

Page 106: Flash Registers

Embedded Flash memory (FLASH) RM0351 FLASH registers 3.7.1 Flash access control register (FLASH_ACR) Address offset: 0x00 Reset value: 0x0000 0600 Access: no wait state, word, half-word and byte access Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 107: Flash Power-Down Key Register (Flash_Pdkeyr)

RM0351 Embedded Flash memory (FLASH) Bit 9 ICEN: Instruction cache enable 0: Instruction cache is disabled 1: Instruction cache is enabled Bit 8 PRFTEN: Prefetch enable 0: Prefetch disabled 1: Prefetch enabled Bits 7:3 Reserved, must be kept at reset value. Bits 2:0 LATENCY[2:0]: Latency These bits represent the ratio of the SYSCLK (system clock) period to the Flash access time. -

Page 108: Flash Option Key Register (Flash_Optkeyr)

Embedded Flash memory (FLASH) RM0351 KEYR[31:16] KEYR[15:0] Bits 31:0 KEYR: Flash key The following values must be written consecutively to unlock the FLACH_CR register allowing flash programming/erasing operations: KEY1: 0x45670123 KEY2: 0xCDEF89AB 3.7.4 Flash option key register (FLASH_OPTKEYR) Address offset: 0x0C Reset value: 0x0000 0000 Access: no wait state, word access OPTKEYR[31:16]... - Page 109 RM0351 Embedded Flash memory (FLASH) Bits 31:17 Reserved, must be kept at reset value. Bit 16 BSY: Busy This indicates that a Flash operation is in progress. This is set on the beginning of a Flash operation and reset when the operation finishes or when an error occurs.

-

Page 110: Flash Control Register (Flash_Cr)

Embedded Flash memory (FLASH) RM0351 Bit 3 PROGERR: Programming error Set by hardware when a double-word address to be programmed contains a value different from '0xFFFF FFFF' before programming, except if the data to write is '0x0000 0000'. Cleared by writing 1. Bit 2 Reserved, must be kept at reset value. - Page 111 RM0351 Embedded Flash memory (FLASH) Bit 27 OBL_LAUNCH: Force the option byte loading When set to 1, this bit forces the option byte reloading. This bit is cleared only when the option byte loading is complete. It cannot be written if OPTLOCK is set. 0: Option byte loading complete 1: Option byte loading requested Bit 26 RDERRIE: PCROP read error interrupt enable...

-

Page 112: Flash Ecc Register (Flash_Eccr)

Embedded Flash memory (FLASH) RM0351 Bits 10:3 PNB[7:0]: Page number selection These bits select the page to erase: If BKER = 0: 00000000: page 0 00000001: page 1 11111111: page 255 If BKER=1 00000000: page 256 00000001: page 257 11111111: page 511 Bit 2 MER1: Bank 1 Mass erase This bit triggers the bank 1 mass erase (all bank 1 user pages) when set. -

Page 113: Flash Option Register (Flash_Optr)

RM0351 Embedded Flash memory (FLASH) Bit 24 ECCIE: ECC correction interrupt enable 0: ECCC interrupt disabled 1: ECCC interrupt enabled Bits 23:21 Reserved, must be kept at reset value. Bit 20 SYSF_ECC: System Flash ECC fail This bit indicates that the ECC error correction or double ECC error detection is located in the System Flash. -

Page 114: Flash Bank 1 Pcrop Start Address Register (Flash_Pcrop1Sr)

Embedded Flash memory (FLASH) RM0351 Bit 21 DUALBANK: Dual-Bank on 512 KB or 256 KB Flash memory devices 0: 256 KB/512 KB Single-bank Flash: Contiguous addresses in Bank 1 1: 256 KB/512 KB Dual-bank Flash: Refer to Table 6 Table Bit 20 BFB2: Dual-bank boot 0: Dual-bank boot disable 1: Dual-bank boot enable... -

Page 115: Flash Bank 1 Pcrop End Address Register (Flash_Pcrop1Er)

RM0351 Embedded Flash memory (FLASH) Access: no wait state when no Flash memory operation is on going, word, half-word access Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. PCROP1_STRT[15:0] Bits 31:16 Reserved, must be kept cleared Bits 15:0 PCROP1_STRT: Bank 1 PCROP area start offset PCROP1_STRT contains the first double-word of the PCROP area. -

Page 116: Flash Bank 1 Wrp Area B Address Register (Flash_Wrp1Br)

Embedded Flash memory (FLASH) RM0351 Res. Res. Res. Res. Res. Res. Res. Res. WRP1A_END[7:0] Res. Res. Res. Res. Res. Res. Res. Res. WRP1A_STRT[7:0] Bits 31:24 Reserved, must be kept cleared Bits 23:16 WRP1A_END: Bank 1 WRP first area “A” end offset WRP1A_END contains the last page of the Bank 1 WRP first area. -

Page 117: Flash Bank 2 Pcrop End Address Register (Flash_Pcrop2Er)

RM0351 Embedded Flash memory (FLASH) PCROP2_STRT[15:0] Bits 31:16 Reserved, must be kept cleared Bits 15:0 PCROP2_STRT: Bank 2 PCROP area start offset PCROP2_STRT contains the first double-word of the Bank 2 PCROP area. 3.7.14 Flash Bank 2 PCROP End address register (FLASH_PCROP2ER) Address offset: 0x48 Reset value: 0x0000 XXXX Access: no wait state when no Flash memory operation is on going, word, half-word access... -

Page 118: Flash Bank 2 Wrp Area B Address Register (Flash_Wrp2Br)

Embedded Flash memory (FLASH) RM0351 3.7.16 Flash Bank 2 WRP area B address register (FLASH_WRP2BR) Address offset: 0x50 Reset value: 0x00XX 00XX Access: no wait state when no Flash memory operation is on going, word, half-word and byte access Res. Res. -

Page 119: Flash Register Map

RM0351 Embedded Flash memory (FLASH) 3.7.17 FLASH register map Table 14. Flash interface - register map and reset values Offset Register LATENCY FLASH_ACR [2:0] 0x00 Reset value FLASH_ PDKEYR[31:0] PDKEYR 0x04 Reset value FLASH_KEYR KEYR[31:0] 0x08 Reset value FLASH_OPT OPTKEYR[31:0] KEYR 0x0C Reset value... - Page 120 Embedded Flash memory (FLASH) RM0351 Table 14. Flash interface - register map and reset values (continued) Offset Register FLASH_ WRP1A_END[7:0] WRP1A_STRT[7:0] WRP1AR 0x2C Reset value X X X X X X X X X X X X X X X X FLASH_ WRP1B_END[7:0] WRP1B_STRT[7:0]...

-

Page 121: Firewall (Fw)

RM0351 Firewall (FW) Firewall (FW) Introduction The Firewall is made to protect a specific part of code or data into the Non-Volatile Memory, and/or to protect the Volatile data into the SRAM 1 from the rest of the code executed outside the protected area. -

Page 122: Firewall Functional Description

The Firewall peripheral is snooping the AMBA buses on which the memories (volatile and non-volatile) are connected. A global architecture view is illustrated in Figure Figure 5. STM32L4x6 firewall connection schematics 4.3.2 Functional requirements There are several requirements to guaranty the highest security level by the application code/data which needs to be protected by the Firewall and to avoid unwanted Firewall alarm (reset generation). -

Page 123: Firewall Segments

RM0351 Firewall (FW) end code needs to embed an IAP located in a write protected segment in order to allow future code updates when the production parts will be Level 2 ROP. Write protection In order to offer a maximum security level, the following points need to be respected: •... -

Page 124: Segment Accesses And Properties

Firewall (FW) RM0351 Volatile data segment Volatile data used by the protected code located into the code segment must be defined into the SRAM 1 memory. The access to this segment is defined into the Section 4.3.4: Segment accesses and properties. -

Page 125: Firewall Initialization

RM0351 Firewall (FW) The Volatile data segment is a bit different from the two others. The segment can be: • Shared (VDS bit in the register) It means that the area and the data located into this segment can be shared between the protected code and the user code executed in a non-protected area. -

Page 126: Firewall States

Firewall (FW) RM0351 Below is the initialization procedure to follow: Configure the RCC to enable the clock to the Firewall module Configure the RCC to enable the clock of the system configuration registers Set the base address and length of each segment (CSSA, CSL, NVDSSA, NVDSL, VDSSA, VDSL registers) Set the configuration register of the Firewall (FW_CR register) Enable the Firewall clearing the FWDIS bit in the system configuration register. - Page 127 RM0351 Firewall (FW) Opening the Firewall As soon as the Firewall is enabled, it is closed. It means that most of the accesses to the protected segments are forbidden (refer to Section 4.3.4: Segment accesses and properties). In order to open the Firewall to interact with the protected segments, it is mandatory to apply the “call gate”...

-

Page 128: Firewall Registers

Firewall (FW) RM0351 Firewall registers 4.4.1 Code segment start address (FW_CSSA) Address offset: 0x00 Reset value: 0x0000 0000 Res. Res. Res. Res. Res. Res. Res. Res. ADD[23:16] ADD[15:8] Bits 31:24 Reserved, must be kept at reset value. Bits 23:8 ADD[23:8]: code segment start address The LSB bits of the start address (bit 7:0) are reserved and forced to 0 in order to allow a 256-byte granularity. -

Page 129: Non-Volatile Data Segment Start Address (Fw_Nvdssa)

RM0351 Firewall (FW) 4.4.3 Non-volatile data segment start address (FW_NVDSSA) Address offset: 0x08 Reset value: 0x0000 0000 Res. Res. Res. Res. Res. Res. Res. Res. ADD[23:16] ADD[15:8] Bits 31:24 Reserved, must be kept at the reset value. Bits 23:8 ADD[23:8]: Non-volatile data segment start address The LSB bits of the start address (bit 7:0) are reserved and forced to 0 in order to allow a 256-byte granularity. -

Page 130: Volatile Data Segment Start Address (Fw_Vdssa)

Firewall (FW) RM0351 4.4.5 Volatile data segment start address (FW_VDSSA) Address offset: 0x10 Reset value: 0x0000 0000 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. [16] ADD[15:6] Bits 31:17 Reserved, must be kept at the reset value. Bits 16:6 ADD[16:6]: Volatile data segment start address The LSB bits of the start address (bit 5:0) are reserved and forced to 0 in order to allow a 64-byte granularity. -

Page 131: Configuration Register (Fw_Cr)

RM0351 Firewall (FW) 4.4.7 Configuration register (FW_CR) Address offset: 0x20 Reset value: 0x0000 0000 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 132: Firewall Register Map

Firewall (FW) RM0351 4.4.8 Firewall register map The table below provides the Firewall register map and reset values. Table 17. Firewall register map and reset values Offset Register FW_CSSA Reset Value FW_CSL LENG Reset Value FW_NVDSSA Reset Value FW_NVDSL LENG Reset Value FW_VDSSA 0x10... -

Page 133: Power Control (Pwr)

RM0351 Power control (PWR) Power control (PWR) Power supplies The STM32L4x devices require a 1.71 V to 3.6 V V operating voltage supply. Several independent supplies (V ), can be provided for specific DDIO2 DDUSB peripherals: • = 1.71 V to 3.6 V is the external power supply for the I/Os, the internal regulator and the system analog such as reset, power management and internal clocks. -

Page 134: Independent Analog Peripherals Supply

Power control (PWR) RM0351 When the VREF+ is double-bonded with VDDA in a package, the internal voltage reference buffer is not available and must be kept disable (refer to datasheet for packages pinout description). must always be equal to V REF- An embedded linear voltage regulator is used to supply the internal digital power V CORE... -

Page 135: Independent I/O Supply Rail

RM0351 Power control (PWR) The V supply can be monitored by the Peripheral Voltage Monitoring, and compared with two thresholds (1.65 V for PVM3 or 2.2 V for PVM4), refer to Section 5.2.3: Peripheral Voltage Monitoring (PVM) for more details. When a single supply is used, V can be externally connected to V through the... -

Page 136: Independent Lcd Supply

Power control (PWR) RM0351 5.1.4 Independent LCD supply The VLCD pin is provided to control the contrast of the glass LCD. This pin can be used in two ways: • It can receive from an external circuitry the desired maximum voltage that is provided on segment and common lines to the glass LCD by the microcontroller. -

Page 137: Voltage Regulator

RM0351 Power control (PWR) Note: Due to the fact that the analog switch can transfer only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is restricted: the speed has to be limited to 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. -

Page 138: Dynamic Voltage Scaling Management

Power control (PWR) RM0351 contents of the registers and internal SRAM1 and SRAM2. • In Stop 1 and Stop 2 modes, the main regulator is off and the low-power regulator (LPR) supplies low power to the V domain, preserving the contents of the CORE registers and of internal SRAM1 and SRAM2. -

Page 139: Power Supply Supervisor

RM0351 Power control (PWR) Power supply supervisor 5.2.1 Power-on reset (POR) / power-down reset (PDR) / brown-out reset (BOR) The device has an integrated power-on reset (POR) / power-down reset (PDR), coupled with a brown-out reset (BOR) circuitry. The BOR is active in all power modes except Shutdown mode, and cannot be disabled. -

Page 140: Peripheral Voltage Monitoring (Pvm)

Power control (PWR) RM0351 Figure 9. PVD thresholds 5.2.3 Peripheral Voltage Monitoring (PVM) Only V is monitored by default, as it is the only supply required for all system-related functions. The other supplies (V and V ) can be independent from V DDIO2 DDUSB and can be monitored with four Peripheral Voltage Monitoring (PVM). -

Page 141: Low-Power Modes

RM0351 Power control (PWR) can be enabled to confirm whether the supply is present or not. The following sequence must be done before using the USB_OTG peripheral: If V is independent from V DDUSB Enable the PVM1 by setting PVME1 bit in the Power control register 2 (PWR_CR2). - Page 142 Power control (PWR) RM0351 regulator is in low-power mode to minimize the regulator's operating current. Refer to Section 5.3.2: Low-power run mode (LP run). ® • Low-power sleep mode: This mode is entered from the Low-power run mode: Cortex M4 is off. Refer to Section 5.3.5: Low-power sleep mode (LP sleep).

-

Page 143: Figure 10. Low-Power Modes Possible Transitions

RM0351 Power control (PWR) Figure 10. Low-power modes possible transitions DocID024597 Rev 3 143/1693... -

Page 144: Table 19. Low-Power Mode Summary

Power control (PWR) RM0351 Table 19. Low-power mode summary Voltage Wakeup Wakeup regulators Mode name Entry Effect on clocks source system clock WFI or Return Sleep CPU clock OFF Same as before Any interrupt from ISR entering Sleep (Sleep-now or no effect on other clocks mode Sleep-on-exit) -

Page 145: Table 20. Functionalities Depending On The Working Mode

RM0351 Power control (PWR) Table 20. Functionalities depending on the working mode Stop 0/1 Stop 2 Standby Shutdown Low- Low- Peripheral Sleep power power VBAT sleep Flash memory (up to 1 MB) SRAM1 (up to 96 KB) SRAM2 (32 KB) FSMC QUADSPI Backup Registers... - Page 146 Power control (PWR) RM0351 Table 20. Functionalities depending on the working mode (continued) Stop 0/1 Stop 2 Standby Shutdown Low- Low- Peripheral Sleep power power VBAT sleep I2Cx (x=1,2) I2C3 SPIx (x=1,2,3) SDMMC1 SWPMI SAIx (x=1,2) DFSDM ADCx (x=1,2,3) DACx (x=1,2) VREFBUF OPAMPx (x=1,2) COMPx (x=1,2)

-

Page 147: Run Mode

RM0351 Power control (PWR) Table 20. Functionalities depending on the working mode (continued) Stop 0/1 Stop 2 Standby Shutdown Low- Low- Peripheral Sleep power power VBAT sleep CRC calculation unit (11) GPIOs pins (10) (10) 1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available. 2. -

Page 148: Low-Power Run Mode (Lp Run)

Power control (PWR) RM0351 Peripheral clock gating In Run mode, the HCLK and PCLK for individual peripherals and memories can be stopped at any time to reduce the power consumption. To further reduce the power consumption in Sleep mode, the peripheral clocks can be disabled prior to executing the WFI or WFE instructions. -

Page 149: Low Power Modes

RM0351 Power control (PWR) Table 21. Low-power run Low-power run mode Description LPR = 0 Mode exit Wait until REGLPF = 0 Increase the system clock frequency Wakeup latency Regulator wakeup time from low-power mode 5.3.3 Low power modes Entering low power mode Low power modes are entered by the MCU by executing the WFI (Wait For Interrupt), or ®... -

Page 150: Sleep Mode

-M4 System Control register. If WFI or return from ISR was used for entry Interrupt: refer to Table 42: STM32L4x6 vector table If WFE was used for entry and SEVONPEND = 0: Wakeup event: refer to Section 12.3.2: Wakeup event management... -

Page 151: Stop 0 Mode

-M4 System Control register. If WFI or Return from ISR was used for entry Interrupt: refer to Table 42: STM32L4x6 vector table If WFE was used for entry and SEVONPEND = 0: Wakeup event: refer to Section 12.3.2: Wakeup event management... - Page 152 Power control (PWR) RM0351 HSE oscillators are disabled. Some peripherals with the wakeup capability (I2Cx (x=1,2,3), U(S)ARTx(x=1,2...5) and LPUART) can switch on the HSI16 to receive a frame, and switch off the HSI16 after receiving the frame if it is not a wakeup frame. In this case, the HSI16 clock is propagated only to the peripheral requesting it.

-

Page 153: Stop 1 Mode

Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 42: STM32L4x6 vector table. If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in event mode. -

Page 154: Stop 2 Mode

Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 42: STM32L4x6 vector table. If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in event mode. - Page 155 RM0351 Power control (PWR) I/O states in Stop 2 mode In the Stop 2 mode, all I/O pins keep the same state as in the Run mode. Entering Stop 2 mode The Stop 2 mode is entered according Section : Entering low power mode, when the ®...

-

Page 156: Table 26. Stop 2 Mode

Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 42: STM32L4x6 vector table. If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in event mode. -

Page 157: Standby Mode

RM0351 Power control (PWR) 5.3.9 Standby mode The Standby mode allows to achieve the lowest power consumption with BOR. It is based ® on the Cortex -M4 deepsleep mode, with the voltage regulators disabled (except when SRAM2 content is preserved). The PLL, the HSI16, the MSI and the HSE oscillators are also switched off. -

Page 158: Table 27. Standby Mode

Power control (PWR) RM0351 Table 27. Standby mode Standby mode Description WFI (Wait for Interrupt) or WFE (Wait for Event) while: ® – SLEEPDEEP bit is set in Cortex -M4 System Control register – No interrupt (for WFI) or event (for WFE) is pending –... -

Page 159: Shutdown Mode

RM0351 Power control (PWR) 5.3.10 Shutdown mode The Shutdown mode allows to achieve the lowest power consumption. It is based on the deepsleep mode, with the voltage regulator disabled. The V domain is consequently CORE powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off. -

Page 160: Auto-Wakeup From Low-Power Mode

Power control (PWR) RM0351 Table 28. Shutdown mode Shutdown mode Description WFI (Wait for Interrupt) or WFE (Wait for Event) while: ® – SLEEPDEEP bit is set in Cortex -M4 System Control register – No interrupt (for WFI) or event (for WFE) is pending –... -

Page 161: Pwr Registers

RM0351 Power control (PWR) PWR registers The peripheral registers can be accessed by half-words (16-bit) or words (32-bit). 5.4.1 Power control register 1 (PWR_CR1) Address offset: 0x00 Reset value: 0x0000 0200. This register is reset after wakeup from Standby mode. Res. -

Page 162: Power Control Register 2 (Pwr_Cr2)

Power control (PWR) RM0351 5.4.2 Power control register 2 (PWR_CR2) Address offset: 0x04 Reset value: 0x0000 0000. This register is reset when exiting the Standby mode. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 163: Power Control Register 3 (Pwr_Cr3)

RM0351 Power control (PWR) Bit 4 PVME1: Peripheral voltage monitoring 1 enable: vs. 1.2V DDUSB 0: PVM1 ( monitoring vs. 1.2V threshold) disable. DDUSB 1: PVM1 ( monitoring vs. 1.2V threshold) enable. DDUSB Bits 3:1 PLS[2:0]: Power voltage detector level selection. These bits select the voltage threshold detected by the power voltage detector: 000: V around 2.0 V... -

Page 164: Power Control Register 4 (Pwr_Cr4)

Power control (PWR) RM0351 Bit 10 APC: Apply pull-up and pull-down configuration When this bit is set, the I/O pull-up and pull-down configurations defined in the PWR_PUCRx and PWR_PDCRx registers are applied. When this bit is cleared, the PWR_PUCRx and PWR_PDCRx registers are not applied to the I/Os. -

Page 165: Power Status Register 1 (Pwr_Sr1)

RM0351 Power control (PWR) Bits 31:10 Reserved, must be kept at reset value. Bit 9 VBRS: V battery charging resistor selection 0: Charge V through a 5 kOhms resistor 1: Charge V through a 1.5 kOhms resistor Bit 8 VBE: V battery charging enable 0: V battery charging disable... -

Page 166: Power Status Register 2 (Pwr_Sr2)

Power control (PWR) RM0351 Bits 31:16 Reserved, must be kept at reset value. Bit 15 WUFI: Wakeup flag internal This bit is set when a wakeup is detected on the internal wakeup line. It is cleared when all internal wakeup sources are cleared. Bits 14:9 Reserved, must be kept at reset value. - Page 167 RM0351 Power control (PWR) Bits 31:16 Reserved, must be kept at reset value. Bit 15 PVMO4: Peripheral voltage monitoring output: V vs. 2.2 V 0: V voltage is above PVM4 threshold (around 2.2 V). 1: V voltage is below PVM4 threshold (around 2.2 V). Note: PVMO4 is cleared when PVM4 is disabled (PVME4 = 0).

-

Page 168: Power Status Clear Register (Pwr_Scr)

Power control (PWR) RM0351 5.4.7 Power status clear register (PWR_SCR) Address offset: 0x18 Reset value: 0x0000 0000. Access: 3 additional APB cycles are needed to write this register vs. a standard APB write. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 169: Power Port A Pull-Down Control Register (Pwr_Pdcra)

RM0351 Power control (PWR) Bits 31:16 Reserved, must be kept at reset value. Bit 15 PU15: Port A pull-up bit 15 When set, this bit activates the pull-up on PA[15] when APC bit is set in PWR_CR3 register. The pull-up is not activated if the corresponding PD15 bit is also set. Bit 14 Reserved, must be kept at reset value. -

Page 170: Power Port B Pull-Down Control Register (Pwr_Pdcrb)

Power control (PWR) RM0351 PU15 PU14 PU13 PU12 PU11 PU10 Bits 31:16 Reserved, must be kept at reset value. Bits 15:0 PUy: Port B pull-up bit y (y=0..15) When set, this bit activates the pull-up on PB[y] when APC bit is set in PWR_CR3 register. The pull-up is not activated if the corresponding PDy bit is also set. -

Page 171: Power Port C Pull-Down Control Register (Pwr_Pdcrc)

RM0351 Power control (PWR) PU15 PU14 PU13 PU12 PU11 PU10 Bits 31:16 Reserved, must be kept at reset value. Bits 15:0 PUy: Port C pull-up bit y (y=0..15) When set, this bit activates the pull-up on PC[y] when APC bit is set in PWR_CR3 register. The pull-up is not activated if the corresponding PDy bit is also set. -

Page 172: Power Port D Pull-Down Control Register (Pwr_Pdcrd)

Power control (PWR) RM0351 Bits 31:16 Reserved, must be kept at reset value. Bits 15:0 PUy: Port D pull-up bit y (y=0..15) When set, this bit activates the pull-up on PD[y] when APC bit is set in PWR_CR3 register. The pull-up is not activated if the corresponding PDy bit is also set. 5.4.15 Power Port D pull-down control register (PWR_PDCRD) Address offset: 0x3C. -

Page 173: Power Port E Pull-Down Control Register (Pwr_Pdcre)

RM0351 Power control (PWR) 5.4.17 Power Port E pull-down control register (PWR_PDCRE) Address offset: 0x44. Reset value: 0x0000 0000. This register is not reset when exiting Standby modes and with PWRRST bit in the RCC_APB1RSTR1 register. Access: Additional APB cycles are needed to access this register vs. a standard APB access (3 for a write and 2 for a read). -

Page 174: Power Port G Pull-Up Control Register (Pwr_Pucrg)

Power control (PWR) RM0351 Access: Additional APB cycles are needed to access this register vs. a standard APB access (3 for a write and 2 for a read). Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 175: Power Port H Pull-Up Control Register (Pwr_Pucrh)

RM0351 Power control (PWR) Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. PD15 PD14 PD13 PD12 PD11 PD10 Bits 31:16 Reserved, must be kept at reset value. Bits 15:0 PDy: Port G pull-down bit y (y=0..15) When set, this bit activates the pull-down on PG[y] when APC bit is set in PWR_CR3 register. - Page 176 Power control (PWR) RM0351 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Bits 31:2 Reserved, must be kept at reset value. Bits 1:0 PDy: Port H pull-down bit y (y=0..1) When set, this bit activates the pull-down on PH[y] when APC bit is set in PWR_CR3 register. 176/1693 DocID024597 Rev 3...

-

Page 177: Pwr Register Map And Reset Value Table

RM0351 Power control (PWR) 5.4.24 PWR register map and reset value table Table 29. PWR register map and reset values Offset Register LPMS PWR_CR1 [1:0] [2:0] 0x000 Reset value PWR_CR2 PLS [2:0] 0x004 Reset value PWR_CR3 0x008 Reset value PWR_CR4 0x00C Reset value PWR_SR1... - Page 178 Power control (PWR) RM0351 Table 29. PWR register map and reset values (continued) Offset Register PWR_PDCRE 0x044 Reset value PWR_PUCRF 0x048 Reset value PWR_PDCRF 0x04C Reset value PWR_PUCRG 0x050 Reset value PWR_PDCRG 0x054 Reset value PWR_PUCRH 0x058 Reset value PWR_PDCRH 0x05C Reset value Refer...

-

Page 179: Reset And Clock Control (Rcc)

RM0351 Reset and clock control (RCC) Reset and clock control (RCC) Reset There are three types of reset, defined as system reset, power reset and backup domain reset. 6.1.1 Power reset A power reset is generated when one of the following events occurs: a Brown-out reset (BOR). -

Page 180: Backup Domain Reset

Reset and clock control (RCC) RM0351 Figure 11. Simplified diagram of the reset circuit Software reset ® The SYSRESETREQ bit in Cortex -M4 Application Interrupt and Reset Control Register must be set to force a software reset on the device (refer to the STM32F3xx/F4xx/L4xx ®... -

Page 181: Clocks

RM0351 Reset and clock control (RCC) Software reset, triggered by setting the BDRST bit in the Backup domain control register (RCC_BDCR). or V power on, if both supplies have previously been powered off. A backup domain reset only affects the LSE oscillator, the RTC, the Backup registers and the RCC Backup domain control register. - Page 182 Reset and clock control (RCC) RM0351 All the peripheral clocks are derived from their bus clock (HCLK, PCLK1 or PCLK2) except: • The 48 MHz clock, used for USB OTG FS, SDMMC and RNG. This clock is derived (selected by software) from one of the three following sources: –...

- Page 183 RM0351 Reset and clock control (RCC) – APB1 clock (PCLK1) – External clock mapped on LPTIMx_IN1 The functionality in Stop mode (including wakeup) is supported only when the clock is LSI or LSE, or in external clock mode. • The RTC and LCD clock which is derived (selected by software) from one of the three following sources: –...

-

Page 184: Figure 12. Clock Tree

Reset and clock control (RCC) RM0351 Figure 12. Clock tree 1. For full details about the internal and external clock source characteristics, please refer to the “Electrical 184/1693 DocID024597 Rev 3... -

Page 185: Hse Clock

RM0351 Reset and clock control (RCC) characteristics” section in your device datasheet. 2. The ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4). When the programmable factor is ‘1’, the AHB prescaler must be equal to ‘1’. 6.2.1 HSE clock The high speed external clock signal (HSE) can be generated from two possible clock... -

Page 186: Hsi16 Clock

Calibration RC oscillator frequencies can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at T =25°C. After reset, the factory calibration value is loaded in the HSICAL[7:0] bits in the... -

Page 187: Msi Clock

The MSI RC oscillator frequency can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at an ambient temperature, TA, of 25 °C. After reset, the factory calibration value is loaded in the... -

Page 188: Lse Clock

Reset and clock control (RCC) RM0351 6.2.4 The device embeds 3 PLLs: PLL, PLLSAI1, PLLSAI2. Each PLL provides up to three independent outputs. The internal PLLs can be used to multiply the HSI16, HSE or MSI output clock frequency. The PLLs input frequency must be between 4 and 16 MHz. The selected clock source is divided by a programmable factor PLLM from 1 to 8 to provide a clock frequency in the requested input range. -

Page 189: Lsi Clock

RM0351 Reset and clock control (RCC) capability (LSEDRV=00) when the LSE is ON. However, once LSEDRV is selected, the drive capability can not be increased if LSEON=1. The LSERDY flag in the Backup domain control register (RCC_BDCR) indicates whether the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware. -

Page 190: Table 30. Clock Source Frequency

Reset and clock control (RCC) RM0351 Table 30. Clock source frequency Clock frequency Product voltage range HSI16 PLL/PLLSAI1/PLLSAI2 80 MHz Range 1 48 MHz 16 MHz 48 MHz (VCO max = 344 MHz) 26 MHz Range 2 24 MHz range 16 MHz 26 MHz (VCO max = 128 MHz) -

Page 191: Adc Clock

RM0351 Reset and clock control (RCC) 6.2.11 ADC clock The ADC clock is derived from the system clock, or from the PLLSAI1 or the PLLSAI2 output. It can reach 80 MHz and can be divided by the following prescalers values: 1,2,4,6,8,10,12,16,32,64,128 or 256 by configuring the ADC123_CCR register. -

Page 192: Figure 14. Frequency Measurement With Tim15 In Capture Mode

Reset and clock control (RCC) RM0351 6.2.15 Clock-out capability • The microcontroller clock output (MCO) capability allows the clock to be output onto the external MCO pin. One of seven clock signals can be selected as the MCO clock. – –... -

Page 193: Figure 15. Frequency Measurement With Tim16 In Capture Mode

RM0351 Reset and clock control (RCC) The input capture channel of the Timer 15 can be a GPIO line or an internal clock of the MCU. This selection is performed through the TI1_RMP bit in the TIM15_OR register. The possibilities are the following ones: •... - Page 194 Reset and clock control (RCC) RM0351 The input capture channel of the Timer 17 can be a GPIO line or an internal clock of the MCU. This selection is performed through the TI1_RMP[1:0] bits in the TIM17_OR register. The possibilities are the following ones: •...

-

Page 195: Low-Power Modes

RM0351 Reset and clock control (RCC) 6.2.17 Peripheral clock enable register (RCC_AHBxENR, RCC_APBxENRy) Each peripheral clock can be enabled by the xxxxEN bit of the RCC_AHBxENR, RCC_APBxENRy registers. When the peripheral clock is not active, the peripheral registers read or write accesses are not supported. -

Page 196: Clock Control Register (Rcc_Cr)

Reset and clock control (RCC) RM0351 RCC registers 6.4.1 Clock control register (RCC_CR) Address offset: 0x00 Reset value: 0x0000 0063. HSEBYP is not affected by reset. Access: no wait state, word, half-word and byte access Res. Res. SAI2 SAI2 SAI1 SAI1 PLLON Res. - Page 197 RM0351 Reset and clock control (RCC) Bits 23:20 Reserved, must be kept at reset value. Bit 19 CSSON: Clock security system enable Set by software to enable the clock security system. When CSSON is set, the clock detector is enabled by hardware when the HSE oscillator is ready, and disabled by hardware if a HSE clock failure is detected.

- Page 198 Reset and clock control (RCC) RM0351 Bit 8 HSION: HSI clock enable Set and cleared by software. Cleared by hardware to stop the HSI16 oscillator when entering Stop, Standby or Shutdown mode. Set by hardware to force the HSI16 oscillator ON when STOPWUCK=1 or HSIASFS = 1 when leaving Stop modes, or in case of failure of the HSE crystal oscillator.

-

Page 199: Internal Clock Sources Calibration Register (Rcc_Icscr)

RM0351 Reset and clock control (RCC) Bit 0 MSION: MSI clock enable This bit is set and cleared by software. Cleared by hardware to stop the MSI oscillator when entering Stop, Standby or Shutdown mode. Set by hardware to force the MSI oscillator ON when exiting Standby or Shutdown mode. Set by hardware to force the MSI oscillator ON when STOPWUCK=0 when exiting from Stop modes, or in case of a failure of the HSE oscillator Set by hardware when used directly or indirectly as system clock. -

Page 200: Clock Configuration Register (Rcc_Cfgr)

Reset and clock control (RCC) RM0351 6.4.3 Clock configuration register (RCC_CFGR) Address offset: 0x08 Reset value: 0x0000 0000 Access: 0 ≤ wait state ≤ 2, word, half-word and byte access 1 or 2 wait states inserted only if the access occurs during clock source switch. From 0 to 15 wait states inserted if the access occurs when the APB or AHB prescalers values update is on going. - Page 201 RM0351 Reset and clock control (RCC) STOPWUCK: Wakeup from Stop and CSS backup clock selection Bit 15 Set and cleared by software to select the system clock used when exiting Stop mode. The selected clock is also used as emergency clock for the Clock Security System on HSE. Warning: STOPWUCK must not be modified when the Clock Security System is enabled by HSECSSON in RCC_CR register and the system clock is HSE (SWS=”10”) or a switch on HSE is requested (SW=”10”).

- Page 202 Reset and clock control (RCC) RM0351 Bits 1:0 SW[1:0]: System clock switch Set and cleared by software to select system clock source (SYSCLK). Configured by HW to force MSI oscillator selection when exiting Standby or Shutdown mode. Configured by HW to force MSI or HSI16 oscillator selection when exiting Stop mode or in case of failure of the HSE oscillator, depending on STOPWUCK value.

-

Page 203: Pll Configuration Register (Rcc_Pllcfgr)

RM0351 Reset and clock control (RCC) 6.4.4 PLL configuration register (RCC_PLLCFGR) Address offset: 0x0C Reset value: 0x0000 1000 Access: no wait state, word, half-word and byte access This register is used to configure the PLL clock outputs according to the formulas: •... - Page 204 Reset and clock control (RCC) RM0351 Bits 22:21 PLLQ[1:0]: Main PLL division factor for PLL48M1CLK (48 MHz clock). Set and cleared by software to control the frequency of the main PLL output clock PLL48M1CLK. This output can be selected for USB, RNG, SDMMC (48 MHz clock). These bits can be written only if PLL is disabled.

- Page 205 RM0351 Reset and clock control (RCC) Bits 14:8 PLLN[6:0]: Main PLL multiplication factor for VCO Set and cleared by software to control the multiplication factor of the VCO. These bits can be written only when the PLL is disabled. VCO output frequency = VCO input frequency x PLLN with 8 =< PLLN =< 86 0000000: PLLN = 0 wrong configuration 0000001: PLLN = 1 wrong configuration 0000111: PLLN = 7 wrong configuration...

-

Page 206: Pllsai1 Configuration Register (Rcc_Pllsai1Cfgr)

Reset and clock control (RCC) RM0351 6.4.5 PLLSAI1 configuration register (RCC_PLLSAI1CFGR) Address offset: 0x10 Reset value: 0x0000 1000 Access: no wait state, word, half-word and byte access This register is used to configure the PLLSAI1 clock outputs according to the formulas: •... - Page 207 RM0351 Reset and clock control (RCC) Bits 22:21 PLLSAI1Q[1:0]: SAI1PLL division factor for PLL48M2CLK (48 MHz clock) Set and cleared by software to control the frequency of the SAI1PLL output clock PLL48M2CLK. This output can be selected for USB, RNG, SDMMC (48 MHz clock). These bits can be written only if SAI1PLL is disabled.

- Page 208 Reset and clock control (RCC) RM0351 Bit 15 Reserved, must be kept at reset value. Bits 14:8 PLLSAI1N[6:0]: SAI1PLL multiplication factor for VCO Set and cleared by software to control the multiplication factor of the VCO. These bits can be written only when the SAI1PLL is disabled.

-

Page 209: Pllsai2 Configuration Register (Rcc_Pllsai2Cfgr)

RM0351 Reset and clock control (RCC) 6.4.6 PLLSAI2 configuration register (RCC_PLLSAI2CFGR) Address offset: 0x14 Reset value: 0x0000 1000 Access: no wait state, word, half-word and byte access This register is used to configure the PLLSAI2 clock outputs according to the formulas: •... - Page 210 Reset and clock control (RCC) RM0351 Bit 16 PLLSAI2PEN: SAI2PLL PLLSAI2CLK output enable Set and reset by software to enable the PLLSAI2CLK output of the SAI2PLL. In order to save power, when the PLLSAI2CLK output of the SAI2PLL is not used, the value of PLLSAI2PEN should be 0.

-

Page 211: Clock Interrupt Enable Register (Rcc_Cier)

RM0351 Reset and clock control (RCC) 6.4.7 Clock interrupt enable register (RCC_CIER) Address offset: 0x18 Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. - Page 212 Reset and clock control (RCC) RM0351 Bit 2 MSIRDYIE: MSI ready interrupt enable Set and cleared by software to enable/disable interrupt caused by the MSI oscillator stabilization. 0: MSI ready interrupt disabled 1: MSI ready interrupt enabled Bit 1 LSERDYIE: LSE ready interrupt enable Set and cleared by software to enable/disable interrupt caused by the LSE oscillator stabilization.

-

Page 213: Clock Interrupt Flag Register (Rcc_Cifr)

RM0351 Reset and clock control (RCC) 6.4.8 Clock interrupt flag register (RCC_CIFR) Address offset: 0x1C Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. - Page 214 Reset and clock control (RCC) RM0351 Bit 3 HSIRDYF: HSI16 ready interrupt flag Set by hardware when the HSI16 clock becomes stable and HSIRDYDIE is set in a response to setting the HSION (refer to Clock control register (RCC_CR)). When HSION is not set but the HSI16 oscillator is enabled by the peripheral through a clock request, this bit is not set and no interrupt is generated.

-

Page 215: Clock Interrupt Clear Register (Rcc_Cicr)

RM0351 Reset and clock control (RCC) 6.4.9 Clock interrupt clear register (RCC_CICR) Address offset: 0x20 Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. -

Page 216: Ahb1 Peripheral Reset Register (Rcc_Ahb1Rstr)

Reset and clock control (RCC) RM0351 Bit 2 MSIRDYC: MSI ready interrupt clear This bit is set by software to clear the MSIRDYF flag. 0: No effect 1: MSIRDYF cleared Bit 1 LSERDYC: LSE ready interrupt clear This bit is set by software to clear the LSERDYF flag. 0: No effect 1: LSERDYF cleared Bit 0 LSIRDYC: LSI ready interrupt clear... -

Page 217: Ahb2 Peripheral Reset Register (Rcc_Ahb2Rstr)

RM0351 Reset and clock control (RCC) Bits 7:2 Reserved, must be kept at reset value. Bit 1 DMA2RST: DMA2 reset Set and cleared by software. 0: No effect 1: Reset DMA2 Bit 0 DMA1RST: DMA1 reset Set and cleared by software. 0: No effect 1: Reset DMA1 6.4.11... -

Page 218: Ahb3 Peripheral Reset Register (Rcc_Ahb3Rstr)

Reset and clock control (RCC) RM0351 Bit 7 GPIOHRST: IO port H reset Set and cleared by software. 0: No effect 1: Reset IO port H Bit 6 GPIOGRST: IO port G reset Set and cleared by software. 0: No effect 1: Reset IO port G Bit 5 GPIOFRST: IO port F reset Set and cleared by software. - Page 219 RM0351 Reset and clock control (RCC) Bits 31:9 Reserved, must be kept at reset value. Bit 8 QSPIRST: Quad SPI memory interface reset Set and cleared by software. 0: No effect 1: Reset QUADSPI Bits 7:1 Reserved, must be kept at reset value. Bit 0 FMCRST: Flexible memory controller reset Set and cleared by software.

-

Page 220: Apb1 Peripheral Reset Register 1 (Rcc_Apb1Rstr1)

Reset and clock control (RCC) RM0351 6.4.13 APB1 peripheral reset register 1 (RCC_APB1RSTR1) Address offset: 0x38 Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access DAC1 CAN1 I2C2 I2C1 UART5 UART4 USART3 USART2 LPTIM1 OPAMP I2C3R Res. - Page 221 RM0351 Reset and clock control (RCC) Bit 21 I2C1RST: I2C1 reset Set and cleared by software. 0: No effect 1: Reset I2C1 Bit 20 UART5RST: UART5 reset Set and cleared by software. 0: No effect 1: Reset UART5 Bit 19 UART4RST: UART4 reset Set and cleared by software.

-

Page 222: Apb1 Peripheral Reset Register 2 (Rcc_Apb1Rstr2)

Reset and clock control (RCC) RM0351 Bit 3 TIM5RST: TIM5 timer reset Set and cleared by software. 0: No effect 1: Reset TIM5 Bit 2 TIM4RST: TIM3 timer reset Set and cleared by software. 0: No effect 1: Reset TIM3 Bit 1 TIM3RST: TIM3 timer reset Set and cleared by software. -

Page 223: Apb2 Peripheral Reset Register (Rcc_Apb2Rstr)

RM0351 Reset and clock control (RCC) 6.4.15 APB2 peripheral reset register (RCC_APB2RSTR) Address offset: 0x40 Reset value: 0x00000 0000 Access: no wait state, word, half-word and byte access DFSDM SAI2 SAI1 TIM17 TIM16 TIM15R Res. Res. Res. Res. Res. Res. Res. -

Page 224: Ahb1 Peripheral Clock Enable Register (Rcc_Ahb1Enr)

Reset and clock control (RCC) RM0351 Bit 14 USART1RST: USART1 reset Set and cleared by software. 0: No effect 1: Reset USART1 Bit 13 TIM8RST: TIM8 timer reset Set and cleared by software. 0: No effect 1: Reset TIM8 timer Bit 12 SPI1RST: SPI1 reset Set and cleared by software. -

Page 225: Ahb2 Peripheral Clock Enable Register (Rcc_Ahb2Enr)

RM0351 Reset and clock control (RCC) Bits 31:17 Reserved, must be kept at reset value. Bit 16 TSCEN: Touch Sensing Controller clock enable Set and cleared by software. 0: TSC clock disable 1: TSC clock enable Bits 15:13 Reserved, must be kept at reset value. Bit 12 CRCEN: CRC clock enable Set and cleared by software. - Page 226 Reset and clock control (RCC) RM0351 Bits 31:19 Reserved, must be kept at reset value. Bit 18 RNGEN: Random Number Generator clock enable Set and cleared by software. 0: Random Number Generator clock disabled 1: Random Number Generator clock enabled Bit 17 Reserved, must be kept at reset value.

-

Page 227: Ahb3 Peripheral Clock Enable Register(Rcc_Ahb3Enr)

RM0351 Reset and clock control (RCC) Bit 2 GPIOCEN: IO port C clock enable Set and cleared by software. 0: IO port C clock disabled 1: IO port C clock enabled Bit 1 GPIOBEN: IO port B clock enable Set and cleared by software. 0: IO port B clock disabled 1: IO port B clock enabled Bit 0 GPIOAEN: IO port A clock enable... - Page 228 Reset and clock control (RCC) RM0351 Note: When the peripheral clock is not active, the peripheral registers read or write access is not supported. LPTIM1 OPAMP DAC1 CAN1 I2C3 I2C2 I2C1 UART5 UART4 USART3 USART2 Res. Res. Res. Res. TIM7 SPI3 SPI2 TIM2...

- Page 229 RM0351 Reset and clock control (RCC) Bit 20 UART5EN: UART5 clock enable Set and cleared by software. 0: UART5 clock disabled 1: UART5 clock enabled Bit 19 UART4EN: UART4 clock enable Set and cleared by software. 0: UART4 clock disabled 1: UART4 clock enabled Bit 18 USART3EN: USART3 clock enable Set and cleared by software.

-

Page 230: Apb1 Peripheral Clock Enable Register 2 (Rcc_Apb1Enr2)

Reset and clock control (RCC) RM0351 Bit 3 TIM5EN: TIM5 timer clock enable Set and cleared by software. 0: TIM5 clock disabled 1: TIM5 clock enabled Bit 2 TIM4EN: TIM4 timer clock enable Set and cleared by software. 0: TIM4 clock disabled 1: TIM4 clock enabled Bit 1 TIM3EN: TIM3 timer clock enable Set and cleared by software. - Page 231 RM0351 Reset and clock control (RCC) Bit 2 SWPMI1EN: Single wire protocol clock enable Set and cleared by software. 0: SWPMI1 clock disable 1: SWPMI1 clock enable Bit 1 Reserved, must be kept at reset value. Bit 0 LPUART1EN: Low power UART 1 clock enable Set and cleared by software.

-

Page 232: Apb2 Peripheral Clock Enable Register (Rcc_Apb2Enr)

Reset and clock control (RCC) RM0351 6.4.21 APB2 peripheral clock enable register (RCC_APB2ENR) Address: 0x60 Reset value: 0x0000 0000 Access: word, half-word and byte access Note: When the peripheral clock is not active, the peripheral registers read or write access is not supported. - Page 233 RM0351 Reset and clock control (RCC) Bit 14 USART1EN: USART1clock enable Set and cleared by software. 0: USART1clock disabled 1: USART1clock enabled Bit 13 TIM8EN: TIM8 timer clock enable Set and cleared by software. 0: TIM8 timer clock disabled 1: TIM8 timer clock enabled Bit 12 SPI1EN: SPI1 clock enable Set and cleared by software.

- Page 234 Reset and clock control (RCC) RM0351 Bits 31:17 Reserved, must be kept at reset value. Bit 16 TSCSMEN: Touch Sensing Controller clocks enable during Sleep and Stop modes Set and cleared by software. 0: TSC clocks disabled by the clock gating during Sleep and Stop modes 1: TSC clocks enabled by the clock gating during Sleep and Stop modes...

- Page 235 RM0351 Reset and clock control (RCC) OTGFS SRAM2 GPIOH GPIOG GPIOF GPIOE GPIOD GPIOC GPIOB GPIOA Res. Res. Res. Res. Res. SMEN SMEN SMEN SMEN SMEN SMEN SMEN SMEN SMEN SMEN SMEN Bits 31:19 Reserved, must be kept at reset value. Bit 18 RNGSMEN: Random Number Generator clocks enable during Sleep and Stop modes Set and cleared by software.

- Page 236 Reset and clock control (RCC) RM0351 Bit 4 GPIOESMEN: IO port E clocks enable during Sleep and Stop modes Set and cleared by software. 0: IO port E clocks disabled by the clock gating during Sleep and Stop modes 1: IO port E clocks enabled by the clock gating during Sleep and Stop modes Bit 3 GPIODSMEN: IO port D clocks enable during Sleep and Stop modes Set and cleared by software.

-

Page 237: Apb1 Peripheral Clocks Enable In Sleep And Stop Modes Register

RM0351 Reset and clock control (RCC) Bit 8 QSPISMEN Quad SPI memory interface clocks enable during Sleep and Stop modes Set and cleared by software. 0: QUADSPI clocks disabled by the clock gating during Sleep and Stop modes 1: QUADSPI clocks enabled by the clock gating during Sleep and Stop modes Bits 7:1 Reserved, must be kept at reset value. - Page 238 Reset and clock control (RCC) RM0351 Bit 25 CAN1SMEN: CAN1 clocks enable during Sleep and Stop modes Set and cleared by software. 0: CAN1 clocks disabled by the clock gating during Sleep and Stop modes 1: CAN1 clocks enabled by the clock gating during Sleep and Stop modes Bit 24 Reserved, must be kept at reset value.

- Page 239 RM0351 Reset and clock control (RCC) Bit 11 WWDGSMEN: Window watchdog clocks enable during Sleep and Stop modes Set and cleared by software. This bit is forced to ‘1’ by hardware when the hardware WWDG option is activated. 0: Window watchdog clocks disabled by the clock gating during Sleep and Stop modes 1: Window watchdog clocks enabled by the clock gating during Sleep and Stop modes...

- Page 240 Reset and clock control (RCC) RM0351 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. LPTIM Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. UART1 2SMEN SMEN SMEN Bits 31:6 Reserved, must be kept at reset value.

- Page 241 RM0351 Reset and clock control (RCC) 6.4.27 APB2 peripheral clocks enable in Sleep and Stop modes register (RCC_APB2SMENR) Address: 0x80 Reset value: 0x0167 7C01 Access: word, half-word and byte access DFSDM SAI2 SAI1 TIM17 TIM16 TIM15 Res. Res. Res. Res. Res.

- Page 242 Reset and clock control (RCC) RM0351 Bit 14 USART1SMEN: USART1clocks enable during Sleep and Stop modes Set and cleared by software. 0: USART1clocks disabled by the clock gating during Sleep and Stop modes 1: USART1clocks enabled by the clock gating during Sleep and Stop modes Bit 13 TIM8SMEN: TIM8 timer clocks enable during Sleep and Stop modes Set and cleared by software.

-

Page 243: Peripherals Independent Clock Configuration Register (Rcc_Ccipr)

RM0351 Reset and clock control (RCC) 6.4.28 Peripherals independent clock configuration register (RCC_CCIPR) Address: 0x88 Reset value: 0x0000 0000 Access: no wait states, word, half-word and byte access DFSDM ADCSEL[1:0] CLK48SEL[1:0] SAI2SEL[1:0] SAI1SEL[1:0] LPTIM2SEL[1:0] LPTIM1SEL[1:0 I2C3SEL[1:0] LPUART1SEL UART5SEL UART4SEL USART3SEL USART2SEL USART1SEL I2C2SEL[1:0]... - Page 244 Reset and clock control (RCC) RM0351 Bits 23:22 SAI1SEL[1:0]: SAI1 clock source selection These bits are set and cleared by software to select the SAI1 clock source. 00: PLLSAI1 “P” clock (PLLSAI1CLK) selected as SAI1 clock 01: PLLSAI2 “P” clock (PLLSAI2CLK) selected as SAI1 clock 10: PLL “P”...

- Page 245 RM0351 Reset and clock control (RCC) Bits 9:8 UART5SEL[1:0]: UART5 clock source selection These bits are set and cleared by software to select the UART5 clock source. 00: PCLK selected as UART5 clock 01: System clock (SYSCLK) selected as UART5 clock 10: HSI16 clock selected as UART5 clock 11: LSE clock selected as UART5 clock Bits 7:6 UART4SEL[1:0]: UART4 clock source selection...

-

Page 246: Backup Domain Control Register (Rcc_Bdcr)

Reset and clock control (RCC) RM0351 6.4.29 Backup domain control register (RCC_BDCR) Address offset: 0x90 Reset value: 0x0000 0000, reset by Backup domain Reset, except LSCOSEL, LSCOEN and BDRST which are reset only by Backup domain power-on reset. Access: 0 ≤wait state ≤3, word, half-word and byte access Wait states are inserted in case of successive accesses to this register. - Page 247 RM0351 Reset and clock control (RCC) Bits 9:8 RTCSEL[1:0]: RTC clock source selection Set by software to select the clock source for the RTC. Once the RTC clock source has been selected, it cannot be changed anymore unless the Backup domain is reset, or unless a failure is detected on LSE (LSECSSD is set).

-

Page 248: Control/Status Register (Rcc_Csr)

Reset and clock control (RCC) RM0351 6.4.30 Control/status register (RCC_CSR) Address: 0x94 Reset value: 0x0C00 0600, reset by system Reset, except reset flags by power Reset only. Access: 0 ≤ wait state ≤ 3, word, half-word and byte access Wait states are inserted in case of successive accesses to this register. LPWR WWDG IWWG... - Page 249 RM0351 Reset and clock control (RCC) Bit 25 OBLRSTF: Option byte loader reset flag Set by hardware when a reset from the Option Byte loading occurs. Cleared by writing to the RMVF bit. 0: No reset from Option Byte loading occurred 1: Reset from Option Byte loading occurred Bit 24 FWRSTF: Firewall reset flag Set by hardware when a reset from the firewall occurs.

-

Page 250: Table 31. Rcc Register Map And Reset Values

Reset and clock control (RCC) RM0351 6.4.31 RCC register map The following table gives the RCC register map and the reset values. Table 31. RCC register map and reset values Off- Register MSIRANGE RCC_CR [3:0] 0x00 Reset value RCC_ICSCR HSITRIM[4:0] HSICAL[7:0] MSITRIM[7:0] MSICAL[7:0]... - Page 251 RM0351 Reset and clock control (RCC) Table 31. RCC register map and reset values (continued) Off- Register RCC_ AHB1RSTR 0x28 Reset value RCC_ AHB2RSTR 0x2C Reset value RCC_ AHB3RSTR 0x30 Reset value RCC_ APB1RSTR1 0x38 Reset value RCC_ APB1RSTR2 0x3C Reset value RCC_ APB2RSTR...

- Page 252 Reset and clock control (RCC) RM0351 Table 31. RCC register map and reset values (continued) Off- Register RCC_ APB1ENR2 0x5C Reset value RCC_ APB2ENR 0x60 Reset value RCC_ AHB1SMENR 0x68 Reset value RCC_ AHB2SMENR 0x6C Reset value RCC_ AHB3SMENR 0x70 Reset value RCC_ APB1SM...

- Page 253 RM0351 Reset and clock control (RCC) Table 31. RCC register map and reset values (continued) Off- Register RCC_BDCR 0x90 [1:0] [1:0] Reset value MSIS RCC_CSR RANGE[3:0] 0x94 Reset value DocID024597 Rev 3 253/1693...

-

Page 254: Introduction