Table of Contents

Advertisement

Quick Links

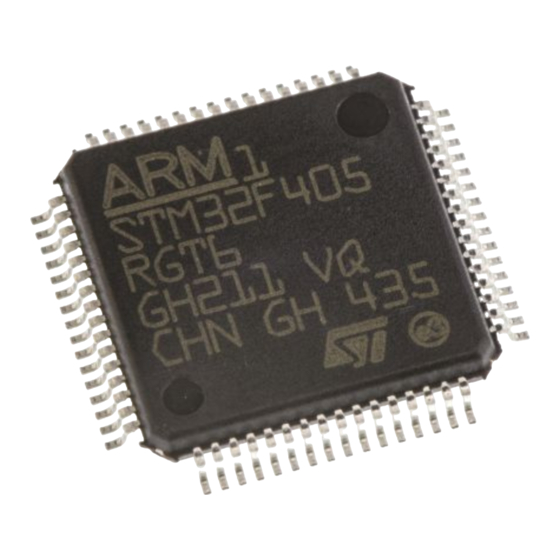

STM32F40xxx, STM32F41xxx, STM32F42xxx, STM32F43xxx

Introduction

This reference manual targets application developers. It provides complete information on

how to use the STM32F405xx/07xx, STM32F415xx/17xx, STM32F42xxx and

STM32F43xxx microcontroller memory and peripherals.

The STM32F405xx/07xx, STM32F415xx/17xx, STM32F42xxx and STM32F43xxx constitute

a family of microcontrollers with different memory sizes, packages and peripherals.

For ordering information, mechanical and electrical device characteristics please refer to the

datasheets.

For information on the ARM Cortex™-M4F core, please refer to the Cortex™-M4F Technical

Reference Manual.

Related documents

Available from STMicroelectronics web site (http://www/st.com):

■

STM32F40x and STM32F41x datasheets

■

STM32F42x and STM32F43x databriefs

■

For information on the ARM Cortex™-M4 core with FPU, refer to the STM32F3xx/F4xxx

Cortex™-M4 programming manual (PM0214).

Table 1.

Microcontrollers

February 2013

Applicable products

Product family

Doc ID 018909 Rev 4

Reference manual

advanced ARM-based 32-bit MCUs

Part numbers and product categories

STM32F405xx, STM32F407xx, STM32F415xx, STM32F417xx,

STM32F427xx, STM32F437xx

RM0090

1/1422

www.st.com

Advertisement

Table of Contents

Need help?

Do you have a question about the STM32F40 Series and is the answer not in the manual?

Questions and answers