Table of Contents

Advertisement

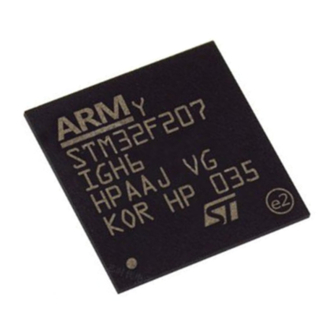

PM0059

Programming manual

STM32F205/215, STM32F207/217 Flash programming manual

Introduction

This programming manual describes how to program the Flash memory of STM32F205/215

and STM32F207/217 microcontrollers. For convenience, these will be referred to as

STM32F20x and STM32F21x in the rest of this document unless otherwise specified.

The STM32F20x and STM32F21xembedded Flash memory can be programmed using in-

circuit programming or in-application programming.

The in-circuit programming (ICP) method is used to update the entire contents of the

Flash memory, using the JTAG, SWD protocol or the boot loader to load the user application

into the microcontroller. ICP offers quick and efficient design iterations and eliminates

unnecessary package handling or socketing of devices.

In contrast to the ICP method, in-application programming (IAP) can use any

2

communication interface supported by the microcontroller (I/Os, USB, CAN, UART, I

C, SPI,

etc.) to download programming data into memory. With IAP, the Flash memory can be re-

programmed while the application is running. Nevertheless, part of the application has to

have been previously programmed in the Flash memory using ICP.

The Flash interface implements instruction access and data access based on the AHB

protocol. It implements a prefetch buffer that speeds up CPU code execution. It also

implements the logic necessary to carry out Flash memory operations (program/erase).

Program/erase operations can be performed over the whole product voltage range.

Read/write protections and option bytes are also implemented.

June 2013

DocID15687 Rev 5

1/29

www.st.com

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for ST STM32F205

-

Page 1: Table 1. Applicable Products

STM32F205/215, STM32F207/217 Flash programming manual Introduction This programming manual describes how to program the Flash memory of STM32F205/215 and STM32F207/217 microcontrollers. For convenience, these will be referred to as STM32F20x and STM32F21x in the rest of this document unless otherwise specified. -

Page 2: Table Of Contents

Contents PM0059 Contents Glossary ........... 5 Flash memory interface . - Page 3 List of tables List of tables Table 1. Applicable products ............1 Table 2.

- Page 4 List of figures List of figures Figure 1. Flash memory interface connection inside system architecture ..... . 6 Figure 2. Sequential 32-bit instruction execution .

-

Page 5: Glossary

PM0059 Glossary Glossary This section gives a brief definition of acronyms and abbreviations used in this document: • The CPU core integrates two debug ports: – JTAG debug port (JTAG-DP) provides a 5-pin standard interface based on the Joint Test Action Group (JTAG) protocol. –... -

Page 6: Flash Memory Interface

Flash memory interface PM0059 Flash memory interface Introduction The Flash memory interface manages CPU AHB I-Code and D-Code accesses to the 1 Mbyte (64 Kbit × 128 bits) Flash memory. It implements the erase and program Flash memory operations and the read and write protection mechanisms. The Flash memory interface accelerates code execution with a system of instruction prefetch and cache lines. -

Page 7: Flash Memory

Flash memory through one of the following interfaces: USART1, USART3, CAN2, USB OTG FS in Device mode (DFU: device firmware upgrade). The bootloader is programmed by ST when the device is manufactured, and protected against spurious write/erase operations. -

Page 8: Read Interface

Flash memory interface PM0059 Read interface 2.4.1 Relation between CPU clock frequency and Flash memory read time To correctly read data from Flash memory, the number of wait states (LATENCY) must be correctly programmed in the Flash access control register (FLASH_ACR) according to the frequency of the CPU clock (HCLK) and the supply voltage of the device. -

Page 9: Adaptive Real-Time Memory Accelerator (Art Accelerator™)

PM0059 Flash memory interface Decreasing the CPU frequency Modify the CPU clock source by writing the SW bits in the RCC_CFGR register If needed, modify the CPU clock prescaler by writing the HPRE bits in RCC_CFGR Check that the new CPU clock source or/and the new CPU clock prescaler value is/are taken into account by reading the clock source status (SWS bits) or/and the AHB prescaler value (HPRE bits), respectively, in the RCC_CFGR register Program the new number of wait states to the LATENCY bits in FLASH_ACR... -

Page 10: Figure 2. Sequential 32-Bit Instruction Execution

Flash memory interface PM0059 Figure 2. Sequential 32-bit instruction execution When the code is not sequential (branch), the instruction may not be present in the currently used instruction line or in the prefetched instruction line. In this case (miss), the penalty in terms of number of cycles is at least equal to the number of wait states. -

Page 11: Erase And Program Operations

PM0059 Flash memory interface Instruction cache memory To limit the time lost due to jumps, it is possible to retain 64 lines of 128 bits in an instruction cache memory. This feature can be enabled by setting the instruction cache enable (ICEN) bit in the FLASH_ACR register. -

Page 12: Program/Erase Parallelism

Flash memory interface PM0059 2.5.2 Program/erase parallelism The Parallelism size is configured through the PSIZE field in the FLASH_CR register. It represents the number of bytes to be programmed each time a write operation occurs to the Flash memory. PSIZE is limited by the supply voltage and by whether the external V supply is used or not. -

Page 13: Programming

PM0059 Flash memory interface Mass Erase To perform Mass Erase, the following sequence is recommended: Check that no Flash memory operation is ongoing by checking the BSY bit in the FLASH_SR register Set the MER bit in the FLASH_CR register Set the STRT bit in the FLASH_CR register Wait for the BSY bit to be cleared 2.5.4... -

Page 14: Interrupts

Flash memory interface PM0059 execution. If this cannot be done safely, it is recommended to flush the caches by setting the DCRST and ICRST bits in the FLASH_CR register. Note: The I/D cache should be flushed only when it is disabled (I/DCEN = 0). 2.5.5 Interrupts Setting the end of operation interrupt enable bit (EOPIE) in the FLASH_CR register enables... -

Page 15: Programming User Option Bytes

PM0059 Flash memory interface Table 7. Description of the option bytes Option bytes (word, address 0x1FFF C000) RDP: Read protection option byte. The read protection is used to protect the software code stored in Flash memory. 0xAA: Level 0, no protection Bits 15:8 0xCC: Level 2, chip protection (debug and boot from RAM features disabled) Others: Level 1, read protection of memories (debug features limited) -

Page 16: Read Protection (Rdp)

Flash memory interface PM0059 The user option bytes can be protected against unwanted erase/program operations by setting the OPTLOCK bit by software. Modifying user option bytes To modify the user option value, follow the sequence below: Check that no Flash memory operation is ongoing by checking the BSY bit in the FLASH_SR register Write the desired option value in the FLASH_OPTCR register Set the option start bit (OPTSTRT) in the FLASH_OPTCR register... -

Page 17: Table 8. Access Versus Read Protection Level

PM0059 Flash memory interface unchanged from before the mass-erase operation. The OTP area is not affected by mass erase and remains unchanged. Mass erase is performed only when Level 1 is active and Level 0 requested. When the protection level is increased (0->1, 1->2, 0->2) there is no mass erase. •... -

Page 18: Write Protections

Flash memory interface PM0059 Figure 3. RDP levels 2.6.4 Write protections The user sectors (0 to 11) in Flash memory can be protected against unwanted write operations due to loss of program counter contexts. When the not write protection bit in sector i (nWRPi, 0 ≤... -

Page 19: One-Time Programmable Bytes

PM0059 Flash memory interface Write protection error flag If an erase/program operation to a write protected area of the Flash memory is performed, the Write Protection Error flag (WRPERR) is set in the FLASH_SR register. If an erase operation is requested, the WRPERR bit is set when: •... -

Page 20: Flash Interface Registers

Flash memory interface PM0059 Flash interface registers 2.8.1 Flash access control register (FLASH_ACR) The Flash access control register is used to enable/disable the acceleration features and control the Flash memory access time according to CPU frequency. Address offset: 0x00 Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access Reserved DCRST ICRST... -

Page 21: Flash Key Register (Flash_Keyr)

PM0059 Flash memory interface 2.8.2 Flash key register (FLASH_KEYR) The Flash key register is used to allow access to the Flash control register and so, to allow program and erase operations. Address offset: 0x04 Reset value: 0x0000 0000 Access: no wait state, word access KEY[31:16] KEY[15:0] Bits 31:0 FKEYR: FPEC key... -

Page 22: Flash Status Register (Flash_Sr)

Flash memory interface PM0059 2.8.4 Flash status register (FLASH_SR) The Flash status register gives information on ongoing program and erase operations. Address offset: 0x0C Reset value: 0x0000 0000 Access: no wait state, word, half-word and byte access Reserved PGSERR PGPERR PGAERR WRPERR OPERR Reserved Reserved... -

Page 23: Flash Control Register (Flash_Cr)

PM0059 Flash memory interface Bits 3:2 Reserved, must be kept cleared. Bit 1 OPERR: Operation error Set by hardware when a flash operation (programming / erase) request is detected and can not be run because of parallelism, alignment, sequence or write protection error. This bit is set only if error interrupts are enabled (ERRIE = 1). -

Page 24: Flash Option Control Register (Flash_Optcr)

Flash memory interface PM0059 Bits 9:8 PSIZE: Program size These bits select the program parallelism. 00 program x8 01 program x16 10 program x32 11 program x64 Bit 7 Reserved, must be kept cleared. Bits 6:3 SNB: Sector number These bits select the sector to erase. 0000 sector 0 0001 sector 1 1011 sector 11... - Page 25 PM0059 Flash memory interface Bits 31:28 Reserved, must be kept cleared. Bits 27:16 nWRP: Not write protect These bits contain the value of the write-protection option bytes after reset. They can be written to program a new write protect value into Flash memory. 0: Write protection active 1: Write protection not active Bits 15:8 RDP: Read protect...

-

Page 26: Flash Interface Register Map

Flash memory interface PM0059 2.8.7 Flash interface register map Table 10. Flash register map and reset values Offset Register LATENC FLASH_ACR Reserved Reserved 0x00 Reset value FLASH_KEY KEY[31:16] KEY[15:0] 0x04 Reset value FLASH_OPT OPTKEYR[31:16] OPTKEYR[15:0] KEYR 0x08 Reset value FLASH_SR Rese Reserved Reserved... -

Page 27: Revision History

PM0059 Revision history Revision history Table 11. Document revision history Date Revision Changes Updated memory organization in memory, and Section 2.3: Flash replace user-specific block by OTP area. Updated addresses in Table 6: Option byte organization. Definition of BOR_LEV[3:2] bits updated in Table 7: Description of the option bytes Section 2.8.6: Flash option control register... - Page 28 Revision history PM0059 Table 11. Document revision history (continued) Date Revision Changes Modified Note 1 Table 3: Number of wait states according to 10-May-2011 CPU clock (HCLK) frequency Note 1 Table 3: Number of wait states according to CPU clock (HCLK) frequency.

- Page 29 No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

Need help?

Do you have a question about the STM32F205 and is the answer not in the manual?

Questions and answers