Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for NXP Semiconductors PN7462 series

- Page 1 UM10858 PN7462 family HW user manual Rev. 1.4 — 14 May 2018 User manual 314514 COMPANY PUBLIC Document information Info Content Keywords PN7462, PN7462 family, PN7362; PN7360; NFC reader Abstract This document describes how to use the PN7462 family.

- Page 2 UM10858 NXP Semiconductors PN7462 family HW user manual Revision history Date Description 20180514 Editorial updates 20180212 Reworking the document to describe complete PN7462 family SDA hold equation added 20170908 GPIO wakeup condition corrected Pull-up and pull-down configuration for SPIM pins corrected...

-

Page 3: Introduction

UM10858 NXP Semiconductors PN7462 family HW user manual 1. Introduction 1.1 General description The PN7462 family is a family of 32-bit ARM Cortex-M0-based NFC microcontrollers offering high performance and low power consumption. It has a simple instruction set and memory addressing along with a reduced code size compared to existing architectures. -

Page 4: Features And Benefits

UM10858 NXP Semiconductors PN7462 family HW user manual 1.2 Features and benefits 1.2.1 Integrated contact interface front-end This chapter applies to the products with contact interface only. • Class A, B, and C cards can work on 1.8 V, 3 V, and 5 V supply •... - Page 5 UM10858 NXP Semiconductors PN7462 family HW user manual • ISO/IEC 14443 Type A and B • Support for MIFARE Classic card • ISO/IEC 15693 and ISO/IEC 18000-3 mode 3 • iClass serial number support • Low power card detection function •...

-

Page 6: Derivates

UM10858 NXP Semiconductors PN7462 family HW user manual − Suspend mode for USB host interface − Processor wake-up from hard power down mode, stand-by mode, suspend mode via: host interface, contact card interface, GPIOs, RF field detection − Integrated PMU to automatically adjust internal regulators, to minimize the power consumption during all possible power modes. -

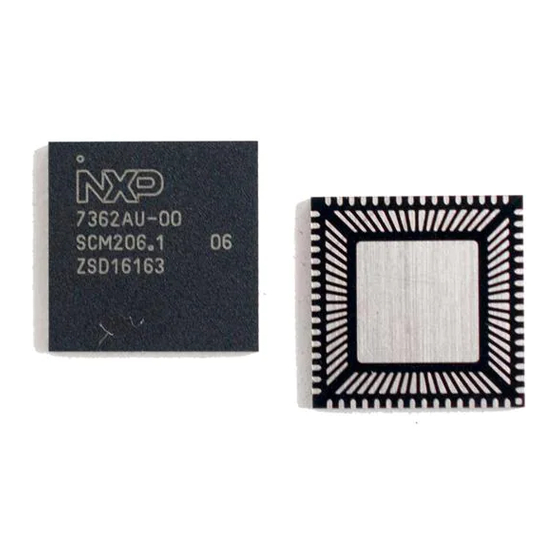

Page 7: Ordering Information

UM10858 NXP Semiconductors PN7462 family HW user manual 1.4 Ordering information Table 1. Ordering information Type Number Package Name Description Version PN7462AUHN 160 kB memory; contact interface; ISO/IEC 7816-3&4 HVQFN64 SOT804-4 UART interface; plastic thermal enhanced very thin quad flat package; no leads;... -

Page 8: Block Diagram Pn7462 Hvqfn64

UM10858 NXP Semiconductors PN7462 family HW user manual 1.5 Block diagram PN7462 HVQFN64 Fig 1. Block diagram UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018... -

Page 9: Block Diagram Pn7462 Vfbga64

UM10858 NXP Semiconductors PN7462 family HW user manual 1.6 Block diagram PN7462 VFBGA64 Fig 2. Block diagram UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018... -

Page 10: Block Diagram Pn736X

UM10858 NXP Semiconductors PN7462 family HW user manual 1.7 Block diagram PN736X Fig 3. Block diagram UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018... -

Page 11: Pn7462 Family Memory

UM10858 NXP Semiconductors PN7462 family HW user manual 2. PN7462 family memory 2.1 Memory mapping The PN7462 family incorporates several distinct memory regions. Fig 4 shows the overall map of the entire address space from user program viewpoint following reset. The APB peripheral area is 512 K in size, and is divided to allow for up to 32 peripherals. - Page 12 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 5. APB memory map UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018...

-

Page 13: On-Chip Flash Memory Map

UM10858 NXP Semiconductors PN7462 family HW user manual 2.2 On-chip flash memory map The PN7462 family contains 160 kB or 80 kB(PN7360) on-chip flash program memory. The flash can be programmed using In-System Programming (ISP) or In-Application Programming (IAP) via the on-chip boot-loader software. -

Page 14: Eeprom Memory Map

UM10858 NXP Semiconductors PN7462 family HW user manual 2.3 EEPROM memory map The PN7462 family embeds 4 kB of on-chip EEPROM data memory. The EEPROM memory map is shown in Fig 7. EEPROM memory mapping UM10858 All information provided in this document is subject to legal disclaimers. -

Page 15: Sram Memory Map

UM10858 NXP Semiconductors PN7462 family HW user manual 2.4 SRAM memory map The PN7462 family contains a total of 12 kB on-chip static RAM memory. The SRAM memory map is presented in Fig 8. SRAM memory mapping UM10858 All information provided in this document is subject to legal disclaimers. -

Page 16: Eeprom Ctrl Module

UM10858 NXP Semiconductors PN7462 family HW user manual 3. EEPROM CTRL module The EEPROM controller module controls the access to 4 kB EEPROM and 160 kB On- chip Flash memories. This comprises: • Reading the content of an EEPROM or Flash word in response to a read-transfer coming from the CPU •... -

Page 17: Ahb Interface

UM10858 NXP Semiconductors PN7462 family HW user manual • 2.8 ms maximum to write a page on the EEPROM, with a max. power consumption of 2 mA • 2.5 ms to write a page on the Flash in typical condition •... -

Page 18: Flash Controller

UM10858 NXP Semiconductors PN7462 family HW user manual 3.4.2 Read operation A read request cannot be handled within one AHB clock cycle, therefore wait states are inserted by the AHB Slave Interface. The targeted EEPROM is 16-bit oriented so 32-bit Read access need additional processing leading to additional wait states. -

Page 19: Register Overview

UM10858 NXP Semiconductors PN7462 family HW user manual Table 5. Wait states for read access on EEPROM Wait states FAST mode Wait states SLOW mode Address Width clock cycles (20 MHz Clock) clock cycles (20 MHz Clock) 32- bit access 3.6 Register overview... -

Page 20: Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) EE_INT_CLR_STATUS 0FE8h 0000_0000h Interrupt CLR_STATUS commands EE_INT_SET_STATUS 0FECh 0000_0000h Interrupt SET_STATUS commands 3.7 Register description Table 7. EE_CTRL (address offset 0x0000h) Symbol Access Value... - Page 21 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description EE_RST_1_COD resets the FLASH controller CRC_CLEAR_1_COD CRC clear function for FLASH FULL_DUMP_READ_1_COD performs a full or partial read of FLASH with CRC Calculation PROG_1_COD start programming data from the page...

- Page 22 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description hverr_dat HV error signal for the EEPROM Table 10. EE_STAT_COD (address offset 0x000Ch) Symbol Access Value Description 31:26 RESERVED Reserved ECC_READ_INVALID_1_COD 1 means that read access can’t be...

- Page 23 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 27:16 ee_CRC_DAT_ADDR_END 7FFh EEPROM CRC calculation end address corresponding to a native 16-bit data access (AHB memory map divided by 2) 15:12 RESERVED Reserved 11:0 ee_CRC_DAT_ADDR_START 000h EEPROM CRC calculation start address...

- Page 24 UM10858 NXP Semiconductors PN7462 family HW user manual Table 18. EE_CRC_0_COD_ADDR (address offset 0x002Ch) Symbol Access Value Description 31:16 ee_CRC_0_COD_ADDR_END 4FFFh FLASH_0 CRC calculation end address corresponding to a native 32-bit data access (AHB memory map divided by 8) 15:0...

- Page 25 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description EE_ECC_READ_NOT_CORRE FLASH_0 Not Correct ECC Read interrupt CT_0_COD_INT_CLR_ENABLE clear enable command EE_ECC_READ_INVALID_0_C FLASH_0 Invalid ECC Read interrupt OD_INT_CLR_ENABLE clear enable command ee_hverr_1_cod_int_clr_enable FLASH_1 High Voltage Error interrupt clear enable command...

- Page 26 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description EE_ECC_READ_NOT_CORRE FLASH_1 not correct ECC read interrupt CT_1_COD_INT_STATUS status variable EE_ECC_READ_INVALID_1_C FLASH_1 Invalid ECC read interrupt OD_INT_STATUS status variable EE_ECC_READ_NOT_CORRE FLASH_0 not correct ECC read interrupt CT_0_COD_INT_STATUS status variable...

- Page 27 UM10858 NXP Semiconductors PN7462 family HW user manual Table 26. EE_INT_CLR_STATUS (address offset 0x0FE8h) Symbol Access Value Description 31:10 RESERVED Reserved EE_ECC_READ_NOT_CORRE FLASH_1 not correct ECC read interrupt CT_1_COD_INT_CLR_STATUS clear status command EE_ECC_READ_INVALID_1_C FLASH_1 Invalid ECC read interrupt clear OD_INT_CLR_STATUS...

-

Page 28: Nested Vectored Interrupt Controller (Nvic)

UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description ee_prog_dat_completed_int_SE EEPROM programming completed T_STATUS interrupt set status command 4. Nested Vectored Interrupt Controller (NVIC) The NVIC is an integral part of the Cortex-M0. The tight coupling to the CPU allows for a low interrupt latency and efficient processing of late arriving interrupts. -

Page 29: Nvic Register Support In The Scs

UM10858 NXP Semiconductors PN7462 family HW user manual EIRQ# Source Description interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO 1 interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO 2 interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO 3 interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO 4 interrupt (rise/fall/both-edge/level-high/level-low interrupt as... - Page 30 UM10858 NXP Semiconductors PN7462 family HW user manual Table 29. NVIC register overview Address Name Type Reset Description enables, or reads the enabled state 0xE000E100 NVIC_ISER 0x00000000 of one or more interrupts 0xE000E104- Reserved 0xE000E17F 0xE000E180 NVIC_ICER 0x00000000 disables, or reads the enabled state...

-

Page 31: Swd

UM10858 NXP Semiconductors PN7462 family HW user manual 4.4 SWD Cortex-M0 processor-based devices use the Serial Wire ARM CoreSight™ debug technology. The Serial Wire Debug (SWD) signals are connected to the pads via the PCR (Power, Clock & Reset) described in Section 0. -

Page 32: Pn7462 Family Power Management

UM10858 NXP Semiconductors PN7462 family HW user manual Address Name Type Reset Description 0xE000E1C SYST_CALIB System Timer Calibration value register For more details, refer to DDI0419C_arm_architecture_v6m_reference_manual which can be found on the ARM webpage. Example timer calculation To use the system tick timer, do the following: a. - Page 33 UM10858 NXP Semiconductors PN7462 family HW user manual 6.1.1 Microcontroller supply In order to use the PN7462 family as microcontroller with host interface following voltages (minimum requirements) need to be supplied: • VBUS • PVDD_IN (if PVDD_OUT is not used, it needs to be shorted to GND) •...

- Page 34 UM10858 NXP Semiconductors PN7462 family HW user manual VBUS DDP(VBUS) VBUSP DDP(VBUS) 1 µF T VSS PN7462 family GNDC GNDP DVDD 1 µF VBUS VBUS DDP(VBUS) DDP(VBUS) VBUSP VBUSP DDP(VBUS) DDP(VBUS) 1 µF 1 µF PVDD_OUT PVDD_OUT PN7462 family PN7462 family...

- Page 35 UM10858 NXP Semiconductors PN7462 family HW user manual In case TVDD_OUT is used • VUP_TX needs to be supplied. Remark: The TVDD_OUT pin must not be left floating, and needs to be at the same voltage as the TVDD_IN pin.

- Page 36 UM10858 NXP Semiconductors PN7462 family HW user manual VBUS PN7462 family VBUS PN7462 family supply supply 470 nF 470 nF T X2 T X2 antenna antenna PN7462 family VUP_T X VUP_T X T X1 T X1 supply supply RF transmitter...

- Page 37 UM10858 NXP Semiconductors PN7462 family HW user manual 1 µF SCVDD 470 nF GDNP VBUSP PN7462 2.7 µF 470 nF 100 nF (1) 470 nF VBUS GNDC DDP(VBUS) DDP(VBUS) 470 nF aaa-021 145 Fig 13. Powering the contact interface SCVDD n.c.

-

Page 38: Power Management Unit

UM10858 NXP Semiconductors PN7462 family HW user manual 6.2 Power Management Unit The Integrated Power Management Unit (PMU) supplies internal analog modules, internal digital logic, memories and pads. It also provides regulated voltages for the contactless and the contact interfaces. The PMU automatically adjusts the internal regulators to minimize the power consumption during all possible power modes. - Page 39 UM10858 NXP Semiconductors PN7462 family HW user manual Pin No Pin Name IN(I)/Out(O) Connection Comment DVDD connected to VMID blocking recommended 100nF capacitor to TVDD_IN externally powered or TVDD_OUT can be set in TVDD_OUT PMU_TXLDO_CONTROL_ VUP_TX externally powered or VBUS 1.8 V output for DVDD...

- Page 40 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 16. PN7462 family basic schematic 6.2.1 Low Drop-Out regulators The PMU embeds several Low Drop-Out regulators (LDO) in order to ensure the stability of the power supply. 6.2.1.1 Main LDO The Main LDO (MLDO) provides 1.8 V for all internal analog, digital and memory modules.

- Page 41 UM10858 NXP Semiconductors PN7462 family HW user manual 6.2.1.2 PVDD_LDO The PVDD_LDO provides 3.3 V for all digital pads. It is supplied by VBUS, and requires a minimum voltage of 4 V to be functional. It delivers a maximum current of 30 mA. The output of the PVDD_LDO is PVDD_OUT pin.

-

Page 42: Pn7462 Family Pmu Digital Control Unit

UM10858 NXP Semiconductors PN7462 family HW user manual 6.2.1.7 Start-up times of LDOs Table 34. Start-up times of LDOs Max Startup Time PVDDLDO 1.5 ms TXLDO 200 µs VCC LDO 22 ms (including DC-to-DC converter, SCLDO and VCCLDO startup times) 500 µs (excluding DC-to-DC and SCLDO) -

Page 43: Interrupts

UM10858 NXP Semiconductors PN7462 family HW user manual 6.4 Interrupts Interrupt signals are generated in the analog part of the PMU as a result of: • TXLDO 5 V monitoring • VCC current limiter • DC-to-DC converter current overload • SCVDD current overload •... - Page 44 UM10858 NXP Semiconductors PN7462 family HW user manual Voltage Monitor Threshold 1 Threshold 2 Threshold 3 VBUS2 2.7 V VBUSP 2.7 V 3.9 V 6.6.1 VBUS monitor The PN7462 family offers two selectable thresholds (2.3 V or 2.7 V) for monitoring the voltage on the VBUS pin.

-

Page 45: Register Overview And Description

UM10858 NXP Semiconductors PN7462 family HW user manual 6.6.4 Latency of voltage monitors Table 36. Latency of voltage monitors Voltage Monitor Latency VBUS1 10 µs VBUS2 10 µs VBUSP 75 µs 6.7 Register overview and description Table 37. PMU register overview (base address 0x4000 8000) - Page 46 UM10858 NXP Semiconductors PN7462 family HW user manual 6.7.1 Detailed register description 6.7.1.1 PMU_STATUS_REG This register is used to observe signals in system mode. Table 38. PMU_STATUS_REG (address offset 0x0000) Symbol Access Value Description 31:25 RESERVED 0x00 Reserved MLDO_LOWPOWER_VBATBUF R-...

- Page 47 UM10858 NXP Semiconductors PN7462 family HW user manual 6.7.1.2 PMU_BG_MON_CONTROL_REG This register is used to enable comparators and set thresholds for the monitors. Table 39. PMU_BG_MON_CONTROL_REG (address offset 0x0004) Symbol Access Value Description 31:11 RESERVED 0x00 Reserved Activates 1.8 V comparator for PVDD_M 1: Enable 1.8 V comparator for PVDD_M...

- Page 48 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 0: Disable 2nd regulator 27:25 RESERVED 0x02 Do not modify value TXLDO_RSTN_SOURCE_SEL 0x00 Source selection bit of TXLDO_digi resetn. 0: resetn source = rst_pcr_system_n 1: resetn source = (~rst_pcr_system_n or...

- Page 49 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 2 = 3.6 V 3 = 4.5 V 4 and others=4.7 V Activates current limiter 1: Enable current limiter TXLDO_LIMITER_EN 0x00 0: Disable current limiter TXLDO_LOW_POWER_EN 0x00 Activates the low-power mode...

- Page 50 UM10858 NXP Semiconductors PN7462 family HW user manual 6.7.1.5 PMU_INTERRUPT_CLR_ENABLE_REG This register is a collection of Clear Interrupt Enable commands with automatic clear if set by software. Table 42. PMU_INTERRUPT_CLR_ENABLE_REG (address offset 0x3FD8) Symbol Access Value Description 31:9 RESERVED 0x00...

- Page 51 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RESERVED 0x00 Reserved PVDD_IRQ_SET_ENABLE 0x00 Enables PVDD interrupt. Automatically cleared after 2 cycles if set by software DCDC_OVERLOAD_IRQ_SET_E 0x00 Enables DC-to-DC converter overload. NABLE Automatically cleared after 2 cycles if set...

- Page 52 UM10858 NXP Semiconductors PN7462 family HW user manual 6.7.1.8 PMU_INTERRUPT_ENABLE_REG This register is a collection of Interrupt Enable commands. Table 45. PMU_INTERRUPT_ENABLE_REG (address offset 0x3FE4) Symbol Access Value Description 31:9 RESERVED 0x00 Reserved VBUSMON2_LOW_IRQ_ENABL Indicates enabled VBUS monitor 2 going...

- Page 53 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description VCC_ILIM_ACT_IRQ_CLEAR_STA 0x00 Clears status of VCC current limiter active interrupt. Automatically cleared after 2 cycles if clear by software RESERVED 0x00 Reserved PVDD_IRQ_CLEAR_STATUS 0x00 Clears status of PVDD interrupt. Automatically...

- Page 54 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description TEMPSENS_ERROR_IRQ_SET_ 0x00 Sets status of temperature sensor interrupt. STATUS Automatically cleared after 2 cycles if set by software 6.7.2 TXLDO Register settings Table 48. TXLDO Register Mode Register...

-

Page 55: Clock Generator

UM10858 NXP Semiconductors PN7462 family HW user manual 7. Clock generator The PN7462 family uses following clock sources: • External 27.12 MHz crystal oscillator • Internal 20 MHz HFO (High Frequency Oscillator) • Internal 380 kHz LFO (Low Frequency Oscillator) •... - Page 56 UM10858 NXP Semiconductors PN7462 family HW user manual 7.1.1 27.12 MHz Crystal oscillator (XTAL) The 27.12 MHz crystal oscillator is used as a reference for all operations requiring high stability of the clock frequency. This includes: contactless interface, contact interface, SPI and I2C master interfaces, HSUART and USB PLL for the USB interface.

-

Page 57: Phase Locked Loop (Usb Pll)

UM10858 NXP Semiconductors PN7462 family HW user manual • Wait for system reset release • Wait for 4 clk_lfo clock cycles (4x(1/380 KHz) ~ 10.53 us) • Set XTAL_ENABLE_KICK to ’1’ • Wait for 4 clk_lfo clock cycles (4x(1/380 KHz) ~ 10.53 us) •... - Page 58 UM10858 NXP Semiconductors PN7462 family HW user manual USB PLL features: • Low-skew, Peak-peak cycle-to-cycle jitter 48 MHz output clock (100 ps typical) • Low Power in active more, low power-down current • On-Chip loop filter, no external RC components needed 7.2.1 USB PLL Clock source selection...

- Page 59 UM10858 NXP Semiconductors PN7462 family HW user manual CLKGEN_USB_PLL_CONTROL_REG.USB_PLL_CLKOUT_SELECT = ’00’ • Crystal Oscillator or External clock CLKGEN_USB_PLL_CONTROL_REG.USB_PLL_CLKOUT_SELECT = ’01’ • USB Clock Disable CLKGEN_USB_PLL_CONTROL_REG.USB_PLL_CLKOUT_SELECT = ’10’ or ‘11’ 7.2.3 USB PLL frequency calculation The USB PLL soft decoder selects pre-defined divider ratios and corresponding bandwidth of the PLL to guarantee stability.

-

Page 60: Clif Pll

UM10858 NXP Semiconductors PN7462 family HW user manual 4. Enable Input Clock Detector CLKGEN_INPUT_CLOCK_DETECTOR_CONTROL_REG.USB_CLK_DETECT_EN ABLE = ’1’. 5. Poll for CLKGEN_STATUS_REG.CLK_IN_DETECT_DONE = ’1’ (after ~5.2 us by default). This will only indicate that the detection procedure is finished, not that there is clock and/or the frequency is the expected one. -

Page 61: Register Overview And Description

UM10858 NXP Semiconductors PN7462 family HW user manual combination of both (depending on the clock settings), is available. This signal can be overridden using CLIF_PLL_CLK_IN_OK_BYPASS register. 7.3.1 Optimum divider settings for CLIF PLL Table 50. Optimum divider settings for PLL1 and PLL2... -

Page 62: Clock Status Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual 7.5 Clock Status Register description Table 52. CLKGEN_STATUS_REG (address 0000h) Symbol Access Value Description 31:27 RESERVED Reserved Indicates the status of clkgen_clif_pll_lock2_o signal. CLIF_CLOCK_PRESENCE_OK 1: CLIF PLL2 lock signal set 0: CLIF PLL2 lock signal not set... - Page 63 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Acknowledged 0: No feedback divider ratio change USB_PLL_LOCK_OVERRIDEN USB_PLL lock overriden status 1: CLKGEN_STATUS_REG.USB_PLL_lock or CLKGEN_USB_PLL_GLOBAL_CONTROL_REG.USB_ PLL_lock_bypass is high. 0: USB PLL Lock is not set USB_PLL_LOCK USB_PLL lock status...

-

Page 64: Usb Pll Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description XTAL_VOLTAGE_MUX_CLOC 0x00 controls XTAL voltage Mux XTAL_SEL_EXTERNAL_CLOC 0x00 Controls XTAL external clock selection if XTAL_CONTROL_SW='1' 1: Select External clock 0: Select XTAL Oscillator clock XTAL_ENABLE 0x00 controls XTAL Enable if XTAL_CONTROL_SW='1'... - Page 65 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) CLKGEN_USB_PLL_NDEC_PDE 0014h 00000000h PLL N and P decoded divider ratio when the soft decoder is not C_WO_SOFTDEC_REG used 7.6.1 PLL Control Register (CLKGEN_USB_PLL_CONTROL_REG - 000Ch) The CLKGEN_USB_PLL_CONTROL_REG register contains the bits that enable and connect PLL1.

- Page 66 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description USB_PLL_PREQ 0x00 USB_PLL post-divider ratio change request 1: Request change of USB_PLL post-divider ratio (ratio taken from register) USB_PLL_NREQ 0x00 USB_PLL pre-divider ratio change request 1: Request change of USB_PLL pre-divider ratio (ratio...

-

Page 67: Clif Pll Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual 7.6.3 PLL N and P decoded divider ratio The CLKGEN_USB_PLL_NDEC_PDEC_WO_SOFTDEC_REG register contains the USB PLL multiplier and divider values. Changes to CLKGEN_USB_PLL_NDEC_PDEC_WO_SOFTDEC register do not take effect until a correct USB feed sequence has been given (see Section 7.2). - Page 68 UM10858 NXP Semiconductors PN7462 family HW user manual Table 61. CLKGEN_CLIF_PLL1_CONTROL_REG (address 0018h) Symbol Access Value Description 31:28 RESERVED 0x00 Reserved CLIF_PLL_LIMUP_OFF1 0x00 pulse limiter for CLIF_PLL 1 CLIF_PLL_FREQ_LIM1 0x00 frequency limiter for CLIF_PLL 1 25:24 CLIF_PLL_SELP1 0x02 Pins to select the BW of CLIF_PLL 1...

- Page 69 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Bypass clif_pll_lock2 CLIF_PLL_FUNC_TEST2_LOCK2 0x00 1: Enable functional CLIF_PLL test chain of lock detector CLIF_PLL_FUNC_TEST1_LOCK2 0x00 1: Enable functional divider test of lock detector 2 7.7.3 CLIF PLL GLOBAL CONTROL REG The CLIF PLL GLOBAL CONTROL REG register contains the bits that enable and connect CLIF PLL.

- Page 70 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 0: Disable the CLIF PLL 7.7.4 INPUT CLOCK DETECTOR CONTROL REGISTER Table 64. CLKGEN_INPUT_CLOCK_DETECTOR_CONTROL_REG (address 0024h) Symbol Access Value Description 31:14 RESERVED Reserved USB_PLL_CLK_IN_OK_BYPASS usb pll clk_in detection override 1: usb_pll_clk_in detection overridden.

-

Page 71: Power Clock And Reset (Pcr)

UM10858 NXP Semiconductors PN7462 family HW user manual 8. Power clock and reset (PCR) The Power, Clock & Reset Unit (PCR) handles the digital startup of the PN7462 family and manages the behavior of the system in low power and active modes. The PCR unit is the only digital block that is powered in the standby mode. -

Page 72: Reset Sources

UM10858 NXP Semiconductors PN7462 family HW user manual Fig 21. Block diagram of PCR Unit 8.1 Reset sources The PN7462 family has 6 possible rest sources. These are described in detail in Table Table 66. Reset sources Source Description Software reset from the PCR peripheral; Resets the whole... -

Page 73: Boot Reason Decoding

UM10858 NXP Semiconductors PN7462 family HW user manual These reset sources trigger the reset generator that generates a global reset pulse. The Reset Generator is active high-level sensitive to the reset sources. As long as one reset source is high, the global reset will be active. After releasing the reset source, the reset pulse will be prolonged to at least one cycle. -

Page 74: Power Modes

UM10858 NXP Semiconductors PN7462 family HW user manual 8.3 Power modes The PN7462 family offers four different power modes allowing customer to optimize its energy consumption. These are: • Active mode • Standby mode • USB suspend mode • Hard Power Down mode 8.3.1 Full Power Mode (Active Mode) - Page 75 UM10858 NXP Semiconductors PN7462 family HW user manual Root cause description Either RF level detector is activated as wakeup source and RF level detector is not enabled or RF field is already present Host Interface is selected as wakeup source and no PVDD is available PVDD current limiter input has seen a 01...

- Page 76 UM10858 NXP Semiconductors PN7462 family HW user manual 8.3.4 Wake-up from Standby/Suspend Mode Standby/suspend mode is left if one of the following conditions is met: • Host activity (SPI, I2C, HSU) for standby mode and USB Resume for suspend mode with following pre-conditions: −...

- Page 77 UM10858 NXP Semiconductors PN7462 family HW user manual LDO/PLL Active Standby Suspend Hardware/Software Full/Low enabling power DCDC/SCLDO/ switches. power/OFF software VCCLDO TXLDO Full/Low Standby-LDO Standby-LDO power/OFF mode mode software PLLs and oscillators OFF: hardware USB PLL ON/OFF ON: software CLIF PLL...

-

Page 78: Clock Box

UM10858 NXP Semiconductors PN7462 family HW user manual 8.4 Clock box The Clock Box is responsible for generating all clock signals for the system. The PCR_CLK_CFG_REG and PCR_CLK_CFG2_REG are used by firmware to gate system and IP clocks going to different modules. -

Page 79: Clock Gating

UM10858 NXP Semiconductors PN7462 family HW user manual The selection is done using the PCR_SELECT_SYSTEMCLOCK [2:0] 001 ... 20 MHz clkHFO (default) 010 ... 24 MHz clkUSBPLL/2 (internal test purpose) 100 ... 27.12 MHz clkXtal (internal test purpose) Others ... INVALID, should not be programmed 8.5 Clock Gating... -

Page 80: I/O Pad Management

UM10858 NXP Semiconductors PN7462 family HW user manual Fig 23. Clock gating 8.6 I/O Pad Management I/O Pad Management allows: • Connecting the GPIO/I2C/SPI to a peripheral IO for device pins that are not connected to a specific peripheral function •... -

Page 81: Register Overview

UM10858 NXP Semiconductors PN7462 family HW user manual PAD Name Power Supply MISO_M, MOSI_M, SCLK_M, NSS_M PVDD_IN_M SCL_M, SDA_M PVDD_IN_M GPIO1 to GPIO12 PVDD_IN SWDIO, SWDCLK PVDD_IN PVDD_IN 8.6.1 Hard Power Down (HPD) State of Pads In the Hard Power Down mode, all digital pad signals will be masked. - Page 82 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description (bits) Offset Bootup register with important values to PCR_BOOT_REG 0x0028 0x00000000 be checked during bootup Control register to enable standby/suspend/soft-restart/clearing PCR_CTRL_REG 0x002C 0x00000000 boot register...

- Page 83 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description (bits) Offset PCR_PADSWDIO_REG 0x0094 0x00000006 SWDIO pad slew rate configuration INTERNAL_USE 0x0098 0x00000006 For internal use RESERVED 0x009C 0x0000020C Reserved RESERVED 0x00A0 0x00000008 Reserved PCR_PADIICM_REG...

-

Page 84: Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description (bits) Offset PCR_INT_ENABLE_REG 0x3FE4 0x00000000 interrupt enable PCR_INT_CLR_STATUS_RE 0x3FE8 0x00000000 interrupt clear status PCR_INT_SET_STATUS_RE 0x3FEC 0x00000000 interrupt set status 8.8 Register description Table 72. PCR_GPREG0_REG (address offset 0x00) - Page 85 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Enable PVDD_M IRQ 0: Disable PVDD_M IRQ Selects the PVDD voltage trigger level 0: PVDD voltage trigger level 1.8 V PVDD_IRQ_VAL 0x00 1: PVDD voltage trigger level 3.3 V...

- Page 86 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Enable low power mode of MLDO 0: Disable low power mode of MLDO To set the DC-to-DC converter in high impedance state enabling the testing of VCCLDO. VUP will be forced from outside.

- Page 87 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 0: Disable the chopper filter for RF Level Detector Enable of RFLD comparator 0: Disable RFLD comparator 1: Enable RFLD comparator RFLD_COMP_ENABLE 0x00 Enable of RFLD envelope detector...

- Page 88 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 17:16 Selects temperature threshold detection for temperature sensor 0 TEMP_DELTA_0 0x01 15:12 Trim value fine for temperature sensor 1 TEMP_CAL_FINE_1 0x08 11:8 Trim value course for temperature sensor 1...

- Page 89 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 11:0 Enables wake-up by the corresponding GPIO 0: gpio1 1: GPIO2 GPIO_WAKEUP_ENABLE 0x0FF e.t.c …. Table 82. PCR_BOOT_REG (address offset 0x28) Symbol Access Value Description RESERVED 0x00 Reserved...

- Page 90 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Clear the boot register RESERVED 0x00 Reserved Enables entering suspend mode SUSPEND 0x00 1: Enter suspend mode entering standby mode STANDBY 0x00 1: Enter standby mode Trigger Soft Reset Source...

- Page 91 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description CLOCK_TIMER_ENABLE 1: Enable clock source for TIMER 0x01 0: Disable clock source for TIMER CLOCK_CRC_ENABLE 1: Enable clock source for CRC 0x01 0: Disable clock source for CRC...

- Page 92 UM10858 NXP Semiconductors PN7462 family HW user manual Table 85. PCR_CLK_CFG2_REG (address offset 0x34) Symbol Access Value Description 31:18 RESERVED 0x00 Reserved CTRL_TXLDO_CLK 0x00 TXLDO clock division select. 0->LFO/2 , 1-> LFO Selects between XTAL clock and external clock. 0 - XTAL...

- Page 93 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 01: DIVby2 10: DIVby4 11: Reserved Table 86. PCR_PADIN_REG (address offset 0x38) Symbol Access Value Description 31:28 RESERVED 0x00 Reserved RESERVED 0x00 Reserved PADIN_CLK_AUX 0x00 input value for CLK_AUX...

- Page 94 UM10858 NXP Semiconductors PN7462 family HW user manual Table 87. PCR_PADOUT_REG (address offset 0x3C) Symbol Access Value Description 31:29 RESERVED 0x00 Reserved RESERVED 0x00 Reserved RESERVED 0x00 Reserved PADOUT_CLK_AUX 0x00 output value for CLK_AUX PADOUT_IO_AUX 0x00 output value for IO_AUX...

- Page 95 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 10: Enable pull up 11: Enable pull down ATX_A_EN_OUT 0x00 1: Enables output driver for ATX_A ATX_A_EN_IN 0x00 1: Enables input driver for ATX_A Table 89. PCR_PAD_ATX_B_REG (address offset 0x44)

- Page 96 UM10858 NXP Semiconductors PN7462 family HW user manual Table 92. PCR_PADDWL_REQ_REG (address offset 0x50) Symbol Access Value Description 31:5 RESERVED 0x00 Reserved Select driver strength for DWLREQ DWLREQ_SLEW_RATE 0x00 1: Enable slew for DWL_REQ Enable pull Up/Down on DWLREQ 10: Enable pull up...

- Page 97 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Enable Slew for IO_AUX Enable pull Up/Down on IO_AUX 10: Enable pull up IO_AUX_PUPD 0x00 11: Enable pull down IO_AUX_EN_OUT 0x00 1: Enables output driver for IO_AUX...

- Page 98 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Select driver strength for GPIO1 GPIO1_SLEW_RATE 0x00 1: Enable Slew for GPIO1 Enable pull Up/Down on GPIO1 01: Enable pull up GPIO1_PUPD 0x00 11: Enable pull down GPIO1_EN_OUT...

- Page 99 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Enable pull Up/Down on GPIO4 10: Enable pull up GPIO4_PUPD 0x00 11: Enable pull down GPIO4_EN_OUT 0x00 1: Enables output driver for GPIO4 GPIO4_EN_IN 0x01 1: Enables input driver for GPIO4 Table 101.

- Page 100 UM10858 NXP Semiconductors PN7462 family HW user manual Table 104. PCR_PADGPIO8_REG (address offset 0x80) Symbol Access Value Description 31:5 RESERVED 0x00 Reserved Select driver strength for GPIO8 GPIO8_SLEW_RATE 0x00 1: Enable slew for GPIO8 Enable pull Up/Down on GPIO8 10: Enable pull up...

- Page 101 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Enable Slew for GPIO11 Enable Pull Up/Down on GPIO11 10: Enable pull up GPIO11_PUPD 0x00 11: Enable pull down GPIO11_EN_OUT 0x00 1: Enables output driver for GPIO11...

- Page 102 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 11: Enable pull down Enables pull up/down functionality on SCL 10: Enable pull up SCL_PUPD 0x00 11: Enable pull down SDA_SLEW 0x00 1: Enables SDA slew rate SCL_SLEW...

- Page 103 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description SW control for SPIM_NSS ECS when SPIM_SW_ENABLE='1' SPIM_NSS_EN_OUT 0x00 1: SPIM NSS enabled as output SW control for SPIM_SCK ECS when SPIM_SW_ENABLE='1' SPIM_SCK_EN_OUT 0x00 1: SPIM CLK enabled as output...

- Page 104 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Value of ct_pres_enable_pup_i coming from CTIF is latched and is used to detect card activity during standby and suspend modes if CTIF is enabled as wakeup source CT_ENABLE_PUP...

- Page 105 UM10858 NXP Semiconductors PN7462 family HW user manual Table 119. PCR_GPREG3_REG (address offset 0xCC) Symbol Access Value Description 31:0 PCR_GPREG3 0x00 general-purpose register for SW Table 120. PCR_GPREG4_REG (address offset 0xD0) Symbol Access Value Description 31:0 PCR_GPREG4 0x00 general-purpose register for SW Table 121.

- Page 106 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description indicates if GPIO7 interrupts are active low/falling edge. 0: Active_high/Rising edge; GPIO7_INTR_ACTIVE_LO 0x00 1 - Active_low/falling edge. indicates if GPIO6 interrupts are active low/falling edge. 0: Active_high/Rising edge;...

- Page 107 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 0: Edge sensitive; 1 - Level sensitive. indicates if GPIO7 interrupts are level sensitive/edge sensitive. 0: Edge sensitive; GPIO7_INTR_LEVEL_SEN SITIVE 0x00 1: Level sensitive. indicates if GPIO6 interrupts are level sensitive/edge sensitive.

- Page 108 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description indicates if GPIO10 interrupts are both positive and negative edge triggered. 0: Not both edge triggered; GPIO10_INTR_BOTH_EDG E_SENSITIVE 0x00 1: Both positive edge and negative edge triggered. indicates if GPIO9 interrupts are both positive and negative edge triggered.

- Page 109 UM10858 NXP Semiconductors PN7462 family HW user manual Table 127. PCR_SELECT_SYSTEMCLOCK_REG (address offset 0xEC) Symbol Access Value Description 31:3 RESERVED 0x00 Reserved Selects the clock source 001: clkHFO (20 MHz) 010: clkUSBPLL/2 (24 MHz) (internal test purpose) 100: clkXtal (27.12 MHz) (internal test purpose)

- Page 110 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Enable manual setting of advanced RF level detection. 1: Enable manual setting of RF level detection ADV_RFLD_TEST_ENABL 0x00 0: Disable Manual setting of RF level detection Table 130. PCR_INT_CLR_ENABLE_REG (address offset 0x3FD8)

- Page 111 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 1: Disable VBUSP monitor low interrupt PVDD current limiter active interrupt clear enable. PVDD_CURLIM_ACT_CLR _ENABLE 0x00 1: Disable PVDD current limiter interrupt Temperature error 1 interrupt clear enable...

- Page 112 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description GPIO2 pad going high interrupt set enable GPIO2_PAD_HIGH_INT_S ET_ENABLE 0x00 1: Enable GPIO2 interrupt GPIO1 pad going high interrupt set enable GPIO1_PAD_HIGH_INT_S ET_ENABLE 0x00 1: Enable GPIO1 interrupt...

- Page 113 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description GPIO8 pad going high interrupt status GPIO8_PAD_HIGH_INT_ST ATUS 0x00 1: Indicates GPIO8 interrupt is set. GPIO7 pad going high interrupt status GPIO7_PAD_HIGH_INT_ST ATUS 0x00 1: Indicates GPIO7 interrupt is set.

- Page 114 UM10858 NXP Semiconductors PN7462 family HW user manual Table 133. PCR_INT_ENABLE_REG (address offset 0x3FE4) Symbol Access Value Description 31:28 RESERVED 0x00 Reserved GPIO12 pad going high interrupt enable GPIO12_PAD_HIGH_INT_E NABLE 0x00 1: Indicates GPIO12 interrupt enabled. GPIO11 pad going high interrupt enable...

- Page 115 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Temperature error 0 interrupt enable TEMPERROR0_INT_ENAB 1: Indicates temperature sensor 0 error interrupt 0x00 enabled. Suspend defaulted interrupt enable SUSPEND_DEFAULTED_I NT_ENABLE 0x00 1: Indicates suspend prevented interrupt enabled.

- Page 116 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description VBUSP monitor going high interrupt clear status VBUSP_MON_HIGH_INT_ 1: Clear VBUSP monitor high interrupt. Auto clear after 2 CLR_STATUS 0x00 cycles. Clif RF field activity observed interrupt clear status CLIF_RFLD_ACT_INT_CLR 1: Clear RF level detected interrupt.

- Page 117 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description GPIO8 pad going high interrupt set status GPIO8_PAD_HIGH_INT_S ET_STATUS 0x00 1: Set GPIO8 interrupt. Auto clear after 2 cycles. GPIO7 pad going high interrupt set status GPIO7_PAD_HIGH_INT_S ET_STATUS 0x00 1: Set GPIO7 interrupt.

-

Page 118: Crc

UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Suspend interrupt set status. SUSPEND_INT_SET_STAT 0x00 1: Set suspend (exit) interrupt. Auto clear after 2 cycles. GPIO interrupt clear status GPIO_INT_SET_STATUS 0x00 1: Set GPIO interrupt. Auto clear after 2 cycles. - Page 119 UM10858 NXP Semiconductors PN7462 family HW user manual The method used to generate the equations for each bit of the new CRC requires 4 steps and depends on the input data width (W) and polynomial width (C). Therefore, each CRC configuration (polynomial width and input data width) requires dedicated equations.

-

Page 120: Lsb And Msb First Functionality

UM10858 NXP Semiconductors PN7462 family HW user manual value (C_prev). Calculate C_new using the previous serial equations as a function of W(n) for each one hot encoded value of C_prev(n): W=0x0; C_prev is one hot encoded: C=4 so the values are 0x1,0x2,0x4,0x8. -

Page 121: Typical Usage Example

UM10858 NXP Semiconductors PN7462 family HW user manual • CRC value is read MSB first on the APB interface Note: The same equations are used for LSB first and for MSB first. A simple serial shift is performed on the input data, preset value and calculated CRC to output the correct CRC value. -

Page 122: Register Overview And Description

UM10858 NXP Semiconductors PN7462 family HW user manual 9.5 Register overview and description 9.5.1 Register overview Table 138. CRC register overview (base address 0x4000 C000) Name Address Width Access Reset value Description offset (bits) CRC_CONTROL_REG 00000000h CRC configuration register CRC_DAT32_REG... - Page 123 UM10858 NXP Semiconductors PN7462 family HW user manual Table 140. CRC_DAT32_REG (address offset 0x04) Symbol Access Value Description 31:0 CRCDAT32 0, 1 for each 32 bits CRC value. Writing to CRCDAT32 triggers a new CRC calculation over a 32 bits written word.

-

Page 124: Random Number Generator

UM10858 NXP Semiconductors PN7462 family HW user manual 10. Random number generator The integrated RNG consists of two main parts: an analog True Random Number Generator (TRNG) connected to a digital Pseudo Random Number Generator (PRNG). The analog TRNG is used to load a new seed into the PRNG. - Page 125 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 24. Block diagram of RNG module 10.2.1 PRNG digital core The module delivers an 8-bit random number. The Pseudo Random Number Generator consists of an 80-bit LFSR with a feedback polynomial and an S-Box substitution for the output of the PRNG.

-

Page 126: Register Overview And Description

UM10858 NXP Semiconductors PN7462 family HW user manual 10.3 Register overview and description 10.3.1 Random number generator register overview Table 145. Random number generator register overview (base address 0x4001 8000) Name Address Width Access Reset value Description offset (bits) RNG_STATUS_REG... -

Page 127: General-Purpose Timers And Watchdog Timers

UM10858 NXP Semiconductors PN7462 family HW user manual 11. General-purpose timers and watchdog timers The PN7462 family includes two 12-bit general purpose timers (on LFO clock domain) with match capabilities two 32-bit general purpose timers (on HFO clock domain) and a Watch Dog Timer (WDT). -

Page 128: Register Overview And Description

UM10858 NXP Semiconductors PN7462 family HW user manual • The watchdog interrupt is connected to the ARM subsystem NMI (non-mask able Interrupt). • The watchdog eventually sends a reset signal to the PCR to reset the chip if the threshold setting is not periodically reloaded by the FW. - Page 129 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) TIMERS_WDOG_INT_SET_STATUS_REG 3FD4h 00000000h Watchdog set interrupt TIMERS_INT_CLR_ENABLE_REG 3FD8h 00000000h Timer clear interrupt enable TIMERS_INT_SET_ENABLE_REG 3FDCh 00000000h Timer set interrupt enable TIMERS_INT_STATUS_REG 3FE0h 00000000h...

- Page 130 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Reset Value Access Type Description TIMER1_MODE 0: single shot 1 - free-running Table 154. TIMERS_TIMER1_TIMEOUT_REG (address offset 0x0010) Symbol Reset Value Access Type Description 31:12 RESERVED Reserved 11:0 TIMER1_TIMEOUT Initial count value of Timer1 in step size of 0.30 ms...

- Page 131 UM10858 NXP Semiconductors PN7462 family HW user manual Table 160. TIMERS_TIMER3_TIMEOUT_REG (address offset 0x0028) Symbol Reset Value Access Type Description 31:0 TIMER3_TIMEOUT Initial count value of Timer3 in step size of 0.30 ms . If set to 0, this feature is disabled.

- Page 132 UM10858 NXP Semiconductors PN7462 family HW user manual Table 166. TIMERS_WDOG_INT_STATUS_REG (address offset 0x3FCC) Symbol Reset Value Access Type Description 31:1 RESERVED reserved WDOG_TIMEOUT_ STATUS Watchdog timeout interrupt status Table 167. TIMERS_WDOG_INT_CLR_STATUS_REG (address offset 0x3FD0) Symbol Reset Value Access Type...

- Page 133 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Reset Access Type Description Value 0: no effect TIMER0_TIMEOUT_SET_ENABLE 1: set enable for Timer0 timeout interrupt 0: no effect Table 171. TIMERS_INT_STATUS_REG (address offset 0x3FE0) Symbol Reset Access Type Description Value...

-

Page 134: Pn7462 Family Contactless Interface

UM10858 NXP Semiconductors PN7462 family HW user manual Table 174. TIMERS_INT_SET_STATUS_REG (address offset 0x3FEC) Symbol Reset Access Type Description Value 31:4 RESERVED reserved TIMER3_TIMEOUT_SET_STATUS 1: set Timer3 timeout interrupt 0: no effect TIMER2_TIMEOUT_SET_STATUS 1: set Timer2 timeout interrupt 0: no effect... -

Page 135: Reader/Writer Modes

UM10858 NXP Semiconductors PN7462 family HW user manual A minimum voltage of 2.3 V enables card emulation, and P2P passive target functionality - in passive load modulation. A voltage above 2.7 V enables the complete contactless functionality. 12.2 Reader/Writer modes 12.2.1 ISO/ IEC14443 type A and Jewel/Topaz PCD modes... - Page 136 UM10858 NXP Semiconductors PN7462 family HW user manual No connection to a host is required to manage the complete ISO/IEC 14443 A protocol. Fig 26 shows the data coding and framing according to ISO/IEC 14443 A. Fig 26. Data coding and framing according to ISO/IEC 14443 A card response The internal CRC coprocessor calculates the CRC value based on the selected protocol.

- Page 137 UM10858 NXP Semiconductors PN7462 family HW user manual Table 176. Communication overview for ISO/IEC 14443 B reader/ writer Communication Signal type Transfer speed direction 106 kbit/s 212 kbit/s 424kbit/s 848 kbit/s Reader to card Reader side 10 % ASK 10 % ASK...

- Page 138 UM10858 NXP Semiconductors PN7462 family HW user manual register TRANSCEIVE_CONTROL_REG in combination with the transmit or the receive command. Unlike for normal operation the receiver is enabled again after a reception is finished. It is necessary to issue the IDLE command in order to leave the RXMultiple cycle. As there is only one receive buffer available but several responses are expected the buffer is split into sub buffers of 32-byte length.

- Page 139 UM10858 NXP Semiconductors PN7462 family HW user manual 3. Erroneous reception - the length byte received indicates a frame length greater than 28. No data is copied to buffer but status byte with LenError bit set is written. 4. Erroneous reception - the length byte is larger than the number of data bytes, which have been received.

-

Page 140: Nfc Modes

UM10858 NXP Semiconductors PN7462 family HW user manual Communication Signal type Transfer speed direction /8192 kbit/s /512 kbit/s 302.08 us Bit length 4.833 ms 13.24 6.62 (6.67) 26.48 52.96 kbit/s kbit/s kbit/s (26.69) kbit/s Card to reader Card side Not supported... - Page 141 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 31. Active communication mode Table 179. Communication overview for active communication mode Communication 106 kbit/s 212 kbit/s 424 kbit/s direction Initiator Target According to ISO/IEC According to FeliCa 8 – 30 % ASK...

- Page 142 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 32. Passive communication mode Table 180. Communication overview for active communication mode Communication 106 kbit/s 212 kbit/s 424 kbit/s direction Initiator Target According to ISO/IEC According to FeliCa 8 – 30 % ASK...

- Page 143 UM10858 NXP Semiconductors PN7462 family HW user manual Communication Signal type Transfer speed direction 106 kbit/s 212 kbit/s 424 kbit/s Bit encoding Manchester BPSK BPSK encoding 12.3.1.5 ISO/IEC14443 B Card operation mode PN7462 family can be also addressed as an ISO/IEC 14443 B card. The following table describes the physical parameters of an ISO/IEC14443 B card mode: Table 182.

- Page 144 UM10858 NXP Semiconductors PN7462 family HW user manual 1. Per default a NFCIP-1 device is in Target mode - meaning its RF field is switched off. 2. The RF level detector is active. 3. Only if it is required by the application the NFCIP-1 device shall switches to Initiator mode.

- Page 145 UM10858 NXP Semiconductors PN7462 family HW user manual 12.3.3.1 General target mode configuration (GTM) Depending on the configuration a certain protocol can be selected/disabled for the card mode detection: • Miller decoder is enabled > TypeA/NFC 106kbps is detected • NRZ decoder is enabled > TypeB 106kbps is detected •...

- Page 146 UM10858 NXP Semiconductors PN7462 family HW user manual 2. Activate Fast-tracking mode a. Set AGC_FAST_MODE_ENABLE = 1 b. Set AGC_FAST_MODE_STEP c. Set AGC_FAST_MODE_DURATION 3. Configure to load the Rx-Divider to nominal value a. Disable the AGC operation by writing “0” to CLIF_AGC_CONFIG0_REG.AGC_MODE_ENABLE.

-

Page 147: Functional Description

UM10858 NXP Semiconductors PN7462 family HW user manual 12.4 Functional Description Fig 33 shows an overview of the Contactless interface. Fig 33. Contactless interface 12.4.1 Clock/Reset Block The Clock/Reset module is the source of all clocks and reset used in the CLIF. - Page 148 UM10858 NXP Semiconductors PN7462 family HW user manual present when the device is within the RF-Field. PLL clock is available as soon as the CLIF PLL is enabled and locked to the input clock. The HFO (high frequency oscillator – 20 MHz nominal) clock is always available as soon systems is active.

- Page 149 UM10858 NXP Semiconductors PN7462 family HW user manual • Decode reader-mode ISO18092 (106 kBd): Manchester decoder (848 kHz subcarrier with load modulation) • Decode reader-mode ISO18092 (212 kBd, 424 kBd: Felica): Manchester decoder (848 kHz subcarrier with load modulation • Decode Felica (212 kBd, 424 kBd): Manchester decoder •...

- Page 150 UM10858 NXP Semiconductors PN7462 family HW user manual 12.4.5 RX-Decoder The Rx-Decoder decodes the bit stream from the signal processing block CLIF SigPro) and performs serial-to-parallel conversion, frame checking (including stop-bit check as well as EOF check) and collision detection. Additionally, the Rx-Decoder handles data integrity checking which means it performs a parity check and hands the received data to the CRC coprocessor for CRC check.

- Page 151 UM10858 NXP Semiconductors PN7462 family HW user manual comply with ISO14443 Type A and B, ISO18092, FeliCa, ISO15693, Jewel, and I-Code EPC-V2 (ISO18000). 12.4.8.1 Functional features • Supports different preset values of the CRC register • Supports 5-bit and 16-bit CRC calculation •...

- Page 152 UM10858 NXP Semiconductors PN7462 family HW user manual 12.4.13 MFC Block The MFC (MIFARE Classic Crypto) block generates the cryptographic data to encipher and decipher data for communication with MIFARE Classic cards and MIFARE Plus cards in SL1. It is supported by a dedicated PRNG.

-

Page 153: Clif Register Overview

UM10858 NXP Semiconductors PN7462 family HW user manual 12.5 CLIF register overview Table 185. CLIF Register overview (base address 0x4000 4000) Name Address Width Access Reset value Description offset (bits) CLIF_CONTROL_REG 0000h 00000000h Main control register for CLIF digital CLIF_CLOCK_CONTROL_REG... - Page 154 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) CLIF_TIMER1_RELOAD_REG 0088h 00000000h CLTimer register CLIF_TIMER2_RELOAD_REG 008Ch 00000000h CLTimer register CLIF_TIMER0_OUTPUT_REG 0090h 00000000h CLTimer register CLIF_TIMER1_OUTPUT_REG 0094h 00000000h CLTimer register CLIF_TIMER2_OUTPUT_REG 0098h 00000000h...

-

Page 155: Register Description

UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) INTERNAL_USE 0124h 00000000h For internal use CLIF_ANA_TX_SHAPE_CONTROL 0128h 00000000h Analog TX shaping control register _REG INTERNAL_USE 012Ch 00000000h For internal use CLIF_ANA_TEST_REG 01FCh... - Page 156 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Note: The transceive command does not finish automatically. It stays in the transceive cycle until stopped via the IDLE/ StopCom command KeepCommand command; This command does not change the...

- Page 157 UM10858 NXP Semiconductors PN7462 family HW user manual Table 188. CLIF_STATUS_REG register (address 0008h) * = reset value Symbol Access Value Description RESERVED reserved DPLL_ENABLE 0*, 1 This bit indicates that the DPLL controller has enabled the DPLL This bit indicates than the AGC has detected the external RF-...

- Page 158 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_ACTIVE 0*, 1 This bit indicates activity of the RXDecoder. If 1 a data reception is ongoing, otherwise the RXDecoder is in idle state. TRANSCEIVE_STATE 0* - 5...

- Page 159 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description INTERNAL_USE 0*, 1 for internal use INITIATOR 0*, 1 Set to 1, the CLIF is configured for initiator mode. Depending on this setting the behavior of the transceive command is...

- Page 160 UM10858 NXP Semiconductors PN7462 family HW user manual Table 193. CLIF_RX_WATERLEVEL_REG register (address 0028h) * = reset value Symbol Access Value Description 31:8 RESERVED Reserved RX_WATERLEVEL 0* - 0xFF Defines a warning level to indicate that RX_WATERLEVEL number of words were already received in the actual frame.

- Page 161 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Note: Bits are skipped at the end of the byte 11:9 TX_FIRST_BITS 0*- 7 Defines how many bits of the first data byte to be sent. If set to 000b all bits of the last data byte are sent.

- Page 162 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 212 kHz 424 kHz 848 kHz Table 197. CLIF_TX_FRAME_CONFIG_REG register (address 0038h) * = reset value Symbol Access Value Description 31:19 RESERVED Reserved 18:16 TX_DATA_CODE_T 0*- 7 Specifies the type of encoding of data to be used...

- Page 163 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description If set to 1, transmission of data is enabled otherwise only TX_DATA_ENABLE symbols are transmitted. Defines which pattern symbol is sent as frame TX_STOP_SYMBOL R/W 0*- 3h stop-symbol...

- Page 164 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description TX_S01_INV_ENV 0*, 1 If set to 1, the output envelope is inverted. TX_S01_ENV_TYPE R/W 0*, 7 Specifies the type of envelope used for transmission of data packets. The selected envelope type is applied to the pseudo bit stream.

- Page 165 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Direct output Manchester code Manchester code with subcarrier BPSK RZ (pulse of half bit length at beginning of second half of bit) RZ (pulse of half bit length at beginning of bit)

- Page 166 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description TX_UNDERSHOOT_ 0* - 1 This mode activates the undershoot prevention circuit only PROT_LAST_SC_E for the last sub-carrier cycle for card-mode transmission. NABLE Note: The bit TX_UNDERSHOOT_PROT_ENABLE must not be set for this mode.

- Page 167 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_PARITY_ERR_8 0*, 1 If set, parity error is detected when only 8 bits in last byte BITS_E NABLE received 18:16 RX_BIT_ALIGN 0* - 7h RxAlign defines the bit position within the byte for the first bit received.

- Page 168 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Odd parity calculation is used RX_PARITY_ENABL 0*, 1 If set to 1, a parity-bit for each byte is expected, will be extracted from data stream and checked for correctness. In case the parity-bit is incorrect, the RX_DATA_INTEGRITY_ERROR flag is set.

- Page 169 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_DATA_INTEGRI 0*, 1 This flag is set to 1, if a data integrity error has been TY_ERROR detected. Possible caused can be a wrong parity or a wrong CRC.

- Page 170 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_CRC_INV 0, 1 Controls the comparison of the CRC checksum for the Rx-Decoder Not inverted CRC value: 0000h, reset value Note: That this nit is cleared by the Mode detector for ISO14443 type A and FeliCa.

- Page 171 UM10858 NXP Semiconductors PN7462 family HW user manual Table 209. CLIF_TIMER0_CONFIG_REG register (address 0078h) * = reset value Symbol Access Value Description T0_STOP_ON_T3_E 0*, 1 T0_STOP_EVENT: If set the timer T0 is stopped when timer XPIRED T3 raises its expiration flag.

- Page 172 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 3.39 MHz counter 1.70 MHz counter 848 kHz counter 424 kHz counter 212 kHz counter 106 kHz counter 53 kHz counter T0_MODE_SEL 0 – 1 Configuration of the timer T0 clock.

- Page 173 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description T1_START_ON_RX_ 0*, 1 T1_START_EVENT: If set, the timer T1 is started when a STARTED data reception begins (1st bit is received). T1_START_ON_RX_ 0*, 1 T1_START_EVENT: If set, the timer T1 is started when a ENDED data reception ends.

- Page 174 UM10858 NXP Semiconductors PN7462 family HW user manual Table 211. CLIF_TIMER2_CONFIG_REG register (address 0080h) * = reset value Symbol Access Value Description T2_STOP_ON_T3_E 0*, 1 T2_STOP_EVENT: If set the timer T2 is stopped when timer XPIRED T3 raises its expiration flag.

- Page 175 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 3.39 MHz counter 1.70 MHz counter 848 kHz counter 424 kHz counter 212 kHz counter 106 kHz counter 53 kHz counter T2_MODE_SEL 0 – 1 Configuration of the timer T2 clock.

- Page 176 UM10858 NXP Semiconductors PN7462 family HW user manual Table 215. CLIF_TIMER0_OUTPUT_REG register (address 0090h) * = reset value Symbol Access Value Description 31:25 RESERVED Reserved T0_RUNNING 0*, 1 Indicates that timer T0 is running (busy) 23:20 RESERVED Reserved 19:0 T0_VALUE...

- Page 177 UM10858 NXP Semiconductors PN7462 family HW user manual Table 219. CLIF_SIGPRO_RM_CONFIG1_REG register (address 00B4h) * = reset value Symbol Access Value Description 31:25 RESERVED Reserved DYNAMIC_BPSK_T 0-1* If set to 1 the threshold for BPSK demodulation is H_ENABLE dynamically adapted while reception.

- Page 178 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description SYNC_HIGH 0* - 1 Defines if the bit grid is fixed at maximum (1) or at a minimum (0) value of the correlation. 0*-1 If set to 1, the demodulation scheme is FSK.

- Page 179 UM10858 NXP Semiconductors PN7462 family HW user manual Table 222. CLIF_AGC_INPUT_REG register (address 00D4h) * = reset value Symbol Access Value Description 31:10 RESERVED Reserved 25:16 AGC_RM_VALUE 0*-3FFh Static AGC value used for reader mode CLIF_AGC_CONFIG0_REG.AGC_INPUT_SEL = 1 & CLIF_AGC_CONFIG0_REG.MODE_SEL = 0 Most sensitive: largest Rx-resistor, i.e., none of the...

- Page 180 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description INTERNAL_USE For internal use INTERNAL_USE 14:13 0*, 3 For internal use INTERNAL_USE 0*, 1 For internal use INTERNAL_USE For internal use INTERNAL_USE 0*, 1 For internal use INTERNAL_USE...

- Page 181 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description INTERNAL_USE 0*, 1 For internal use INTERNAL_USE 0*, 1 For internal use INTERNAL_USE 0*, 1 For internal use INTERNAL_USE 0*, 1 For internal use INTERNAL_USE 0*, 1 For internal use...

- Page 182 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description if 1 -> TX output is inverted (clk_13m56_n is used); 0 TX2_INV_CM 0*, 1 -> clk_13m56 is used if 1 -> TX output is inverted (clk_13m56_n is used); 0...

- Page 183 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description TX_CW_TO_MAX_R 0* - 1h TX HI output is the maximum voltage obtainable from charge pump (RM setting); if set to 1 -> TX_CW_AMPLITUDE_RM is overruled. TX_CW_TO_MAX_A 0-1*h TX HI output is the maximum voltage obtainable from charge LM_CM pump (CM setting);...

- Page 184 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 50 % 65 % 80 % 11:10 CM_MILLER_TAU 0h – 3h Configuration bits for the time constant of the reference generation in Miller demodulator 8 µs (cap of 125 f) 2 µs (cap of 500 f)

- Page 185 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description Note that the phase settings can be refined (on top of this configuration) in 5°C steps using CLIF_DPLL_INIT_REG. DPLL_CLOCK_CONFIG_ALM. 0 °C 45 °C 90 °C 135 °C 180 °C 225 °C...

- Page 186 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RESERVED 0*, 1 Reserved 22:19 TX_SET_ILOAD 0h-Fh, Ah* settings for set_iload and corresponding assumed load current in the output path 18:13 RESERVED 0h*-3Fh Reserved 12:7 RESERVED 0h*-3Fh Reserved...

- Page 187 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description 17:16 INTERNAL_USE 0*-3h For internal use Proportional: 2^(-3) and Integral: 2^(-20) Proportional: 2^(-4) and Integral: 2^(-21) Proportional: 2^(-5) and Integral: 2^(-22) Proportional: 2^(-6) and Integral: 2^(-23) 15:14 RESERVED...

- Page 188 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_SC_DET_IRQ_CLR_ENA 0, 1 Writing 1 to this register does clear the corresponding IRQ ENABLE flag RX_SOF_DET_IRQ_CLR_EN 0, 1 Writing 1 to this register does clear the corresponding IRQ...

- Page 189 UM10858 NXP Semiconductors PN7462 family HW user manual Table 238. CLIF_INT_SET_ENABLE_REG register (address 3FDCh) * = reset value Symbol Access Value Description 31:30 RESERVED Reserved AGC_RFOFF_DET_ 0, 1 Writing 1 to this register does set the corresponding IRQ IRQ_SET_ENABLE ENABLE flag...

- Page 190 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description STATE_CHANGE_IRQ_SET_ 0, 1 Writing 1 to this register does set the corresponding IRQ ENABLE ENABLE flag CARD_ACTIVATED_IRQ_SE 0, 1 Writing 1 to this register does set the corresponding IRQ...

- Page 191 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_SOF_DET_IRQ 0*, 1 Set to 1 by hardware, when in reader mode an SOF is detected RX_EMD_IRQ 0*, 1 Set to 1 by hardware, when an EMD event is detected...

- Page 192 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_DATA_AV_IRQ_ENABLE R 0*, 1 If this bit is 1 the corresponding IRQ can propagate to the CPUs IRQ controller RX_BUFFER_OVERFLOW_I 0*, 1 If this bit is 1 the corresponding IRQ can propagate to the...

- Page 193 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description IDLE_IRQ_ENABLE 0*, 1 If this bit is 1 the corresponding IRQ can propagate to the CPUs IRQ controller TX_IRQ_ENABLE 0*, 1 If this bit is 1 the corresponding IRQ can propagate to the...

- Page 194 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description TX_RFON_IRQ_CLR_STATU 0*, 1 Writing 1 to this register does clear the corresponding IRQ STATUS flag TX_RFOFF_IRQ_CLR_STATU 0*, 1 Writing 1 to this register does clear the corresponding IRQ...

- Page 195 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Value Description RX_EMD_IRQ_SET_STATUS R 0*, 1 Writing 1 to this register does set the corresponding IRQ STATUS flag TIMER3_IRQ_SET_STATUS 0*, 1 Writing 1 to this register does set the corresponding IRQ...

-

Page 196: Dynamic Power Control (Dpc)

UM10858 NXP Semiconductors PN7462 family HW user manual 12.7 Dynamic Power Control (DPC) 12.7.1 DPC description The Dynamic Power Control allows to adjust the Transmitter output current dependent on the loading condition of the antenna. A lookup table (LUT) is used to configure the output voltage and by this control the transmitter current. - Page 197 UM10858 NXP Semiconductors PN7462 family HW user manual transmitter supply voltage configurations - can be defined by the application, up to 15 gears are available. Fig 35. Transmitter supply voltage configuration, V > 3.5 V DD(TVDD) 12.7.2 DPC EEPROM values Following table (Table 243) shows the EEPROM address, variable name as well as the description and access rights of all DPC values.

- Page 198 UM10858 NXP Semiconductors PN7462 family HW user manual 0x201328 wControlCycle DPC_TIME Sets the value for the periodic regulation. Time base is 1/20 MHz. (Example: Value of 20000 is equal to 1 0x201353 bAgcXi DPC_XI Trim Value of the AGC value...

- Page 199 UM10858 NXP Semiconductors PN7462 family HW user manual 8:11 are not taken into account. 0x20132E wGuardTimeFastMode DPC_GUARD_F Guard time after AGC fast mode has AST_MODE been triggered. This happens in the following scenarios: - End of Receive - End of Transmit...

- Page 200 UM10858 NXP Semiconductors PN7462 family HW user manual 8..11: TAU_MOD_RISIN G (Sign bit + 3-bit value) 12..15: RESIDUAL_CARRI ER (Sign bit + 3-bit value) 16..31: Bitmask identifying technology and baud rate UM10858 All information provided in this document is subject to legal disclaimers.

-

Page 201: Adaptive Waveform Control (Awc)

UM10858 NXP Semiconductors PN7462 family HW user manual 12.8 Adaptive Waveform Control (AWC) Depending on the level of detected detuning of the antenna, RF wave shaping related register settings can be automatically updated. The shaping related register settings are stored in a lookup table located in EEPROM, and selected dependent on the actual gear. - Page 202 UM10858 NXP Semiconductors PN7462 family HW user manual subtracted from the existing configuration. For an increasing gear value, the defined change is cumulative. The PCD shaping LUT (LookUp Table) value is stored beginning at EEPROM address 0x201368. Each value is stored LSB first.

-

Page 203: Pn7462 Family Contact Interface

UM10858 NXP Semiconductors PN7462 family HW user manual 13. PN7462 family Contact interface Note: This chapter only applies to family members with contact and/or ISO7816 interface. The PN7462 family integrates contact interface to enable communication with ISO7816 and EMVCo contact smart cards, without the need for an external contact front end. It offers a high level of security for the cards by performing current limitation, short-circuit detection, ESD protection as well as supply supervision. -

Page 204: Typical Application Schematics

UM10858 NXP Semiconductors PN7462 family HW user manual • Supports the asynchronous protocols T=0 and T=1 in accordance with ISO7816 and • Versatile 24-bit time-out counter for Answer To Reset (ATR) and waiting times processing • Specific Elementary Time Unit (ETU) counter for Block Guard Time (BGT): 22 in T=1 and 16 in T=0 •... - Page 205 UM10858 NXP Semiconductors PN7462 family HW user manual Table 245. Contact Smart card pins – Main slot Pins description for the main contact smart card slot Pin name Pin n° Description Specific requirement VBUSP PN7462 family for the contact Must be > 3 V for Class A cards...

-

Page 206: Specific Blocks

UM10858 NXP Semiconductors PN7462 family HW user manual For more details about the pins and power supply, refer to the PN7462 family datasheet. For deeper description of usage of each pin, please refer to the PN7462 family contact interface application note. - Page 207 UM10858 NXP Semiconductors PN7462 family HW user manual 6. CLK cycles with RST at logic level one, the bit MUTE is set to logic level one. 7. If the card answers within the correct time window, the CLK cycles count is stopped and the application may send commands to the card.

-

Page 208: Connect An External Tda

UM10858 NXP Semiconductors PN7462 family HW user manual − When the micro-controller reads a character, the FIFO size pointer is decremented. − A read operation when the FIFO is empty will not cause any action for the FIFO (size pointer unchanged). In this case, 0 is read. - Page 209 UM10858 NXP Semiconductors PN7462 family HW user manual communicate with two smart cards at the same time as there is only one protocol control block for all cards. The figure below shows an overview of the connections when PN7462 family is used to control several smart cards.

-

Page 210: Registers

UM10858 NXP Semiconductors PN7462 family HW user manual (1) This figure only shows the link between PN7462 family and TDA8026, but is not an application schematic. External components are not showed here. Fig 39. External TDA8026 connection The default PN7462 family FW embeds a SW controlling a TDA8026. - Page 211 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset Description offset (bits) Value ct_gtr1_reg 0010h 00000000h Guard Time Register slot 1 ct_gtr2_reg 0010h 00000000h Guard Time Register slot 2 ct_ucr11_reg 0014h 00000000h UART Configuration Register 1 slot 1...

- Page 212 UM10858 NXP Semiconductors PN7462 family HW user manual Table 248. Register bit overview Name Access Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset value RESERV RESERV RESERV pres con pres pup...

- Page 213 UM10858 NXP Semiconductors PN7462 family HW user manual Name Access Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset value RESERV RESERV RESERV RESERV RESERV INTAUX PRES XXXX X000 usr1 RESERV RESERV...

- Page 214 UM10858 NXP Semiconductors PN7462 family HW user manual SLOT SELECT REGISTER UART STATUS REGISTER 1 TIME-OUT REGISTER 1 UART STATUS REGISTER 2 TIME-OUT REGISTER 2 MIXED STATUS REGISTER TIME-OUT REGISTER 3 FIFO STATUS REGISTER TIME-OUT CONFIGURATION REGISTER UART TRANSMIT REGISTER...

- Page 215 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2 Registers description 13.6.2.1 Register ct_ssr_reg (Slot Select Register) This configuration register enables to select the I/O line used and also to reset the whole Contact UART. Table 249. Ct_ssr_reg (address 0000h) bit description...

- Page 216 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.2 Register ct_pdr1_lsb_reg/ct_pdr2_lsb_reg (Programmable Divider Register Least Significant Byte) This configuration register is the least significant byte of a 16-bit counter used to define the ETU. This register is doubled: ct_pdr1_lsb_reg is dedicated to the full slot and ct_pdr2_lsb_reg is dedicated to the auxiliary slot.

- Page 217 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 41. ETU (and card clock CLK) generation 13.6.2.4 Register ct_fcr_reg (FIFO Control Register) This configuration register defines the FIFO threshold (interrupt signaled by the ft bit of register ct_usr1_reg) and the number of repetition of character in case of Parity Error (interrupt signaled by the pe bit of register ct_usr1_reg).

- Page 218 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value the card. If not, the firmware has the possibility to pursue the transmission. By reading the number of bytes present into the FIFO (ffl bits), it can determine which character has been naked PEC +1 times by the card.

- Page 219 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.6 Register ct_ucr11_reg/ct_ucr12_reg (UART Configuration Register 1) This configuration register defines the reception and transmission settings. This register is doubled: ct_ucr11_reg is dedicated to the full slot and ct_ucr12_reg is dedicated to the auxiliary slot. Both registers share the same address, the selection is done via bit IOauxen of register ct_ssr_reg.

- Page 220 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.7 Register ct_ucr21_reg/ct_ucr22_reg (UART Configuration Register 2) This configuration register defines the reception and transmission settings. This register is doubled: ct_ucr21_reg is dedicated to the full slot and ct_ucr22_reg is dedicated to the auxiliary slot. Both registers share the same address, the selection is done via bit IOauxen of register ct_ssr_reg.

- Page 221 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.8 Register ct_ccr1_reg/ct_ccr2_reg (Clock Configuration Register) This configuration register defines the card clock frequency. This register is doubled: ct_ccr1_reg is dedicated to the full slot (card 1) and ct_ccr2_reg is dedicated to the auxiliary slot (card 2). Both registers share the same address, the selection is done via bit IOauxen of register ct_ssr_reg.

- Page 222 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value ACC2 - ACC0 R/W 000b Asynchronous Card Clock Defines the card clock frequency: • 000: card clock frequency = fclk_ip • 001: card clock frequency = fclk_ip /2 •...

- Page 223 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value WARM When set to logic 1: a warm reset procedure is started. Set to logic 0 by hardware when a START bit is detected or when MUTE bit is set to logic 1.

- Page 224 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value MCL15 – MCL8 R/W 1010 Most significant byte of a programmable 16-bit clock counter (see ATR 0100b counter Functional Description). 13.6.2.13 Register ct_mchr_lsb_reg (Mute card CounteR RST High register Least Significant...

- Page 225 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value Dynamic change (while activated) is not supported. The choice" should be done before activating the card. clk_sr1 - CLK slew rate clk_sr0 Card clock slew rate selection.

- Page 226 UM10858 NXP Semiconductors PN7462 family HW user manual Symbol Access Reset Description Value - In case of word access (bit wrdacc = 1 in register ct_ucr2_reg), 4 bytes are written into the FIFO: UTR31 - UTR24: byte 4 (last byte to transmit)

- Page 227 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.20 Register ct_toc_reg (Time-Out Configuration) This configuration register is used for setting different configurations of the time-out counter as given in Table 269 “Timer settings”; all other configurations are undefined. Table 268. ct_toc_reg (address 0058h) bit description...

- Page 228 UM10858 NXP Semiconductors PN7462 family HW user manual TOC Value Operating Mode count will not be affected and the new count value will be taken into account at the next start bit. An interrupt is given, and bit TO2 is set within register ct_usr2_reg when the terminal count is reached.

- Page 229 UM10858 NXP Semiconductors PN7462 family HW user manual 13.6.2.21 Register ct_fsr_reg (FIFO Status register) This status register enables to know how many bytes are present into the FIFO; it doesn’t generate any interrupt. Table 270. ct_fsr_reg (address 005Ch) bit description...

- Page 230 UM10858 NXP Semiconductors PN7462 family HW user manual Table 272. ct_usr1_reg (address 0064h) bit description Symbol Access Reset Description Value 31:6 RESERVED Reserved During ATR, set to logic 1 when the card has not answered (it has not sent MUTE its ATR) within the time defined by the mute counter while RST was at logic 1 (see registers ct_mcrh_lsb_reg &...

- Page 231 UM10858 NXP Semiconductors PN7462 family HW user manual Remark: When both bits EARLY and MUTE are high, it means that the card answered (sent its ATR) too early between 200 CLK periods after I/O line goes high and before RST goes high.

-

Page 232: Pn7462 Family Interfaces

UM10858 NXP Semiconductors PN7462 family HW user manual 14. PN7462 family Interfaces 14.1 I2C Master Interface The I2C bus is a simple two-wire bi-directional serial communication interface that is intended for inter-IC communication over short distances. The I2C-bus uses only two wires: a serial clock line (SCL) and a serial data line (SDA). - Page 233 UM10858 NXP Semiconductors PN7462 family HW user manual 14.1.2 General description A typical I ²C bus configuration is shown in 42. The master device generates all of the serial clock pulses and the START and STOP conditions. Depending on the state of the direction bit (R/W), two types of data transfers are possible on the I2C-bus: •...

- Page 234 UM10858 NXP Semiconductors PN7462 family HW user manual In the master transmitter mode data is transmitted from master to slave. The first byte transmitted contains the slave address and Write bit. The data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. The I2C Master in Master Transmitter mode supports the automatic continuation of the I2C transmission without the need of altering the data in the FIFO or the register content.

- Page 235 UM10858 NXP Semiconductors PN7462 family HW user manual 14.1.4 TX/RX programming Flowcharts Fig 43. TX programming Flowchart UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018...

- Page 236 UM10858 NXP Semiconductors PN7462 family HW user manual Fig 44. RX programming Flowchart UM10858 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2018. All rights reserved. User manual Rev. 1.4 — 14 May 2018...

- Page 237 UM10858 NXP Semiconductors PN7462 family HW user manual 14.1.5 Baud rate calculation The SCL (serial clock line) frequency calculation is based on 27.12 MHz clock. The BAUDRATE_REG register (see Table 277) controls the speed of the I2C bus transmissions. The SCL (serial clock) line frequency is determined as follows.

- Page 238 UM10858 NXP Semiconductors PN7462 family HW user manual 14.1.7 External wiring The I2C controller operates on an external clock. For proper operation, external blocks must supply a clock signal to the apb_clk pin. Furthermore, as can be seen in 45, the analog characteristics of the I2C bus (data and clock are connected to pull-up resistors) cause that the SCL and SDA lines must be driven by a pull-down circuit also called “I2C”.

- Page 239 UM10858 NXP Semiconductors PN7462 family HW user manual Name Address Width Access Reset value Description offset (bits) BYTECOUNT_STATUS_REG 0x0018 0x00000000 Register bit field to indicate the status of number of bytes transmitted or received STATUS_REG 0x001C 0x0000002C Register bit fields to indicate the current status...

- Page 240 UM10858 NXP Semiconductors PN7462 family HW user manual 14.1.9 Register description 14.1.9.1 CONFIG_REG This register is used to configure the I2C master. Table 276. CONFIG_REG (address offset 0x0000) Legend: * reset value; <= mandatory value Symbol Access Value Description 31:5...