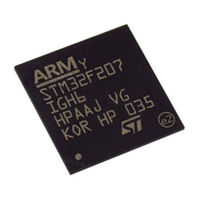

ST STM32F207 series Manuals

Manuals and User Guides for ST STM32F207 series. We have 3 ST STM32F207 series manuals available for free PDF download: Reference Manual, Programming Manual

ST STM32F207 series Reference Manual (1378 pages)

advanced Arm-based 32-bit MCUs

Brand: ST

|

Category: Microcontrollers

|

Size: 17 MB

Table of Contents

-

-

Memory Map51

-

Bit Banding54

-

-

-

-

Sleep Mode73

-

Stop Mode74

-

Standby Mode76

-

-

-

-

SYSCFG Registers159

-

-

(Syscfg_Exticr1)160

-

-

-

(Syscfg_Exticr2)161

-

(Syscfg_Exticr3)161

-

(Syscfg_Exticr4)162

-

-

-

EXTI Registers172

-

-

DMA Introduction176

-

-

DMA Transactions179

-

Arbiter181

-

DMA Streams181

-

Circular Mode186

-

Fifo190

-

Flow Controller194

-

Error Management196

-

DMA Interrupts197

-

DMA Registers198

-

DMA Register Map208

-

-

-

ADC Introduction212

-

-

ADC Clock214

-

Analog Watchdog216

-

Timing Diagram216

-

Scan Mode217

-

Data Alignment220

-

Data Management224

-

Multi ADC Mode225

-

Interleaved Mode231

-

ADC Interrupts238

-

ADC Registers239

-

-

(Adc_Cdr)253

-

-

-

-

DAC Introduction256

-

-

DAC Data Format258

-

DAC Conversion259

-

DMA Request261

-

Noise Generation261

-

-

DAC Registers268

-

-

(Dac_Dhr12L1)272

-

-

-

(Dac_Dhr12L2)273

-

-

-

(Dac_Dhr12Ld)274

-

-

DAC Register Map276

-

-

-

DCMI Pins278

-

DCMI Clocks278

-

-

DMA Interface280

-

Synchronization282

-

Capture Modes285

-

Crop Feature286

-

Fifo288

-

JPEG Format288

-

DCMI Interrupts290

-

Advertisement

ST STM32F207 series Reference Manual (1381 pages)

Advanced Arm-based 32-bit MCUs

Brand: ST

|

Category: Microcontrollers

|

Size: 18 MB

Table of Contents

-

-

Glossary46

-

S0: I-Bus49

-

S1: D-Bus49

-

S2: S-Bus49

-

Busmatrix50

-

Memory Map51

-

Bit Banding54

-

Sleep Mode73

-

Stop Mode74

-

Standby Mode76

-

Reset84

-

System Reset84

-

Power Reset85

-

Clocks86

-

HSE Clock88

-

HSI Clock89

-

LSE Clock90

-

LSI Clock91

-

RCC Register Map135

-

Port Pins148

-

(X = a151

-

GPIO Registers151

-

(X = a152

-

(X = a154

-

(X = a156

-

SYSCFG Registers159

-

(Syscfg_Exticr1)160

-

(Syscfg_Exticr2)161

-

(Syscfg_Exticr3)161

-

(Syscfg_Exticr4)162

-

NVIC Features164

-

EXTI Registers172

-

DMA Introduction176

-

DMA Transactions179

-

Arbiter181

-

DMA Streams181

-

Circular Mode186

-

Fifo190

-

Flow Controller194

-

Error Management196

-

DMA Interrupts197

-

DMA Registers198

-

DMA Register Map208

-

ADC Introduction212

-

ADC Clock214

-

Analog Watchdog216

-

Timing Diagram216

-

Scan Mode217

-

Data Alignment220

-

Data Management224

-

Using the DMA224

-

Multi ADC Mode225

-

Interleaved Mode231

-

ADC Interrupts238

-

ADC Registers239

-

(Adc_Cdr)253

-

DAC Introduction256

-

DAC Data Format258

-

DAC Conversion259

-

DMA Request261

-

Noise Generation261

-

DAC Registers268

-

(Dac_Dhr12L1)272

-

(Dac_Dhr12L2)273

-

(Dac_Dhr12Ld)274

-

DAC Register Map276

-

DCMI Clocks278

-

DCMI Pins278

-

DMA Interface280

-

Synchronization282

-

Capture Modes285

-

Crop Feature286

-

Data Formats288

-

Fifo288

-

JPEG Format288

-

RGB Format289

-

Ycbcr Format289

-

DCMI Interrupts290

-

Time-Base Unit306

-

Counter Modes308

-

Clock Selection319

-

PWM Input Mode326

-

PWM Mode328

-

One-Pulse Mode338

-

Debug Mode347

-

Time-Base Unit378

-

Counter Modes379

-

Clock Selection389

-

PWM Input Mode395

-

PWM Mode397

-

One-Pulse Mode400

-

Debug Mode413

-

Time-Base Unit440

-

Counter Modes442

-

Clock Selection445

-

PWM Mode452

-

One-Pulse Mode453

-

Debug Mode458

-

Time-Base Unit485

-

Counting Mode487

-

Clock Source489

-

Debug Mode490

-

Debug Mode497

-

IWDG Registers498

-

Debug Mode504

-

Table 71. Table504

-

WWDG Registers505

-

Data Type522

-

CRYP Busy State526

-

Context Swapping528

-

CRYP Interrupts530

-

CRYP Registers531

-

RNG Introduction544

-

Error Management545

-

Operation545

-

RNG Registers545

-

RNG Register Map548

-

Data Type552

-

Message Padding555

-

Hash Operation556

-

HMAC Operation556

-

Context Swapping557

-

HASH Interrupt558

-

HASH Registers559

-

Introduction570

-

Tamper Detection579

-

Alarm Output581

-

RTC Interrupts581

-

RTC Registers583

-

(Rtc_Tafcr)595

-

RTC Register Map596

-

Mode Selection599

-

I2C Slave Mode601

-

I2C Master Mode604

-

Error Conditions609

-

Smbus610

-

DMA Requests613

-

I 2 C Interrupts615

-

I 2 C Debug Mode617

-

I 2 C Registers617

-

I2C Register Map629

-

Transmitter635

-

Receiver638

-

Parity Control654

-

Smartcard660

-

USART Interrupts669

-

USART Registers670

-

SPI Introduction682

-

SPI Features683

-

I 2 S Features684

-

CRC Calculation700

-

Status Flags702

-

Error Flags706

-

SPI Interrupts707

-

Figure 269. I711

-

Clock Generator716

-

Figure 283. I717

-

I 2 S Slave Mode720

-

Status Flags722

-

Error Flags723

-

I 2 S Interrupts723

-

Table 101. I723

-

DMA Features724

-

Mode)730

-

SPI Register Map734

-

SDIO Adapter739

-

Card Reset750

-

Block Write752

-

Block Read753

-

SD I/O Mode765

-

R1B770

-

Response Formats770

-

R4 (Fast I/O)771

-

R4B772

-

SDIO Interrupts774

-

Aborting CMD61775

-

CE-ATA Interrupt775

-

HW Flow Control776

-

SDIO Registers776

-

SDIO Response 1780

-

Tx Mailboxes794

-

Normal Mode796

-

Silent Mode797

-

Test Mode797

-

Loop Back Mode798

-

Debug Mode799

-

Message Storage807

-

Bit Timing809

-

Error Management809

-

Bxcan Interrupts811

-

CAN Registers813

-

DMA Controller838

-

DMA Features840

-

PTP Features840

-

Ethernet Pins841

-

MAC Interrupts866

-

MAC Filtering867

-

DMA Arbiter883

-

DMA Interrupts906

-

General Features958

-

OTG Pins960

-

USB Peripheral963

-

USB Host967

-

SRP-Capable Host968

-

USB Host States968

-

Host Channels970

-

Host Scheduler971

-

Host Sofs972

-

SOF Trigger972

-

Peripheral Sofs973

-

USB Data Fifos975

-

Host Rx FIFO977

-

Device Mode978

-

Host Tx Fifos978

-

Host Mode979

-

CSR Memory Map983

-

Host-Mode Registers1009

-

(Otg_Fs_Pcgcctl)1042

-

OTG_FS Register Map1043

-

Core Initialization1052

-

Host Initialization1053

-

Operational Model1072

-

OTG_HS Introduction1098

-

OTG_HS Main Features1098

-

General Features1099

-

Host-Mode Features1100

-

High-Speed OTG PHY1101

-

OTG Pins1101

-

HNP Dual Role Device1102

-

ID Line Detection1102

-

OTG Dual-Role Device1102

-

SRP Dual-Role Device1103

-

Peripheral States1104

-

Peripheral Endpoints1105

-

SRP-Capable Host1108

-

USB Host States1109

-

Host Channels1110

-

Host Scheduler1112

-

Host Sofs1113

-

Peripheral Sofs1113

-

SOF Trigger1113

-

FIFO RAM Allocation1116

-

Host Mode1116

-

Peripheral Mode1116

-

OTG_HS Interrupts1117

-

CSR Memory Map1119

-

Host-Mode Registers1147

-

(Otg_Hs_Pcgcctl)1189

-

OTG_HS Register Map1189

-

Core Initialization1204

-

Host Initialization1205

-

DMA Mode1206

-

Operational Model1234

-

FSMC Main Features1261

-

AHB Interface1262

-

Block Diagram1262

-

General Timing Rules1270

ST STM32F207 series Programming Manual (29 pages)

Brand: ST

|

Category: Microcontrollers

|

Size: 0 MB

Table of Contents

-

Glossary

5 -

-

Option Bytes14

-

Advertisement

Advertisement