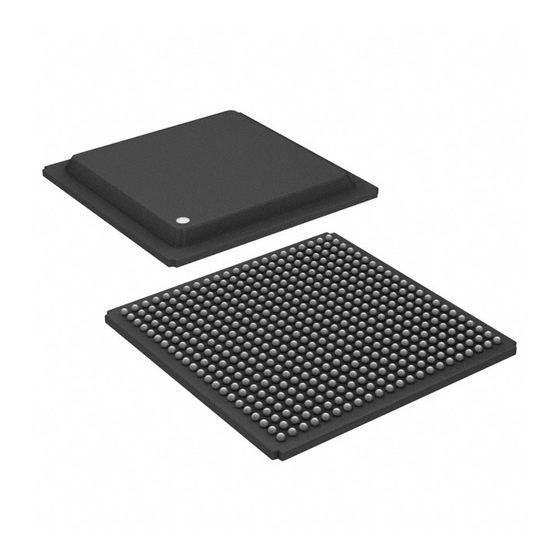

Analog Devices ADSP-TS101 TigerSHARC Manuals

Manuals and User Guides for Analog Devices ADSP-TS101 TigerSHARC. We have 1 Analog Devices ADSP-TS101 TigerSHARC manual available for free PDF download: Hardware Reference Manual

Analog Devices ADSP-TS101 TigerSHARC Hardware Reference Manual (410 pages)

Brand: Analog Devices

|

Category: Computer Hardware

|

Size: 10 MB

Table of Contents

Advertisement

Advertisement

Related Products

- Analog Devices TigerSHARC ADSP-TS201S

- Analog Devices ADSP-21262 SHARC

- Analog Devices ADSP-21267 SHARC

- Analog Devices adsp-2100

- Analog Devices SHARC ADSP-21065L

- Analog Devices SHARC ADSP-21369

- Analog Devices SHARC ADSP-21486

- Analog Devices Blackfin ADSP-BF533

- Analog Devices Blackfin ADSP-BF536

- Analog Devices Blackfin ADSP-BF549