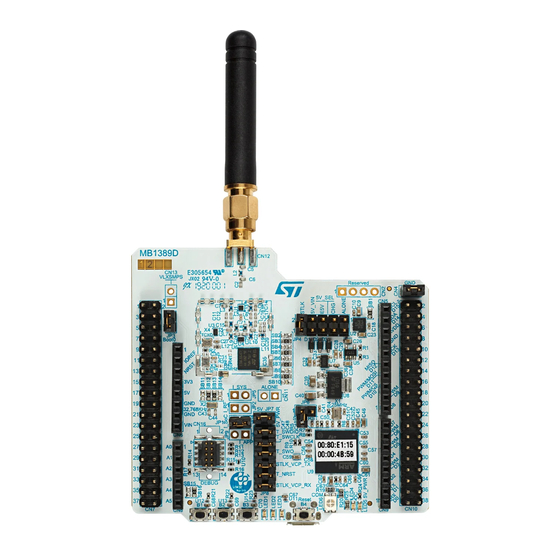

STMicroelectronics STM32WL5 Series MCU Manuals

Manuals and User Guides for STMicroelectronics STM32WL5 Series MCU. We have 1 STMicroelectronics STM32WL5 Series MCU manual available for free PDF download: Reference Manual

STMicroelectronics STM32WL5 Series Reference Manual (1450 pages)

Advanced Arm-based 32-bit MCUs with Sub-GHz Radio Solution

Brand: STMicroelectronics

|

Category: Microcontrollers

|

Size: 28 MB

Table of Contents

-

-

Glossary60

-

CPU2 Boot65

-

SRAM Erase66

-

Introduction71

-

Interrupts85

-

Empty Check99

-

Introduction117

-

RSSLIB Functions117

-

FLASH Interrupts127

-

FLASH Registers129

-

(Flash_Ipccbr)144

-

(Flash_Srrvr)150

-

Transmitter157

-

Receiver158

-

Rf-Pll159

-

Lora Modem161

-

Lora Framing163

-

FSK Modem165

-

Generic Framing166

-

MSK Modem166

-

BPSK Modem168

-

BPSK Framing169

-

Calibration Mode172

-

Sleep Mode172

-

Startup Mode172

-

Standby Mode173

-

(Subghz_Paocpr)221

-

Power Supplies228

-

CPU2 Boot239

-

Low-Power Modes241

-

Run Mode249

-

Table 47. Lprun250

-

Sleep Mode252

-

Stop 0 Mode254

-

Stop 1 Mode256

-

Stop 2 Mode257

-

Standby Mode259

-

Shutdown Mode261

-

PWR Registers263

-

PWR Register Map283

-

Power Reset286

-

Reset286

-

System Reset286

-

Clocks288

-

PKA SRAM Reset288

-

HSI16 Clock294

-

MSI Clock294

-

Pll295

-

LSE Clock296

-

LSI Clock297

-

SPI2S2 Clock299

-

ADC Clock300

-

RTC Clock300

-

Timer Clock300

-

True RNG Clock301

-

Watchdog Clock301

-

Preloaded)900

-

(Tim16/17)932

-

IDLE = 50 Μs)1086

-

(M Bits = 00)1144

-

(M Bits = 01)1145

-

(M Bits = 00)1146

-

FIFO Disabled)1162

-

FIFO Disabled)1226

-

Figure 368. I1284

Advertisement

Advertisement

Related Products

- STMicroelectronics STM32WLEx

- STMicroelectronics STM32WL55 Series

- STMicroelectronics STM32WL54 Series

- STMicroelectronics STM32L151UCY6

- STMicroelectronics STM32L152QCH6

- STMicroelectronics STM32F469I-DISCO

- STMicroelectronics STM32F050F4

- STMicroelectronics STM32F050K4

- STMicroelectronics STM32F050G6

- STMicroelectronics STM32L151QCH6