Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Analog Devices SHARC ADSP-2136 Series

- Page 1 ADSP-2136x SHARC Processor ® Hardware Reference Includes ADSP-21362, ADSP-21363, ADSP-21364, ADSP-21365, ADSP-21366 Revision 2.0, June 2009 Part Number 82-000501-01 Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106 www.BDTIC.com/ADI...

- Page 2 Analog Devices, Inc. Printed in the USA. Disclaimer Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use;...

-

Page 3: Table Of Contents

CONTENTS PREFACE Purpose of This Manual ............... xxxi Intended Audience ............... xxxi Manual Contents ................ xxxii What’s New in This Manual ............xxxiv Technical or Customer Support ..........xxxvi Supported Processors ..............xxxvii Product Information ..............xxxvii MyAnalog.com ..............xxxviii Processor Product Information .......... - Page 4 Contents INTRODUCTION ADSP-2136x SHARC Design Advantages ........1-1 SHARC Family Product Offerings ........... 1-5 Processor Architectural Overview ..........1-6 Processor Core ................ 1-7 Processor Peripherals ............... 1-7 I/O Processor ..............1-7 Digital Applications Interface (DAI) ........1-9 Development Tools ..............1-10 Architecture Enhancements ............

- Page 5 Contents DMA Channel Allocation ............. 2-10 DMA Channel Priority ............... 2-11 DMA Channel Arbitration Modes ......... 2-14 Peripheral DMA Bus ............2-14 Rotating Priority by Group ............ 2-15 DMA Channel Interrupts ............2-16 Internal Transfer Completion ..........2-16 DMA Channel Interrupt Priorities ......... 2-16 Interrupt Versus Channel Priorities ........

- Page 6 Contents TCB Storage ................2-30 Serial Port TCB ..............2-30 Parallel Port TCB ..............2-30 SPI TCB ................2-31 I/O Processor Register Access ............2-32 IOP Access Conditions ............2-32 Interrupt Latency ............. 2-33 TCB Chain Loading Access ........... 2-34 IOP Register Access Arbitration ..........

- Page 7 Contents Functional Description ............4-4 Multiplexed Operation ............4-4 Address Cycles ..............4-4 Data Cycles ................. 4-5 Data Buffers ................4-6 Read Path ................4-6 Write Path ................4-7 Operation Modes ..............4-8 8-Bit Mode ................. 4-8 16-Bit Mode ............... 4-9 Parallel Port Registers ..............

- Page 8 Contents Core-Stall Driven Transfers ..........4-17 Interrupts ................... 4-18 DMA Interrupts ..............4-19 Core Interrupts ..............4-19 Throughput ................4-19 8-Bit Access ................4-20 16-Bit Access ................ 4-21 8-Bit Versus 16-Bit SRAM Modes ......... 4-22 Parallel Port Effect Latency ............ 4-23 Programming Model ..............

- Page 9 Contents Miscellaneous Buffers ............5-12 Signal Routing Matrix by Groups ........... 5-13 DAI Group Routing .............. 5-14 Rules for SRU Connections ........... 5-16 Making SRU Connections ............. 5-16 Routing Capabilities .............. 5-20 Default Routing ................5-21 Interrupt Controller ..............5-24 System versus Exception Interrupts ........

- Page 10 Contents SRU SPORT Receive Master ........... 6-7 SRU SPORT Signal Integrity ..........6-7 Functional Description ..............6-9 Registers ..................6-10 Control Registers (SPCTLx) ..........6-12 Multichannel Control Registers (SPMCTLxy) ....... 6-12 Data Buffers ................. 6-13 Transmit Buffers (TXSPxA/B) ........... 6-13 Transmit Path ...............

- Page 11 Contents Master Clock ..............6-25 Master Frame Sync ............6-26 Slave Mode ............... 6-26 Clock Source (ICLK, MSTR) ..........6-27 Sampling Edge (CKRE) ............6-27 Frame Sync Options ..............6-28 Framed Versus Unframed Frame Syncs ........6-28 Internal Versus External Frame Syncs (IFS, IMFS, MSTR) ............

- Page 12 Contents Selecting Transmit and Receive Channel Order (L_FIRST) ..............6-39 Multichannel Operation ............6-40 Frame Syncs Signals ............6-42 Transmit Valid Signals ............6-43 Multichannel Mode Control Bits ........6-44 Number of Channels (NCH) ..........6-45 Frame Delay (MFD) ............6-45 Channel Selection Registers ...........

- Page 13 Contents Buffer Hang Disable (BHD) ..........6-55 Effect Latency ............... 6-55 Programming Model ..............6-56 Setting Up and Starting Chained DMA ........6-56 Enter DMA Chain Insertion Mode ........6-57 Programming Examples ............... 6-57 SERIAL PERIPHERAL INTERFACE PORTS Features ..................7-1 Pin Descriptions ................

- Page 14 Contents Status Register (SPISTATx) ........... 7-18 Multi Master Error (MME) ..........7-19 Transmission Error Bit (TUNF) ........7-20 Reception Error Bit (ROVF) ..........7-20 Transmit Collision Error Bit (TXCOL) ......7-20 BAUD Rate Register (SPIBAUDx) ........7-21 DMA Control Register (SPIDMACx) ........7-21 Data Transfer Types ..............

- Page 15 Contents Loopback Routing ............7-33 Programming Model ..............7-33 Master Mode Core Transfers ..........7-33 Slave Mode Core Transfers ............. 7-35 Master Mode DMA Transfers ..........7-36 Slave Mode DMA Transfers ........... 7-38 Chained DMA Transfers ............7-39 Stopping Core Transfers ............7-40 Stopping DMA Transfers ............

- Page 16 Contents Pin Descriptions ..............8-11 SRU Programming ............8-12 Register Descriptions ............8-12 Control Register (IDP_PP_CTL) ........8-12 PDAP Data Packing .............. 8-13 Mode 11 (No Packing) ............. 8-13 Mode 10 (Packing by 2) ............ 8-14 Mode 01 (Packing by 3) ............ 8-14 Mode 00 (Packing by 4) ............

- Page 17 Contents Servicing Interrupts ............8-24 Debug Features ................8-24 Buffer Hang Disable .............. 8-25 Shadow Registers ..............8-25 Core FIFO Write ..............8-25 IDP Effect Latency ..............8-26 Programming Model ..............8-26 Setting Miscellaneous Bits ............. 8-26 Starting Core Interrupt-Driven Transfer ......... 8-27 Starting A Standard DMA Transfer ........

- Page 18 Contents Operation ..................9-7 Mode Selection ............... 9-8 Pulse Width Modulation Mode (PWM_OUT) ....9-9 PWM Waveform Generation ......... 9-12 Single-Pulse Generation ..........9-13 Pulse Mode ..............9-13 Pulse Width Count and Capture Mode (WDTH_CAP) ..9-14 External Event Watchdog Mode (EXT_CLK) ....9-17 Interrupts ...................

- Page 19 Contents Operation Modes ................ 10-6 Groups Synchronization ............10-6 PWM Timer ..............10-7 Edge-Aligned Mode ............10-8 Center-Aligned Mode ............10-9 Switching Frequencies ............10-11 Dead Time ................10-12 Duty Cycles ................ 10-13 Duty Cycles and Dead Time ..........10-13 Over-Modulation ............

- Page 20 Contents Pin Descriptions ..............11-3 SRU Programming ..............11-4 Functional Description ............11-5 Input Data Format ..............11-7 Output Data Mode ............... 11-8 Operation Modes ..............11-9 Standalone Mode .............. 11-9 Full Serial Mode ............... 11-9 Register Descriptions ............11-9 Control Register (DITCTL) ..........

- Page 21 Contents Emphasized Audio Data ..........11-19 Single-Channel Double-Frequency Mode ......11-19 Interrupts ................. 11-20 Transmitter Interrupt ............11-20 Receiver Interrupts .............. 11-20 Debug Features ................. 11-21 Loopback Routing ............... 11-21 Programming Model ..............11-21 Programming the Transmitter ..........11-21 Programming the Receiver ........... 11-22 Interrupted Data Streams on the Receiver ......

- Page 22 Contents Control Registers (SRCCTLn) ..........12-11 Data Format ..............12-12 Word Width ..............12-12 Ratio Registesr (SRCRATx) ..........12-13 Operation Modes ..............12-13 TDM Daisy Chain Mode ............ 12-14 TDM Output Daisy Chain ..........12-14 TDM Input Daisy Chain ..........12-15 Bypass Mode ...............

- Page 23 Contents External Trigger Mode ..............13-9 Frame Sync ................. 13-10 Phase Shift ................13-11 Phase Shift Settings ............. 13-11 Pulse Width ................ 13-13 Bypass Mode ............... 13-13 Bypass as a Pass Through ..........13-14 Bypass as a One-Shot ............13-14 Programming Examples .............

- Page 24 Contents Output Clock Generator ............14-9 Core Clock (CCLK) ............14-9 Peripheral Clock (PCLK) ..........14-10 Bypass Clock ..............14-10 Power Savings ..............14-10 Power Supplies ................. 14-11 Power Supply for the PLL ............ 14-11 Power-Up Sequence ..............14-11 Input Clock ................ 14-11 PLL Start-Up ..............

- Page 25 Contents System Components ..............14-26 Supervisory Circuits ............14-26 Designing for High Frequency Operation ........14-28 Other Recommendations and Suggestions ......14-29 Decoupling and Grounding ..........14-29 Oscilloscope Probes ............. 14-30 Recommended Reading ............14-31 Processor Booting ..............14-32 Boot Mechanisms ..............14-32 Booting Process ..............

- Page 26 Contents 8-Bit SPI Packing ............14-46 Kernel Boot Time ............... 14-47 Definition of Terms ............14-48 REGISTERS REFERENCE I/O Processor Registers ..............A-2 Notes on Reading Register Drawings ........A-3 System Control Register (SYSCTL) ......... A-4 Power Management Control Register (PMCTL) ..............A-6 Peripheral Registers ..............

- Page 27 Contents PWM Global Status Register (PWMGSTAT) ....A-24 PWM Control Register (PWMCTLx) ....... A-25 PWM Status Registers (PWMSTATx) ....... A-26 PWM Period Registers (PWMPERIODx) ......A-27 PWM Output Disable Registers (PWMSEGx) ....A-27 PWM Polarity Select Registers (PWMPOLx) ....A-28 PWM Channel Duty Control Registers (PWMAx, PWMBx) ............

- Page 28 Contents Parallel Data Acquisition Port Control Register (IDP_PP_CTL) ............. A-50 Input Data Port FIFO Register (IDP_FIFO) ..... A-53 IDP Status Register (DAI_STAT0) ........A-54 IDP Status Register 1 (DAI_STAT1) ......... A-56 Peripheral Timer Registers ............. A-56 Timer Configuration Registers (TMxCTL) ......A-56 Timer Status Registers (TMxSTAT) ........

- Page 29 Contents Receive Status Register (DIRSTAT) ......A-75 Receive Status Registers for Subframe A (DIRCHANL) ............A-77 Receive Status Registers for Subframe B (DIRCHANR) ............A-77 DAI Interrupt Controller Registers ........A-77 DAI Status Register .............. A-78 Digital Applications Interface Status Register (DAI_STAT) ..............

- Page 30 Contents INTERRUPTS Programmable Interrupt Control Registers ........B-1 Programmable Interrupt Control Register 0 (PICR0) ....B-3 Programmable Interrupt Control Register 1 (PICR1) ....B-4 Programmable Interrupt Control Register 2 (PICR2) ....B-5 Programmable Interrupt Control Register 3 (PICR3) ....B-5 AUDIO FRAME FORMATS Overview ..................

-

Page 31: Preface

ADSP-21362/3/4/5/6 Processors contains information about the peripheral set and I/O properties for these products. These are 32-bit, fixed- and floating-point digital signal processors from Analog Devices for use in computing, communications, and consumer applications. The manual provides information on the processor’s I/O architecture and the operation of the peripherals associated with each model. -

Page 32: Manual Contents

Manual Contents Manual Contents This manual provides detailed information about the ADSP-2136x pro- cessors in the following chapters: • Chapter 1, “Introduction” Provides an architectural overview of the ADSP-2136x SHARC processors. • Chapter 2, “I/O Processor” Describes input/output processor architecture, and provides direct memory access (DMA) procedures for the processor peripherals. - Page 33 Preface • Chapter 8, “Input Data Port” Discusses the function of the input data port (IDP) which provides a low overhead method of routing signal routing unit (SRU) sig- nals back to the core’s memory. • Chapter 9, “Peripheral Timers” The processor processors contain three identical 32-bit timers that can be used to interface with external devices.

-

Page 34: What's New In This Manual

What’s New in This Manual • Appendix A, “Registers Reference” Provides a graphical presentation of all registers and describes the bit usage in each register. • Appendix B “Interrupts” Provides information on the programmable interrupt control regis- ters ( ). These registers allow programs to substitute the PICRx default interrupts for some other interrupt source. - Page 35 Preface Where appropriate, the chapters contain the following informa- tion, presented in this order: • Primary features • Hardware interface (pins) • Basic function of the peripheral • Primary registers used by this peripheral • Basic peripheral operation, including DMA •...

-

Page 36: Technical Or Customer Support

), Mode Mask register ( LIRPTL MMASK Technical or Customer Support You can reach Analog Devices, Inc. Customer Support in the following ways: • Visit the Embedded Processing and DSP products Web site at http://www.analog.com/processors/technicalSupport • E-mail tools questions to processor.tools.support@analog.com... -

Page 37: Supported Processors

Preface Supported Processors The following is the list of Analog Devices, Inc. processors supported in VisualDSP++®. TigerSHARC® (ADSP-TSxxx) Processors The name TigerSHARC refers to a family of floa ting-point and fixed-point [8-bit, 16-bit, and 32-bit] processors. VisualDSP++ currently supports the following TigerSHARC families: ADSP-TS101 and ADSP-TS20x. -

Page 38: Myanalog.com

Product Information MyAnalog.com is a free feature of the Analog Devices Web site that allows MyAnalog.com customization of a Web page to display only the latest information on products you are interested in. You can also choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests. -

Page 39: Related Documents

Preface • Fax questions or requests for information to 1-781-461-3010 (North America) +49-89-76903-157 (Europe) • Access the FTP Web site at ftp ftp.analog.com ftp 137.71.25.69) ftp://ftp.analog.com Related Documents The following publications that describe the ADSP-2136x processor (and related processors) are available online: •... -

Page 40: Online Technical Documentation

Product Information Online Technical Documentation Online documentation comprises the VisualDSP++ Help system, software tools manuals, hardware tools manuals, processor manuals, the Dinkum Abridged C++ library, and Flexible License Manager (FlexLM) network license manager software documentation. You can easily search across the entire VisualDSP++ documentation set for any topic of interest. -

Page 41: Accessing Documentation From Windows

• Double-click any file that is part of the VisualDSP++ documenta- tion set. Using the Windows Start Button • Access VisualDSP++ online Help by clicking the Start button and choosing Programs, Analog Devices, VisualDSP++, and VisualDSP++ Documentation. files by clicking the Start button and choosing • Access the .PDF... -

Page 42: Conventions

Conventions Conventions Text conventions used in this manual are identified and described as follows. Example Description Close command Titles in reference sections indicate the location of an item within the Visu- (File menu) alDSP++ environment’s menu system (for example, the Close command appears on the File menu). - Page 43 Preface Additional conventions, which apply only to specific chapters, may appear throughout this document. ADSP-2136x SHARC Processor Hardware Reference xliii www.BDTIC.com/ADI...

- Page 44 Conventions xliv ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI...

-

Page 45: Adsp-2136X Sharc Design Advantages

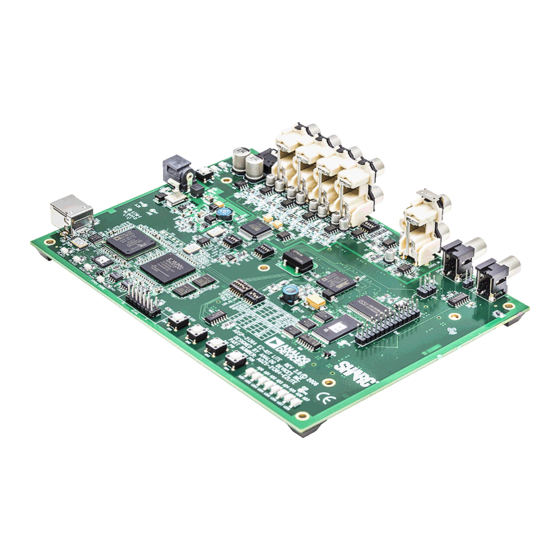

1 INTRODUCTION The ADSP-2136x SHARC processors are high performance 32-bit proces- sors used for high quality audio, medical imaging, communications, military, test equipment, 3D graphics, speech recognition, motor control, imaging, and other applications. By adding on-chip SRAM, integrated I/O peripherals, and an additional processing element for single-instruc- tion, multiple-data (SIMD) support, this processor builds on the ADSP-21000 family DSP core to form a complete system-on-a-chip. - Page 46 ADSP-2136x SHARC Design Advantages a single cycle. The buses and instruction cache provide rapid, unimpeded data flow to the core, thereby maintaining the execution rate. The ADSP-2136x processors contain the following architectural features: • Two processing elements (PEx and PEy), each containing 32-bit IEEE floating-point computation units—multiplier, arithmetic logic unit (ALU), shifter, and data register file.

- Page 47 Introduction Figure 1-1 illustrates a typical single processor system. ADSP-2136 x RE SETOUT CLKIN CLOCK X TAL LATCH AD1 5-0 ADDR CLK_CFG1-0 PARALLEL PORT BOOTCFG1 -0 DATA RAM, ROM FLAG3-1 BOO T ROM I /O DEVI CE FLAG0 (OPTI ONAL) DAI_P1 DAI_ P2 S DAT...

- Page 48 ADSP-2136x SHARC Design Advantages register file, supply two operands to the ALU, supply two operands to the multiplier, and receive three results from the ALU and mul- tiplier. The processor’s 48-bit orthogonal instruction word supports parallel data transfers and arithmetic operations in the same instruction.

-

Page 49: Sharc Family Product Offerings

Introduction • Input data port (IDP). The IDP provides an additional input path to the processor core, configurable as eight channels of serial data or seven channels of serial data and a single channel of up to 20-bit wide parallel data. •... -

Page 50: Processor Architectural Overview

333 MHz 1 The ADSP-21362 and ADSP-21365 processors provide the Digital Transmission Content Pro- tection protocol, a proprietary security protocol. Contact your Analog Devices sales office for more information. 2 Audio decoding algorithms include PCM, Dolby Digital EX, Dolby Prologic IIx, DTS 96/24, Neo:6, DTS ES, MPEG2 AAC, MP3, and functions like Bass management, Delay, Speaker equalization, Graphic equalization, and more. -

Page 51: Processor Core

Introduction Processor Core The processor core of the processor consists of two processing elements (each with three computation units and data register file), a program sequencer, two data address generators, a timer, and an instruction cache. All digital signal processing occurs in the processor core. For complete information, see the SHARC Processor Programming Reference. - Page 52 Processor Architectural Overview associated with it to service the dual serial data pins. Programmable data direction provides greater flexibility for serial communications. Serial port data can automatically transfer to and from on-chip memory using DMA. Each of the serial ports offers a TDM multichannel mode (up to 128 channels) and supports μ-law or A-law companding.

-

Page 53: Digital Applications Interface (Dai)

Introduction ROM-based security. For those processors with application code in the on-chip ROM, an optional ROM securityfeature is included. This feature provides hardware support for securing user software code by preventing unauthorized reading from the enabled code. The processor does not boot-load any external code, executing exclusively from internal ROM. -

Page 54: Development Tools

Development Tools Development Tools The ADSP-2136x processor is supported by VisualDSP++, an easy to use Integrated Development and Debugging Environment (IDDE). VisualDSP++ allows you to manage projects from start to finish from within a single, integrated interface. Because the project development and debug environments are integrated, you can move easily between editing, building, and debugging activities. -

Page 55: I/O Architecture Enhancements

Introduction I/O Architecture Enhancements The I/O processor provides greater throughput than the ADSP-2106x processors. The DMA controller supports 25 channels compared to 14 channels on the ADSP-2116x processor. Instruction Set Enhancements The ADSP-2136x processor provides source code compatibility with the previous SHARC processor family members, to the assembly source code level. - Page 56 Architecture Enhancements 1-12 ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

- Page 57 2 I/O PROCESSOR In applications that use extensive off-chip data I/O, programs may find it beneficial to use a processor resource other than the processor core to per- form data transfers. The ADSP-2136x pro cessor contains an I/O processor (IOP) that supports a variety of DMA (direct memory access) operations. Each DMA operation transfers an entire block of data.

-

Page 58: Dma Controller Operation

DMA Controller Operation The I/O processor runs at CCLK ÷ 2 clock speed. • Internal memory ↔ SPORT (DAI) • Internal memory ← IDP (DAI) unidirectional • Internal memory ↔ SPI • Internal memory ↔ Internal memory (MTM) By managing DMA, the I/O processor frees the processor core, allowing it to perform other operations while off-chip data I/O occurs as a back- ground task. -

Page 59: Dma Transfers Between Internal Memory

I/O Processor An instance where standard DMA can be used is to copy data from a peripheral to internal memory for processor booting. With the help of the loader tool, the tag (header information) of the boot stream is decoded to get the storage information which includes the index, modify, and count of a specific array to start another standard DMA. -

Page 60: General Procedure For Configuring Dma

General Procedure for Configuring DMA General Procedure for Configuring DMA To configure the processors to use DMA, use the following general procedure. 1. Configure the peripheral(s): • Parallel port (PPCTL) • Serial ports (SPORTs) • Serial peripheral interface ports (SPI) •... -

Page 61: Summary

I/O Processor 6. Start the DMA • Set the applicable bits in the appropriate registers. The following sections provide more detailed DMA information for spe- cific peripherals. Summary Because the IOP registers are memory-mapped, the processors have access to program DMA operations. A program sets up a DMA channel by writ- ing the transfer's parameters to the DMA parameter registers. -

Page 62: Standard Dma Parameter Registers

IOP Registers Standard DMA Parameter Registers The parameter registers described below control the source and destina- tion of the data, the size of the data buffer, and the step size used. Index registers. Shown in Table 2-2, provide an internal memory address, acting as a pointer to the next internal memory DMA read or write loca- tion. - Page 63 I/O Processor Table 2-3. Modify Registers Register Name Width (Bits) Description IMSP0–5A SPORTA IMSP0–5B SPORTB IMSPI IMSPIB SPIB IDP_DMA_M0–7 IDP_DMA_M0–7A IDP modify A (ping pong) IDP_DMA_M0–7B IDP modify B (ping pong) IMMTMW MTM Write IMMTMR MTM Read IMPP Parallel Port EMPP Parallel Port (external address) Count registers.

-

Page 64: Standard Dma Status Registers

IOP Registers Chain pointer registers. Shown in Table 2-5, hold the starting address of the TCB (parameter register values) for the next DMA operation on the corresponding channel. These registers also control whether the I/O pro- cessor generates an interrupt when the current DMA process ends. Table 2-5. -

Page 65: Chaining Dma Status Registers

I/O Processor Chaining DMA Status Registers In the registers shown in Table 2-7 Two status bits are available: one for DMA status and one for chain loading DMA status. Table 2-7. Chaining DMA Status Registers Register Name Width (Bits) Description PPCTL Parallel port control SPMCTLxy... -

Page 66: Dma Channel Allocation

IOP Registers Table 2-8. Data Buffers (Cont’d) Buffer Name FIFO Depth Description SPI DMA (DMA only) SPIB DMA (DMA only) IDP_FIFO IDP FIFO Receive MTM read/write DMA only TXPP Parallel Port Transmit RXPP Parallel Port Receive Some data buffers provide debug support to enable the buffer hang disable ) bit. -

Page 67: Dma Channel Priority

I/O Processor DMA channels vary by processormodel. For a breakdown of DMA channels for a particular model, see the ADSP-2136x SHARC Pro- cessor Data Sheet. Also note that each DMA channel has a specific peripheral assigned to it. DMA Channel Priority Table 2-9 shows the paths for internal DMA requests within the I/O processor. - Page 68 DMA Channel Priority Table 2-9. DMA Channel Priorities (Cont’d) Peripheral Control/Status Parameter Data Buffer Description Channel Group Registers Registers Number SPCTL4, IISP4A, IMSP4A, RXSP4A or Serial Port 4A SPMCTL45 CSP4A, CPSP4A TXSP4A Data SPCTL4, IISP4B, IMSP4B, RXSP4B or Serial Port 4B SPMCTL45 CSP4B, CPSP4B TXSP4B...

- Page 69 I/O Processor Table 2-9. DMA Channel Priorities (Cont’d) Peripheral Control/Status Parameter Data Buffer Description Channel Group Registers Registers Number IDP_CTL0, IDP_DMA_I4, IDP_FIFO DAI IDP IDP_CTL1, IDP_DMA_M4, Channel 4 IDP_FIFO, IDP_DMA_C4, DAI_STAT IDP_DMA_I4A, IDP_DMA_I4B, IDP_DMA_PC4 IDP_CTL0, IDP_DMA_I5, IDP_FIFO DAI IDP IDP_CTL1, IDP_DMA_M5, Channel 5 IDP_FIFO,...

-

Page 70: Dma Channel Arbitration Modes

DMA Channel Priority Table 2-9. DMA Channel Priorities (Cont’d) Peripheral Control/Status Parameter Data Buffer Description Channel Group Registers Registers Number MTMCTL IIMTMW, MTM FIFO Memory-to- IMMTMW, memory write CMTMW data MTMCTL IIMTMR, MTM FIFO Memory-to- IMMTMR, memory read CMTMR data DMA Channel Arbitration Modes DMA channel arbitration is the method that the arbiter uses to determine how groups rotate priority with other channels. -

Page 71: Rotating Priority By Group

I/O Processor In the fixed priority scheme, the lower indexed peripheral (Table 2-9) has the highest priority. INTERNAL MEMORY I/F ARBITER IOD BUS PERIPHERAL ARBITER Parallel SPIB SPORT0 SPORT1 Port Figure 2-1. I/O Processor Bus Structure Rotating Priority by Group In the rotating priority scheme, the default priorities at reset are the same as that of the fixed priority. -

Page 72: Dma Channel Interrupts

DMA Channel Priority When none of the peripherals request bus access, the highest priority peripheral, for example, peripheral 0, is granted the bus. However, this does not change the currently assigned priorities to various peripherals. Within a peripheral group, the priority is highest for the higher indexed peripheral (see Table 2-9). -

Page 73: Interrupt Versus Channel Priorities

I/O Processor two interrupts to have priorities that are higher and lower than the serial ports. For more information, see the Program Sequencer “Interrupts and Sequencing” in the SHARC Processor Programming Reference. Interrupt Versus Channel Priorities At default, the DMA interrupt priorities do not match the DMA channel priorities (Table 2-10). -

Page 74: Dma Controller Addressing

DMA Channel Priority DMA Controller Addressing Figure 2-2 shows a block diagram of the I/O processor’s address generator (DMA controller). “Standard DMA Parameter Registers” on page 2-6 lists the parameter registers for each DMA channel. The parameter registers are uninitialized following a processor reset. The I/O processor generates addresses for DMA channels much the same way that the Data Address Generators (DAGs) generate addresses for data memory accesses. - Page 75 I/O Processor DMA ADDRESS GENERATOR (INTERNAL ADDRESSES) LOCAL BUS INTERNAL MEMORY MODIFIER INDEX (ADDRESS) ADDRESS POST-MODIFY DMA WORD COUNTER LOCAL BUS – 1 COUNT CHAIN POINTER WORKING REGISTER DMA ADDRESS GENERATOR (EXTERNAL ADDRESSES) LOCAL BUS EXTERNAL EIPP EMPP ECPP MEMORY EXT.

-

Page 76: Dma Chaining

DMA Chaining • If the I/O processor modifies the internal index register past the maximum 19-bit value to indicate an address out of internal mem- ory, the index wraps around to zero. With the offset for the SHARC processor, the wraparound address is 0x80000. •... -

Page 77: Chain Pointer Register

I/O Processor automatically initializes and then begins another DMA transfer when the current DMA transfer is complete. In addition to the standard DMA parameter registers, each DMA channel also has a chain pointer register that points to the next set of DMA parameters stored in the processor’s internal memory. -

Page 78: Chain Assignment

DMA Chaining Table 2-12. Chain Pointer Register for SPORTs, SPI, Parallel Port (xCPx) Name Description 18–0 IIx address Next chain pointer address Program controlled interrupt 0 = no interrupt after current TCB 1 = interrupt after current TCB Bit 19 of the chain pointer register is the program controlled interrupt ) bit. - Page 79 I/O Processor T C B 1 TC B 2 I I x I I x I M x I M x If pointing to zero, C P x C P x chain operation ends Figure 2-3. Chaining in the SPI and Serial Ports The address field of the chain pointer registers is only 19 bits wide.

-

Page 80: Starting Chain Loading

DMA Chaining Chained DMA operations may only occur within the same chan- nel. The processor does not support cross-channel chaining. Starting Chain Loading A DMA sequence is defined as the sum of the DMA transfers for a single channel, from when the parameter registers initialize to when the count register decrements to zero. -

Page 81: Tcb Chain Loading Priority

I/O Processor TCB Chain Loading Priority A TCB chain load request is prioritized like all DMA channels. Therefore, the TCB chain loading request has the same priority level as the DMA channel itself. The I/O processor latches a TCB loading request and holds it until the load request has the highest priority. -

Page 82: Configuring Iop/Core Interaction

Configuring IOP/Core Interaction A DMA sequence starts when one of the following occurs. • Chaining is disabled, and the DMA enable bit transitions from low to high. • Chaining is enabled, DMA is enabled, and the chain pointer regis- ter address field is written with a non zero value. In this case, TCB chain loading of the channel parameter registers occurs first. -

Page 83: Interrupt-Driven I/O

I/O Processor Interrupt-Driven I/O Programs can check the appropriate status register (for example SPCTL the serial ports) to determine which channels are performing a DMA or chained DMA. All DMA channels can be active or inactive. If a channel is active, a DMA is in progress on that channel. -

Page 84: Polling Dma Channel Status

Configuring IOP/Core Interaction processor latches into the , and IRPTL LIRPTL DAI_IRPTL_H DAI_IRPTL_L registers. The I/O processor only generates a DMA complete interrupt when the channel’s count register decrements to zero as a result of actual DMA transfers. Writing zero to a count register does not generate the interrupt. -

Page 85: Standard Dma Status

I/O Processor Because polling uses processor core resources, it is not as efficient as an interrupt-driven system. Also note that polling the DMA sta- tus registers reduces I/O bandwidth (core higher priority like I/O, “IOP Performance” on page 2-35). The DMA controllers in the ADSP-2136x processor maintain the status information of each channel for the different DMA modes in each of the peripherals registers:... -

Page 86: Tcb Storage

TCB Storage TCB Storage This section lists all the different TCB memory allocations used for DMA chaining on the peripherals. Note that all TCBs must be located in inter- nal memory. Serial Port TCB The serial ports support single and chained DMA. Table 2-13 shows the required TCB for chained DMA... -

Page 87: Spi Tcb

I/O Processor Table 2-14. Parallel Port TCBs (Cont’d) Address Register CP[18:0] – 0x4 EIPP External Index CP[18:0] – 0x5 EMPP External Modifier CP[18:0] – 0x6 ECPP External Count For more information on programming DMA, refer to the specific periph- eral chapters. ... -

Page 88: I/O Processor Register Access

I/O Processor Register Access I/O Processor Register Access All of the I/O processor’s registers are memory-mapped, ranging from address 0x0000 0000 to 0x0003 FFFF. IOP Access Conditions The IOP registers are physically located in two clock domains. 1. Core domain ( )—... -

Page 89: Interrupt Latency

I/O Processor The following situations also incur additional stall cycles. 1. Attempting to write to (or read from) a full (or empty) DMA buffer (IDP and SPORT) causes the core to hang indefinitely, unless the (buffer hang disable) bit for that peripheral is set SPCTLx PPCTL IDP_CTL... -

Page 90: Tcb Chain Loading Access

I/O Processor Register Access ISR_Routine: R0 = 0x0; dm(SPICTL) = R0; /* disable SPI */ lcntr=10, do (pc,1) until lce; nop; rti; TCB Chain Loading Access Table 2-17 lists the time required to load a specific TCB from the internal memory into the DMA controller. -

Page 91: Iop Performance

I/O Processor IOP Performance Since the I/O processor controls the I/O bus, the maximum bandwidth is × 32-bit as shown in achieved with Table 2-17. PCLK Table 2-17. I/O Processor TCB Chain Loading Access Chained TCB Type TCB Size Number of Core Cycles SPI DMA, SPORT DMA Parallel Port DMA... - Page 92 I/O Processor Register Access 2-36 ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

-

Page 93: Memory-To-Memory Port Dma

3 MEMORY-TO-MEMORY PORT DMA Table 3-1 and the following list describe the MTM features. Table 3-1. MTM Port Feature Summary Feature Availability Connectivity Multiplexed Pinout SRU DAI Required SRU DAI Default Routing Interrupt Default Routing Yes (P15I) Protocol Master Capable Slave Capable Transmission Simplex Transmission Half Duplex... -

Page 94: Features

Features Table 3-1. MTM Port Feature Summary (Cont’d) Feature Availability Local Memory Clock Operation PCLK Features The memory-to-memory port incorporates: • 2 DMA channels (read and write) • Internal to internal transfers • Data engine for DTCP applications (only for special part numbers) Functional Description The memory-to-memory DMA controller is capable of transferring 64-bit bursts of data between internal memories. -

Page 95: Buffer

Memory-to-Memory Port DMA 64-bit data from one internal memory location to another. This register also allows verification of current DMA status during writes and reads. Buffer bit in the register can be set to flush the FIFO and MTMFLUSH MTMCTL reset the read/write pointers. -

Page 96: Programming Model

Programming Model Programming Model This data transfer can be set up using the following procedure. 1. Program the DMA registers for both channels. 2. Set (=1) the bit (bit 1) in the register to flush the MTMFLUSH MTMCTL FIFO and reset the read/write pointers. 3. - Page 97 Memory-to-Memory Port DMA /* Fill the source buffer */ lcntr=LENGTH(source), do fill until lce; dm(i0,1)=r0; fill: r0=rot r0 by 1; /* Set the interrupt mask for MTMDMA */ bit set imask MTMI; bit set mode1 IRPTEN; /* Flush the MTMDMA FIFO */ r0=MTMFLUSH;...

- Page 98 Programming Example ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

-

Page 99: Parallel Port

4 PARALLEL PORT The ADSP-2136x processor has a parallel port that allows bidirectional transfers between it and external parallel devices. Using the parallel port bus and control lines, the processor can interface to 8-bit or 16-bit wide external memory devices. The parallel port provides a DMA interface between internal and external memory and has the ability to support core driven data transfer modes (see Table... -

Page 100: Features

Features Table 4-1. Parallel Port Feature Summary (Cont’d) Feature Availability DMA Data Access DMA Channels DMA Chaining Interrupt Source Core/DMA Boot Capable Local Memory Clock Operation PCLK/3 Features • Support for standard SRAMs • Interface requires only 16 Pins for address and data •... -

Page 101: Pin Descriptions

Parallel Port transfers, and the programming model, with a programming example. Figure 4-1 shows a block diagram of the parallel port. DMD, PMD BUS IOD BUS PARALLEL PORT DATA_RX RXPP PPSI AD15-0 DATA_TX TXPP PPSO ADDR CONTROL STATUS ALE, WR, RD Figure 4-1. -

Page 102: Multiplexed Pin Functions

Pin Descriptions Multiplexed Pin Functions The parallel port pins can function as flag pins and the parallel data acqui- sition port pins can function as address pins. For complete information on the pin multiplexing scheme used with these processors, see “Parallel Port Pin Multiplexing”... -

Page 103: Data Cycles

Parallel Port pin is active high by default, but can be set active low via the bit (bit 13) in the parallel port control ( ) register. PPALEPL PPCTL Since polarity is active high by default, systems using parallel port boot mode must use address latching hardware that can pro- cess this active high signal. -

Page 104: Data Buffers

Pin Descriptions Data Buffers The parallel port has two data buffers or FIFOs, one each for reads and writes. These are explained the following sections. Read Path The parallel port has a two stage data FIFO for receiving data ( ). -

Page 105: Write Path

Parallel Port Write Path The parallel port has a two stage data FIFO for transmitting data ( TXPP The first stage ( ) is a 32-bit register that receives data from the inter- TXPP nal memory via the DMA controller or a core write. The data in TXPP moved to the second 32-bit register, . -

Page 106: Operation Modes

Pin Descriptions Operation Modes The external interface follows the standard asynchronous SRAM access protocol. The programmable data cycle duration bit ( ) and optional PPDUR bus hold cycle bit ( ) are provided to interface with memories having different access time requirements. The data cycle duration is pro- grammed via the bit in the register. -

Page 107: 16-Bit Mode

Parallel Port are provided through during the second half of the cycle A7–0 AD15–8 when the signal is asserted. The bits provides the data dur- AD7–0 ing the same cycle when is asserted. Eight-bit mode enables a larger external address range. ADSP-2136x SRAM 16M X 8... -

Page 108: Parallel Port Registers

Parallel Port Registers FIFOs and high speed A/D and D/A converters and offers the maximum throughput available on the parallel port (111M byte/sec). In 16-bit mode, 16 bits (maximum) of external address are available through latching the 16 bits of from into the external latch A15–0... -

Page 109: Control Register (Ppctl)

Parallel Port Control Register (PPCTL) The parallel port control ( ) register is a memory-mapped register and PPCTL is used to configure and enable the parallel port system. This register also contains status information for the Tx/Rx FIFO, the state of DMA, and for external bus availability. -

Page 110: Dma Transfers

Data Transfer Types Unlike the external port on previous SHARC processors, the ADSP-2136x core cannot directly access the external parallel bus. Instead, the core initializes two registers to indicate the external address and address modifier and then accesses data through inter- mediate registers. -

Page 111: Chained Dma Transfers

Parallel Port Before initializing a chain pointer DMA, it is important that are set to zero. ECPP ICPP Chained DMA Transfers DMA chaining is enabled by setting the (bit 30 in register). PPCHEN PPCTL When chaining is enabled, the next set of DMA parameters are loaded from internal memory after the current DMA cycle and new DMA starts. -

Page 112: Core-Driven Transfers

Data Transfer Types • A DMA transfer can be interrupted by resetting the bit, but PPDEN none of the other control settings (except for the bit) should PPEN be changed. If the parallel port remains enabled, then interrupted DMA can be resumed by setting the bit again. -

Page 113: Interrupt Driven Accesses

Parallel Port When the core accesses either the registers, the parallel port TXPP RXPP writes/fetches data to/from the specified external address. The details of this functionality and the four main techniques to manage each transfer are detailed in the following sections. In general, core-driven transfers are most advantageous when performing single-word accesses and/or accesses to non-sequential addresses. -

Page 114: Status-Driven Transfers (Polling)

Data Transfer Types To facilitate this, the (latch) bit of the register is set to one in LIRPTL every core cycle where the buffer is not full or, in receive mode, in TXPP every core cycle in which the buffer has valid data. When fast 16-bit RXPP wide parallel devices are accessed, there may be as few as ten core cycles between each transfer. -

Page 115: Core-Stall Driven Transfers

Parallel Port register—parallel port data cycle duration ( ) and bus hold cycle PPDUR enable ( PPBHC Please refer to “Functional Description” on page 4-4 for further explana- tion of the parallel port bus cycles, but in summary, programs can use the following values. -

Page 116: Interrupts

Interrupts • While a DMA transfer is active, the core may only write the PPEN bits of . Accessing any of the DMA parameter reg- PPDEN PPCTL isters or other bits in during an active transfer will cause the PPCTL parallel port to malfunction. -

Page 117: Dma Interrupts

Parallel Port DMA Interrupts When DMA is enabled, the maskable inte rrupt occurs when the DMA block transfer has completed (when theDMA internal word count register decrements to zero). ICPP When DMA chaining is enabled and the bit is set in the register, CPPP interrupts are generated whenever the current DMA ends. -

Page 118: 8-Bit Access

Throughput As described in “Functional Description” on page 4-4, parallel port accesses require both cycles to latch the external address and addi- tional data cycles to transmit or receive data. Therefore, the throughput on the parallel port is determined by the duration and number of these cycles per word. -

Page 119: 16-Bit Access

Parallel Port For example, assume = 0, and the parallel port is in 8-bit PPDUR3 mode. The first byte on a new page takes six peripheral clock cycles (three for the cycle and three for the data cycle), and the next sequential 255 bytes consume three peripheral clock cycles each. -

Page 120: 8-Bit Versus 16-Bit Sram Modes

Throughput There should be a correlation between the register values. ECPP ICPP In 16-bit mode, the value should be double that of ECPP ICPP 8-Bit Versus 16-Bit SRAM Modes When considering whether to employ the 16- or 8-bit mode in a particu- lar design, a few key points should be considered. -

Page 121: Parallel Port Effect Latency

Parallel Port • When the DMA external modifier is set to zero, ( = 0), the EMPP address does not change after the first cycle, therefore an cycle is only inserted on the first cycle. In this case, the 16-bit port can run twice as fast as the 8-bit port, as the overhead for cycles is zero. -

Page 122: Configuring The Parallel Port For Dma

Programming Model Configuring the Parallel Port for DMA Use the following steps to configure the parallel port for a standard DMA transfer. 1. Set (or reset) the bit in the register. Depending on PPTRAN PPCTL whether the operation is write or read, ensure that FIFO is empty and the external interface is idle by reading the status of the bits respectively. -

Page 123: Configuring The Parallel Port For Core Access

Parallel Port register. Once the DMA descriptors are fetched, normal DMA exe- cution starts and continues until the register contains all CPPP zeros. Configuring the Parallel Port for Core Access The following steps provide the basic procedure for setting up and initiat- ing a data transfer using the core. -

Page 124: Programming Examples

Programming Examples Programming Examples The program shown in Listing 4-1 performs a chained DMA. Listing 4-1. Parallel Port Chained DMA #include <def21364.h> #include <sru21364.h> #include <SRU.h> #define N 5 .section/pm seg_rth; nop; nop; nop; nop; nop; jump start; rti; rti; /* PP interrupt service routine at location 0x00090050 */ .section/pm seg_pp;... - Page 125 Parallel Port r0 = PPEN | PPDUR20 | PPDEN | PPTRAN | PPCHEN | PPBHC; dm(PPCTL) = r0; nop; ADSP-2136x SHARC Processor Hardware Reference 4-27 www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

- Page 126 Programming Examples 4-28 ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

-

Page 127: Digital Application Interface

5 DIGITAL APPLICATION INTERFACE The digital application interface (DAI) is comprised of a groups of periph- erals and its respective signal routing unit (SRU). The inputs and outputs of the peripherals are not directly connected to external pins. Rather, the SRUs connect the peripherals to a set ofpins and to each other, based on a set of configuration registers. - Page 128 Features Table 5-1. Routing Unit Feature Summary (Cont’d) Feature Open-drain Three-state High Impedance Programmable Pull-up I/O Level Status Register Interrupts Interrupt Source Core (DAILI or DAIHI) Total Channels Miscellaneous I/O channels Peripheral Channels Clock Operation PCLK/2 The DAI may be used to connect combinations of inputs to combinations of outputs.

-

Page 129: Functional Description

Digital Application Interface Functional Description Figure 5-1 shows how the DAI pin buffers are connected via the SRU. The DAI is comprised of four primary blocks: • Peripherals (A/B/C) associated with the DAI • A Signal Routing Unit (SRU) • DAI I/O pin buffers •... - Page 130 Functional Description PERIPHERAL INTERNAL CHIP NODE PIN BUFFER ROUTING PERIPHERAL CHIP MISCELLANEOUS BUFFER PERIPHERAL Figure 5-1. DAI Functional Block Diagram Note that Figure 5-1 is a simplified representation of a DAI system. In a real representation, the SRU and DAI would show several types of data being routed from several sources including the following.

-

Page 131: Signal Naming Conventions

Digital Application Interface • Asynchronous sample rate converters (SRC) • S/PDIF transmitter • S/PDIF receiver • DAI Interrupts (miscellaneous) Signal Naming Conventions Each peripheral associated with the DAI does not have any dedicated I/O pins for off-chip communication. Instead, the I/O pin is only accessible in the chip internally and is known as an internal node. -

Page 132: Dai Peripherals

DAI Peripherals DAI Peripherals All peripherals within the DAI that have bidirectional pins that generate a corresponding pin enable signal. Typically, the settings within a periph- eral’s control registers determine if a bidirectional pin is an input or an output, and is then driven accordingly. Both the peripheral control regis- ters and the configuration of the SRU can effect the direction of signal flow in a pin buffer. -

Page 133: I/O Pin Buffers

Digital Application Interface For each bidirectional line, the SPORT provides three separate signals. For example, a SPORT clock has three separate SRU connections (instead of one physical pin): • input clock to the SPORT ( SPORTx_CLK_I • output clock of the SPORT ( SPORTx_CLK_O •... -

Page 134: Pin Buffers As Signal Output

DAI Peripherals The notation for pin input and o utput connections can be quite confusing at first because, in a typical system, a pin is simply a wire that connects to a device. The manner in which the pins are routed within the SRU requires additional nomenclature. - Page 135 Digital Application Interface either an output or an input. Although the direction of a DAI pin is set simply by writing to a memory-mapped register, most often the pin’s direction is dictated by the designated use of that pin. For example, if the DAI pin were to be hard wired to only the input of another intercon- nected circuit, it would not make se nse for the corresponding pin buffer to be configured as an input.

-

Page 136: Pin Buffers As Signal Input

DAI Peripherals Pin Buffers as Signal Input When the DAI pin is to be used only as an input, connect the correspond- ing pin buffer enable to logic low as shown inFigure 5-6. This disables the buffer amplifier and allows an off-chip so urce to drive the value present on the DAI pin and at the pin buffer output. -

Page 137: Programmable Pull-Up Resistors

Digital Application Interface Programmable Pull-Up Resistors The pin buffer allows systems to attach a pull-up connected to the pad (high impedance) or disconnected (three state). This is controlled through register. DAI_PULLUP Pin Buffers as Open Drain For peripherals like the SPI (multi processing), the bus protocol requires the pin drivers to work in open drain mode (Figure 5-7) for transmit and... -

Page 138: Miscellaneous Buffers

DAI Peripherals Miscellaneous Buffers The miscellaneous buffers are used to interconnect signals from different routing groups. These buffers are similar to the DAI pin buffers with three basic differences. 1. Only for internal connections, no pin buffer enable required output always feeds DAI interrupt latch register and MISCxx_O Group F ( PBENx_I... -

Page 139: Signal Routing Matrix By Groups

Digital Application Interface Signal Routing Matrix by Groups The SRU can be compared to a set of patch bays, which contains a bank of inputs and a bank of outputs. For each input, there is a set of permissible output options. Outputs can feed to any number of inputs in parallel, but every input must be patched to exactly one valid output source. -

Page 140: Dai Group Routing

DAI Peripherals DAI Group Routing Each group has a unique encoding for its associated output signals and a set of configuration registers. For example, DAI group A is used to route clock signals. The memory-mapped registers, , contain bit fields SRU_CLKx corresponding to the clock inputs of various peripherals. - Page 141 Digital Application Interface SPORT5_CLK [32:1] SPORT5_CLK [32:1] SPORT5_CLK [32:1] SPORT5_CLK [32:1] SPORT5_CLK [32:1] SPORT5_CLK [32:1] Figure 5-9. Example DAI SRU Group A Multiplexing (SRU_CLKx) ADSP-2136x SHARC Processor Hardware Reference 5-15 www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

-

Page 142: Rules For Sru Connections

DAI Peripherals Rules for SRU Connections There are two rules which apply to all routing: 1. Each input must connect to exactly one output 2. An output can feed any number of inputs As an example: • is routed to SPORT0_CLK_O SPORT1_CLK_I •... - Page 143 Digital Application Interface Note that it is not possible to connect a signal in one group directly to a signal in a different group (analogous to wiring from one patch bay to another). However, group D is largely devoted to routing in this vein.

- Page 144 DAI Peripherals Example 1 SPORT0_CLK_I SPORT0_CLK_O SPORT0_CLK_PBEN_O SPORT1_CLK_I SPORT1_CLK_O SPORT1_CLK_PBEN_O Example 2 SPORT0_CLK_I SPORT0_CLK_O SPORT0_CLK_PBEN_O SPORT1_CLK_I DAI_PB04_O SPORT1_CLK_O EXTERNAL PACKAGE ENABLE DAI_PB04_O DAI_PB04_I CONNECTION SPORT1_CLK_PBEN_O PBEN04_I Figure 5-10. SRU Connection to SPORTs (Example 1 and 2) 5-18 ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI for the ADSP-21362/3/4/5/6 Processors...

- Page 145 Digital Application Interface Example 3 DAI_PB01_O DAI_PB01_O EXTERNAL PACKAGE ENABLE DAI_PB01_I CONNECTION DAI_PBEN01_I DAI_PB02_O DAI_PB02_O EXTERNAL PACKAGE ENABLE DAI_PB02_I CONNECTION HIGH DAI_PBEN02_I Example 4 DAI_PB01_O DAI_PB01_O EXTERNAL PACKAGE ENABLE DAI_PB01_I CONNECTION PBEN01_I DAI_PB02_O EXTERNAL DAI_PB02_O PACKAGE ENABLE DAI_PB02_I CONNECTION TIMER0_O DAI_PBEN02_I Figure 5-11.

-

Page 146: Routing Capabilities

DAI Peripherals Routing Capabilities Table 5-1 provides an overview about the different routing capabilities for the DAI unit. The DAI groups allow routing of specific signals like clocks, data, frame syncs. Table 5-2. DAI Routing Capabilities DAI Group Input (xxxx_I) Output (xxxx_O) A–Clocks SPORT5–0... -

Page 147: Default Routing

Digital Application Interface Table 5-2. DAI Routing Capabilities (Cont’d) DAI Group Input (xxxx_I) Output (xxxx_O) E– DAI Interrupt 31–22 TIMER2–0 DAI Pin Buffer Miscellaneous FLAG15–10 PDAP output strobe 20–1 Signals TIMER2–0 PCG AB (CLK, FS) Logic level high SPIB (control, data) S/PDIF TX (block start) Logic level low MISCA5–0... - Page 148 Default Routing IDP7-0_DAT_I DIR_I DIT_DAT_I SRC_3-0_DAT_IP_I SRC_3-0_TDM_OP_I SPORT0_DA_I SPORT1_DA_I SPORT1_DA_O SPORT0_DA_O Pin01 Pin05 PBEN_O PBEN_O SPORT0_DB_I SPORT1_DB_I SPORT1_DB_O SPORT0_DB_O Pin02 Pin06 PBEN_O PBEN_O SPORT0_CLK_I SPORT1_CLK_I SPORT0_CLK_O SPORT1_CLK_O Pin03 Pin07 PBEN_O PBEN_O SPORT0_FS_I SPORT1_FS_I SPORT0_FS_O SPORT1_FS_O Pin04 Pin08 PBEN_O PBEN_O Figure 5-12. DAI Default Routing 5-22 ADSP-2136x SHARC Processor Hardware Reference www.BDTIC.com/ADI...

- Page 149 Digital Application Interface SPORT2_DA_I SPORT4_DA_I SPORT2_DA_O SPORT4_DA_O Pin09 Pin15 PBEN_O PBEN_O SPORT2_DB_I SPORT4_DB_I SPORT2_DB_O SPORT4_DB_O Pin10 Pin16 PBEN_O PBEN_O SPORT2_CLK_I SPORT4_CLK_I SPORT2_CLK_O SPORT4_CLK_O PBEN_O PBEN_O SPORT2_FS_I SPORT4_FS_I SPORT2_FS_O SPORT4_FS_O PBEN_O PBEN_O SPORT3_CLK_I SPORT5_CLK_I SPORT5_CLK_O SPORT3_CLK_O Pin13 Pin19 PBEN_O PBEN_O SPORT3_FS_I SPORT5_FS_I SPORT3_FS_O SPORT5_FS_O...

-

Page 150: Interrupt Controller

Interrupt Controller Interrupt Controller The DAI contains a dedicated interrupt controller that signals the core when DAI peripheral events occur. System versus Exception Interrupts Generally, interrupts are classified as system or exception. Exception events include any hardware interrupts (for example, resets) and emula- tion interrupts, math exceptions, and illegal accesses to memory that does not exist. -

Page 151: Functional Description

Digital Application Interface Functional Description There are several registers in the DAI interrupt controller that can be con- figured to control how the DAI interrupts are reported to and serviced by the core’s interrupt controller. The DAI contains its own interrupt controller that indicates to the core when DAI audio peripheral related events have occurred. -

Page 152: Miscellaneous Interrupts

Interrupt Controller Just as the core has its own interrupt latch registers ( IRPTL LIRPTL the DAI has its own latch registers ( ). When DAI_IRPTL_L DAI_IRPTL_H a DAI interrupt is configured to be high priority, it is latched in the register. -

Page 153: Interrupt Events

Digital Application Interface Two registers ( ) replace the DAI periph- DAI_IRPTL_RE DAI_IRPTL_FE eral’s version of the register. As with the register, these DAI IMASK IMASK registers provide a way to specify which interrupts to notice and handle, and which interrupts to ignore. These dual registers function like the register, but with a higher degree of granularity. -

Page 154: Servicing Interrupts

Interrupt Controller falling edge of the waveform may be used as an interrupt source as well. Programs may select any of these three conditions: • Latch on the rising edge • Latch on the falling edge • Latch on both the rising and falling edge Table 5-3 shows which interrupts are valid on rising and or falling edges. -

Page 155: Debug Features

Digital Application Interface configurable channels ( ). When is read, the DAI_INT[31:0] DAI_IRPTL_H high priority latched interrupts are cleared. When is read, the DAI_IRPTL_L low priority latched interrupts are cleared. For more information, see “DAI Interrupt Controller Registers” on page A-77. ... -

Page 156: Loop Back Routing

Debug Features Loop Back Routing The serial peripherals (SPORT and SPI) support an internal loop back mode. If the loop back bit for each peripheral is enabled, it connects the transmitter with the receiver block internally (does not signal off-chip). The SRU can be used for this propose. -

Page 157: Programming Model

Digital Application Interface Programming Model As discussed in the previous sections, the signal routing unit is controlled by writing values that correspond to signal sources into bit fields that fur- ther correspond to signal inputs. The SRU is arranged into functional groups such that the registers that are made up of these bit fields accept a common set of source signal values. - Page 158 Programming Model Additional example code is available on the Analog Devices Web site. There is a macro that has been created to connect peripherals used in a DAI configuration. This code can be used in both assembly and C code. See the...

-

Page 159: Serial Ports

6 SERIAL PORTS The ADSP-2136x processors have six independent, synchronous serial ports (SPORTs) that provide an I/O interface to a wide variety of periph- eral devices. They are called SPORT0, SPORT1, SPORT2, SPORT3, SPORT4, and SPORT5. Each SPORT has its own set of control registers and data buffers. - Page 160 Table 6-1. Serial Port Feature Summary (Cont’d) Feature SPORT5–0[AB] Access Type Data Buffer Core Data Access DMA Data Access DMA Channels 2 per SPORT DMA Chaining Interrupt Source Core/DMA Boot Capable Local Memory Clock Operation PCLK/4 Bidirectional (transmit or receive) functions provide greater flexibility for serial communications.

- Page 161 Serial Ports I/O DATA/DMA BUS PM/DM DATA BUS TXSPxB RXSPxB RXSPxA TRANSMIT DATA RECEIVE DATA TXSPxA RECEIVE DATA BUFFER BUFFER TRANSMIT DATA BUFFER BUFFER HARDWARE HARDWARE COMPANDING COMPANDING (COMPRESSION) (COMPRESSION) SPORTS 1, 3, & 5 ONLY SPORTS 0, 2, & 4 ONLY TRANSMIT RECEIVE RECEIVE SHIFT...

-

Page 162: Features

Features Features Serial ports offer the following features and capabilities: • Four operation modes (“Selecting Operating Modes” on page 6-18): 1. Standard serial 2. Left-justified 3. I 4. Multichannel • Two bidirectional channels (A and B) per serial port, configurable as either transmitters or receivers. - Page 163 Serial Ports • DMA transfers to and from on-chip and off-chip memory. Each SPORT can automatically receive or transmit an entire block of data both on- and off-chip. • Chained DMA operations for multiple data blocks, see “DMA Chaining” on page 2-20.

-

Page 164: Pin Descriptions

Pin Descriptions Pin Descriptions Table 6-2 describes pin function. Table 6-2. SPORT Pin Descriptions Internal Nodes Direction Description SPORT5–0_DA_I/O Data Receive or T ransmit Channel A. Bidirectional data pin. This signal can be configured as an output to transmit serial data, or as an input to receive serial data. -

Page 165: Sru Sport Receive Master

Serial Ports Table 6-3. SPORT DAI/SRU Signal Connections Internal Node DAI Connection SRU Register Inputs SPORT5–0_CLK_I Group A SRU_CLK1–0 SPORT5–0_FS_I Group C SRU_FS0 SPORT5–0_DA_I Group B SRU_DAT2–0 SPORT5–0_DB_I Outputs SPORT5–0_CLK_O Group A, D SPORT5–0_FS_O Group C, D SPORT5–0_DA_O Group B, D SPORT5–0_DB_O SPORT5–0_CLK_PBEN_O Group F... - Page 166 SRU Configuration and frame sync registers, the reflection sensitivity in these signals can be avoided. Figure 5-10 on page 5-18 shows the default routing of the serial port where the SRU maps: • the signal from the DAI pin ( ) back to the SPORT DAI_PBxx_O clock input (...

-

Page 167: Functional Description

Serial Ports Functional Description A serial port receives serial data on one of its bidirectional serial data sig- nals configured as inputs, or transmits serial data on the bidirectional serial data signals configured as outputs. It can receive or transmit on both channels simultaneously and unidirectionally, where the pair of data sig- nals can both be configured as either transmitters or receivers. -

Page 168: Registers

Registers application program must use the correct serial port data buffers, accord- ing to the value of bit. The bit enables either the transmit SPTRAN SPTRAN data buffers for the transmission of A and B channel data, or it enables the receive data buffers for the reception of A and B channel data. - Page 169 Serial Ports the shaded cells denote that the bits have same function in all operating modes. Table 6-4. SPCTLx Control Bit Comparison Multichannel Mode S and Left-Justified Transmit Control Bits Receive Control Standard Serial Mode Mode (SPORT0, 2, 4) Bits (SPORT1, 3, 5) SPEN_A SPEN_A Reserved...

-

Page 170: Control Registers (Spctlx)

Registers Table 6-4. SPCTLx Control Bit Comparison (Cont’d) Multichannel Mode S and Left-Justified Transmit Control Bits Receive Control Standard Serial Mode Mode (SPORT0, 2, 4) Bits (SPORT1, 3, 5) SCHEN_B SCHEN_B SCHEN_B SCHEN_B 22 FS_BO Reserved Reserved Reserved 24 SP EN_B SPEN_B Reserved... -

Page 171: Data Buffers

Serial Ports registers are described in “SPORT Multichannel Control Registers (SPM- CTLxy)” on page A-43. Data Buffers When programming the serial port channel (A or B) as a transmitter, only the corresponding buffers become active while the TXSPxA TXSPxB receive buffers remain inactive. -

Page 172: Transmit Path

Registers Transmit Path If the serial port is configured as a serial transmitter, the data transmitted is written to the buffer. The data is (optionally) com- TXSPxA TXSPxB panded in hardware on the primary A channel (SPORT 0, 2, and 4 only), then automatically transferred to the transmit shift register, because com- panding is not supported on the secondary B channels. -

Page 173: Receive Path

Serial Ports been received. The data is then loaded to internal memory by the DMA controller or read directly by the program running on the processor core. Receive Path If the serial data signal is configured as a serial receiver ( = 0), the SPTRAN receive portion of the SPORT shifts in data from the... - Page 174 Registers Bits 31–30 ( and bits 28–27 ( in the registers indi- RXS_A) RXS_B) SPCTLx cate the status of the channel’s receive buffer contents as follows: 00 = buffer empty, 01 = reserved, 10 = buffer partially full, 11 = buffer full. If your program causes the core processor to attempt to read from an empty receive buffer or to write to a full transmit buffer, the access is delayed until the buffer is accessed by the external I/O device.

-

Page 175: Multichannel Buffer Status

Serial Ports Two complete 32-bit words can be stored in the receive buffer while a third word is being shifted in. The third word overwrites the second if the first word has not been read out (by the processor core or the DMA con- troller). -

Page 176: Selecting Operating Modes

Selecting Operating Modes overflow/underflow status bit in the ROVF_x TUVF_x SPCTLx register becomes fixed in multichannel mode only as either the overflow status bit (SPORTs 1, 3, and 5) or under- ROVF_x TUVF_x flow status bit (SPORTs 0, 2, and 4). Selecting Operating Modes The SPORTs operate in four modes: •... -

Page 177: Mode Selection

Serial Ports Mode Selection The serial port operating mode can be selected via the and the SPCTLx SPM- registers. “Serial Port Registers” on page A-30. CTLxy 1. The operating mode bit 11( ) of the register selects OPMODE SPCTLx between I S, left-justified, and standard serial/multichannel mode. -

Page 178: Data Word Formats

Data Word Formats Table 6-5. SPORT Operation Modes (Cont’d) SPCTLx Bits SPMCTLxy bits Bit 11 Bit 17 Bit 16 MCEA MCEB OPERATING MODES Multichannel A Channels Multichannel B Channels Multichannel A and B Channels Data Word Formats The format of the data words transmitted over the serial ports is config- ured by the , and bits of the... -

Page 179: Endian Format (Lsbf)

Serial Ports Table 6-6. Data Length versus Modes (Cont’d) Mode Word Length (SLEN) bits 8–32 Multichannel 3–32 Although the word lengths can be 3 to 32 bits, transmitting or receiving words smaller than 7 bits at one-fourth the full peripheral clock rate of the serial port may cause incorrect operation when DMA chaining is enabled. -

Page 180: Data Type (Dtype)

Data Word Formats The first 16-bit (or smaller) word is right-justified in bits 15–0 of the packed word, and the second 16-bit (or smaller) word is right-justified in bits 31–16. This applies to both receive (packing) and transmit (unpack- ing) operations. Companding can be used with word packing or unpacking. -

Page 181: Companding The Data Stream

Serial Ports Transmit or receive sign extension is selected by bit 0 of in the DTYPE register and is common to all transmit or receive channels. If bit 0 SPCTLx is set, sign extension occurs on selected channels that do not have DTYPE companding selected. -

Page 182: Companding As A Function

Data Word Formats Companding As a Function Since the values in the transmit and receive buffers are actually com- panded in place, the companding hardware can be used without transmitting (or receiving) any data, for example during testing or debug- ging. -

Page 183: Clock Signal Options

Serial Ports Clock Signal Options Each serial port has a clock signal ( ) for transmitting and SPORTx_CLK receiving data on the two associated data signals. The clock signals are configured by the bits of the control registers. A sin- ICLK CKRE SPCTLx... -

Page 184: Master Frame Sync

Clock Signal Options CLKDIV = (PCLK/4 x SCLK) – 1 Master Frame Sync The bit field specifies how many transmit or receive clock cycles are FSDIV counted before a frame sync pulse is generated. In this way, a frame sync can initiate periodic transfers. -

Page 185: Clock Source (Iclk, Mstr)

Serial Ports data is output. This delay may limit the receiver’s speed of operation. Refer to the ADSP-2136x SHARC Processor Data Sheet for exact timing specifications. Externally-generated late transmit frame syncs also experience a delay from when they arrive to when data is output. This can also limit the max- imum serial clock speed. -

Page 186: Frame Sync Options

Frame Sync Options data and frame syncs. Note that transmit data and frame sync signals change their state on the clock edge that is not selected. For example, the transmit and receive functions of any two serial ports connected together should always select the same value for so inter- CKRE nally-generated signals are driven on one edge and received signals are... -

Page 187: Internal Versus External Frame Syncs (Ifs, Imfs, Mstr)

Serial Ports must be loaded into the transmit buffer before the previous word is shifted out and transmitted. When is cleared (=0), the corresponding frame sync signal is not required. A single frame sync is required to initiate communications but it is ignored after the first bit is transferred. -

Page 188: Logic Level Frame Syncs (Lfs, Lmfs)

Frame Sync Options When is set (=1), the corresponding frame sync signal is generated internally by the processor, and the signal is an output. The SPORTx_FS frequency of the frame sync signal is determined by the value of the frame sync divisor ( ) in the registers. -

Page 189: Early Versus Late Frame Syncs (Lafs)

Serial Ports Bit 16 in the registers selects the logic level of the transmit data SPCTLx valid signal ( ) as active low (inverted) if set (=1), or active SPORTx_TDV_O high if cleared (=0). These signals are actually , reconfigured as SPORTx_FS outputs during multichannel operation. -

Page 190: Data-Independent Frame Sync (One Channel)

Frame Sync Options checked during the first bit. They do not need to be asserted after that time period. Figure 6-4 illustrates the two modes of frame signal timing. SPORTX_CLK LATE FRAME SYNC EARLY FRAME SYNC DATA Figure 6-4. Normal Versus Alternate Framing Data-Independent Frame Sync (One Channel) When transmitting data out of the SPORT ( = 1), the inter-... -

Page 191: Data Independent Frame Sync (Two Channels)

Serial Ports SPORT channel’s transmit buffer. Once data is loaded into the transmit buffer, it is not transmitted until the next frame sync is generated. This mode of operation allows data to be transmitted only at specific times. When = 0 and = 0, a receive signal is generated DIFS... -

Page 192: Operating Modes

Operating Modes Note that the SPORT DMA controller typically keeps the transmit buffer full. The application is responsible for filling the transmit buffers with data. Operating Modes The following sections provide detailed information on each operating mode available using the serial ports. It should be noted that many bits in the SPORT registers that control the function of the mode are the same bit but have a different name depending on the operating mode. -

Page 193: Clocking Options

Serial Ports • Internal clock enable ( ICLK • Word length ( , 3–32 bits) SLEN • Channel enable ( SPEN_A SPEN_B Clocking Options In standard serial mode, the serial portscan either accept an external serial clock or generate it internally. The bit in the register deter- ICLK... -

Page 194: Left-Justified Mode

Operating Modes register. The frame sync can be configured to be active high or SPCTL active low through the bit in the register. The timing between SPCTL the frame sync signal and the first bit of data either transmitted or received is also selectable through the bit in the register. -

Page 195: Left-Justified Mode Timing Control Bits

Serial Ports To transmit or receive words continuously in left-justified mode, load the register with the same value as . For example, for 8-bit data FSDIV SLEN words ( = 7), set = 7. SLEN FSDIV Left-Justified Mode Timing Control Bits Several bits in the control register enable and configure left-justi- SPCTLx... -

Page 196: I 2 S Mode

Operating Modes SPORTX_CLK SPORTx_FS/WS LEFT-JUSTIFIED MODE LSB n-1 MSB n LSB n MSB n+1 SPORTx_DA/DB DATA SAMPLE n-1 SAMPLE n SAMPLE n +1 Figure 6-5. Word Select Timing in Left-justified Mode S Mode S mode is a three-wire serial bus standard protocol for transmission of two-channel (stereo) pulse code modulation (PCM) digital audio data. -

Page 197: I 2 S Mode Timing Control Bits

Serial Ports transmitting the fixed number of words. The transmission of this dummy word toggles , generating an edge. Transmission SPORTx_FS of the dummy word is not required when the I S receiver is a serial port. S Mode Timing Control Bits Several bits in the register enable and configure I S mode... - Page 198 Operating Modes For I S operation ( = 1), the transfer starts on the left chan- L_FIRST nel first. SPORTx _CLK SPORTx _FS/WS I 2 S MODE LSB n-1 MSB n LSB n MSB n+1 SPORTx_DA/DB DATA WORD n-1 WORD n WORD n+1 RIGHT CHANNEL...

- Page 199 Serial Ports 1. The primary A channels of SPORT1, 3, and 5 are capable of expansion only, and the primary A channels of SPORT0, 2, and 4 are capable of compression only. 2. In multichannel mode, SPORT0 and SPORT1 work in pairs; SPORT0 is the transmit channel, and SPORT1 is the receive chan- nel.

- Page 200 Operating Modes Table 6-8. TDM Signal Descriptions (Cont’d) Internal Nodes (routed to any Direction Description DAI pin buffer) SPORT01/23/45_TDV_O Transmit d ata valid. SPORT 0 generates the trans- mit data valid pulse (TDV01) for the SPORT0/1 pair. SPORT 2 generates the transmit valid pulse (TDV23) for the SPORT2/3 pair.

- Page 201 Serial Ports SPORTs are paired when multichannel mode is selected. In this mode, transmit/receive directions are fixed where SPORTS 0, 2, and 4 act as transmitters, and SPORTs 1, 3, and 5 act as receivers. Transmit Valid Signals are used as a transmit data valid SPORT0_FS SPORT2_FS SPORT4_FS...

- Page 202 Operating Modes • The ) is used as transmit data valid for external TDV01 SPORT0_FS logic. This signal is active only during transmit channels. • The transfer is received on channel 0 (word 0), and transmits on channels 1 and 2 (word 1 and 2) WORD 0 WORD 1 WORD 2...

- Page 203 Serial Ports Setting the bits enables multichannel operation for both MCEA MCEB receive and transmit sides of the SPORT0/1, SPORT2/3 or SPORT4/5 pair. Number of Channels (NCH) Select the number of channels used in multichannel operation by using the 7-bit field in the multichannel control register.

- Page 204 Operating Modes while disabled channel words are ignored. Up to 128 channels are avail- able for transmitting and receiving. The multichannel selection registers enable and disable individual chan- nels. The registers for each serial port are shown in “SPORT Transmit Select Registers (MTxCSy)”...

- Page 205 Serial Ports Receive Selection Registers Setting a particular bit to 1 in the register MR1CS0–3 MR3CS0–3 MR5CS0–3 causes the serial port to receive the word in that channel’s position of the data stream. The received word is loaded into the receive buffer. Clearing the bit in the register causes the serial port to ignore the data.

- Page 206 Data Transfer Types When performing core-driven transfers, write to the buffer designated by bit setting in the registers. For DMA-driven transfers, SPTRAN SPCTLx the serial port logic performs the data transfer from internal memory to/from the appropriate buffer depending on the bit setting.

- Page 207 Serial Ports receives or starts to transmit a data word. The processor’s on-chip DMA controller handles the DMA transfer, allowing the processor core to con- tinue running until the entire block of data is transmitted or received. Service routines can then operate on the block of data rather than on sin- gle words, significantly reducing overhead.

- Page 208 Data Transfer Types Although the DMA transfers are performed with 32-bit words, serial ports can handle word sizes from 3 to 32 bits, with 8 to 32 bits for I S mode. If serial words are 16 bits or smaller, they can be packed into 32-bit words for each DMA transfer.

- Page 209 Serial Ports When the count register of an active DMA channel reaches zero (0), the SPORT generates the corresponding interrupt. DMA Chaining Each channel also has a DMA chaining enable bit ( SCHEN_A SCHEN_B in its control register. SPCTLx Each SPORT DMA channel also has a chain pointer register ( CPSPxy register functions are used in chained DMA operations.

- Page 210 Interrupts DMA Chain Insertion Mode It is possible to insert a single SPORT DMA operation or another DMA chain within an active SPORT DMA chain. Programs may need to per- form insertion when a high priority DMA requires service and cannot wait for the current chain to finish.

- Page 211 Serial Ports “Single Word Transfers” on page 6-47). The priority of the serial port interrupts is shown in Table 2-9 on page 2-11. Multiple interrupts can occur if both SPORTs transmit or receive data in the same cycle. Any interrupt can be masked in the register;...

- Page 212 Debug Features Debug Features The following sections provide information on debugging features avail- able with the serial ports. SPORT Loopback When the SPORT loopback bit, (bit 12), is set in the regis- SPMCTLxy ter, the serial port is configured in an internal loopback connection as follows: SPORT0 and SPORT1 work as a pair for internal loopback, SPORT2 and SPORT3 work as pairs, and SPORT4 and SPORT5 work as pairs.

- Page 213 Serial Ports the SPORT is configured in Loopback mode. This prevents contention with the internal loopback data transfer. Only transmit clock and transmit frame sync options may be used in loopback mode—programs must ensure that the serial port is set up correctly in the control registers.

- Page 214 Programming Model The SPORT is ready to start transmitting or receiving three serial clock cycles after they are enabled in the control register. No serial clocks SPCTLx are lost from this point on. This delay does also apply in slave mode (external clock/frame sync) for synchronization.

- Page 215 Serial Ports Enter DMA Chain Insertion Mode Chain insertion lets the SPORTs insert a single SPORT DMA operation or another DMA chain within an active SPORT DMA chain. 1. Enter chain insertion mode by setting = 0 and = 1 in SDENx SCHENx the channel’s DMA control register.

- Page 216 Programming Examples Listing 6-1. SPORT Transmit Using DMA #include <def21364.h> #include <sru21364.h> #include <SRU.h> /* Default Buffer Length */ #define BUFSIZE 10 .SECTION/DM seg_dmda; /* TX Buffers */ .var tx_buf1a[BUFSIZE] = 0x11111111, 0x22222222, 0x33333333, 0x44444444, 0x55555555, 0x66666666, 0x77777777, 0x88888888, 0x99999999, 0xAAAAAAAA;...

- Page 217 Serial Ports /* TX Transfer Control Blocks */ .var tx_tcb1[4] = 0,BUFSIZE,1,tx_buf1a; .var tx_tcb2[4] = 0,BUFSIZE,1,tx_buf1b; /* RX Transfer Control Blocks */ .var rx_tcb1[4] = 0,BUFSIZE,1,rx_buf0a; .var rx_tcb2[4] = 0,BUFSIZE,1,rx_buf0b; /* Main code section */ .global _main; .SECTION/PM seg_pmco; _main: r0 = 0;...

- Page 218 Programming Examples SDEN_A| /* Enable Channel A DMA */ SCHEN_A| /* Enable Channel A DMA Chaining */ IFS| /* Internally-generated Frame Sync */ ICLK; /* Internally-generated Clock */ dm(SPCTL1) = ustat4; /* Configure SPORT0 as a receiver */ /* externally generating clock and frame sync */ r0 = 0x0;...

- Page 219 Serial Ports /* Next TCB location for tx_tcb1 is tx_tcb2 */ /* Mask the first 19 bits of the TCB location */ r0 = (tx_tcb2 + 3) & 0x7FFFF; dm(tx_tcb1) = r0; /* Initialize SPORT DMA transfer by writing to the CP reg */ dm(CPSP1A) = r0;...

- Page 220 Programming Examples bit set mode1 CBUFEN; /* enable circular buffers */ /* SPORT Loopback: Use SPORT2 as RX & SPORT3 as TX */ /* Initially clear SPORT control registers */ r0 = 0x00000000; dm(SPCTL2) = r0; dm(SPCTL3) = r0; dm(SPMCTL23) = r0; /* Set up DAG registers */ i4 = tx_buf2a;...

- Page 221 Serial Ports dm(SPCTL2) = ustat4; /* Configure SPORT3 as a receiver */ /* externally generating clock and frame sync */ r0 = 0x0; dm(DIV3) = R0; ustat3 = SPEN_A| /* Enable Channel A */ SLEN32| /* 32-bit word length */ FSR;...

- Page 222 Programming Examples 0x77777777, 0x88888888, 0x99999999, 0xAAAAAAAA; /*Receive buffer*/ .var rx_buf4a[BUFSIZE]; /* Main code section */ .global _main; .SECTION/PM seg_pmco; _main: /* SPORT Loopback: Use SPORT4 as RX & SPORT5 as TX */ /* initially clear SPORT control register */ r0 = 0x00000000; dm(SPCTL4) = r0;...

- Page 223 Serial Ports /* SPORT 4 Internal DMA memory access modifier */ r0 = 1; dm(IMSP4A) = r0; /* SPORT 4 Number of DMA5 transfers to be done */ r0 = length(rx_buf4a); dm(CSP4A) = r0; /* set internal loopback bit for SPORT4 & SPORT5 */ bit set ustat3 SPL;...