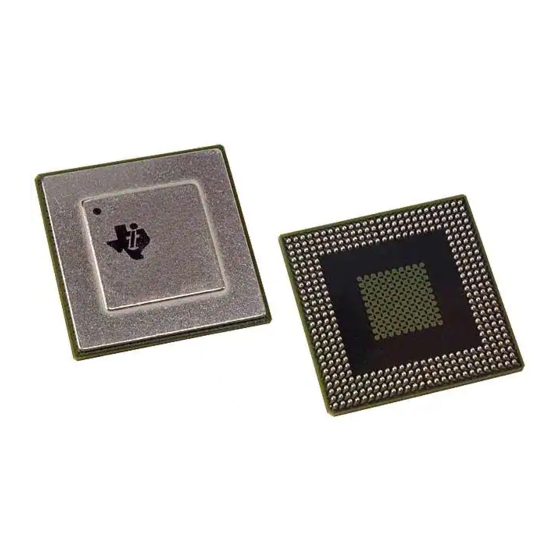

Texas Instruments TMS320C6201 Manuals

Manuals and User Guides for Texas Instruments TMS320C6201. We have 3 Texas Instruments TMS320C6201 manuals available for free PDF download: Reference Manual, Manual, Errata

Texas Instruments TMS320C6201 Reference Manual (477 pages)

TMS320C6000 series Peripherals

Brand: Texas Instruments

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

Advertisement

Texas Instruments TMS320C6201 Errata (29 pages)

Digital Signal Processor Silicon Errata

Brand: Texas Instruments

|

Category: Signal Processors

|

Size: 0 MB

Table of Contents

Texas Instruments TMS320C6201 Manual (70 pages)

FIXED-POINT DIGITAL SIGNAL PROCESSOR

Brand: Texas Instruments

|

Category: Computer Hardware

|

Size: 1 MB

Table of Contents

Advertisement

Advertisement

Related Products

- Texas Instruments TMS320C64x DSP

- Texas Instruments TMS320C6726

- Texas Instruments TMS320C6722

- Texas Instruments TMS320C6727

- Texas Instruments TMS320C6713

- Texas Instruments TMS320C642x DSP

- Texas Instruments TMS320C6474

- Texas Instruments TMS320C6670

- Texas Instruments TMS320C6000 Series

- Texas Instruments TMS320C62 Series