Table of Contents

Advertisement

Quick Links

Overview

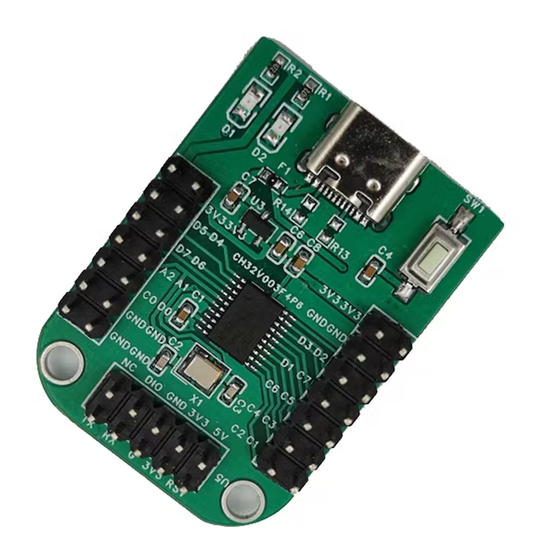

CH32V003 series are industrial-grade general-purpose microcontrollers designed based on 32-bit RISC-V

instruction set and architecture. It adopts QingKe V2A core, RV32EC instruction set, and supports 2 levels of

interrupt nesting. The series are mounted with rich peripheral interfaces and function modules. Its internal

organizational structure meets the low-cost and low-power embedded application scenarios.

This manual provides detailed information on the use of the CH32V003 series for the user's application

development, and is applicable to products with different memory capacities, functional resources, and

packages in the series; any differences will be specially explained in the corresponding functional chapters.

RISC-V core version overview

Features

Instruction

set

Core

versions

QingKe

RV32EC

V2A

Abbreviated description of the bit attribute in the register:

Register bit

properties

RF

RO

RZ

WO

WA

WZ

RW

RWA

RW1

RW0

RW1T

CH32V003 Reference Manual

Hardware

Interrupt

stack

nesting

levels

levels

2

2

Read-only property that reads a fixed value.

Read-only attribute, changed by hardware.

Read-only property, auto bit clear 0 after read operation.

Write only attribute (not readable, read value uncertain)

Write-only attribute, writable in Safe mode.

Write only attribute, auto bit clear 0 after write operation.

Readable and writable.

Readable, writable in Safe mode.

Readable, write 1 is valid, write 0 is invalid.

Readable, write 0 valid, write 1 invalid.

Readable, write 0 invalid, write 1 flipped.

Number of

Integer

fast interrupt

division

channels

periodicity

2

None

Property description

Vector

Extensions

table

instruction

protection

model

Address

or

Support

command

V1.3

Memory

None

Advertisement

Table of Contents

Summary of Contents for WCH CH32V003 Series

- Page 1 The series are mounted with rich peripheral interfaces and function modules. Its internal organizational structure meets the low-cost and low-power embedded application scenarios. This manual provides detailed information on the use of the CH32V003 series for the user's application development, and is applicable to products with different memory capacities, functional resources, and packages in the series;...

- Page 2 Chapter 1 Memory and Bus Architecture 1.1 Bus architecture The CH32V003 series is designed based on the RISC-V instruction set, and its architecture interacts the core, arbitration unit, DMA module, SRAM storage and other parts through multiple buses. The design integrates a...

- Page 3 CH32V003 Reference Manual http://wch.cn on this bus. The data bus (D-Code) connects the core to the FLASH data interface for constant loading and debugging. The system bus connects the core to the bus matrix and is used to coordinate accesses to the core, DMA, SRAM and peripherals.

- Page 4 CH32V003 Reference Manual http://wch.cn 1.2 Memory image The CH32V003 family contains program memory, data memory, core registers, peripheral registers, and more, all addressed in a 4GB linear space. System storage stores data in small-end format, i.e., low bytes are stored at the low address and high bytes are stored at the high address.

- Page 5 CH32V003 Reference Manual http://wch.cn 1.2.1 Memory allocation Built-in 2KB SRAM, starting address 0x20000000, supports byte, half-word (2 bytes), and full-word (4 bytes) access. Built-in 16KB program Flash memory (CodeFlash) for storing user applications. Built-in 1920B System memory (bootloader) for storing the system bootloader (factory-cured bootloader).

- Page 6 CH32V003 Reference Manual http://wch.cn Chapter 2 Power Control (PWR) 2.1 Overview The system operating voltage V ranges from 2.7 to 5.5V, and the built-in voltage regulator provides the 1.5V power supply required by the core. Figure 2-1 Block diagram of power supply structure power supply domain 1.5V...

- Page 7 CH32V003 Reference Manual http://wch.cn and with the external interrupt register (EXTI) setting, it can generate relevant interrupts to notify the system in time for pre-power down operations such as data saving. The specific configuration is as follows. Set the PLS[2:0] field of the PWR_CTLR register to select the voltage threshold to be monitored.

- Page 8 CH32V003 Reference Manual http://wch.cn 2.3.1 Low-power configuration options WFI and WFE WFI: The microcontroller is woken up by an interrupt source with interrupt controller response, and the interrupt service function will be executed first after the system wakes up (except for microcontroller reset).

- Page 9 CH32V003 Reference Manual http://wch.cn A precision external low frequency 128KHz crystal LSI can be selected as the auto-wakeup count time base. 2.4 Register description Table 2-2 PWR-related registers list Name Access address Description Reset value R32_PWR_CTLR 0x40007000 Power control register...

- Page 10 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [31:3] Reserved Reserved PVD output status flag bit. This bit is valid when PVDE=1 of PWR_CTLR register. 1: VDD and VDDA are below the PVD threshold set by PVD0 PLS[2:0]. 0: VDD and VDDA are above the PVD threshold set by PLS[2:0].

- Page 11 CH32V003 Reference Manual http://wch.cn Reserved AWUPSC Reset Name Access Description value [31:4] Reserved Reserved Counting time base 0000: Prescaler off. 0001: Prescaler off. 0010: Divided by 2 0011: Divided by 4 0100: Divided by 8 0101: Divided by 16 0110: Divided by 32...

- Page 12 CH32V003 Reference Manual http://wch.cn Chapter 3 Reset and Clock Control (RCC) The controller provides different forms of resets and configurable clock tree structures based on the division of power areas and peripheral power management considerations in the application. This section describes the scope of each clock in the system.

- Page 13 CH32V003 Reference Manual http://wch.cn Figure 3-1 System reset structure NRST System Reset Power Reset Software Res et WWDG Reset IWDG Reset Low-power management Reset V1.3...

- Page 14 CH32V003 Reference Manual http://wch.cn 3.3 Clock 3.3.1 System clock structure Figure 3-2 CH32V003 clock tree block diagram to gpio(internal,to time) IWDGCLK 128kHz to independent watchdog LSI RC to pwr(low power clock source) RCC_CFGR0 4~25MHz OSC_IN PLLSRC HSE OSC OSC_OUT SYSCLK...

- Page 15 CH32V003 Reference Manual http://wch.cn 3.3.2 High-speed clock (HSI/HSE) HSI is a high-speed clock signal generated by the system's internal 24MHz RC oscillator. HSI RC oscillator can provide system clock without any external devices. It has a short start-up time. HSI is enabled and disabled by setting the HSION bit in the RCC_CTLR register, and the HSIRDY bit indicates whether the HSI RC oscillator is stable or not.

- Page 16 CH32V003 Reference Manual http://wch.cn 3.3.3 Low-speed clock (LSI) The LSI is a low-speed clock signal generated by the system's internal RC oscillator of approximately 128 KHz. It can be kept running in shutdown and standby modes and provides the clock reference for the RTC clock, independent watchdog and wake-up unit.

- Page 17 CH32V003 Reference Manual http://wch.cn 3.3.5.4 Microcontroller clock output (MCO) The microcontroller allows outputting clock signals to the MCO pins. The following 4 clock signals can be selected as MCO clock outputs by configuring the multiplexed push-pull output mode in the corresponding GPIO port registers by configuring the MCO[2:0] bits of the RCC_CFGR0 register.

- Page 18 CH32V003 Reference Manual http://wch.cn PLL clock-ready lock flag bit. PLLRDY 1: PLL clock lock. 0: PLL clock is not locked. PLL clock enable control bit. 1: Enables the PLL clock. PLLON 0: Turn off the PLL clock. Note: After entering Standby low-power mode, this bit is cleared by hardware to 0.

- Page 19 CH32V003 Reference Manual http://wch.cn 3.4.2 Clock configuration register0 (RCC_CFGR0) Offset address: 0x04 30 29 Reserved MCO[2:0] Reserved 14 13 ADCPRE[4:0] Reserved HPRE[3:0] SWS[1:0] SW[1:0] Reset Name Access Description value [31:27] Reserved Reserved Microcontroller MCO pin clock output control. 0xx: no clock output.

- Page 20 CH32V003 Reference Manual http://wch.cn 0111: SYSCLK divided by 8. 1000: SYSCLK divided by 2. 1001: SYSCLK divided by 4. 1010: SYSCLK divided by 8. 1011: SYSCLK divided by 16. 1100: SYSCLK divided by 32. 1101: SYSCLK divided by 64. 1110: SYSCLK divided by 128.

- Page 21 CH32V003 Reference Manual http://wch.cn 0: No action. [15:13] Reserved Reserved PLL-ready interrupt enable bit. PLLRDYIE 1: Enable the PLL-ready interrupt. 0: Disable the PLL-ready interrupt. HSE-ready interrupt enable bit. HSERDYIE 1: Enable HSE-ready interrupt. 0: Disable HSE-ready interrupt. HSI-ready interrupt enable bit.

- Page 22 CH32V003 Reference Manual http://wch.cn TIM1 module reset control. TIM1RST 1: Reset module; 0: No effect. Reserved Reserved ADC1 module reset control. ADC1RST 1: Reset module; 0: No effect. [8:6] Reserved Reserved PD port module reset control for I/O. IOPDRST 1: Reset module; 0: No effect.

- Page 23 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [31:3] Reserved Reserved SRAM interface module clock enable bit. 1: SRAM interface module clock on during Sleep mode. SRAMEN 0: The SRAM interface module clock is turned off in Sleep mode.

- Page 24 CH32V003 Reference Manual http://wch.cn 3.4.8 APB1 Peripheral clock enable register (RCC_APB1PCENR) Offset address: 0x1C I2C1 Reserved Reserved Reserved TIM2 Reserved Reserved Reset Name Access Description value [31:29] Reserved Reserved Power interface module clock enable bit. PWREN 1: Module clock is on; 0: Module clock is off.

- Page 25 CH32V003 Reference Manual http://wch.cn occurs; cleared by software writing of the RMVF bit. Software reset flag. 1: Software reset occurs. SFTRSTF 0: No software reset occurs. Set to 1 by hardware when a software reset occurs; software write RMVF bit cleared.

- Page 26 CH32V003 Reference Manual http://wch.cn Chapter 4 Independent Watchdog (IWDG) The system is equipped with an independent watchdog (IWDG) to detect logic errors and software faults caused by external environmental disturbances. the IWDG clock source is derived from the LSI and can run independently of the main program, making it suitable for applications requiring low accuracy.

- Page 27 CH32V003 Reference Manual http://wch.cn a system reset from occurring. Write 0xAAAA to the IWDG_CTLR register to allow the hardware to update the IWDG_RLDR register value to the watchdog counter. This action needs to be executed regularly after the watchdog function is turned on, otherwise a watchdog reset action will occur.

- Page 28 CH32V003 Reference Manual http://wch.cn 4.3.3 Reload register (IWDG_RLDR) Offset address: 0x08 Reserved RL [11:0] Name Access Description Reset value [15:12] Reserved Reserved Counter reload value. Write 0x5555 to the KEY before modifying this field. When 0xAAAA is written to the KEY, the value...

- Page 29 CH32V003 Reference Manual http://wch.cn Chapter 5 Window Watchdog (WWDG) A Window Watchdog is generally used to monitor system operation for software faults such as external disturbances, unforeseen logic errors, and other conditions. It requires a counter refresh (dog feeding) within a specific window time (with upper and lower limits), otherwise earlier or later than this window time the watchdog circuit will generate a system Reset.

- Page 30 CH32V003 Reference Manual http://wch.cn a comparison with the current counter, the value is configured by user software and will not change. It is used as the upper limit value of the window time. Watchdog enable: WDG_CTLR register WDGA bit software set to 1, to turn on the watchdog function, you can system reset.

- Page 31 CH32V003 Reference Manual http://wch.cn 5.2.2 Debug mode When the system enters Debug mode, the counter of WWDG can be configured by the debug module register to continue or stop. 5.3 Register description Table 5-1 WWDG-related registers list Name Access address...

- Page 32 CH32V003 Reference Manual http://wch.cn operation can only be performed when the counter value is less than the window value and greater than 0x3F. 5.3.3 Status register (WWDG_STATR) Offset address: 0x08 Reserved EWIF Name Access Description Reset value [15:1] Reserved WO Reserved Wake up the interrupt flag bit early.

- Page 33 Chapter 6 Interrupt and Events (PFIC) The CH32V003 series has a built-in programmable fast interrupt controller (PFIC Programmable Fast Interrupt Controller) that supports up to 255 interrupt vectors. The current system manages 23 peripheral interrupt channels and 4 core interrupt channels, the others are reserved.

- Page 34 CH32V003 Reference Manual http://wch.cn programmable ADC global Interrupt 0x00000074 programmable I2C1_EV I2C1 event interrupt 0x00000078 programmable I2C1_ER I2C1 error interrupt 0x0000007C programmable USART1 USART1 global interrupt 0x00000080 programmable SPI1 SPI1 global Interrupt 0x00000084 programmable TIM1BRK TIM1 brake interrupt 0x00000088 programmable...

- Page 35 CH32V003 Reference Manual http://wch.cn pending bit. Enabling an EXTI channel as an event channel eliminates the need for the CPU to clear the interrupt flag bit and the PFIC pending bit after waking up from the WFE. 6.4.3 Description Using an external interrupt requires configuring the corresponding external interrupt channel, i.e. selecting the corresponding trigger edge and enabling the corresponding interrupt.

- Page 36 CH32V003 Reference Manual http://wch.cn 6.5.1.1 Interrupt enable register (EXTI_INTENR) Offset address: 0x00 Reserved Reserved MR9 MR8 MR7 MR6 MR5 MR4 MR3 MR2 MR1 MR0 Name Access Description Reset value [31:10] Reserved Reserved Enable the interrupt request signal for external interrupt channel x.

- Page 37 CH32V003 Reference Manual http://wch.cn Reserved TR9 TR8 TR7 TR6 TR5 TR4 TR3 TR2 TR1 TR0 Name Access Description Reset value [31:10] Reserved Reserved Enable falling edge triggering of external interrupt channel x. [9:0] 0: Disable falling edge triggering for this channel.

- Page 38 CH32V003 Reference Manual http://wch.cn R32_PFIC_GISR 0xE000E04C PFIC interrupt global status register 0x00000000 PFIC VTF interrupt ID configuration R32_PFIC_VTFIDR 0xE000E050 0x00000000 register PFIC VTF interrupt 0 offset address R32_PFIC_VTFADDRR0 0xE000E060 0x00000000 register PFIC VTF interrupt 1 offset address R32_PFIC_VTFADDRR1 0xE000E064 0x00000000...

- Page 39 CH32V003 Reference Manual http://wch.cn 2#-3# interrupt current enable state. 1: The current numbered interrupt is [3:2] INTENSTA2_3 enabled. 0: The current numbered interrupt is not enabled. [1:0] Reserved Reserved 6.5.2.2 PFIC interrupt enable status register 2 (PFIC_ISR2) Offset address: 0x04...

- Page 40 CH32V003 Reference Manual http://wch.cn 6.5.2.4 PFIC interrupt pending status register 2 (PFIC_IPR2) Offset address: 0x24 Reserved Reserved PENDSTA[38:32] Name Access Description Reset value [31:7] Reserved Reserved 32#-38# Interrupt current pending status. [6:0] PENDSTA32_38 1: The current number break is pending.

- Page 41 CH32V003 Reference Manual http://wch.cn Writing 1 is valid, writing 0 is invalid. Note: Same function as the PFIC_SCTLR register SYSRESET bit. [6:0] Reserved Reserved 6.5.2.7 PFIC interrupt global status register (PFIC_GISR) Offset address: 0x4C Reserved Reserved NESTSTA[7:0] Name Access Description...

- Page 42 CH32V003 Reference Manual http://wch.cn Name Access Description Reset value VTF interrupt 0 service program address [31:1] ADDR0 bit[31:1], bit0 is 0. VTF interrupt 0 enable bit. VTF0EN 1: enable VTF interrupt 0 channel; 0: off. 6.5.2.10 PFIC VTF interrupt 1 address register (PFIC_VTFADDRR1)

- Page 43 CH32V003 Reference Manual http://wch.cn Reserved INTEN[38:32] Name Access Description Reset value [31:7] Reserved Reserved 32#-38# interrupt enable control. [6:0] INTEN32_38 1: current number interrupt enable. 0: No effect. 6.5.2.13 PFIC interrupt enable clear register 1 (PFIC_IRER1) Offset address: 0x180 INTRESET[31:16]...

- Page 44 CH32V003 Reference Manual http://wch.cn Reser PEND Rese PEND Reserved Reserved SET14 rved SET12 SET3 SET2 Name Access Description Reset value 16#-31# interrupt pending setting. [31:16] PENDSET16_31 1: current numbered interrupt hang. 0: No effect. Reserved Reserved 14# Interrupt hang setting.

- Page 45 CH32V003 Reference Manual http://wch.cn Reserved Reserved 14# Interrupt hang clear. 1: The current numbered interrupt clears PENDRESET14 the pending state. 0: No effect. Reserved Reserved 12# Interrupt hang clear. 1: The current numbered interrupt clears PENDRESET12 the pending state. 0: No effect.

- Page 46 CH32V003 Reference Manual http://wch.cn 2#-3# interrupt execution status. [3:2] IACTS2_3 1: current number interruption in execution. 0: The current number interrupt is not executed. [1:0] Reserved Reserved 6.5.2.20 PFIC interrupt activation status register 2 (PFIC_IACTR2) Offset address: 0x304 Reserved Reserved...

- Page 47 CH32V003 Reference Manual http://wch.cn RESE Reserved WFIT SLEE SLEEP Reser Reserved ONPE ONEX DEEP Name Access Description Reset value System reset, clear 0 automatically. write 1 SYSRESET valid, write 0 invalid, same effect as PFIC_CFGR register. [30:6] Reserved Reserved SETEVENT Set the event to wake up the WFE case.

- Page 48 CH32V003 Reference Manual http://wch.cn Name Access Description Reset value [31:2] Reserved Reserved Interrupt nesting enable. INESTEN 0: interrupt nesting function off. 1: Interrupt nesting function is enabled. Hardware stack enable. HWSTKEN 0: hardware stacking function off. 1: Hardware stacking function is enabled.

- Page 49 CH32V003 Reference Manual http://wch.cn Name Access Description Reset value Software interrupt trigger enable (SWI). 1: Triggering software interrupts. SWIE 0: Turn off the trigger. After entering software interrupt, software clear 0 is required, otherwise it is continuously triggered. [30:4] Reserved Reserved Auto-reload count enable bit.

- Page 50 CH32V003 Reference Manual http://wch.cn 6.5.4.4 Counting comparison register (STK_CMPLR) Offset address: 0x10 CMP[31:16] CMP[15:0] Name Access Description Reset value [31:0] RW Set the comparison counter value to 32 bits. V1.3...

- Page 51 CH32V003 Reference Manual http://wch.cn Chapter 7 GPIO and Alternate function (GPIO/AFIO) The GPIO port can be configured for multiple input or output modes, with built-in pull-up or pull-down resistors that can be turned off, and can be configured for push-pull or open-drain functions. the GPIO port can also be multiplexed for other functions.

- Page 52 CH32V003 Reference Manual http://wch.cn 7.2.2 GPIO initialization function Just after reset, the GPIO ports run in the initial state, when most I/O ports are running in the floating input state, but there are also peripheral related pins such as HSE that are running on the peripheral multiplexing function.

- Page 53 CH32V003 Reference Manual http://wch.cn 7.2.7 Output configuration Figure 7-3 GPIO module output configuration structure block diagram Input data Read register TTL Schmitt Protection trigger diode Input driver I/O pin Write Bit set/reset registers Output driver Protection diode P-MOS Output Output data...

- Page 54 CH32V003 Reference Manual http://wch.cn 7.2.9 Analog input configuration Figure 7-5 The configuration structure when the GPIO module is used as an analog input To on-chip Analog Input peripheral Input data Read register TTL Schmitt Protection trigger diode Input driver I/O pin...

- Page 55 CH32V003 Reference Manual http://wch.cn Full-duplex Master mode Push-pull multiplexed output Full-duplex Slave mode Floating input or pull-up input Simple bi-directional data SPIx_MOSI Push-pull multiplexed output line/Master mode Simple bi-directional data Not used line/Slave mode Full-duplex Master mode Floating input or pull-up input...

- Page 56 CH32V003 Reference Manual http://wch.cn R32_GPIOD_BCR 0x40011414 PD port reset register 0x00000000 R32_GPIOA_LCKR 0x40010818 PA port configuration lock register 0x00000000 R32_GPIOC_LCKR 0x40011018 PC port configuration lock register 0x00000000 R32_GPIOD_LCKR 0x40011418 PD port configuration lock register 0x00000000 7.3.1.1 Port configuration register low (GPIOx_CFGLR) (x=A/C/D)

- Page 57 CH32V003 Reference Manual http://wch.cn 7.3.1.3 Port output register (GPIOx_OUTDR) (x=A/C/D) Offset address: 0x0C Reserved Reserved ODR7 ODR6 ODR5 ODR4 ODR3 ODR2 ODR1 ODR0 Name Access Description Reset value [31:8] Reserved Reserved For output modes. (y=0-7), the data output by the port. These data can only be operated in 16-bit form.

- Page 58 CH32V003 Reference Manual http://wch.cn form. 7.3.1.6 Port configuration lock register (GPIOx_LCKR) (x=A/C/D) Offset address: 0x18 Reserved Reserved LCKK LCK7 LCK6 LCK5 LCK4 LCK3 LCK2 LCK1 LCK0 Name Access Description Reset value [31:9] Reserved Reserved The lock key, which can be written in a specific sequence to achieve locking, but which can be read out at any time.

- Page 59 CH32V003 Reference Manual http://wch.cn USAR PA12 I2C1 SPI1 Reserved TIM2RM[1:0] TIM1RM[1:0] Reserved Name Access Description Reset value [31:27] Reserved Reserved These bits are used to configure the I/O ports for SW function and trace function. SWD (SDI) is the debug interface to access the core. It is always used as a SWD port after system reset.

- Page 60 CH32V003 Reference Manual http://wch.cn 00: Default mapping (CH1/ETR/PD4, CH2/PD3, CH3/PC0, CH4/PD7). 01: Partial mapping (CH1/ETR/PC5, CH2/PC2, CH3/PD2, CH4/PC1). 10: Partial mapping (CH1/ETR/PC1, CH2/PD3, CH3/PC0, CH4/PD7). Complete mapping (CH1/ETR/PC1, CH2/PC7, CH3/PD6, CH4/PD5). Remap bits for timer 1. These bits can be read and written by the user.

- Page 61 CH32V003 Reference Manual http://wch.cn EXTI7[1:0] EXTI6[1:0] EXTI5[1:0] EXTI4[1:0] EXTI3[1:0] EXTI2[1:0] EXTI1[1:0] EXTI0[1:0] Name Access Description Reset value [31:16] Reserved Reserved [15:14] [13:12] (x=0-7), external interrupt input pin configuration [11:10] bit. Used to determine to which port pins the [9:8] external interrupt pins are mapped.

- Page 62 CH32V003 Reference Manual http://wch.cn Chapter 8 Direct Memory Access Control (DMA) Direct Memory Access Controller (DMA) provides a high-speed data transfer method between peripherals and memory or between memory and memory without CPU intervention, and data can be moved quickly through DMA to save CPU resources for other operations.

- Page 63 CH32V003 Reference Manual http://wch.cn (MEM2MEM=1), the channel is turned on (EN=1) to start data transfer. This mode does not support cyclic mode. The configuration process is as follows. Set the first address of the peripheral register or the memory data address in the memory-to-memory mode (MEM2MEM=1) in the DMA_PADDRx register.

- Page 64 CH32V003 Reference Manual http://wch.cn function with programmable pointer increments. The first transmitted data address they access is stored in the DMA_PADDRx and DMA_MADDRx registers.By setting the PINC bit or MINC position 1 of the DMA_CFGRx register, the peripheral address self-increment mode or memory address self-increment mode can be enabled, respectively.

- Page 65 CH32V003 Reference Manual http://wch.cn Figure 8-1 DMA1 request image Table 8-2 DMA1 peripheral mapping table for each channel Peripherals Channel1 Channel 2 Channel 3 Channel 4 Channel 5 Channel 6 Channel 7 ADC1 ADC1 SPI1 SPI1_RX SPI1_TX USART1 USART1_TX USART1_RX...

- Page 66 CH32V003 Reference Manual http://wch.cn R32_DMA_CNTR2 0x40020020 DMA channel 2 number of data register 0x00000000 R32_DMA_PADDR2 0x40020024 DMA channel 2 peripheral address register 0x00000000 R32_DMA_MADDR2 0x40020028 DMA channel 2 memory address register 0x00000000 R32_DMA_CFGR3 0x40020030 DMA channel 3 configuration register 0x00000000...

- Page 67 CH32V003 Reference Manual http://wch.cn Offset address: 0x04 + (x-1)*0x400 CTEIF CHTIF CTCIF CGIF CTEIF CHTIF CTCIF CGIF CTEIF CHTIF CTCIF CGIF Reserved CTEIF CHTIF CTCIF CGIF CTEIF CHTIF CTCIF CGIF CTEIF CHTIF CTCIF CGIF CTEIF CHTIF CTCIF CGIF Reset Name...

- Page 68 CH32V003 Reference Manual http://wch.cn Memory address incremental incremental mode enable. 1: Enable incremental memory address increment MINC operation. 0: Memory address remains unchanged operation. Peripheral address incremental incremental mode enable. 1: Enable incremental incremental operation of the PINC peripheral address.

- Page 69 CH32V003 Reference Manual http://wch.cn 8.3.5 DMA Channel x peripheral address register (DMA_PADDRx)(x=1/2/3/4/5/6/7 ) Offset address: 0x10 + (x-1)*20 + (y-1)*0x400 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0...

- Page 70 CH32V003 Reference Manual http://wch.cn Chapter 9 Analog-to-digital Converter (ADC) The ADC module contains a 10-bit successive approximation type analog-to-digital converter with up to 24MHz input clock. It supports 8 external channels and 2 internal signal source sampling sources. Single conversion and continuous conversion of channels, automatic scan mode between channels, intermittent mode, external trigger mode, double sampling, trigger delay, etc.

- Page 71 CH32V003 Reference Manual http://wch.cn 9.2 Functional description 9.2.1 Module structure Figure 9-1 ADC module block diagram Rule channel data Conversion ends EOC=1 register (16 bits) End of Injection convers io n Injection channel data JEOC=1 register (4×16 bits) -ADC_IOFRx[9:0] ADC_IN0...

- Page 72 CH32V003 Reference Manual http://wch.cn Channel configuration The ADC module provides 10 channel sampling sources, including 8 external channels and 2 internal channels. They can be configured into two types of conversion groups: regular groups and injection groups. to achieve a group conversion consisting of a series of conversions in any order on any number of channels.

- Page 73 CH32V003 Reference Manual http://wch.cn value written after the offset defined in the ADC_IOFRx register, there will be positive and negative cases, so there are sign bits (SIGNB). Figure 9-2 Data left alignment Rule group data register Inject group data register...

- Page 74 CH32V003 Reference Manual http://wch.cn trigger group channels (ADC_ISQR) one by one method in sequence. Trigger injection method: When the rule group channel conversion process can be inserted into the injection group channel all conversion, and then continue the rule group channel conversion afterwards; but...

- Page 75 CH32V003 Reference Manual http://wch.cn same group is converted automatically when the current channel conversion is finished. In the scan mode, there is a subdivision into triggered injection mode and automatic injection mode depending on the status of the IAUTO bit.

- Page 76 CH32V003 Reference Manual http://wch.cn can only be used for a group of conversions. Continuous conversion The continuous conversion mode of the ADC is entered by setting the CONT bit of the ADC_CTLR2 register to 1. This mode starts another conversion as soon as the previous ADC conversion is finished, and the conversion does not stop at the last channel of the selection group, but continues again from the first channel of the selection group.

- Page 77 CH32V003 Reference Manual http://wch.cn 9.3 Register description Table 9-5 ADC-related registers list Name Access address Description Reset value R32_ADC_STATR 0x40012400 ADC status register 0x00000000 R32_ADC_CTLR1 0x40012404 ADC control register 1 0x00000000 R32_ADC_CTLR2 0x40012408 ADC control register 2 0x00000000 R32_ADC_SAMPTR1 0x4001240C...

- Page 78 CH32V003 Reference Manual http://wch.cn 1: Conversion complete. 0: The conversion is not completed. This bit is set to 1 by hardware (end of rule or injection channel group conversion), cleared by software to 0 (write 1 is invalid) or when reading ADC_RDATAR.

- Page 79 CH32V003 Reference Manual http://wch.cn Note: This mode requires disabling the external trigger function of the injection channel. In scan mode, use the analog watchdog enable bit on a single channel. AWDSGL 1: Using an analog watchdog on a single channel (AWDCH[4:0] selection).

- Page 80 CH32V003 Reference Manual http://wch.cn 0 by software after the conversion starts. External trigger transition mode enable for the rule channel. EXTTRIG 1: Use of external events to initiate conversions. 0: Turn off the external event activation function. External trigger event selection for initiating rule channel conversion.

- Page 81 CH32V003 Reference Manual http://wch.cn down mode. Note: A conversion is initiated when only ADON is changed in the register, and no new conversion is initiated if there are any other bits sent for change. 9.3.4 ADC Sample time configuration register 1 (ADC_SAMPTR1)

- Page 82 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [31:10] Reserved Reserved The data offset value of the injected channel x. When converting the injected channels, this value defines [9:0] JOFFSETx the value used to subtract from the original conversion data.

- Page 83 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [31:24] Reserved Reserved Number of channels to be converted in a regular channel [23:20] conversion sequence. 0000-1111: 1-16 conversions. The number of the 16th conversion channel in the rule [19:15] SQ16 sequence (0-9).

- Page 84 CH32V003 Reference Manual http://wch.cn The number of the 4th conversion channel in the rule [19:15] sequence (0-9). The number of the 3th conversion channel in the rule [14:10] sequence (0-9). The number of the 2th conversion channel in the rule [9:5] sequence (0-9).

- Page 85 CH32V003 Reference Manual http://wch.cn DATA[15:0] Reset Name Access Description value Rule channel conversion data (data left-aligned or right- [31:0] DATA aligned) 9.3.15 ADC Delayed data register (ADC_DLYR) Offset address: 0x50 Reserved DLYS Reserved DLYVLU Reset Name Access Description value [31:10]...

- Page 86 CH32V003 Reference Manual http://wch.cn Chapter 10 Advanced-control Timer (ADTM) The Advanced-control timer Module contains a powerful 16-bit auto-reload timer, TIM1, which can be used to measure pulse width or generate pulses, PWM waves, etc. It is used in motor control, power supply, etc.

- Page 87 CH32V003 Reference Manual http://wch.cn Figure 10-1 Block diagram of advanced-control timer structure Internal clock(CK_INT) CK_TIM18 from RCC Trigger ETRF Polarity selection, controller Edge detector and Prescaler ETRP TRGO To other timers To DAC and ADC Input filter ITR0 ITR1 TRGI...

- Page 88 CH32V003 Reference Manual http://wch.cn 10.2.2 Clock input Figure 10-2 Block diagram of CK_PSC source for advanced-control timer TIMx_SMCR TS[2:0] ITRx TI1_ED TI2F TI1F TI1FP1 Encoder TI2F_Rising mode Edge TI2FP2 Filter detector ETRF TI2F_Falling TRGI External clock mode 1 CC2P ICF[3:0]...

- Page 89 CH32V003 Reference Manual http://wch.cn ECE position is set, the external clock source mode 2 is used. when using the external clock source mode 2, ETRF is selected as CK_PSC. the ETR pin becomes ETRP after passing through the optional inverter (ETP), divider (ETPS), and then ETRF after passing through the filter (ETF).

- Page 90 CH32V003 Reference Manual http://wch.cn Figure 10-3 Block diagram of the structure of the comparison capture channel TI1F_ED To the slave mode controller TI1F_Rising TI1FP1 TI1F Filter Edge TI1F_Falling downcounter detector Divider TI2FP1 /1,/2,/4,/8 ICF[3:0] CC1P/CC1NP TIMx_CHCTLR1 TIMx_CCER (from slave mode...

- Page 91 CH32V003 Reference Manual http://wch.cn 10.3 Functionality and Implementation The implementation of the complex functions of the advanced-control timer are all achieved by the operation of the timer's compare capture channel, clock input circuit and counter and peripheral parts. The clock input to the timer can come from multiple clock sources, including the input to the compare capture channel.

- Page 92 CH32V003 Reference Manual http://wch.cn 10.3.3 Forced output mode The output pattern of the timer's compare capture channel can be forced by software to output a determined level without relying on comparison of the compare capture register's shadow register with the core counter.

- Page 93 CH32V003 Reference Manual http://wch.cn output pin) and can output two complementary signals (OCx and OCxN). OCx and OCxN can be independently set for polarity via the CCxP and CCxNP bits, independently set for output enable via CCxE and CCxNE, and independently set for output enable via the MOE, OIS, OISN, OSSI, and OSSR bits for deadband and other controls.

- Page 94 CH32V003 Reference Manual http://wch.cn Figure 10-5 Generation of single pulse Set TI2 to trigger. Setting the CC2S field to 01b to map TI2FP2 to TI2; setting the CC2P bit to 0b to set TI2FP2 as rising edge detection; setting the TS field to 110b to set TI2FP2 as trigger source; setting the SMS field to 110b to set TI2FP2 to be used to start the counter.

- Page 95 CH32V003 Reference Manual http://wch.cn 10.3.10 Timer synchronization mode Timers are capable of outputting clock pulses (TRGO) and receiving inputs from other timers (ITRx). The source of ITRx (TRGO from other timers) is different for different timers. The timer internal trigger connections are shown in Table 10-2.

- Page 96 CH32V003 Reference Manual http://wch.cn 0: Turn off the indication function 1: Enables the indication function. Note: When enabled, [16] of CHxCVR indicates the level corresponding to the capture value. Capture value mode configuration. 0: The capture value is the value of the actual counter...

- Page 97 CH32V003 Reference Manual http://wch.cn update interrupt or DMA request is generated by any of the following events. -Counter overflow/underflow -Setting the UG position -Updates generated from the mode controller Disable updates, the software allows/disables the generation of UEV events by means of this bit.

- Page 98 CH32V003 Reference Manual http://wch.cn the synchronization information (TRGO) sent to the slave timer in master mode. The possible combinations are as follows. 000: The UG bit of the Reset-TIMx_EGR register is used as the trigger output (TRGO). In the case of a reset...

- Page 99 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value ETR trigger polarity selection, this bit selects whether to input ETR directly or to input the inverse of ETR. 1: Invert ETR, low or falling edge active; 0: ETR, active high or rising edge.

- Page 100 CH32V003 Reference Manual http://wch.cn 101: Filtered timer input 1 (TI1FP1). 110: Filtered timer input 2 (TI2FP2). 111: External trigger input (ETRF). The above only changes when SMS is 0. Note: See Table 10-2 for details. Reserved Reserved Input mode selection field. Selects the clock and trigger mode of the core counter.

- Page 101 CH32V003 Reference Manual http://wch.cn channel 3. Compare the DMA request enable bit of capture channel 2. 1: allows comparison of DMA requests for capture CC2DE channel 2. 0: Disable comparison of DMA requests for capture channel 2. Compare the DMA request enable bit of capture channel 1.

- Page 102 CH32V003 Reference Manual http://wch.cn 1: the value of the counter is captured into the capture comparison register when the status of CC1IF has been set. 0: No duplicate captures are generated. Reserved Reserved The brake interrupt flag bit, once the brake input is valid, by hardware for this position bit, can be cleared by software.

- Page 103 CH32V003 Reference Manual http://wch.cn Reserved TG COMG CC4G CC3G CC2G CC1G UG Reset Name Access Description value [15:8] Reserved Reserved The brake event generation bit, which is set and cleared by software, is used to generate a brake event. 1: Generate a brake event. At this point, MOE=0,...

- Page 104 CH32V003 Reference Manual http://wch.cn incremental counting mode; if in decremental counting mode, the core counter takes the value of the reload value register. 10.4.7 Compare/Capture control register 1 (TIM1_CHCTLR1) Offset address: 0x18 The channel can be used in input (capture mode) or output (compare mode), and the direction of the channel is defined by the corresponding CCxS bit.

- Page 105 CH32V003 Reference Manual http://wch.cn comparison result is changed or when switching from freeze mode to PWM mode in the output comparison mode. Compare Capture Register 2 preload enable bit. 1: Enable the preload function of compare capture registers, read and write operations only operate on the...

- Page 106 CH32V003 Reference Manual http://wch.cn digital filter length. The digital filter consists of an event counter, which records N events and then generates a jump in the output. 0000: no filter, sampled at fDTS. 1000: sampling frequency Fsampling = Fdts/8, N = 6.

- Page 107 CH32V003 Reference Manual http://wch.cn OC4CE OC4M[2:0] OC4PE OC4FE OC3CE OC3M[2:0] OC3PE OC3FE CC4S[1:0] CC3S[1:0] IC4F[3:0] IC4PSC[1:0] IC3F[3:0] IC3PSC[1:0] Comparison mode (pin direction is output). Reset Name Access Description value OC4CE RW Compare capture channel 4 clear enable bit. [14:12] OC4M RW Compare the Capture Channel 4 mode setting field.

- Page 108 CH32V003 Reference Manual http://wch.cn CC2E RW Compare the capture channel 2 output enable bit. Compare capture channel 1 complementary output CC1NP polarity setting bit. Compare capture channel 1 complementary output CC1NE enable bit. CC1P RW Compare capture channel 1 output polarity setting bit.

- Page 109 CH32V003 Reference Manual http://wch.cn 10.4.14 Compare/Capture register 1 (TIM1_CH1CVR) Offset address: 0x34 CH1CVR[15:0] Reset Name Access Description value [15:0] CH1CVR RW Compare the value of capture register channel 1. 10.4.15 Compare/Capture register 2 (TIM1_CH2CVR) Offset address: 0x38 CH2CVR[15:0] Reset Name...

- Page 110 CH32V003 Reference Manual http://wch.cn Auto output enable. 1: the MOE can be set by software or set in the next update event. 0: MOE can only be set by software. The brake input polarity setting bit. 1: brake input active high.

- Page 111 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [15:13] Reserved Reserved The length of the DMA continuous transmission, the [12:8] actual value of which is the value of this field + 1. [7:5] Reserved Reserved These bits define the offset of the DMA in continuous...

- Page 112 CH32V003 Reference Manual http://wch.cn Chapter 11 General-purpose Timer (GPTM) The general-purpose timer module contains a 16-bit auto-reloadable timer, TIM2, for measuring pulse width or generating pulses of a specific frequency, PWM waves, etc. It can be used in automation control, power supply, etc.

- Page 113 CH32V003 Reference Manual http://wch.cn can also be output as TRGO to other peripherals such as timers and ADCs. The core of the general-purpose timer is a 16-bit counter (CNT). cK_PSC is divided by a prescaler (PSC) to become cK_CNT and then finally fed to the CNT, which supports incremental counting mode, decremental counting mode, and incremental and decremental counting mode, and has an auto-reload register (ATRLR) to reload the initialization value for the CNT at the end of each counting cycle.

- Page 114 CH32V003 Reference Manual http://wch.cn External clock source mode 1. External clock source mode 2. Encoder mode. All 4 clock source sources mentioned above can be selected by these 4 operations. 11.2.3.1 Internal clock source (CK_INT) If the general-purpose timer is started when the SMS field is held at 000b, then it is the internal clock source (CK_INT) that is selected as the clock.

- Page 115 CH32V003 Reference Manual http://wch.cn Figure 11-3 Block diagram of the structure of the comparison capture channel TI1F_ED To the slave mode controller TI1F_Rising TI1FP1 TI1F Filter Edge TI1F_Falling downcounter detector Divider TI2FP1 /1,/2,/4,/8 ICF[3:0] CC1P/CC1NP TIMx_CHCTLR1 TIMx_CCER (from slave mode...

- Page 116 CH32V003 Reference Manual http://wch.cn of the compare capture host channel and clock source selection directly determines its function. The compare capture channel is bidirectional and can operate in both input and output modes. 11.3.1 Input capture mode The input capture mode is one of the basic functions of the timer. The principle of input capture mode is that when a determined edge on the ICxPS signal is detected, a capture event is generated and the current value of the counter is latched into the compare capture register (R16_TIMx_CHCTLRx).

- Page 117 CH32V003 Reference Manual http://wch.cn forces OCxREF to high. Note that by forcing OCxM to 100b or 101b, the comparison process between the internal main counter and the compare capture register is still going on, the corresponding flags are still set, and interrupts and DMA requests are still being generated.

- Page 118 CH32V003 Reference Manual http://wch.cn Figure 11-4 Event Generation and Impulse Response OC1REF ATRLR CHxCVR DELAY PULSE As shown in Figure 11-4, a positive pulse of length Tpulse needs to be generated on OC1 after a delay Tdelay at the beginning of a rising edge detected on the TI2 input pin.

- Page 119 CH32V003 Reference Manual http://wch.cn 11.3.8 Timer synchronization mode Timers are capable of outputting clock pulses (TRGO) and also receiving inputs from other timers (ITRx). The source of ITRx (TRGO from other timers) is different for different timers. The timer internal trigger connections are shown in Table 11-2.

- Page 120 CH32V003 Reference Manual http://wch.cn 0: Turn off the indication function 1: Enables the indication function. Note: When enabled, [17] of CHxCVR indicates the level corresponding to the capture value. Capture value mode configuration. 0: The capture value is the actual counter value...

- Page 121 CH32V003 Reference Manual http://wch.cn -Counter overflow/underflow -Setting the UG position -Updates generated from the mode controller Disable updates, the software allows/disables the generation of UEV events via this bit. 1: UEV is disabled. no update event is generated and the registers (ATRLR, PSC, CHCTLRx) maintain their values.

- Page 122 CH32V003 Reference Manual http://wch.cn 011: comparison pulse that triggers the output to send a positive pulse (TRGO) when a capture or a successful comparison occurs, when the CC1IF flag is to be set (even if itis already high). 100: The OC1REF signal is used as a trigger output (TRGO.

- Page 123 CH32V003 Reference Manual http://wch.cn 0110: sampling frequency Fsampling = Fdts/4, N = 6. 0111: sampling frequency Fsampling = Fdts/4, N = 8. 1000: sampling frequency Fsampling = Fdts/8, N = 6. 1001: sampling frequency Fsampling = Fdts/8, N = 8.

- Page 124 CH32V003 Reference Manual http://wch.cn Reserv Reserv CC4D CC3D CC2D CC1D Reserv Reserv CC4I CC3I CC2I CC1I Reset Name Access Description value Reserved Reserved Trigger the DMA request enable bit. 1: Allowing DMA requests to be triggered. 0: Triggering of DMA requests is prohibited.

- Page 125 CH32V003 Reference Manual http://wch.cn 11.4.5 Interrupt Status Register (TIM2_INTFR) Offset address: 0x10 Reserved CC4OF CC3OF CC2OF CC1OF Reserved TIF Reserved CC4IF CC3IF CC2IF CC1IF UIF Reset Name Access Description value [15:13] Reserved Reserved CC4OF WO Compare capture channel 4 to repeat capture flag bits.

- Page 126 CH32V003 Reference Manual http://wch.cn reinitialized by a trigger event. 11.4.6 Interrupt Status Register (TIM2_INTFR) Offset address: 0x14 Reserved TG Reserved CC4G CC3G CC2G CC1G UG Reset Name Access Description value [15:7] Reserved Reserved The trigger event generation bit, which is set by software and cleared by hardware, is used to generate a trigger event.

- Page 127 CH32V003 Reference Manual http://wch.cn the channel in input mode. OC2CE OC2M[2:0] OC2PE OC2FE OC1CE OC1M[2:0] OC1PE OC1FE CC2S[1:0] CC1S[1:0] IC2F[3:0] IC2PSC[1:0] IC1F[3:0] IC1PSC[1:0] Comparison mode (pin direction is output). Reset Name Access Description value Compare capture channel 2 clear enable bit.

- Page 128 CH32V003 Reference Manual http://wch.cn written at any time, and the newly written value takes effect immediately. Note: Once the LOCK level is set to 3 and CC1S=00, this bit cannot be modified. PWM mode can be used only in single pulse mode (OPM=1) without confirming the pre-load register, otherwise its action is not determined.

- Page 129 CH32V003 Reference Manual http://wch.cn 1100: sampling frequency Fsampling = Fdts/16, N = 8. 0101: sampling frequency Fsampling = Fdts/2, N = 8. 1101: sampling frequency Fsampling = Fdts/32, N = 5. 0110: sampling frequency Fsampling = Fdts/4, N = 6.

- Page 130 CH32V003 Reference Manual http://wch.cn [6:4] OC3M RW Compare the capture channel 3 mode setting field. OC3PE RW Compare Capture Register 3 preload enable bit. OC3FE RW Compare capture channel 3 fast enable bit. [1:0] CC3S RW Compare capture channel 3 input selection fields.

- Page 131 CH32V003 Reference Manual http://wch.cn 11.4.11 Counting clock prescaler (TIM2_PSC) Offset address: 0x28 PSC[15:0] Reset Name Access Description value The dividing factor of the prescaler of the timer; the [15:0] clock frequency of the counter is equal to the input frequency of the divider/(PSC+1).

- Page 132 CH32V003 Reference Manual http://wch.cn [15:0] CH3CVR RW Compare the value of capture register channel 3. 11.4.16 Compare/capture register 4 (TIM2_CH4CVR) Offset address: 0x40 CH4CVR[15:0] Reset Name Access Description value [15:0] CH4CVR RW Compare the value of capture register channel 4.

- Page 133 CH32V003 Reference Manual http://wch.cn Chapter 12 Universal Synchronous Asynchronous Receiver Transmitter (USART) The module contains one Universal Synchronous Asynchronous Transceiver USART1. 12.1 Main features Full-duplex or half-duplex synchronous or asynchronous communication NRZ data format Fractional baud rate generator, up to 3Mbps...

- Page 134 CH32V003 Reference Manual http://wch.cn setting on the M (word length) bit, and finally a configurable number of stop bits. If equipped with a parity check bit, the last bit of the data word is the check bit. After the TE is set an idle frame is sent, which is 10 or 11 bits high and contains the stop bit.

- Page 135 CH32V003 Reference Manual http://wch.cn Figure 12-2 USART clock timing example (M=0) Figure 12-3 Data Sample Hold Time CK (capture strobe on CK rising edge in this example) Data on RX valid DATA bit (from slave) SETUP HOLD 1/16 bit time...

- Page 136 CH32V003 Reference Manual http://wch.cn (R16_USARTx_CTLR3), but it is also necessary to turn off LIN mode, half duplex mode and IR mode, i.e. to ensure that the LINEN, HDSEL and IREN bits are in reset, but CLKEN can be turned on to output the clock, these bits are in control registers 2 and 3 (R16_USARTx_CTLR2 and R16_USARTx_CTLR3).

- Page 137 CH32V003 Reference Manual http://wch.cn CTS, transmit complete (TC), receive data ready (TXNE), dataoverflow (ORE), line idle (IDLE), parity error (PE), disconnect flag (LBD), noise (NE), overflow for multi-buffered communication (ORT), and frame error (FE), among others. Table 12-1 Relationship between interrupts and corresponding enable bits...

- Page 138 CH32V003 Reference Manual http://wch.cn cleared by software. If LBDIE is already set, an interrupt will be generated. 1: LIN disconnection detected. 0: No detection of pending LIN disconnection. Send data register empty flag. This bit is set by hardware when the data in the TDR register is transferred to the shift register by hardware.

- Page 139 CH32V003 Reference Manual http://wch.cn interrupt. If the EIE bit is set, the FE flag position bit generates an interrupt in multi-buffer communication mode. Frame error flag. This bit will be set by hardware when a synchronization error, excessive noise or disconnect character is detected.

- Page 140 CH32V003 Reference Manual http://wch.cn 12.10.4 USART Control register 1 (USART_CTLR1) Offset address: 0x0C Reserved TXEI RXNE IDLEI Reserved PEIE TCIE RE RWU SBK Name Access Description Reset value [31:14] Reserved Reserved USART enable bit. When this bit is set, both the USART divider and the output stop working after the current byte transfer is completed.

- Page 141 CH32V003 Reference Manual http://wch.cn 1: Send; 0: Do not send. 12.10.5 USART Control register 2 (USART_CTLR2) Offset address: 0x10 Reserved Reser LINE Reser LBDI Reser STOP ADD[3:0] Name Access Description Reset value [31:15] Reserved Reserved LIN mode enable, set to enable LIN mode. The...

- Page 142 CH32V003 Reference Manual http://wch.cn 1: The clock pulse of the last data bit is output to the CK pin Note: This bit cannot be modified after enabling transmit. Reserved RW Reserved LIN break detection interrupt enable, this position LBDIE bit enables interrupts caused by LBD.

- Page 143 CH32V003 Reference Manual http://wch.cn 12.10.7 USART Guard time and prescaler register (USART_GPR) Offset address: 0x18 Reserved GT[7:0] PSC[7:0] Name Access Description Reset value [31:16] Reserved Reserved Guard time value. This bit-field gives the Guard time value in terms of number of baud clocks. This [15:8] is used in Smartcard mode.

- Page 144 CH32V003 Reference Manual http://wch.cn Chapter 13 Inter-integrated Circuit (I2C) interface The Internal Integrated Circuit Bus (I2C) is widely used for communication between microcontrollers and sensors and other off-chip modules, it supports multi-master and multi-slave modes, and can communicate at 100KHz (standard) and 400KHz (fast) using only two lines (SDA and SCL). Timing and DMA, with CRC checksum function.

- Page 145 CH32V003 Reference Manual http://wch.cn Figure 13-2 shows the functional block diagram of the I2C module. Data register Noise Data Data shift register filter control Comparator PEC calculation Own address register Dual address register Clock Noise PEC register filter control Clock control...

- Page 146 CH32V003 Reference Manual http://wch.cn sent is the address byte, the first 7 bits represent the address of the target slave device, the 8 bit determines the direction of the subsequent message, 0 means the master device writes data to the slave device, 1 means the master device reads information to the slave device.

- Page 147 CH32V003 Reference Manual http://wch.cn 7-bit address), the I2C module will go to transmitter mode and the TRA bit will indicate whether it is currently receiver or transmitter mode. In transmit mode, after clearing the ADDR bit, the I2C module sends bytes from the data register to the SDA line via a shift register.

- Page 148 CH32V003 Reference Manual http://wch.cn 13.6 Clock extension If clock extension is disabled, then there is a possibility of overrun/underrun errors. However, if clock extension is enabled: In transmit mode, if TxE is set and BTF is set, SCL will always be low, always waiting for the user to read the status register and write the data to be sent to the data register.

- Page 149 CH32V003 Reference Manual http://wch.cn Figure 13-4 I2C Interrupt Request 13.9 DMA DMA can be used to send and receive bulk data. The ITBUFEN bit of the control register cannot be set when using DMA. Transmission using DMA DMA mode can be activated by setting the DMAEN bit of the CTLR2 register. As long as the TxE bit is set, data will be loaded by DMA from the set memory into the data register of the I2C.

- Page 150 CH32V003 Reference Manual http://wch.cn 13.10 Packet error checking Packet Error Checksum (PEC) is an additional CRC8 checksum step to provide transmission reliability, calculated for each bit of serial data using the following polynomial. +X+1 The PEC calculation is activated by the ENPEC bit in the control register and is performed on all information bytes, including address and read/write bits.

- Page 151 CH32V003 Reference Manual http://wch.cn hardware after the PE has been cleared. 1: ACK bit controls the ACK or NAK of the next byte received in the shift register. The next byte received in the PEC shift register is the PEC.

- Page 152 CH32V003 Reference Manual http://wch.cn 13.11.2 I2C Control register 2(I2C1_CTLR2) Offset address: 0x04 ITBU ITEV ITER Reserved LAST Reserved FREQ[5:0] Name Access Description Reset value [15:13] Reserved Reserved DMA last transfer bit. 1:Next DMA EOT is the last transfer. 0:Next DMA EOT is not the last transfer.

- Page 153 CH32V003 Reference Manual http://wch.cn 0: 7-bit slave address (does not respond to 10-bit address) [14:10] Reserved Reserved Interface address, bits 9-8 when using a 10-bit [9:8] ADD9_8 address, ignored when using a 7-bit address. [7:1] ADD7_1 RW Interface address, bits 7-1.

- Page 154 CH32V003 Reference Manual http://wch.cn received byte will be lost; when in send mode, no new data is written to the data register, and the same byte will be sent twice. 0: No overrun or underrun events. Acknowledge failure bit. Cleared by software writing 0, or by hardware when PE=0.

- Page 155 CH32V003 Reference Manual http://wch.cn byte. For 7-bit addressing, the bit is set after the ACK of the byte. 0:No end of address transmission. In Slave mode: 1:Received address matched. 0:Address mismatched or not received. Start bit. Cleared by software by reading the SR1...

- Page 156 CH32V003 Reference Manual http://wch.cn 13.11.8 I2C Clock register (I2C1_CKCFGR) Offset address: 0x1C F/S DUTY Reserved CCR[11:0] Name Access Description Reset value Master mode selection bit. 1:Fm mode I2C. 0:Sm mode I2C Duty cycle of high-level time over low-level time in Fm.

- Page 157 CH32V003 Reference Manual http://wch.cn Chapter 14 Serial Peripheral Interface (SPI) SPI supports data interaction in a three-wire synchronous serial mode, plus a chip selector line to support hardware switching between Master and Slave modes, and supports communication on a single data line.

- Page 158 CH32V003 Reference Manual http://wch.cn determined by SSI, this case is generally used in SPI Master mode. NSS is controlled by hardware: when NSS output is enabled, i.e., when SSOE is set, the NSS pin will be actively pulled low when the SPI host sends output outward, and a hardware error will be generated if the NSS pin is pulled low;...

- Page 159 CH32V003 Reference Manual http://wch.cn Configure the NSS pin, for example by setting the SSOE bit and letting the hardware set the NSS. it is also possible to set the SSM bit and set the SSI bit high. To set the MSTR bit and the SPE bit, you need to make sure that the NSS is already high at this time.

- Page 160 CH32V003 Reference Manual http://wch.cn 14.2.7 Errors Master mode fault (MODF) When the SPI is operating in NSS pin hardware management mode, an external pull-down of the NSS pin occurs; or in NSS pin software management mode, the SSI bit is cleared; or the SPE bit is cleared, causing the SPI to be shut down;...

- Page 161 CH32V003 Reference Manual http://wch.cn mode. 1: Initiate CRC calculation. 0: CRC calculation is disabled. After the next data transfer, send the value of the CRC register. This should be set immediately after CRCNEXT the last data is written to the data register.

- Page 162 CH32V003 Reference Manual http://wch.cn Control register 2 Name Access Description Reset value [15:8] Reserved Reserved Tx buffer empty interrupt enable bit. Setting this TXEIE bit allows an interrupt to be generated when TXE is set. RX buffer not empty interrupt enable bit. Used to...

- Page 163 CH32V003 Reference Manual http://wch.cn Channel side. This flag is set by hardware and reset by a software sequence. 1:Channel Right has to be transmitted or has CHSID been received. 0:Channel Left has to be transmitted or has been received. Transmit buffer empty.

- Page 164 CH32V003 Reference Manual http://wch.cn checksum of the received byte. Setting CRCEN resets this register. The calculation method uses the polynomial used in CRCPOLY. 8-bit mode only the lower 8 bits are involved in the calculation, 16-bit mode all 16 bits are involved in the calculation.

- Page 165 CH32V003 Reference Manual http://wch.cn Chapter 15 Electronic Signature (ESIG) The electronic signature contains the chip identification information: the flash memory area capacity and a unique identifier. It is burned into the system storage area of the memory module by the manufacturer at the factory and can be read by SWD (SDI) or application code.

- Page 166 CH32V003 Reference Manual http://wch.cn Name Access Description Reset value [31:0] U_ID[63:32] The 32-63 digits of UID. 15.2.4 UID register (ESIG_UNIID3) U_ID[95:80] U_ID[79:64] Name Access Description Reset value [31:0] U_ID[95:64] The 64-95 digits of UID. V1.3...

- Page 167 CH32V003 Reference Manual http://wch.cn Chapter 16 Flash Memory and User Option Bytes 16.1 Flash memory organization The internal flash memory of the chip is organized as follows. Table 16-1 Flash Memory Organization Block Name Address Range Size(byte) Page 0 0x0800 0000 – 0x0800 003F Page 1 0x0800 0040 –...

- Page 168 CH32V003 Reference Manual http://wch.cn R32_FLASH_KEYR 0x40022004 FPEC key register R32_FLASH_OBKEYR 0x40022008 OBKEY register R32_FLASH_STATR 0x4002200C Status register 0x00000000 R32_FLASH_CTLR 0x40022010 Configuration register 0x00000080 R32_FLASH_ADDR 0x40022014 Address register R32_FLASH_OBR 0x4002201C Select word register 0x03FFFFFE R32_FLASH_WPR 0x40022020 Write protection register 0xFFFFFFF R32_FLASH_MODEKEYR...

- Page 169 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value Select word key for entering the select word key [31:0] OBKEYR to release OPTWRE. 16.3.4 OBKEY register (FLASH_OBTKEYR) Offset address: 0x08 25 24 23 Reserved WRPRT LOCK MODE Reserved Reserved Reset...

- Page 170 CH32V003 Reference Manual http://wch.cn Reset Name Access Description value [31:20] Reserved Reserved BUFRST BUF reset operation BUFLOAD Cache data into BUF FTER Performs a fast page (64Byte) erase operation. FTPG Performs quick page programming operations. Fast programming lock. Write '1' only. When...

- Page 171 CH32V003 Reference Manual http://wch.cn ADDR[15:0] Name Access Description Reset value The flash memory address, when programming, is the programmed address, and when erasing, is the [31:0] ADDR start address of the erase. When the BSY bit in FLASH_SR register is '1', this register cannot be written.

- Page 172 CH32V003 Reference Manual http://wch.cn Each bit represents 1K bytes (16 pages) of storage write protection status. Note: WPR is loaded from the user-selected word area after a system reset. 16.3.9 Extended key register (FLASH_MODEKEYR) Offset address: 0x24 MODEKEYR[31:16] MODEKEYR[15:0] Name...

- Page 173 CH32V003 Reference Manual http://wch.cn 16.4.3 Main memory standard programming Standard programming can be written 2 bytes at a time. When the PG bit of FLASH_CTLR register is '1', each half-word (2 bytes) written to the flash address will initiate programming once, and writing any non-half-word data will cause the FPEC to generate a bus error.

- Page 174 CH32V003 Reference Manual http://wch.cn Figure 16-2 FLASH Page Erase Read the LOCK bit of FLASH_CTRL Perform "Unlock Flash LOCK bit=1? Memory" operation Set FLASH_CTLR的PER bit=1 Write the erased page header address in FLASH_ADDR register (erase 8 pages at a time) Set FLASH_CTLR STRT bit=1 BSY bit=1?...

- Page 175 CH32V003 Reference Manual http://wch.cn Set the MER bit of FLASH_CTLR register to '1' to enable the whole chip erase mode. Set the STAT bit of FLASH_CTLR register to '1' to start the erase action. Wait for the BYS bit to become '0' or the EOP bit of FLASH_STATR register to be '1' to indicate the end of erase, and clear the EOP bit to 0.

- Page 176 CH32V003 Reference Manual http://wch.cn Check the FLASH_CTLR register FLOCK bit, if it is 1, you need to execute the "fast programming mode unlock" operation. Check the BSY bit of the FLASH_STATR register to confirm that there are no other programming operations in progress.

- Page 177 CH32V003 Reference Manual http://wch.cn Low-power management reset configuration for standby mode. STANDBY 1: Enabling low-power management reset for Standby _RST mode. 0: Disable low-power management reset for Standby mode. Reserved Reserved Independent Watchdog (IWDG) hardware enable configuration. 1: IWDG is enabled by software and disabled from being enabled by hardware.

- Page 178 CH32V003 Reference Manual http://wch.cn of programming, and clear the EOP bit to 0. Read the programmed address data checksum. Continue programming you can repeat steps 5-7 and end programming to clear the OBPG bit to 0. Note: When "Read Protected" in the modified selection word becomes "Unprotected", a whole-slice erase of the main memory will be performed automatically.

- Page 179 CH32V003 Reference Manual http://wch.cn Chapter 17 Extended configuration 17.1 Extended configuration The system provides the EXTEND extended configuration unit (EXTEND_CTR register). This unit uses the AHB clock and performs a reset action only at system reset. It mainly includes the following extended control bit functions.

- Page 180 CH32V003 Reference Manual http://wch.cn LOCKUP monitoring function. 1: Enabled, performs a reset and sets LKUPEN LOCKUP_RESET when a lock-up occurs on the system. 0: Not enabled. [5:0] Reserved Reserved V1.3...

- Page 181 CH32V003 Reference Manual http://wch.cn Chapter 18 Debug Support (DBG) 18.1 Main features This register allows the MCU to be configured in the debug state. It includes: Independent Watchdog (IWDG) enabled counters Window Watchdog (WWDG) enabled counters Timer1 enabled counters Timer2 enabled counters 18.2 Register description...

Need help?

Do you have a question about the CH32V003 Series and is the answer not in the manual?

Questions and answers