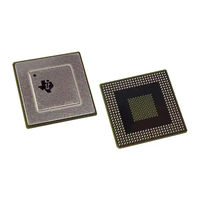

Texas Instruments TMS320C6701 Manuals

Manuals and User Guides for Texas Instruments TMS320C6701. We have 1 Texas Instruments TMS320C6701 manual available for free PDF download: Reference Manual

Texas Instruments TMS320C6701 Reference Manual (477 pages)

TMS320C6000 series Peripherals

Brand: Texas Instruments

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

Advertisement

Advertisement

Related Products

- Texas Instruments TMS320C6711D

- Texas Instruments TMS320C67X+ DSP

- Texas Instruments TMS320C6745 DSP

- Texas Instruments TMS320C642 Series

- Texas Instruments TMS320C6202

- Texas Instruments TMS320C6211

- Texas Instruments TMS320C6711

- Texas Instruments TMS320C80

- Texas Instruments TMS320C82

- Texas Instruments TMS320C55 Series