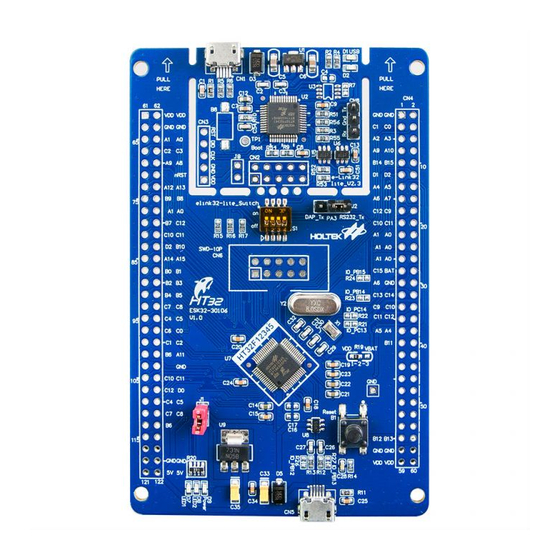

HOLTEK HT32F12345 Manuals

Manuals and User Guides for HOLTEK HT32F12345. We have 1 HOLTEK HT32F12345 manual available for free PDF download: User Manual

HOLTEK HT32F12345 User Manual (590 pages)

32-Bit Microcontroller with Arm Cortex-M3 Core

Brand: HOLTEK

|

Category: Microcontrollers

|

Size: 6 MB

Table of Contents

-

-

Introduction42

-

Features42

-

-

Page Erase46

-

Mass Erase47

-

Register Map52

-

-

-

-

Introduction69

-

Features70

-

Register Map75

-

-

-

Introduction82

-

Features82

-

-

Register Map92

-

-

-

-

Introduction117

-

Register Map118

-

Apbprstr0121

-

Apbprstr1122

-

-

-

Introduction124

-

Features125

-

Register Map127

-

-

-

-

Introduction159

-

Features160

-

Register Map161

-

-

-

Introduction166

-

Features169

-

Register Map169

-

-

-

Introduction171

-

Features171

-

Register Map174

-

-

-

-

Introduction180

-

Features181

-

-

ADC Clock Setup182

-

Conversion Modes182

-

Analog Watchdog190

-

Interrupts190

-

PDMA Request191

-

-

Register Map191

-

-

Adctsr204

-

-

-

Introduction215

-

Features215

-

-

Register Map218

-

-

-

Introduction224

-

Features225

-

-

Counter Mode225

-

Clock Controller227

-

Slave Controller230

-

Input Stage235

-

Output Stage236

-

Digital Filter242

-

PDMA Request249

-

-

Register Map250

-

-

-

-

Introduction284

-

Features284

-

Register Map287

-

-

-

Introduction291

-

Features292

-

-

Counter Mode293

-

Clock Controller296

-

Slave Controller298

-

Input Stage303

-

Output Stage304

-

Digital Filter317

-

Lock Level Table324

-

PDMA Request325

-

-

Register Map326

-

-

-

-

Introduction365

-

Features365

-

-

Register Map368

-

-

-

Introduction375

-

Features375

-

Register Map377

-

-

-

384384

-

Introduction384

-

Features385

-

-

Data Validity386

-

Arbitration389

-

Bus Error390

-

Address Snoop390

-

Operation Mode390

-

PDMA Interface396

-

Register Map397

-

-

-

-

Introduction411

-

Features412

-

-

Master Mode412

-

Slave Mode412

-

Status Flags417

-

-

Register Map420

-

-

-

-

Introduction431

-

Features432

-

-

Irda436

-

RS485 Mode438

-

PDMA Interface441

-

Register Map441

-

-

-

-

Introduction455

-

Features456

-

-

PDMA Interface459

-

Register Map459

-

-

-

Introduction467

-

Features467

-

-

Endpoints468

-

Ep_Sram468

-

Double-Buffering469

-

Remote Wake-Up471

-

-

Register Map471

-

-

-

-

Introduction496

-

Features496

-

-

AHB Master497

-

PDMA Channel497

-

Channel Transfer498

-

Channel Priority498

-

Transfer Request499

-

Address Mode499

-

Auto-Reload500

-

-

Register Map500

-

-

-

-

Introduction514

-

Features514

-

-

EBI Bank Access525

-

EBI Ready526

-

PDMA Request527

-

Register Map527

-

-

-

-

539539

-

Introduction539

-

Features539

-

-

Register Map549

-

-

-

-

Introduction559

-

Features559

-

Register Map561

-

-

-

Introduction565

-

Features565

-

-

SD Clock566

-

SD Protocol567

-

Command568

-

Response568

-

Data569

-

Buffer Status571

-

DMA Request571

-

Interrupt571

-

Register Map572

-

Advertisement