Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Xilinx VCU110

- Page 1 VCU110 Evaluation Board User Guide UG1073 (v1.2) March 26, 2016...

-

Page 2: Revision History

1-24, Table 1-25, Table 1-40, and Table 1-59. Added thickness information to Appendix F, Board Specifications. Updated the UltraScale XCVU190-2FLGC2104EES9847 FPGA part number throughout. 01/16/2016 11/21/2015 Initial Xilinx release. VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016... -

Page 3: Table Of Contents

VCU110 Evaluation Board Features ........ - Page 4 VCU110 Zynq-7000 AP SoC XC7Z010 System Controller ........

- Page 5 Please Read: Important Legal Notices ..........156 VCU110 Evaluation Board www.xilinx.com...

-

Page 6: Chapter 1: Vcu110 Evaluation Board Features

Appendix H, Additional Resources and Legal Notices for references to documents, files, and resources relevant to the VCU110 board. VCU110 Evaluation Board Features The VCU110 evaluation board features are listed here. Detailed information for each feature is provided in Feature Descriptions, starting on page •... - Page 7 Chapter 1: VCU110 Evaluation Board Features Three SI5328 clock multiplier and jitter attenuators ° SMA user clock connector pair (differential) ° • 52 GTY transceivers (13 Quads) 5 Quads connected to Interlaken connector ° 2 Quads connected to 2 BullsEye™ SMA connectors °...

-

Page 8: Block Diagram

The page numbers shown in Figure 1-1 refer to schematic page numbers in the VCU110 schematic XTP407. The VCU110 evaluation board can be damaged by electrostatic discharge (ESD). Follow ESD CAUTION! prevention measures when handling the board. X-Ref Target - Figure 1-1... -

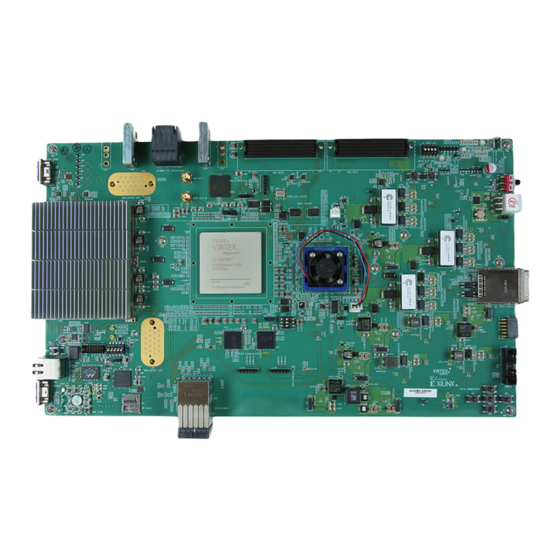

Page 9: Board Layout

IMPORTANT: the board. The VCU110 evaluation board can be damaged by electrostatic discharge (ESD). Follow ESD CAUTION! prevention measures when handling the board. X-Ref Target - Figure 1-2... - Page 10 Chapter 1: VCU110 Evaluation Board Features Table 1-1: VCU110 Board Component Descriptions Schematic Callout Feature Notes 0381556 Page Number Virtex UltraScale XCVU190-2FLGC2104EES9847 XCVU190-2FLGC2104EES9847, FPGA, (U1) (with fan-sink on soldered FPGA) COFAN 30-5530-03 Transceivers, 13 Quads Embedded within FPGA U1 9-12...

- Page 11 Chapter 1: VCU110 Evaluation Board Features Table 1-1: VCU110 Board Component Descriptions (Cont’d) Schematic Callout Feature Notes 0381556 Page Number I2C Bus, Topology and Bus Switches, I2C Bus MUX TI PCA9544ARGYR (U80) GPIO LEDs, green 0603 User GPIO LEDs, (DS6-DS10, DS31-DS33)

-

Page 12: Feature Descriptions

FPGA. For further information on Virtex UltraScale FPGAs, see Virtex UltraScale Architecture Data Sheet (DS893), [Ref FPGA Device Configuration The VCU110 board supports two of the five UltraScale FPGA configuration modes: • Master SPI using the onboard dual Quad SPI (QSPI) flash memory •... - Page 13 1-2. The mode switches M2, M1, and M0 are on SW16 positions 1, 2, and 3 respectively as shown in Figure 1-3. The FPGA default mode setting M[2:0] = 101, selecting the JTAG configuration mode. Table 1-2: VCU110 Board FPGA Configuration Modes Configuration SW16 DIP Switch Bus Width CCLK Direction...

- Page 14 Chapter 1: VCU110 Evaluation Board Features Encryption Key Backup Circuit The XCVU190 FPGA U1 implements bitstream encryption key technology. The VCU110 board provides the encryption key backup battery circuit shown in Figure 1-4. The Seiko TS518FE rechargeable 1.5V lithium button-type battery B1 is soldered to the board with the positive output connected to the XCVU190 FPGA U1 V pin AN13.

- Page 15 Chapter 1: VCU110 Evaluation Board Features I/O Voltage Rails There are eight I/O banks available on the XCVU190 device and the VCU110 board. The voltages applied to the FPGA I/O banks (shown in Figure 1-5) used by the VCU110 board are...

-

Page 16: Qdr2+ Component Memory

Chapter 1: VCU110 Evaluation Board Features Table 1-3: I/O Bank Voltage Rails (Cont’d) FPGA (U1) Bank Power Supply Rail Net Name Voltage HR Bank 84 VCC1V8_FPGA 1.8V HR Bank 94 VCC1V8_FPGA 1.8V QDR2+ Component Memory [Figure 1-2, callout 4] The 144 Mb QDR2+ component memory system is comprised of one 18-bit separate I/O (SIO) device (Cypress CY7C2663KV18-550BZXC) located at U168. - Page 17 Chapter 1: VCU110 Evaluation Board Features Table 1-4: QDR2 Memory U168 18-bit SIO I/F to FPGA U1 Banks 66 and 67 (Cont’d) FPGA (U1) Pin Schematic Net Name I/O Standard Pin Number Pin Name AV24 QDR2_18B_A3 HSTL_I_DCI AW22 QDR2_18B_A4 HSTL_I_DCI...

-

Page 18: Rld3 Component Memory

QDRII+ Design Guidelines section of the LogiCORE IP UltraScale Architecture-Based FPGAs Memory Interface Solutions Product Guide V5.0 (PG150) [Ref 3] for Vivado Design Suite. The VCU110 QDR2 memory component interface is a 40Ω impedance implementation. For more details about the Cypress QDR2+ component memory, see the Cypress... - Page 19 Chapter 1: VCU110 Evaluation Board Features Table 1-5: RLD3 Memory U141 36-bit I/F to FPGA U1 Banks 70 and 71 (Cont’d) FPGA (U1) Pin Schematic Net Name I/O Standard RLD3_36B_DQ4 SSTL12 RLD3_36B_DQ5 SSTL12 RLD3_36B_DQ6 SSTL12 RLD3_36B_DQ7 SSTL12 RLD3_36B_DQ8 SSTL12 RLD3_36B_DQ9...

- Page 20 Chapter 1: VCU110 Evaluation Board Features Table 1-5: RLD3 Memory U141 36-bit I/F to FPGA U1 Banks 70 and 71 (Cont’d) FPGA (U1) Pin Schematic Net Name I/O Standard RLD3_36B_QK0_N SSTL12 RLD3_36B_QK1_P DIFF_SSTL12 RLD3_36B_QK1_N DIFF_SSTL12 RLD3_36B_QK2_P DIFF_SSTL12 RLD3_36B_QK2_N DIFF_SSTL12 RLD3_36B_QK3_P...

- Page 21 Chapter 1: VCU110 Evaluation Board Features The connections between RLD3 component memory U173 and XCVU190 bank 72 are listed Table 1-6. Table 1-6: RLD3 Memory U173 18-bit I/F to FPGA U1 Bank 72 FPGA (U1) Pin Schematic Net Name I/O Standard...

- Page 22 RLD3 Design Guidelines section of LogiCORE IP UltraScale Architecture-Based FPGAs Memory Interface Solutions Product Guide (PG150) [Ref 3] for Vivado Design Suite. The VCU110 RLD3 memory component interface is a 40Ω impedance implementation. For more details about the Micron RLD3 component memory, see the Micron...

-

Page 23: Dual Quad-Spi Flash Memory

For details on Bank 0 pins, see the UltraScale Architecture Configuration User Guide (UG570) Note: [Ref Figure 1-6 shows the connections of the linear dual Quad-SPI flash memory on the VCU110 evaluation board. For more details, see the Micron N25QU512ABA8E12-0SIT data sheet [Ref 22]. - Page 24 Chapter 1: VCU110 Evaluation Board Features X-Ref Target - Figure 1-6 UTIL_3V3 VCC1V8 VCC1V8 VCC1V8 R894 R310 R893 4.7K 2.40K R350 R396 R395 1/10W 1/10W 4.7K 0.1UF 1/10W 1/10W QSPI0_VCC MT25QU512ABA8E12-0SIT QSPI0_IO3 FPGA_CCLK DQ3_HOLD_B QSPI0_IO0 RST_B_NC0 QSPI0_CS_B QSPI0_IO1 QSPI0_IO2 DQ2_W_B...

-

Page 25: Hybrid Memory Cube

Chapter 1: VCU110 Evaluation Board Features The connections between the dual Quad SPI components U182, U183 and XCVU190 banks 0 and 65 are listed in Table 1-7. Table 1-7: Dual-QSPI Memory U182, U183 I/F to FPGA U1 Banks 0 and 65... - Page 26 Chapter 1: VCU110 Evaluation Board Features The connections between the HMC component U160 Bank L0 and XCVU190 GTH Quads 229-232 are listed in Table 1-8. The nets with _C_P or _C_N in their net names are series capacitor coupled. Table 1-8: HMC Memory U160 L0 I/F to FPGA U1 GTH Quads 229-232...

- Page 27 Chapter 1: VCU110 Evaluation Board Features Table 1-8: HMC Memory U160 L0 I/F to FPGA U1 GTH Quads 229-232 (Cont’d) FPGA Connected Connected Pin Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Name Device HMC_L0TX_10_P MGTHTXP0_230...

- Page 28 Chapter 1: VCU110 Evaluation Board Features Table 1-8: HMC Memory U160 L0 I/F to FPGA U1 GTH Quads 229-232 (Cont’d) FPGA Connected Connected Pin Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Name Device HMC_L0TX_4_P MGTHTXP0_231...

- Page 29 Chapter 1: VCU110 Evaluation Board Features Table 1-8: HMC Memory U160 L0 I/F to FPGA U1 GTH Quads 229-232 (Cont’d) FPGA Connected Connected Pin Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Name Device HMC_L0TX_3_P MGTHTXP0_232...

- Page 30 Chapter 1: VCU110 Evaluation Board Features The connections between the HMC component U160 Bank L1 and XCVU190 GTH Quads (225-228) are listed in Table 1-9. The nets with _C_P or _C_N in their net names are series capacitor coupled. Table 1-9: HMC Memory U160 L1 I/F to FPGA U1 GTH Quads 225-228...

- Page 31 Chapter 1: VCU110 Evaluation Board Features Table 1-9: HMC Memory U160 L1 I/F to FPGA U1 GTH Quads 225-228 (Cont’d) FPGA Connected Connected Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Pin Name Device HMC_L1TX_4_P MGTHTXP0_226...

- Page 32 Chapter 1: VCU110 Evaluation Board Features Table 1-9: HMC Memory U160 L1 I/F to FPGA U1 GTH Quads 225-228 (Cont’d) FPGA Connected Connected Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Pin Name Device HMC_L1TX_11_P MGTHTXP0_227...

- Page 33 Chapter 1: VCU110 Evaluation Board Features Table 1-9: HMC Memory U160 L1 I/F to FPGA U1 GTH Quads 225-228 (Cont’d) FPGA Connected Connected Connected FPGA (U1) Pin Name (U1) Schematic Net Name Bank Pin Number Pin Name Device HMC_L1TX_12_P MGTHTXP0_228...

-

Page 34: Micro-Sd Card Interface

[Figure 1-2, callout 8] The VCU110 board includes a secure digital input/output (SDIO) interface to provide user access to general purpose nonvolatile micro-SD memory cards for configuration. The micro-SD card slot is designed to support 50 MHz high speed micro-SD cards. The SDIO signals are connected to U111 XC7Z010 Zynq SoC system controller Bank 500, which has its set to SYS_1V8 1.8V. -

Page 35: Usb Jtag Interface

(host side) to micro-B (VCU110 board side) USB cable. A 2 mm JTAG header (J3) is also provided in parallel for access by Xilinx download cables such as the Platform Cable USB II and the Parallel Cable IV. JTAG initiated configuration takes priority over the configuration method selected through the FPGA mode pins M[2:0], wired to SW16 positions [1:3]. -

Page 36: Jtag Chain Fmc Connector Bypass

VCU110 Evaluation Board Features JTAG Chain FMC Connector Bypass When an FMC mezzanine card is attached to the VCU110 board it is automatically added to the JTAG chain through electronically controlled single-pole single-throw (SPST) switches U26 (HPC0) and U132 (HPC1). The SPST switches are in a normally closed state and transition to an open state when an FMC mezzanine card is attached. - Page 37 J136 (PCIE_CABLE_CLK_C_P/N) USER_SMA_CLOCK J34(P)/J35(N) Two SMA input connectors J34/J35 (USER_SMA_CLOCK_P/N) Table 1-12 lists the VCU110 clock sources connections. Table 1-12: VCU110 Clock Sources to XCVU190 FPGA U1 Connections Clock Source Reference Connected Connection or FPGA Schematic Net Name I/O Standard...

- Page 38 Chapter 1: VCU110 Evaluation Board Features Table 1-12: VCU110 Clock Sources to XCVU190 FPGA U1 Connections (Cont’d) Clock Source Reference Connected Connection or FPGA Schematic Net Name I/O Standard Designator (U1) Bank and Pin U180.11 CFP4_SI5328_OUT1_BUF2_C_P AE36 GTY 125 REFCLK0 U180.12...

-

Page 39: System Clock

Chapter 1: VCU110 Evaluation Board Features Table 1-12: VCU110 Clock Sources to XCVU190 FPGA U1 Connections (Cont’d) Clock Source Reference Connected Connection or FPGA Schematic Net Name I/O Standard Designator (U1) Bank and Pin J34.1 USER_SMA_CLOCK_P LVDS AY27 J35.1 USER_SMA_CLOCK_N... - Page 40 Chapter 1: VCU110 Evaluation Board Features The 300 MHz system clock circuit is shown in Figure 1-8. X-Ref Target - Figure 1-8 VCC1V2_FPGA R1150 R1151 1.00K 1.00K 1/16W 1/16W SYSCLK_300_C_P SYSCLK_300_P SYS_1V8 C853 C852 C851 C850 C849 C848 SYSCLK_300_C_N SYSCLK_300_N 0.1UF...

-

Page 41: Programmable User Clock

On power-up, the U32 SI570 user clock defaults to an output frequency of 156.250 MHz. User applications can change the output frequency within the range of 10 MHz to 810 MHz through an I2C interface. Power cycling the VCU110 evaluation board resets the user clock to the default frequency of 156.250 MHz. -

Page 42: Jitter-Attenuating Clock Multipliers

1/16W Figure 1-10: HMC Jitter-Attenuating Clock Multiplier The VCU110 board second Silicon Labs SI5328C jitter attenuator U179 is on the back side of the board. FPGA U1 user logic can implement a clock recovery circuit and then output this clock to a differential I/O pair on I/O bank 128 (CFP4_REC_CLOCK2_C_P, U1 pin V34 and CFP4_REC_CLOCK2_C_N, U1 pin V35) for jitter attenuation. - Page 43 Chapter 1: VCU110 Evaluation Board Features The U179/U180 jitter attenuated clock multiplier circuit is shown in Figure 1-11. X-Ref Target - Figure 1-11 CFP4_SI5328_VCC UTIL_3V3 FERRITE-220 L104 C2071 10UF 6.3V UTIL_3V3 114.285MHZ C2069 CFP4_SI5328_XTAL_XA CFP4_SI5328_XTAL_XB 1/10W GND1 GND2 CFP4_SI5328_OUT1_BUF1_C_P R1484...

- Page 44 Chapter 1: VCU110 Evaluation Board Features The third SI5328 U181 jitter-attenuated clock multiplier circuit is shown in Figure 1-12. X-Ref Target - Figure 1-12 UTIL_3V3 C2081 1/10W EXAMAX_SI5328_OUT1_BUF1_C_P SI53340-B-GM R1490 EXAMAX_SI5328_OUT1_BUF1_C_N EXAMAX_SI5328_OUT1_BUF1_P CLK0_P Q0_P EXAMAX_SI5328_OUT1_BUF1_N CLK0_N Q0_N EXAMAX_SI5328_OUT1_BUF2_P UTIL_3V3 ILKN_EXAMAX_SI5328_VCC...

-

Page 45: User Sma Clock

User SMA Clock [Figure 1-2, callout 15] The VCU110 evaluation board provides an SMA pair for the user to source a differential LVDS clock to FPGA U1 Bank 67. USER_SMA_CLOCK_P and USER_SMA_CLOCK_N are connected to XCVU190 FPGA U1 (V 1.5V) HP Bank 67 GC pins AY27 and AY28, respectively. -

Page 46: Gty Transceivers

The GTY transceivers in the XCVU190 are grouped into four channels described as Quads. The reference clock for a Quad can be sourced from the Quad above or Quad below the GTY Quad of interest. There are thirteen GTY Quads (Banks 120-132) on the VCU110 board with connectivity as shown below: The VCU110 board provides access to 13 of 13 GTY transceiver Quads: •... - Page 47 Chapter 1: VCU110 Evaluation Board Features Quad 125: • REFCLK0 - CFP4_SI5328_OUT1_BUF2_C_P/N (U180) • REFCLK1 - not connected • Four GTY transceivers allocated to CFP4_MOD1_TX/RX[0:3]_P/N (J108) Quad 126: • REFCLK0 - BULLSEYE1_GTY_REFCLK0_C_P/N (J87) • REFCLK1 - BULLSEYE1_GTY_REFCLK1_C_P/N (J87) • Four GTY transceivers allocated to BULLSEYE1_GTY_TX/RX[0:3]_P/N (J87) Quad 127: •...

- Page 48 • Four GTY transceivers allocated to ILKN_TX/RX[16:19]_P/N (J121) Table 1-13 through Table 1-25 below list the VCU110 FPGA U1 GTY bank 120-122 and 124-133 connections, respectively. Table 1-13: VCU110 FPGA U1 GTY Quad 120 Connections Connected FPGA (U1) Pin FPGA (U1)

- Page 49 Chapter 1: VCU110 Evaluation Board Features Table 1-13: VCU110 FPGA U1 GTY Quad 120 Connections (Cont’d) Connected FPGA (U1) Pin FPGA (U1) Connected Connected Schematic Net Name Name Pin Name Device Number MGTREFCLK1P_120 AM34 MGTREFCLK1N_120 AM35 Notes: 1. MGT connections I/O standard not applicable.

- Page 50 Chapter 1: VCU110 Evaluation Board Features Table 1-15: VCU110 FPGA U1 GTY Quad 122 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_122 AW40 CFP4_MOD0_TX3_P TX3P--TX0P MGTYTXN0_122 AW41 CFP4_MOD0_TX3_N...

- Page 51 Chapter 1: VCU110 Evaluation Board Features Table 1-16: VCU110 FPGA U1 GTY Quad 124 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_124 AR40 BULLSEYE2_GTY_TX0_P MGTYTXN0_124 AR41 BULLSEYE2_GTY_TX0_N MGTYRXP0_124...

- Page 52 Chapter 1: VCU110 Evaluation Board Features Table 1-17: VCU110 FPGA U1 GTY Quad 125 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_125 AL40 CFP4_MOD1_TX3_P TX3P--TX0P MGTYTXN0_125 AL41 CFP4_MOD1_TX3_N...

- Page 53 Chapter 1: VCU110 Evaluation Board Features Table 1-18: VCU110 FPGA U1 GTY Quad 126 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_126 AG40 BULLSEYE1_GTY_TX0_P MGTYTXN0_126 AG41 BULLSEYE1_GTY_TX0_N MGTYRXP0_126...

- Page 54 Chapter 1: VCU110 Evaluation Board Features Table 1-19: VCU110 FPGA U1 GTY Quad 127 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_127 AC40 CFP4_MOD2_TX3_P TX3P--TX0P MGTYTXN0_127 AC41 CFP4_MOD2_TX3_N...

- Page 55 Chapter 1: VCU110 Evaluation Board Features Table 1-20: VCU110 FPGA U1 GTY Quad 128 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_128 CFP4_MOD3_TX3_P TX3P--TX0P MGTYTXN0_128 CFP4_MOD3_TX3_N TX3N--TX0N MGTYRXP0_128...

- Page 56 Chapter 1: VCU110 Evaluation Board Features Table 1-21: VCU110 FPGA U1 GTY Quad 129 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_129 ILKN_TX0_P TX0_P MGTYTXN0_129 ILKN_TX0_N TX0_N MGTYRXP0_129...

- Page 57 Chapter 1: VCU110 Evaluation Board Features Table 1-22: VCU110 FPGA U1 GTY Quad 130 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_130 ILKN_TX4_P TX4_P MGTYTXN0_130 ILKN_TX4_N TX4_N MGTYRXP0_130...

- Page 58 Chapter 1: VCU110 Evaluation Board Features Table 1-23: VCU110 FPGA U1 GTY Quad 131 Connections FPGA Schematic Connected Connected Connected FPGA (U1) Pin Name (U1) Pin Net Name Pin Number Pin Name Device MGTYTXP0_131 ILKN_TX8_P TX8_P MGTYTXN0_131 ILKN_TX8_N TX8_N MGTYRXP0_131...

- Page 59 Chapter 1: VCU110 Evaluation Board Features Table 1-24: VCU110 FPGA U1 GTY Quad 132 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_132 ILKN_TX12_P TX12_P MGTYTXN0_132 ILKN_TX12_N TX12_N MGTYRXP0_132...

- Page 60 Chapter 1: VCU110 Evaluation Board Features Table 1-25: VCU110 FPGA U1 GTY Quad 133 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_133 ILKN_TX16_P TX16_P MGTYTXN0_133 ILKN_TX16_N TX16_N MGTYRXP0_133...

-

Page 61: Gth Transceivers

The GTH transceivers in the XCVU190 are grouped into four channels described as Quads. The reference clock for a Quad can be sourced from the Quad above or Quad below the GTH Quad of interest. There are thirteen GTH Quads (banks 220-232) on the VCU110 board, with connectivity as shown here: Quad 220: •... - Page 62 Chapter 1: VCU110 Evaluation Board Features Quad 225: • REFCLK0 - not connected • REFCLK1 - not connected • Four GTH transceivers allocated to HMC_L1 TX and RX[0,1,2,6]_P/N (U160) Quad 226: • REFCLK0 - HMC_SI5328_OUT2_BUF2_C_P/N (U165) • REFCLK1 - not connected •...

- Page 63 • Four GTH transceivers allocated to PCIE_CABLE_TX and RX[0:3]_P/N (J136) Table 1-26 through Table 1-38 list the VCU110 FPGA U1 GTH Quads 220-222 and 224-233 connections, respectively. Table 1-26: VCU110 FPGA U1 GTH Quad 220 Connections FPGA Connected Connected Pin...

- Page 64 Chapter 1: VCU110 Evaluation Board Features Table 1-26: VCU110 FPGA U1 GTH Quad 220 Connections (Cont’d) FPGA Connected Connected Pin Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Name Device MGTREFCLK0P_220 AN11 MGTREFCLK0N_220 AN10 MGTREFCLK1P_220 AM13...

- Page 65 Chapter 1: VCU110 Evaluation Board Features Table 1-28: VCU110 FPGA U1 GTH Quad 222 Connections Connected FPGA (U1) Pin FPGA Connected Connected Schematic Net Name Name (U1) Pin Pin Name Device Number MGTHTXP0_222 FMC_HPC1_DP4_C2M_P DP4_C2M_P MGTHTXN0_222 FMC_HPC1_DP4_C2M_N DP4_C2M_N MGTHRXP0_222 FMC_HPC1_DP4_M2C_P...

- Page 66 Chapter 1: VCU110 Evaluation Board Features Table 1-29: VCU110 FPGA U1 GTH Quad 224 Connections FPGA Connected FPGA (U1) Pin Connected Connected (U1) Schematic Net Name Name Pin Name Device Number MGTHTXP0_224 FMC_HPC1_DP0_C2M_P DP0_C2M_P MGTHTXN0_224 FMC_HPC1_DP0_C2M_N DP0_C2M_N MGTHRXP0_224 FMC_HPC1_DP0_M2C_P DP0_M2C_P...

- Page 67 Chapter 1: VCU110 Evaluation Board Features Table 1-30: VCU110 FPGA U1 GTH Quad 225 Connections FPGA (U1) Schematic Net Connected Pin Connected Pin Connected FPGA (U1) Pin Name Name Number Name Device MGTHTXP0_225 HMC_L1TX_0_P AD18 L1RXP_0 MGTHTXN0_225 HMC_L1TX_0_N AD17 L1RXN_0...

- Page 68 Chapter 1: VCU110 Evaluation Board Features Table 1-31: VCU110 FPGA U1 GTH Quad 226 Connections Connected FPGA (U1) Pin FPGA Connected Connected Schematic Net Name Name (U1) Pin Pin Name Device Number MGTHTXP0_226 HMC_L1TX_4_P AF20 L1RXP_4 MGTHTXN0_226 HMC_L1TX_4_N AF19 L1RXN_4...

- Page 69 Chapter 1: VCU110 Evaluation Board Features Table 1-32: VCU110 FPGA U1 GTH Quad 227 Connections FPGA Connected Pin Connected Pin Connected FPGA (U1) Pin Name (U1) Schematic Net Name Number Name Device MGTHTXP0_227 HMC_L1TX_11_P AG29 L1RXP_11 MGTHTXN0_227 HMC_L1TX_11_N AG28 L1RXN_11...

- Page 70 Chapter 1: VCU110 Evaluation Board Features Table 1-33: VCU110 FPGA U1 GTH Quad 228 Connections FPGA (U1) Connected Connected Pin Connected FPGA (U1) Pin Name Schematic Net Name Pin Number Name Device MGTHTXP0_228 HMC_L1TX_12_P AC25 L1RXP_12 MGTHTXN0_228 HMC_L1TX_12_N AC24 L1RXN_12...

- Page 71 Chapter 1: VCU110 Evaluation Board Features Table 1-34: VCU110 FPGA U1 GTH Quad 229 Connections Schematic Net Connected Connected Pin Connected FPGA (U1) Pin Name FPGA (U1) Pin Name Pin Number Name Device MGTHTXP0_229 HMC_L0TX_12_P L0RXP_12 MGTHTXN0_229 HMC_L0TX_12_N L0RXN_12 MGTHRXP0_229...

- Page 72 Chapter 1: VCU110 Evaluation Board Features Table 1-35: VCU110 FPGA U1 GTH Quad 230 Connections FPGA Connected Connected Pin Connected FPGA (U1) Pin Name (U1) Schematic Net Name Name Device Number MGTHTXP0_230 HMC_L0TX_10_P L0RXP_10 MGTHTXN0_230 HMC_L0TX_10_N L0RXN_10 MGTHRXP0_230 HMC_L0RX_10_C_P L0TXP_10...

- Page 73 Chapter 1: VCU110 Evaluation Board Features Table 1-36: VCU110 FPGA U1 GTH Quad 231 Connections FPGA (U1) Connected Connected Pin Connected FPGA (U1) Pin Name Schematic Net Name Pin Number Name Device MGTHTXP0_231 HMC_L0TX_4_P L0RXP_4 MGTHTXN0_231 HMC_L0TX_4_N L0RXN_4 MGTHRXP0_231 HMC_L0RX_4_C_P...

- Page 74 Chapter 1: VCU110 Evaluation Board Features Table 1-37: VCU110 FPGA U1 GTH Quad 232 Connections FPGA (U1) Pin FPGA (U1) Connected Connected Pin Connected Schematic Net Name Name Pin Number Name Device MGTHTXP0_232 HMC_L0TX_3_P L0RXP_3 MGTHTXN0_232 HMC_L0TX_3_N L0RXN_3 MGTHRXP0_232 HMC_L0RX_3_C_P...

- Page 75 Chapter 1: VCU110 Evaluation Board Features Table 1-38: VCU110 FPGA U1 GTH Quad 233 Connections FPGA (U1) Connected Connected Pin Connected FPGA (U1) Pin Name Schematic Net Name Pin Number Name Device MGTHTXP0_233 PCIE_CABLE_TX3_C_P PETP3 MGTHTXN0_233 PCIE_CABLE_TX3_C_N PETN3 MGTHRXP0_233 PCIE_CABLE_RX3_P...

-

Page 76: Pci Express Endpoint Connectivity

REFCLK0 pins of GTH Quad 233. The PCIe J136 connection to FPGA U1 GTH Quad 233 is detailed in Table 1-39. Table 1-39: VCU110 PCIe Cable Connector J136 to FPGA U1 GTH Quad 233 Connections FPGA (U1) Pin Name FPGA (U1) Connected Connected Pin... -

Page 77: Cfp Module Quad Connectors (Cfp4)

[Figure 1-2, callout 17] The VCU110 board contains a 100G C form-factor pluggable (CFP) Quad connector assembly comprised of four sub-module assemblies (J107-J110), each of which accepts a CFP optical module. The connector is housed within a single CFP4 cage assembly. - Page 78 The CFP module J107-J110 connections to the GTY Quads 122, 125, 127 and 128 are detailed in Table 1-40 through Table 1-42. Table 1-40: VCU110 FPGA U1 GTY Quad 122 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name...

- Page 79 Chapter 1: VCU110 Evaluation Board Features Table 1-41: VCU110 FPGA U1 GTY Quad 125 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_125 CFP4_MOD1_TX3_P TX3P--TX0P MGTYTXN0_125 CFP4_MOD1_TX3_N TX3N--TX0N MGTYRXP0_125...

- Page 80 Chapter 1: VCU110 Evaluation Board Features Table 1-42: VCU110 FPGA U1 GTY Quad 127 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_127 CFP4_MOD2_TX3_P TX3P--TX0P MGTYTXN0_127 CFP4_MOD2_TX3_N TX3N--TX0N MGTYRXP0_127...

- Page 81 Chapter 1: VCU110 Evaluation Board Features Table 1-43: VCU110 FPGA U1 GTY Quad 128 Connections FPGA Connected Connected Connected FPGA (U1) Pin Name Schematic Net Name (U1) Pin Pin Number Pin Name Device MGTYTXP0_128 CFP4_MOD3_TX3_P TX3P--TX0P MGTYTXN0_128 CFP4_MOD3_TX3_N TX3N--TX0N MGTYRXP0_128...

-

Page 82: 10/100/1,000Mb/S Tri-Speed Ethernet Phy

[Figure 1-2, callout 18] The VCU110 evaluation board uses the Marvell Alaska PHY device (88E1111) at U58 for Ethernet communications at 10 Mb/s, 100 Mb/s, or 1,000 Mb/s. The board supports SGMII mode only. The PHY connection to a user-provided Ethernet cable is through RJ-45 connector P3, a Halo HFJ11-1G01E-L12RL with built-in magnetics and status LEDs. - Page 83 Chapter 1: VCU110 Evaluation Board Features Table 1-45 details the FPGA U1 to U58 M88E111 Ethernet PHY connections. Table 1-45: FPGA U1 to Ethernet PHY U58 Connections M88E111 PHY U58 FPGA (U1) Pin Net Name I/O Standard Name BB21 PHY_MDIO...

-

Page 84: Ethernet Phy Status Leds

The Ethernet PHY status LEDs are integrated into the metal frame of the P3 RJ-45 connector. These LEDs are visible on the left edge of the VCU110 board when it is installed into a PCIe slot in a PC chassis. The two PHY status LEDs are integrated within the frame of the RJ45... -

Page 85: I2C Bus, Topology And Bus Switches

For more technical information on the CP2105GM and the VCP drivers, visit the Silicon Labs website [Ref 26]. Xilinx UART IP is expected to be implemented in the FPGA logic using IP like the LogiCORE IP AXI UART Lite v2.0 Product Guide for Vivado Design Suite (PG142) [Ref 10]. - Page 86 Chapter 1: VCU110 Evaluation Board Features The VCU110 evaluation board I2C bus topology overview is shown in Figure 1-16. X-Ref Target - Figure 1-16 12V_SW Maxim power regulators X10 – x18 UTIL_3V3 to SYS_1V8 PMBUS SDA, SYS_1V8 Level Maxim MAXIM_CABLE_B...

- Page 87 Chapter 1: VCU110 Evaluation Board Features A zoomed in view of the I2C bus switches is shown in Figure 1-17. X-Ref Target - Figure 1-17 Figure 1-17: I2C Bus IIC_MAIN Bus Switches User applications that communicate with devices on one of the downstream I2C buses must first set up a path to the desired bus through the U28 or U80 bus switch at I2C address 0x74 (0b1110100) or 0x75 (0b1110101) respectively.

-

Page 88: Status And User Leds

Technical Reference Manual (UG585) [Ref 13]. Status and User LEDs [Figure 1-2, callout 23] Table 1-48 defines VCU110 board status and user LEDs. Table 1-48: VCU110 Board Status and User LEDs Reference Designator Description INIT OR'D POWER GOOD GPIO_LED_1 GPIO_LED_0 GPIO_LED_2... - Page 89 Chapter 1: VCU110 Evaluation Board Features Table 1-48: VCU110 Board Status and User LEDs (Cont’d) Reference Designator Description DS16 VCC1V2_PGOOD DS17 MGTAVTT_PGOOD DS19 VADJ_1V8_PGOOD DS21 VCCINT_PGOOD DS24 VCC1V8_PGOOD DS25 MGTVCCAUX_PGOOD DS26 12V ON DS27 SYS_2V5 ON DS28 SYS_1V8 ON DS31...

-

Page 90: User I/O

Chapter 1: VCU110 Evaluation Board Features User I/O [Figure 1-2, callouts 23-26] The VCU110 board provides the following user and general purpose I/O capabilities: • Eight user LEDs (callout 23) GPIO_LED [7-0]: DS31, DS32, DS33, DS10, DS9, DS8, DS6, DS7 °... -

Page 91: User Pushbuttons

Chapter 1: VCU110 Evaluation Board Features User Pushbuttons [Figure 1-2, callout 24] Figure 1-19 shows the user pushbuttons circuit. X-Ref Target - Figure 1-19 VADJ_1V8_FPGA R839 1/10W Pushbutton TL3301EF100QG GPIO_SW_N SW10 4.70K 1/16W VADJ_1V8_FPGA VCC1V2_FPGA VADJ_1V8_FPGA R840 R838 R841 1/10W... -

Page 92: Cpu Reset Pushbutton

Chapter 1: VCU110 Evaluation Board Features CPU Reset Pushbutton [Figure 1-2, callout 25] Figure 1-20 shows the CPU reset pushbutton circuit. X-Ref Target - Figure 1-20 VCC1V2_FPGA Pushbutton TL3301EF100QG CPU_RESET 4.70K 1/16W Figure 1-20: CPU Reset Pushbutton VCU110 Evaluation Board www.xilinx.com... -

Page 93: Gpio Dip Switch

4.70KΩ 4.70KΩ 1/16W 1/16W Figure 1-21: CPU GPIO DIP Switch Table 1-49 lists the GPIO Connections to FPGA U1. Table 1-49: VCU110 GPIO Connections to FPGA U1 FPGA Pin (U1) Schematic Net Name I/O Standard GPIO GPIO LEDs (Active-High) GPIO_LED_0 LVCMOS12 DS7.1... -

Page 94: User Pmod Gpio Header

User PMOD GPIO Header [Figure 1-2, callout 29] The VCU110 evaluation board supports one right-angle (FEMALE) PMOD GPIO receptacle J52. The PMOD nets connected to J52 are accessed through level-shifter U41 (PMOD0). The level-shifter is wired to XCVU190 FPGA U1 bank71. -

Page 95: Switches

[Figure 1-2, callout 30] The VCU110 board power switch is SW1. Sliding the switch actuator from the off to on position applies 12VDC power from the power input connector J15. Green LED DS26 illuminates when the VCU110 board 12V power is on. See the VCU110 Board Power System section for details on the onboard power system. - Page 96 The VCU110 Evaluation Kit provides the adapter cable shown in Figure 1-23 for powering the VCU110 board from the ATX power supply 4-pin peripheral connector. The Xilinx part number for this cable is 2600304, and is equivalent to Sourcegate Technologies part number is AZCBL-WH-1109.

- Page 97 Chapter 1: VCU110 Evaluation Board Features Program_B Pushbutton Switch [Figure 1-2, callout 27] Switch SW4 grounds the XCVU190 FPGA U1 PROGRAM_B pin when pressed. This action clears the FPGA programmable logic configuration. The FPGA_PROG_B signal is connected to XCVU190 FPGA U1 pin AE14.

-

Page 98: Samtec Bullseye1 Connector

1-2, callout 40] The VCU110 board provides two compact, multi-connector surface mount pad patterns. Each pad pattern implements 20 connections configured on the VCU110 board as 10 differential pairs. BULLSEYE1 (J87) is connected to FPGA U1 MGTY Bank 126. Figure 1-26 shows BULLSEYE1 J87. - Page 99 Chapter 1: VCU110 Evaluation Board Features BULLSEYE1 J87 connections are detailed in Table 1-51. Table 1-51: VCU110 BULLSEYE1 SMA J87 to FPGA U1 Connections GTY Quad 126 BULLSEYE1 FPGA (U1) FPGA (U1) Pin J87 Pin Schematic Net Name MGT Quad...

-

Page 100: Samtec Bullseye2 Connector

Chapter 1: VCU110 Evaluation Board Features Samtec BULLSEYE2 Connector [Figure 1-2, callout 42] BULLSEYE2 is connected to FPGA U1 MGTY Bank 124. Figure 1-27 shows BULLSEYE2 J122. X-Ref Target - Figure 1-27 CCC-J-020 BULLSEYE2_GTY_REFCLK1_P BULLSEYE2_GTY_REFCLK1_N BULLSEYE2_GTY_RX3_P BULLSEYE2_GTY_RX3_N BULLSEYE2_GTY_TX3_P BULLSEYE2_GTY_TX3_N BULLSEYE2_GTY_TX2_P... - Page 101 Chapter 1: VCU110 Evaluation Board Features BULLSEYE2 J122 connections are detailed in Table 1-52. Table 1-52: VCU110 BULLSEYE2 SMA J122 to FPGA U1 Connections GTY Quad 124 BULLSEYE2 FPGA (U1) J122 Pin Schematic Net Name FPGA (U1) Pin Name MGT Quad...

-

Page 102: Pcie Cable Connector

Chapter 1: VCU110 Evaluation Board Features PCIe Cable Connector [Figure 1-2, callout 16] The PCIe cable connector is connected to FPGA U1 GTH Quad 233. Figure 1-28 shows the J136 connector. The TX_P/N pairs and the CLK_P/N pair are series capacitor coupled to Bank 233. - Page 103 FPGAs Gen3 Integrated Block for PCI Express v1.0 Product Guide for Vivado Design Suite (PG156) [Ref 8]. See [Ref 27] for additional information about the PCI Express® standard. Table 1-53: VCU110 PCIe Cable Conn. J136 to FPGA U1 Connections GTH Quad 233 FPGA Connected Connected Pin Connected FPGA (U1) Pin Name...

-

Page 104: Interlaken Connector

[Figure 1-2, callout 42] The VCU110 board provides an FCI Interlaken connector at J121. Five FPGA U1 GTY Quads (129-133) implement twenty transmit/receive differential pair channels. The Interlaken connector DATA, CLK and SYNC control signals are connected to FPGA U1 Bank 65. - Page 105 Chapter 1: VCU110 Evaluation Board Features Table 1-54: VCU110 Interlaken Connector J121 Connections (Cont’d) Interlaken Interlaken FPGA FPGA (U1) Pin J121 Pin J121 Pin Schematic Net Name FPGA U1 Bank (U1) Pin Name Name Number TX4_P ILKN_TX4_P MGTYTXP0_130 TX4_N ILKN_TX4_N...

- Page 106 Chapter 1: VCU110 Evaluation Board Features Table 1-54: VCU110 Interlaken Connector J121 Connections (Cont’d) Interlaken Interlaken FPGA FPGA (U1) Pin J121 Pin J121 Pin Schematic Net Name FPGA U1 Bank (U1) Pin Name Name Number TX12_P ILKN_TX12_P MGTYTXP0_132 TX12_N ILKN_TX12_N...

- Page 107 Chapter 1: VCU110 Evaluation Board Features Table 1-54: VCU110 Interlaken Connector J121 Connections (Cont’d) Interlaken Interlaken FPGA FPGA (U1) Pin J121 Pin J121 Pin Schematic Net Name FPGA U1 Bank (U1) Pin Name Name Number TX20_P TX20_N RX20_P RX20_N TX21_P...

-

Page 108: Examax Backplane Connector

ExaMAX Backplane Connector [Figure 1-2, callout 43] The VCU110 board provides an FCI ExaMAX backplane connector at J116. Two FPGA U1 GTY Quads (121 and 120) implement eight differential transmit/receive pair channels. The ExaMAX J116 to FPGA U1 connections are detailed in Table 1-55. -

Page 109: Fpga Mezzanine Card (Fmc) Interface

Chapter 1: VCU110 Evaluation Board Features Table 1-55: VCU110 ExaMAX J116 to FPGA U1 GTY Quads 121-120 Connections (Cont’d) ExaMAX ExaMAX J116 Schematic Net FPGA (U1) FPGA (U1) Pin J116 Pin MGT Quad Pin Number Name Name Name TX5_P EXAMAX_TX5_P... -

Page 110: Fmc Hpc0 Connector J22

• 1 differential clock • 159 ground and 15 power connections The VCU110 board FMC V voltage VADJ_1V8_FPGA for the J22 and J2 FMC connectors is determined by the MAX15301 U30 voltage regulator described in the VCU110 Board Power System section. - Page 111 Chapter 1: VCU110 Evaluation Board Features The HPC0 J22 connections to FPGA U1 are shown in Table 1-56 through Table 1-60. Table 1-56: J22 VITA 57.1 FMC HPC0 Sections A and B to FPGA U1 Connections Schematic Schematic FPGA FPGA...

- Page 112 Chapter 1: VCU110 Evaluation Board Features Table 1-57: J22 VITA 57.1 FMC HPC0 Sections C and D to FPGA U1 Connections Schematic Schematic FPGA FPGA HPC0 Net Name Standard HPC0 Net Name Standard FMC_HPC0_DP0_C2M_P VADJ_1V8_PGOOD LVCMOS18 AP18 FMC_HPC0_DP0_C2M_N FMC_HPC0_GBTCLK0_M2C_P AL11...

- Page 113 Chapter 1: VCU110 Evaluation Board Features Table 1-58: J22 VITA 57.1 FMC HPC0 Sections E and F to FPGA U1 Connections Schematic Schematic U1 FPGA FPGA HPC0 Net Name Standard HPC0 Net Name Standard FMC_HPC0_PG_M2C LVCMOS18 BD20 VADJ _1V8_FPGA VADJ _1V8_FPGA Notes: 1.

- Page 114 Chapter 1: VCU110 Evaluation Board Features Table 1-59: J22 VITA 57.1 FMC HPC0 Sections G and H to FPGA U1 Connections Schematic Schematic U1 FPGA FPGA HPC0 Net Name Standard HPC0 Net Name Standard FMC_HPC0_VREF_A_M2C (1)(2) FMC_HPC0_PRSNT_M2C_B LVCMOS18 FMC_HPC0_LA00_CC_P LVDS...

-

Page 115: Fmc Hpc1 Connector J2

Chapter 1: VCU110 Evaluation Board Features Table 1-60: J22 VITA 57.1 FMC HPC0 Sections J and K to FPGA U1 Connections Schematic Schematic U1 FPGA FPGA HPC0 Net Name Standard HPC0 Net Name Standard FMC HPC1 Connector J2 [Figure 1-2, callout 34] The HPC connector at J2 implements a subset of the full FMC HPC connectivity: •... - Page 116 Chapter 1: VCU110 Evaluation Board Features • 2 GT clocks • 1 differential clock • 159 ground and 15 power connections The HPC1 J2 connections to FPGA U1 are shown in Table 1-61 through Table 1-65. Table 1-61: J2 VITA 57.1 FMC HPC1 Sections A and B to FPGA U1 Connections...

- Page 117 Chapter 1: VCU110 Evaluation Board Features Table 1-62: J2 VITA 57.1 FMC HPC1 Sections C and D to FPGA U1 Connections Schematic Schematic FPGA FPGA HPC1 Net Name Standard HPC1 Net Name Standard FMC_HPC1_DP0_C2M_P VADJ_1V8_PGOOD LVCMOS18 AP18 FMC_HPC1_DP0_C2M_N FMC_HPC1_GBTCLK0_M2C_P AG11...

- Page 118 Chapter 1: VCU110 Evaluation Board Features Table 1-63: J2 VITA 57.1 FMC HPC1 Sections E and F to FPGA U1 Connections Schematic Schematic FPGA FPGA HPC1 Net Name Standard HPC1 Net Name Standard FMC_HPC1_PG_M2C LVCMOS18 BA21 VADJ_1V8_FPGA VADJ_1V8_FPGA VCU110 Evaluation Board www.xilinx.com...

- Page 119 Chapter 1: VCU110 Evaluation Board Features Table 1-64: J2 VITA 57.1 FMC HPC1 Sections G and H to FPGA U1 Connections Schematic Net Name FPGA Schematic Net Name FPGA HPC1 Standard HPC1 Standard FMC_HPC1_VREF_A_M2C FMC_HPC1_PRSNT_M2C_B AP21 AV33 AU33 FMC_HPC1_LA00_CC_P LVCMOS18...

-

Page 120: Vcu110 Board Power System

Standard HPC1 Net Name Standard VCU110 Board Power System The VCU110 hosts a Maxim PMBus based power system. Each individual Maxim MAX20751EKX or MAX15301 voltage regulator has a PMBus interface. Figure 1-29 shows the VCU110 power system block diagram. VCU110 Evaluation Board www.xilinx.com... - Page 121 Page 89 VCC1V5 QDR2_VTERM_0V75 Reg. @ 3A Page 90 VCC1V2 RLD3_VTERM_0V6 Reg. 0.6 @ 3A Page 90 SYS_5V0 Regulator @ 1A Page 88 Figure 1-29: VCU110 Power System Block Diagram VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 122 Chapter 1: VCU110 Evaluation Board Features The VCU110 evaluation board uses power regulators and PMBus compliant POL controllers from Maxim Integrated Circuits to supply the core and auxiliary voltages listed in Table 1-66. Table 1-66: Onboard Power System Devices Power...

-

Page 123: Monitoring Voltage And Current

SYSMON Power System Measurement UltraScale FPGAs provide an analog front end (SYSMON) block. The SYSMON contains a single 10-bit 0.2 MSPS ADC. The VCU110 board SYSMON ADC interface includes current measuring capability for all Maxim power controller sourced rails. The Maxim PowerTool GUI can display the rail voltage for all Maxim power controller sourced rails. - Page 124 Chapter 1: VCU110 Evaluation Board Features Several rail current measurements are made available to SYSMON through an Analog Devices ADG707BRU multiplexer U75. Each Maxim controlled rail has a TI INA333 op amp strapped across a series current sense resistors' Kelvin terminals. This op amp has its gain adjusted to give 0.75V - 1V at the expected full scale current value for the rail.

- Page 125 Chapter 1: VCU110 Evaluation Board Features Table 1-67 lists the VCU110 board SYSMON power system voltage and current measurement details for the external U75 MUX. Table 1-67: VCU110 Board SYSMON Measurements through MUX U75 Isense Op Amp 8-to-1 Mux. U75...

-

Page 126: Sysmon Headers J80, J81

Figure 1-31. The fan turns on when the VCU110 is powered on due to pull-up resistor R422. The SM_FAN_PWM and SM_FAN_TACH signals are wired to XCVU190 FPGA U1 Bank 65 pins AT21 and AT19 respectively, enabling the user to implement their own fan speed control IP in the FPGA U1 logic. -

Page 127: Vcu110 Zynq-7000 Ap Soc Xc7Z010 System Controller

The system controller is an ease-of-use feature that sets up or queries onboard resources available to the XCVU190 UltraScale FPGA U1 on the VCU110. Programmable clocks, the internal UltraScale FPGA system monitor block (SYSMON), and the Maxim power controllers VCU110 Evaluation Board www.xilinx.com... - Page 128 Chapter 1: VCU110 Evaluation Board Features are accessible through an I2C interface connected to both the system controller and the FPGA. A Silicon Labs Si570 programmable low-jitter clock is used to provide a system clock for FPGA designers. Through a UART (115200-8-N-1) text interface, the system clock (Si570) can be set to any frequency between 10 MHz and 810 MHz.

-

Page 129: Appendix A: Default Switch And Jumper Settings

Appendix A Default Switch and Jumper Settings The default switch and jumper settings for the VCU110 evaluation board are provided in this appendix. Switches Default switch settings are listed in Table A-1. Table A-1: Default Switch Settings Figure 1-2 Schematic... -

Page 130: Jumpers

U1 VP pin V12 pull down SYSMON_VP 20.5KΩ to GND U1 VN pin W11 pull down SYSMON_VN 20.5KΩ to GND X-Ref Target - Figure A-1 Figure A-1: VCU110 Board Jumper Header Locations VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016... -

Page 131: Appendix B: Vita 57.1 Fmc Connector Pinouts

Figure B-1 shows the pinout of the FPGA mezzanine card (FMC) high pin count (HPC) connector defined by the VITA 57.1 FMC specification. For a description of how the VCU110 evaluation board implements the FMC specification, see FPGA Mezzanine Card (FMC) Interface, page 109. -

Page 132: Appendix C: Getting Started With System Controller

Appendix C Getting Started with System Controller Overview The Xilinx system controller is an ease-of-use application that runs at power-up on all UltraScale FPGA evaluation boards. These select board features can be controlled and monitored: • Programmable clocks • Power system monitoring (PMBus) •... - Page 133 (UG1036) [Ref 20]. 3. With the VCU110 evaluation board power turned off, install the USB cable supplied in the VCU110 evaluation board kit (standard type-A end to host computer, type Micro-B end to VCU110 evaluation board connector J4). 4. Turn on the VCU110 evaluation board. The PC recognizes that new hardware is connected, and runs the driver installation wizard to complete the installation of the CP2015GM bridge chip drivers.

-

Page 134: Appendix D: Master Constraints File Listing

Master Constraints File Listing Overview The master Xilinx design constraints (XDC) file template for the VCU110 board provides for designs targeting the VCU110 evaluation board. Net names in the constraints file correlate with net names on the latest VCU110 evaluation board schematic. Identify the appropriate pins and replace the net names with net names in the user RTL. - Page 135 PACKAGE_PIN N37 [get_ports "ILKN_SI5328_OUT2_BUF3_C_N"] set_property PACKAGE_PIN N36 [get_ports "ILKN_SI5328_OUT2_BUF3_C_P"] set_property PACKAGE_PIN L37 [get_ports "ILKN_SI5328_OUT2_BUF4_C_N"] set_property PACKAGE_PIN L36 [get_ports "ILKN_SI5328_OUT2_BUF4_C_P"] set_property PACKAGE_PIN J37 [get_ports "ILKN_SI5328_OUT2_BUF5_C_N"] set_property PACKAGE_PIN J36 [get_ports "ILKN_SI5328_OUT2_BUF5_C_P"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 136 IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_D0"] set_property PACKAGE_PIN AM24 [get_ports "QDR2_18B_D1"] set_property IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_D1"] set_property PACKAGE_PIN AN23 [get_ports "QDR2_18B_D2"] set_property IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_D2"] set_property PACKAGE_PIN AP22 [get_ports "QDR2_18B_D3"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 137 PACKAGE_PIN AW26 [get_ports "QDR2_18B_Q12"] set_property IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_Q12"] set_property PACKAGE_PIN AU28 [get_ports "QDR2_18B_Q13"] set_property IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_Q13"] set_property PACKAGE_PIN AU27 [get_ports "QDR2_18B_Q14"] set_property IOSTANDARD HSTL_I_DCI [get_ports "QDR2_18B_Q14"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 138 IOSTANDARD SSTL12 [get_ports "RLD3_18B_BA2"] set_property PACKAGE_PIN G20 [get_ports "RLD3_18B_BA3"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_18B_BA3"] set_property PACKAGE_PIN K16 [get_ports "RLD3_18B_DQ0"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_18B_DQ0"] set_property PACKAGE_PIN L15 [get_ports "RLD3_18B_DQ1"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 139 PACKAGE_PIN J15 [get_ports "RLD3_18B_QVLD0"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_18B_QVLD0"] set_property PACKAGE_PIN D19 [get_ports "RLD3_18B_CK_N"] set_property IOSTANDARD DIFF_SSTL12 [get_ports "RLD3_18B_CK_N"] set_property PACKAGE_PIN D20 [get_ports "RLD3_18B_CK_P"] set_property IOSTANDARD DIFF_SSTL12 [get_ports "RLD3_18B_CK_P"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 140 IOSTANDARD SSTL12 [get_ports "RLD3_36B_DQ6"] set_property PACKAGE_PIN C29 [get_ports "RLD3_36B_DQ7"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_36B_DQ7"] set_property PACKAGE_PIN B28 [get_ports "RLD3_36B_DQ8"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_36B_DQ8"] set_property PACKAGE_PIN K29 [get_ports "RLD3_36B_DQ9"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 141 PACKAGE_PIN E28 [get_ports "RLD3_36B_DM0"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_36B_DM0"] set_property PACKAGE_PIN L30 [get_ports "RLD3_36B_DM1"] set_property IOSTANDARD SSTL12 [get_ports "RLD3_36B_DM1"] set_property PACKAGE_PIN G23 [get_ports "RLD3_36B_DK0_N"] set_property IOSTANDARD DIFF_SSTL12 [get_ports "RLD3_36B_DK0_N"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 142 PACKAGE_PIN AV30 [get_ports "HMC_REFCLK_SEL"] set_property IOSTANDARD LVCMOS15 [get_ports "HMC_REFCLK_SEL"] set_property PACKAGE_PIN AW30 [get_ports "HMC_FERR_B"] set_property IOSTANDARD LVCMOS15 [get_ports "HMC_FERR_B"] set_property PACKAGE_PIN AW28 [get_ports "HMC_P_RST_B"] set_property IOSTANDARD LVCMOS15 [get_ports "HMC_P_RST_B"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 143 PACKAGE_PIN BA31 [get_ports "FMC_HPC0_LA07_P"] set_property IOSTANDARD LVDS [get_ports "FMC_HPC0_LA07_P"] set_property PACKAGE_PIN BB31 [get_ports "FMC_HPC0_LA07_N"] set_property IOSTANDARD LVDS [get_ports "FMC_HPC0_LA07_N"] set_property PACKAGE_PIN BE29 [get_ports "FMC_HPC0_LA08_P"] set_property IOSTANDARD LVDS [get_ports "FMC_HPC0_LA08_P"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 144 IOSTANDARD LVDS [get_ports "FMC_HPC1_LA06_P"] set_property PACKAGE_PIN AT36 [get_ports "FMC_HPC1_LA06_N"] set_property IOSTANDARD LVDS [get_ports "FMC_HPC1_LA06_N"] set_property PACKAGE_PIN AV35 [get_ports "FMC_HPC1_LA07_P"] set_property IOSTANDARD LVDS [get_ports "FMC_HPC1_LA07_P"] set_property PACKAGE_PIN AW35 [get_ports "FMC_HPC1_LA07_N"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 145 PACKAGE_PIN BC25 [get_ports "TX_DIS_MOD2_CFP4_LS"] set_property IOSTANDARD LVCMOS15 [get_ports "TX_DIS_MOD2_CFP4_LS"] set_property PACKAGE_PIN AP26 [get_ports "MOD_ABS_MOD2_CFP4_LS"] set_property IOSTANDARD LVCMOS15 [get_ports "MOD_ABS_MOD2_CFP4_LS"] set_property PACKAGE_PIN AN30 [get_ports "MOD_LOPWR_MOD2_CFP4_LS"] set_property IOSTANDARD LVCMOS15 [get_ports "MOD_LOPWR_MOD2_CFP4_LS"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 146 PACKAGE_PIN AN20 [get_ports "ILKN_FC_RX_SYNC_LS"] set_property IOSTANDARD LVCMOS18 [get_ports "ILKN_FC_RX_SYNC_LS"] set_property PACKAGE_PIN AW17 [get_ports "ILKN_FC_TX_CLK_LS"] set_property IOSTANDARD LVCMOS18 [get_ports "ILKN_FC_TX_CLK_LS"] set_property PACKAGE_PIN AN21 [get_ports "ILKN_FC_TX_DATA_LS"] set_property IOSTANDARD LVCMOS18 [get_ports "ILKN_FC_TX_DATA_LS"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 147 PACKAGE_PIN AM16 [get_ports "GPIO_SW_W"] set_property IOSTANDARD LVCMOS18 [get_ports "GPIO_SW_W"] set_property PACKAGE_PIN AY13 [get_ports "GPIO_SW_E"] set_property IOSTANDARD LVCMOS18 [get_ports "GPIO_SW_E"] set_property PACKAGE_PIN L26 [get_ports "GPIO_SW_C"] set_property IOSTANDARD LVCMOS12 [get_ports "GPIO_SW_C"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 148 IOSTANDARD LVCMOS18 [get_ports "PMBUS_ALERT_FPGA"] set_property PACKAGE_PIN K24 [get_ports "MAXIM_CABLE_B_FPGA"] set_property IOSTANDARD LVCMOS12 [get_ports "MAXIM_CABLE_B_FPGA"] # PCIE CABLE CONNECTOR set_property PACKAGE_PIN AN16 [get_ports "PCIE_CABLE_FPGA_CPERST_B"] set_property IOSTANDARD LVCMOS18 [get_ports "PCIE_CABLE_FPGA_CPERST_B"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

- Page 149 Appendix D: Master Constraints File Listing # 1.8V POWER GOOD set_property PACKAGE_PIN AP18 [get_ports "VADJ_1V8_PGOOD_LS"] set_property IOSTANDARD LVCMOS18 [get_ports "VADJ_1V8_PGOOD_LS"] VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016...

-

Page 150: Appendix E: Board Setup

Appendix E Board Setup See the VCU110 Board Interface Test Tutorial on xilinx.com/vcu110 to get started using the evaluation board. This tutorial provides instructions for setting up the board to test all the internal and external board interfaces. VCU110 Evaluation Board www.xilinx.com... -

Page 151: Appendix F: Board Specifications

Thickness (± 10%): 0.150 inch (0.381 cm) Length: 14.45 inches (36.7 centimeters) Environmental Temperature Operating: 0°C to +45°C Storage: –25°C to +60°C Humidity 10% to 90% non-condensing Operating Voltage +12 V VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016... -

Page 152: Appendix G: Regulatory And Compliance Information

This product is designed and tested to conform to the European Union directives and standards described in this section. Refer to the VCU110 board master answer record concerning the CE requirements for the PC Test Environment: VCU110 Evaluation Kit Master — Answer Record (AR 62604) -

Page 153: Standards

This product complies with Directive 2002/95/EC on the restriction of hazardous substances (RoHS) in electrical and electronic equipment. This product complies with CE Directives 2006/95/EC, Low Voltage Directive (LVD) and 2004/108/EC, Electromagnetic Compatibility (EMC) Directive. VCU110 Evaluation Board www.xilinx.com Send Feedback UG1073 (v1.2) March 26, 2016... -

Page 154: Appendix H: Additional Resources And Legal Notices

The most up to date information related to the VCU107 board and its documentation is available on the following websites. VCU110 Evaluation Kit VCU110 Evaluation Kit Master — Answer Record (AR 62604) These Xilinx documents provide supplemental material useful with this guide: 1. Virtex UltraScale Architecture Data Sheet (DS893) 2. - Page 155 18. Zynq-7000 All Programmable SoC Packaging and Pinout Product Specification (UG865) 19. Silicon Labs CP210x USB-to-UART Installation Guide (UG1033) 20. Tera Term Terminal Emulator Installation Guide (UG1036) For additional documents associated with Xilinx devices, design tools, intellectual property, boards, and kits see the Xilinx documentation website.

- Page 156 (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.

Need help?

Do you have a question about the VCU110 and is the answer not in the manual?

Questions and answers