Summary of Contents for Xilinx Virtex UltraScale FPGA VCU1287

- Page 1 Virtex UltraScale FPGA VCU1287 Characterization Kit IBERT Getting Started Guide Vivado Design Suite UG1203 (v2016.4) December 15. 2016...

-

Page 2: Revision History

Updated for Vivado Design Suite 2016.1. Design file rdf0368-vcu1287-ibert-2015-4.zip changed to 04/13/2016 2016.1 rdf0368-vcu1287-ibert-2016-1.zip. Updated Figure 1-20 Figure 1-29. Added Training Resources in Appendix 02/22/2016 Initial Xilinx release. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 3: Table Of Contents

Xilinx Resources ........ -

Page 4: Overview

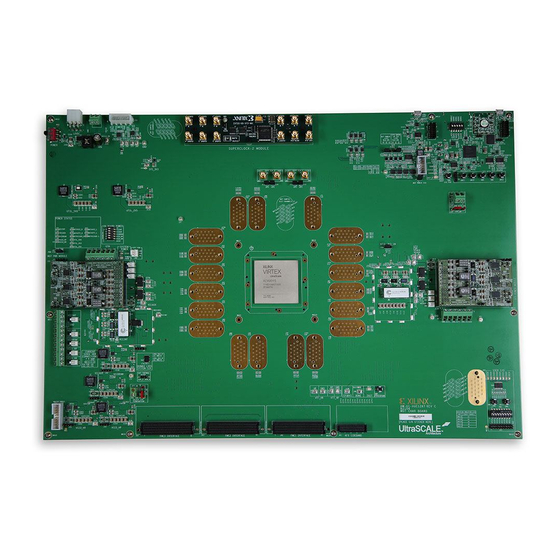

VCU1287 IBERT Getting Started Guide Overview This document describes setting up the Virtex UltraScale FPGA VCU1287 GTH and GTY Transceiver Characterization Board to run the Integrated Bit Error Ratio Test (IBERT) demonstration using the Vivado® Design Suite. The designs required to run the IBERT demonstration are stored in a Secure Digital (SD) memory card that is provided with the VCU1287 board. -

Page 5: Requirements

The hardware and software required to rebuild the IBERT demonstration designs are: • Xilinx Vivado Design Suite 2016.4 • PC with a version of the Windows operating system supported by Xilinx Vivado Design Suite VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. -

Page 6: Setting Up The Vcu1287 Board

VOLTAGE header, J18, and place another jumper across Si570 INH header J11. d. Screw down a 50Ω SMA terminator onto each of the six unused Si5368 clock output SMA connectors: J7, J8, J12, J15, J16, and J17. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 7: Extracting The Project Files

The Vivado Design Suite BIT files required to run the IBERT demonstrations are located in rdf0368-vcu1287-ibert-2016-4.zip on the SD card provided with the VCU1287 board. The BIT files are also available online at the Virtex UltraScale FPGA VCU1287 Characterization Kit documentation website. -

Page 8: Running The Gth Ibert Demonstration

Quads 133, 232, and 233 are not available on the XCVU095 device. Note: X-Ref Target - Figure 1-1 X15535-121416 Figure 1-1: VCU1287 GTH and GTY Quad Locations VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... - Page 9 The Si570 oscillator does not support LVDS output on the Rev B and earlier revisions of the Note: SuperClock-2 module. For more information on the SuperClock-2 module, see the HW-CLK-101-SCLK2 SuperClock-2 Module User Guide (UG770) [Ref VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 10 X-Ref Target - Figure 1-5 X15544-121416 Figure 1-5: Bulls Eye Connector Attached to Quad 224 VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 11 To ensure good connectivity, it is recommended that the adapters be secured with a wrench; Note: however, do not over-tighten the SMAs. X-Ref Target - Figure 1-6 X15545-121416 Figure 1-6: SMA F-F Adapter VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 12 VCU1287 board with the cable connections required for the Quad 224 GTH IBERT demonstration. X-Ref Target - Figure 1-8 X15547-121416 Figure 1-8: Cable Connections for Quad 224 GTH IBERT Demonstration VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 13: Starting The Superclock-2 Module

Outputs from either source can be used to drive the transceiver reference clocks. To start the SuperClock-2 module: 1. The SuperClock-2 module is configured using the Xilinx XC7Z010CLG225 Zynq-7000APSoC System Controller command line which can be accessed through a serial communication terminal connection using the enhanced communication port of... - Page 14 Silicon Lab USB-UART Bridge. Set up a new connection as in Figure 1-12, and press the Return key to connect to view the System Controller options menu. X-Ref Target - Figure 1-12 X15551-121416 Figure 1-12: Terminal Setting VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 15 5. View VCU1287 Saved Clocks in EEPROM 6. Set VCU1287 Clock Restore Options 7. Read VCU1287 Si570 Frequency 8. Read VCU1287 Si5368 Frequency 0. Return to Main Menu VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 16: Configuring The Fpga

2 - Free-Run using XA-XB crystal Configuring the FPGA The VCU1287 board additionally utilizes the Xilinx XC7Z010CLG225 Zynq-7000 AP SoC System Controller to implement a System Integrated Configuration Engine (System ICE) to configure the FPGA using one of the configuration *.bit files provided on the SD card in 8-bit SMAP configuration mode. - Page 17 Table 1-1: IBERT Examples Bitstream Number IBERT Demonstration Design Bitstream Number QUAD_124 QUAD_125 QUAD_126 QUAD_127 QUAD_128 QUAD_129 QUAD_130 QUAD_131 QUAD_224 QUAD_225 QUAD_226 QUAD_227 QUAD_228 QUAD_229 QUAD_230 QUAD_231 VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 18: Setting Up The Vivado Design Suite

4. Select option (8) to configure the FPGA with the Quad 224 IBERT example design. Press Enter and review the terminal for configuration progress: Enter a Bitstream number (0-15): Info: xilinx.sys opened Info: Opening rev_1/set8/config.def Info: Configuration definition file "rev_1/set8/config.def" opened... - Page 19 2. Start the Vivado Design Suite on the host computer and click Flow > Open Hardware Manager (highlighted in Figure 1-14). X-Ref Target - Figure 1-14 X15553-121416 Figure 1-14: Vivado Design Suite, Open Hardware Manager VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 20 4. An Open Hardware Target wizard opens. Click Next in the first window. 5. In the Hardware Server Settings window, select Local server (target is on local machine). Click Next. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 21 Design Suite default warnings and notifications setting has not been changed. Press Yes to automatically detect the links (Figure 1-17). X-Ref Target - Figure 1-17 X15556-121416 Figure 1-17: Auto-Detect the Serial I/O Links VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 22 Create Links or by clicking the Create Links button (Figure 1-18). X-Ref Target - Figure 1-18 X15557-121416 Figure 1-18: Serial I/O Analyzer – Create Links VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 23 MGT_X0Y1/TX (xcvu095_0/Quad_224) to MGT_X0Y1/RX (xcvu095_0/Quad_224) ° MGT_X0Y2/TX (xcvu095_0/Quad_224) to MGT_X0Y2/RX (xcvu095_0/Quad_224) ° MGT_X0Y3/TX (xcvu095_0/Quad_224) to MGT_X0Y3/RX (xcvu095_0/Quad_224) ° X-Ref Target - Figure 1-19 X15558-121416 Figure 1-19: Create Links Window VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 24: Viewing Gth Transceiver Operation

Increase the TX differential swing of the transceiver (to compensate for any loss due to PCB process variation). • Click the respective TX Reset button followed by BERT Reset. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 25: Closing The Ibert Demonstration

To stop the IBERT demonstration: 1. Close the Vivado Design Suite by selecting File > Exit. 2. Place the main power switch SW1 in the OFF position. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 26: Running The Gty Ibert Demonstration

X-Ref Target - Figure 1-21 X15560-121416 Figure 1-21: Bulls Eye Connector Attached to Quad 124 VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... - Page 27 TX3_N → SMA F-F Adapter → RX3_N To ensure good connectivity, it is recommended that the adapters be secured with a wrench; Note: however, do not over tighten the SMAs. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 28: Starting The Superclock-2 Module

IBERT demonstration. For both of the GTH and GTY IBERT demonstrations, the output clock frequency is preset to 125.00 MHz. See the description for Starting the SuperClock-2 Module, page for more details. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 29: Configuring The Fpga

Configuring the FPGA Similar to the GTH IBERT example, the VCU1287 board can be configured using the onboard Xilinx XC7Z010CLG225 Zynq-7000APSoC System Integrated Configuration Engine (SystemICE) in 8-bit SMAP configuration mode. Or the FPGA can be configured through the Vivado Design Suite using the *.bit files available on the SD card and online (as collection rdf0368-vcu1287-ibert-2016-4.zip) at the... - Page 30 4. Select option (0) to configure the FPGA with the Quad 124 IBERT example design. Press Enter and review the terminal for configuration progress. Enter a Bitstream number (0-15): Info : xilinx.sys opened Info : Opening rev_1/set0/config.def Info : Configuration definition file "rev_1/set0/config.def" opened...

-

Page 31: Setting Up The Vivado Design Suite

2. Start the Vivado Design Suite on the host computer and click Flow > Open Hardware Manager (highlighted in Figure 1-23). X-Ref Target - Figure 1-23 X15553-121416 Figure 1-23: Vivado Design Suite, Open Hardware Manager VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... - Page 32 4. An Open Hardware Target wizard opens. Click Next in the first window. 5. In the Hardware Server Settings window, select Local server (target is on local machine). Click Next. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 33 Design Suite default warnings and notification have not been changed. Press Yes to automatically detect the links (Figure 1-26). X-Ref Target - Figure 1-26 X15556-121416 Figure 1-26: Auto-detect the Serial I/O Links VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 34 10. If links are created manually, the Create Links window is displayed. The options in this window are used to link any TX GT to any RX GT. To create links, select the TX GT and RX VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 35 MGT_X0Y1/TX (xcvu095_0/Quad_124) to MGT_X0Y1/RX (xcvu095_0/Quad_124) ° MGT_X0Y2/TX (xcvu095_0/Quad_124) to MGT_X0Y2/RX (xcvu095_0/Quad_124) ° MGT_X0Y3/TX (xcvu095_0/Quad_124) to MGT_X0Y3/RX (xcvu095_0/Quad_124) ° X-Ref Target - Figure 1-28 X15564-121416 Figure 1-28: Create Links Window VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 36: Viewing Gty Transceiver Operation

Increase the TX differential swing of the transceiver (to compensate for any loss due to PCB process variation). • Click the respective TX Reset button followed by BERT Reset. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 37: Closing The Ibert Demonstration

To stop the IBERT demonstration: 1. Close the Vivado Design Suite by selecting File > Exit. 2. Place the main power switch SW1 in the off position. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... -

Page 38: Chapter 2: Creating The Ibert Cores

For more details on generating IBERT cores, see the Vivado Design Suite User Guide: Programming and Debugging (UG908) [Ref 1. Start the Vivado Design Suite. X-Ref Target - Figure 2-1 X15566-121416 Figure 2-1: Vivado Design Suite Initial Window VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... - Page 39 Part field. A Select Device window displays. Use the drop-down menu items to narrow the choices. Select the xcvu095-ffvb2104-3-e device (see Figure 2-2). Click OK. X-Ref Target - Figure 2-2 X15567-121416 Figure 2-2: Select Device VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 40 IP (Figure 2-3). Click Finish. Make sure the directory name does not include spaces. Note: X-Ref Target - Figure 2-3 X15568-121416 Figure 2-3: Manage IP Settings VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 41 6. In the IP Catalog window, expand the Debug & Verification folder, expand the Debug folder, and double-click IBERT UltraScale GTH (Figure 2-4). X-Ref Target - Figure 2-4 X15569-121416 Figure 2-4: IP Catalog VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 42 7. A Customize IP window opens. In the Protocol Definition tab, set the LineRate(Gbps) to 12.5. Change Refclk(MHz) to 125. Keep defaults for other fields (Figure 2-5). X-Ref Target - Figure 2-5 X15570-121416 Figure 2-5: Customize IP – Protocol Definition VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 43 8. In the Protocol Selection tab, use the Protocol Selected drop-down menu next to QUAD_224 to select Custom 1/12.5 Gb/s (Figure 2-6). X-Ref Target - Figure 2-6 X15540-121416 Figure 2-6: Customize IP – Protocol Selection VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 44 P Package Pin (the FPGA pins to which the system clock is connected), and make sure the Frequency (MHz) is set to 300 (Figure 2-7). X-Ref Target - Figure 2-7 X15571-121416 Figure 2-7: Customize IP - Clock Settings VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 45 10. Click OK. Click Generate in the next window to generate the output products (Figure 2-8). X-Ref Target - Figure 2-8 X15572-121416 Figure 2-8: Generate Output Products VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 46 2-9). Specify a location to save the design, click OK, and the design opens in a new Vivado Design Suite window. X-Ref Target - Figure 2-9 X15573-121416 Figure 2-9: Open IP Example Design VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 47 12. In the Sources window, Design Sources should now show the IBERT design example (Figure 2-10). X-Ref Target - Figure 2-10 X15574-121416 Figure 2-10: Design Sources File Hierarchy VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 48 Chapter 2: Creating the IBERT Cores 13. Click Run Synthesis from the Flow Navigator to synthesize the design (Figure 2-11). X-Ref Target - Figure 2-11 X15575-121416 Figure 2-11: Run Synthesis VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 49 15. When the implementation is done, an Implementation Completed window opens. Select Generate Bitstream and click OK (Figure 2-13). X-Ref Target - Figure 2-13 X15577-121416 Figure 2-13: Implementation Completed VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 50 16. When the Bitstream Generation Completed dialog window appears, click Cancel (Figure 2-14). X-Ref Target - Figure 2-14 X15578-121416 Figure 2-14: Bitstream Generation Complete 17. Navigate to the ...\ibert_ultrascale_gth_0_example\ibert_ultrascale_gth_0_exampl e.runs\impl_1 directory to locate the generated bitstream. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 51: Creating The Gty Ibert Core

Simulator for Target simulator, Mixed for Simulator language, and a directory to save the customized IP (Figure 2-3). Click Finish. Make sure the directory name does not include spaces. Note: VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com... - Page 52 6. In the IP Catalog window, expand the Debug & Verification folder, expand the Debug folder, and double-click IBERT UltraScale GTY (Figure 2-15). X-Ref Target - Figure 2-15 X15579-121416 Figure 2-15: IP Catalog VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 53 7. A Customize IP window opens. In the Protocol Definition tab, set the LineRate(Gb/s) to 28.00. Change Refclk(MHz) to 125. Keep defaults for the other fields (Figure 2-16). X-Ref Target - Figure 2-16 X15580-121416 Figure 2-16: Customize IP– Protocol Definition VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 54 8. In the Protocol Selection tab, use the Protocol Selected drop-down menu next to QUAD_124 to select Custom 1 / 28.00 Gbps (Figure 2-17). X-Ref Target - Figure 2-17 X15581-121416 Figure 2-17: Customize IP– Protocol Selection VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 55 P Package Pin (the FPGA pins where the system clock is connected), and make sure the Frequency (MHz) is set to 300 (Figure 2-18). X-Ref Target - Figure 2-18 X15582-121416 Figure 2-18: Customize IP– Clock Settings VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 56 10. Click OK. Click Generate in the next window to generate the output products (Figure 2-19). X-Ref Target - Figure 2-19 X15583-121416 Figure 2-19: Generate Output Products VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 57 2-20). Specify a location to save the design, click OK, and the design opens in a new Vivado Design Suite window. X-Ref Target - Figure 2-20 X15584-121416 Figure 2-20: Open IP Example Design VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

- Page 58 (Figure 2-13). 16. When the Bitstream Generation Completed dialog window appears, click Cancel (Figure 2-14). 17. Navigate to the ...\ibert_ultrascale_gty_0_example\ibert_ultrascale_gty_0_exampl e.runs\impl_1 directory to locate the generated bitstream. VCU1287 IBERT Getting Started Guide Send Feedback UG1203 (v2016.4) December 15. 2016 www.xilinx.com...

-

Page 59: Appendix A: Warranty

Customer. For any breach by Xilinx of this limited warranty, the exclusive remedy of Customer and the sole liability of Xilinx shall be, at the option of Xilinx, to replace or repair the affected products, or to refund to Customer the price of the affected products. The availability of replacement products is subject to product discontinuation policies at Xilinx. -

Page 60: Appendix B: Additional Resources And Legal Notices

Virtex UltraScale FPGA VCU1287 Characterization Kit Virtex UltraScale FPGA VCU1287 Characterization Kit documentation Virtex UltraScale FPGA VCU1287 Characterization Kit Master Answer Record (AR 66056) These documents provide supplemental material useful with this guide: 1. VCU1287 Characterization Board User Guide (UG1121) 2. -

Page 61: Training Resources

Xilinx’s Terms of Sale which can be viewed at https://www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance;...

Need help?

Do you have a question about the Virtex UltraScale FPGA VCU1287 and is the answer not in the manual?

Questions and answers