Altera Nios II User Manual

Hide thumbs

Also See for Nios II:

- Reference manual (56 pages) ,

- Hardware development manual (42 pages) ,

- User manual (40 pages)

Table of Contents

Advertisement

Quick Links

Download this manual

See also:

Reference Manual

Advertisement

Table of Contents

Summary of Contents for Altera Nios II

- Page 1 Nios II Processor Reference Handbook Nios II Processor Reference Handbook 101 Innovation Drive San Jose, CA 95134 www.altera.com NII5V1-13.1 Document last updated for Altera Complete Design Suite version: 13.1 Document publication date: February 2014...

- Page 2 © 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html.

-

Page 3: Table Of Contents

Getting Started with the Nios II Processor ........ - Page 4 How to Contact Altera ........

-

Page 5: Chapter Revision Dates

Chapter Revision Dates The chapters in this document, Nios II Processor Reference Handbook, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed. Chapter 1. Introduction Revised: February 2014 Part Number: NII51001-13.1.0 Chapter 2. - Page 6 Chapter Revision Dates Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 7: Section I. Nios Ii Processor Design

■ Chapter 2, Processor Architecture ■ Chapter 3, Programming Model Chapter 4, Instantiating the Nios II Processor ■ For information about the revision history for chapters in this section, refer to “Document Revision History” in each individual chapter. February 2014 Altera Corporation... - Page 8 I–2 Section I: Nios II Processor Design Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 9: Chapter 1. Introduction

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Page 10: Getting Started With The Nios Ii Processor

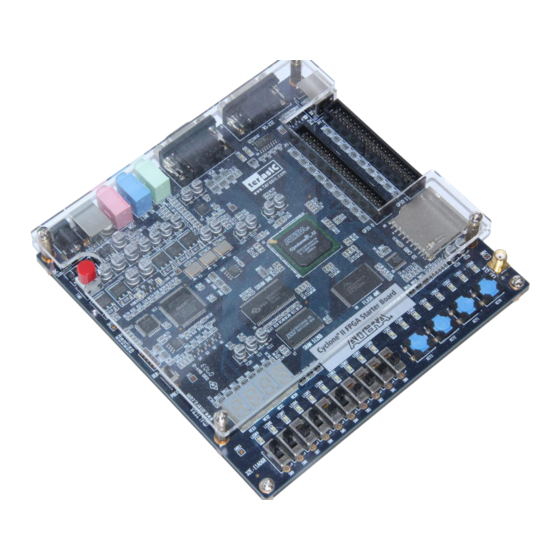

A Nios II processor system consists of a Nios II processor core, a set of on-chip peripherals, on-chip memory, and interfaces to off-chip memory, all implemented on a single Altera device. -

Page 11: Customizing Nios Ii Processor Designs

Extra resources can provide a few extra gates and registers as glue logic for the board design; or extra resources can implement entire systems. For example, a Nios II processor system consumes only 5% of a large Altera FPGA, leaving the rest of the chip’s resources available to implement other functions. -

Page 12: Configurable Soft Processor Core Concepts

Configurable Soft Processor Core The Nios II processor is a configurable soft IP core, as opposed to a fixed, off-the-shelf microcontroller. You can add or remove features on a system-by-system basis to meet performance or price goals. - Page 13 The custom logic is integrated into the Nios II processor’s arithmetic logic unit (ALU). Similar to native Nios II instructions, custom instruction logic can take values from up to two source registers and optionally write back a result to a destination register.

-

Page 14: Opencore Plus Evaluation

■ Program a device and verify your design in hardware. You only need to purchase a license for the Nios II processor when you are completely satisfied with its functionality and performance, and want to take your design to production. -

Page 15: Document Revision History

Chapter 1: Introduction 1–7 Document Revision History Table 1–1. Document Revision History (Part 2 of 2) Date Version Changes September 2004 Maintenance release. May 2004 Initial release. February 2014 Altera Corporation Nios II Processor Reference Handbook... - Page 16 1–8 Chapter 1: Introduction Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 17: Chapter 2. Processor Architecture

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Page 18: Processor Implementation

A functional unit can be implemented in hardware, emulated in software, or omitted entirely. A Nios II implementation is a set of design choices embodied by a particular Nios II processor core. All implementations support the instruction set defined in the Instruction Set Reference chapter of the Nios II Processor Reference Handbook. -

Page 19: Register File

The Nios II processor can optionally have one or more shadow register sets. A shadow register set is a complete set of Nios II general-purpose registers. When shadow register sets are implemented, the CRS field of the status register indicates which register set is currently in use. -

Page 20: Arithmetic Logic Unit

The ALU supports arithmetic shift right and logical shift right/left. The ALU supports rotate left/right. Unimplemented Instructions Some Nios II processor core implementations do not provide hardware to support the entire Nios II instruction set. In such a core, instructions without hardware support are known as unimplemented instructions. - Page 21 Chapter 2: Processor Architecture 2–5 Arithmetic Logic Unit Floating-Point Instructions The Nios II architecture supports single precision floating-point instructions with two components: ■ Floating Point Hardware 2—This component supports floating-point instructions as specified by the IEEE Std 754-2008 but with simplified, non-standard rounding modes.

- Page 22 (2) This operation is not fully compliant with IEEE 754-2008. Floating Point Custom Instruction 2 Component You can add floating-point custom instructions to any Nios II processor design. The floating-point division hardware requires more resources than the other instructions. The Floating Point Hardware 2 component supports the following single-precision floating-point operations: ■...

- Page 23 ? 1 : 0 Supported None a >= b fcmpeqs (a = b) ? 1 : 0 Supported None a == b ≠ fcmpnes b) ? 1 : 0 Supported None a != b February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 24 2 cycles. An N-cycle multi-cycle custom instruction has N - 2 register stages inside the custom instruction because the Nios II processor registers the result from the custom instruction and allows another cycle for g wire delays in the source operand bypass multiplexers.

-

Page 25: Reset And Debug Signals

Chapter 2: Processor Architecture 2–9 Reset and Debug Signals Reset and Debug Signals The table below describes the reset and debug signals that the Nios II processor core supports. Table 2–4. Nios II Processor Debug and Reset Signals Signal Name... - Page 26 When the EIC interface and shadow register sets are implemented on the Nios II core, you must ensure that your software is built with the Nios II EDS version 9.0 or higher. Earlier versions have an implementation of the eret instruction that is incompatible with shadow register sets.

-

Page 27: Memory And I/O Organization

As a result, the memory and I/O organization varies from system to system. A Nios II core uses one or more of the following to provide memory and I/O access: ® Instruction master port—An Avalon Memory-Mapped (Avalon-MM) master port ■... - Page 28 Avalon Slave Port Instruction and Data Buses The Nios II architecture supports separate instruction and data buses, classifying it as a Harvard architecture. Both the instruction and data buses are implemented as Avalon-MM master ports that adhere to the Avalon-MM interface specification. The data master port connects to both memory and peripheral components, while the instruction master port connects only to memory components.

- Page 29 Memory” on page 2–15 for details. Data Master Port The Nios II data bus is implemented as a 32-bit Avalon-MM master port. The data master port performs two functions: ■ Read data from memory or a peripheral when the processor executes a load...

-

Page 30: Cache Memory

Byte-enable signals on the master port specify which of the four byte-lane(s) to write during store operations. When the Nios II core is configured with a data cache line size greater than four bytes, the data master port supports pipelined Avalon-MM transfers. - Page 31 The largest block of performance-critical data is smaller than the data cache Optimal cache configuration is application specific, although you can make decisions that are effective across a range of applications. For example, if a Nios II processor system includes only fast, on-chip memory (i.e., it never accesses slow, off-chip memory), an instruction or data cache is unlikely to offer any performance gain.

- Page 32 Physically, a tightly-coupled memory port is a separate master port on the Nios II processor core, similar to the instruction or data master port. A Nios II core can have zero, one, or multiple tightly-coupled memories. The Nios II architecture supports tightly-coupled memory for both instruction and data access.

-

Page 33: Memory Management Unit

Instantiating the Nios II Processor chapter of the Nios II Processor Reference Handbook. The Nios II MMU is optional and mutually exclusive from the Nios II MPU. Nios II systems can include either an MMU or MPU, but cannot include both an MMU and MPU on the same Nios II processor core. -

Page 34: Jtag Debug Module

Instantiating the Nios II Processor chapter of the Nios II Processor Reference Handbook. The Nios II MPU is optional and mutually exclusive from the Nios II MMU. Nios II systems can include either an MPU or MMU, but cannot include both an MPU and MMU on the same Nios II processor core. -

Page 35: Software Breakpoints

Soft processor cores such as the Nios II processor offer unique debug capabilities beyond the features of traditional, fixed processors. The soft nature of the Nios II processor allows you to debug a system in development using a full-featured debug core, and later remove the debug features to conserve logic resources. - Page 36 When a trigger condition occurs during processor execution, the JTAG debug module triggers an action, such as halting execution, or starting trace capture. The table below lists the trigger actions supported by the Nios II JTAG debug module. Table 2–6. Trigger Actions...

- Page 37 Certain trace features require additional licensing or debug tools from third-party debug providers. For example, an on-chip trace buffer is a standard feature of the Nios II processor, but using an off-chip trace buffer requires additional debug software and hardware provided by MIPS Technologies or Lauterbach GmbH.

-

Page 38: Document Revision History

Removed references to SOPC Builder. ■ Added references to new Qsys system integration tool. ■ May 2011 11.0.0 Moved interrupt vector custom instruction information to the Instantiating the Nios II ■ Processor chapter. December 2010 10.1.0 Added reference to tightly-coupled memory tutorial. - Page 39 ■ October 2005 5.1.0 Maintenance release. May 2005 5.0.0 Added tightly-coupled memory. December 2004 Added new control register ctl5. September 2004 Updates for Nios II 1.01 release. May 2004 Initial release. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 40 2–24 Chapter 2: Processor Architecture Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 41: Chapter 3. Programming Model

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Page 42: Memory Management Unit

Recommended Usage Including the Nios II MMU in your Nios II hardware system is optional. The MMU is only useful with an operating system that takes advantage of it. Many Nios II systems have simpler requirements where minimal system software or a ®... -

Page 43: Memory Management

Memory Protection The Nios II MMU maintains read, write, and execute permissions for each page. The TLB provides the permission information when translating a VPN. The operating system can control whether or not each process is allowed to read data from, write data to, or execute instructions on each particular page. - Page 44 Whenever an instruction attempts to access a page that either has no TLB mapping, or lacks the appropriate permissions, the MMU generates an exception. The Nios II processor’s precise exceptions enable the system software to update the TLB, and then re-execute the instruction if desired.

- Page 45 Avalon switch fabric. Bit 31 is not used to specify data cacheability, as it is in Nios II cores without MMUs. Virtual memory partitions that bypass the TLB have a default data cacheability property, as described in the abmove table, Virtual Memory .

-

Page 46: Tlb Organization

Memory Management Unit TLB Organization A TLB functions as a cache for the operating system’s page table. In Nios II processors with an MMU, one main TLB is shared by instruction and data accesses. The TLB is stored in on-chip RAM and handles translations for instruction fetches and instructions that perform data accesses. - Page 47 C is the cacheable flag. Determines the default data cacheability of a page. Can be overridden for data accesses using I/O load and store family of Nios II instructions. R is the readable flag. Allows load instructions to read a page.

-

Page 48: Memory Protection Unit

For information about memory protection with virtual memory management, refer to the Memory Management Unit section. When present and enabled, the MPU monitors all Nios II instruction fetches and data memory accesses to protect against errant software execution. The MPU is a hardware facility that system software uses to define memory regions and their associated access permissions. - Page 49 The maximum supported region size equals the Nios II address space (a function of the address ranges of slaves connected to the Nios II masters). Any access outside of the Nios II address space is considered not to match any region and triggers an MPU region violation exception.

-

Page 50: Registers

Working with the MPU section for more information. Registers The Nios II register set includes general-purpose registers and control registers. In addition, the Nios II/f core can optionally have shadow register sets. This section discusses each register type. General-Purpose Registers The Nios II architecture provides thirty-two 32-bit general-purpose registers, r0 through r31. -

Page 51: Control Registers

When writing to control registers, all undefined bits must be written as zero. The Nios II architecture supports up to 32 control registers. All nonreserved control registers have names recognized by the assembler. - Page 52 Registers The status Register The value in the status register determines the state of the Nios II processor. All status bits are set to predefined values at processor reset. Some bits are exclusively used by and available only to certain features of the processor, such as the MMU, MPU or external interrupt controller (EIC) interface.

- Page 53 All fields in the estatus register have read/write access. All fields reset to 0. When the Nios II processor takes an interrupt, if status.eh is zero (that is, the MMU is in nonexception mode), the processor copies the contents of the status register to estatus.

- Page 54 The cpuid Register The cpuid register holds a constant value that you define in the Nios II Processor parameter editor to uniquely identify each processor in a multiprocessor system. In Qsys, unique values must be assigned manually. Writing to the cpuid register has no effect.

- Page 55 When your system contains an MMU or MPU, the extra exception information is always enabled. When no MMU or MPU is present, the Nios II Processor parameter editor gives you the option to have the processor provide the extra exception information.

- Page 56 TLB lookup. When G = 1, tlbmisc.PID is ignored and only the Read/Write virtual page number is used in the TLB lookup. PFN is the physical frame number field. All unused upper bits must Only with Read/Write be zero. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 57 The RD Flag System software triggers a TLB read operation by setting tlbmisc.RD (with a wrctl instruction). A TLB read operation loads the following register fields with the contents of a TLB entry: February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 58 The size of the PID field is configured in Qsys at system generation, and can be from 8 to 14 bits. If system software defines a process identifier smaller than the PID field, unused upper bits must be written as zero. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 59 Misaligned data address Misaligned destination address ■ Refer to Nios II Exceptions (In Decreasing Priority Order) table for more information on these exceptions. The PERM Flag During a general exception, the processor sets PERM to one for a TLB permission violation exception, and clears PERM to zero otherwise.

- Page 60 If there is no MMU or MPU and the Nios II address space is less than 32 bits, unused high-order bits are written and read as zero. If there is no MMU, bit 31 of a data address (used to bypass the data cache) is always zero in the BADDR field.

- Page 61 BASE field (bits 6 though 9 of the mpubase register) must be zero. Similarly, if the Nios II address space is less than 31 bits, unused high-order bits must also be written as zero and are read as zero.

- Page 62 (1) The MASK and LIMIT fields are mutually exclusive. Refer to mpucc Control Register Field for MASK Variation Table and mpuacc Control Register Field for LIMIT Variation Table. The following sections provide more information about the mpuacc fields. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 63 Bit 31 of the mpuacc register is not used by the MASK field. Because memory region size is already a power of two, one less bit is needed. The MASK field contains the following value, where region_size is in bytes: MASK = 0x1FFFFFF << log2(region_size >> 6) February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 64 Refer to the MPU Region Read and Write Operations section for more information. The RD flag always returns 0 when read by a rdctl instruction. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 65 When shadow register sets are implemented, status.CRS indicates the register set currently in use. A Nios II core can have up to 63 shadow register sets. If n is the configured number of shadow register sets, the shadow register sets are numbered from 1 to n.

- Page 66 When shadow register sets and the EIC interface are implemented on the Nios II core, you must ensure that your software is built with the Nios II EDS version 9.0 or later. Earlier versions have an implementation of the eret instruction that is incompatible with shadow register sets.

- Page 67 (2) If the EIC interface and shadow register sets are not present, SRS always reads as 0, and the processor behaves accordingly. The sstatus register is present in the Nios II core if both the EIC interface and shadow register sets are implemented. There is one copy of sstatus for each shadow register set.

-

Page 68: Working With The Mpu

The MPU region write operation sets the values for mpubase.BASE, mpuacc.MASK or mpuacc.LIMIT, mpuacc.C, and mpuacc.PERM as the new attributes for the MPU region. Nios II Processor Reference Handbook February 2014 Altera Corporation... -

Page 69: Working With Ecc

Working with ECC Enabling ECC The ECC is disabled on system reset. Before enabling the ECC, initialize the Nios II RAM blocks to avoid spurious ECC errors. The Nios II processor executes the INITI instruction on each cache line, which initializes the instruction cache RAM. - Page 70 Chapter 3: Programming Model Working with ECC Nios II processor instructions that write to every register (except register 0) initialize the register file RAM blocks. If shadow register sets are present, this step is performed for all registers in the shadow register set using the WRPRS instruction.

-

Page 71: Exception Processing

Exception processing is the act of responding to an exception, and then returning, if possible, to the pre-exception execution state. All Nios II exceptions are precise. Precise exceptions enable the system software to re-execute the instruction, if desired, after handling the exception. - Page 72 ■ Reset exception—Occurs when the Nios II processor is reset. Control is transferred to the reset address you specify in the Nios II processor IP core setup parameters. Break exception—Occurs when the JTAG debug module requests control. Control is ■...

- Page 73 Table 3–35 on page 3–33. Control is transferred to the exception address you specify in the Nios II processor IP core setup parameters. The following table columns specify information for the exceptions: Exception—Gives the name of the exception.

- Page 74 3–34 Chapter 3: Programming Model Exception Processing Table 3–35. Nios II Exceptions (In Decreasing Priority Order) (Part 2 of 2) Exception Type Available Cause Address Vector Illegal instruction Illegal instruction Instruction-related General exception ea–4 detection on, MMU, or MPU Unimplemented instruction...

- Page 75 Reset Exceptions When a processor reset signal is asserted, the Nios II processor performs the following steps: 1. Sets status.RSIE to 1, and clears all other fields of the status register.

- Page 76 Break Exceptions A break is a transfer of control away from a program’s normal flow of execution for the purpose of debugging. Software debugging tools can take control of the Nios II processor via the JTAG debug module. Break processing is the means by which software debugging tools implement debug and diagnostic features, such as breakpoints and watchpoints.

-

Page 77: Interrupt Exceptions

Requested nonmaskable interrupt (RNMI) mode—Refer to “Requested NMI Mode” The Nios II processor EIC interface connects to a single EIC, but an EIC can support a daisy-chained configuration. In a daisy-chained configuration, multiple EICs can monitor and prioritize interrupts. The EIC directly connected to the processor presents the processor with the highest-priority interrupt from all EICs in the daisy chain. - Page 78 Requested Interrupt Level The Nios II processor uses the RIL to decide when to take a maskable interrupt. The interrupt is taken only when the RIL is greater than status.IL. The RIL is ignored for nonmaskable interrupts.

- Page 79 Internal Interrupt Controller When the internal interrupt controller is implemented, a peripheral device can request a hardware interrupt by asserting one of the Nios II processor’s 32 interrupt-request inputs, irq0 through irq31. A hardware interrupt is generated if and only if all three of these conditions are true: The PIE bit of the status control register is one.

- Page 80 3–40 Chapter 3: Programming Model Exception Processing Although shadow register sets can be implemented in any Nios II/f processor, the internal interrupt controller does not have features to take advantage of it as external interrupt controllers do. Figure 3–2. Relationship Between ienable, ipending, PIE and Hardware Interrupts...

- Page 81 Illegal Instruction Illegal instructions are instructions with an undefined opcode or opcode-extension field. The Nios II processor can check for illegal instructions and generate an exception when an illegal instruction is encountered. When your system contains an MMU or MPU, illegal instruction checking is always on. When no MMU or MPU is present, you have the option to have the processor check for illegal instructions.

- Page 82 This exception is implemented only in Nios II processors that include the MMU. Misaligned Data Address The Nios II processor can check for misaligned data addresses of load and store instructions and generate an exception when a misaligned data address is encountered.

- Page 83 A destination address is considered misaligned if the target byte address of the instruction is not a multiple of four. Division Error The Nios II processor can check for division errors and generate an exception when a division error is encountered. For information about controlling this option, refer to the...

- Page 84 Exception Processing Double TLB Miss Double TLB miss exceptions are implemented only in Nios II processors that include the MMU. When a TLB miss exception occurs while software is currently processing an exception (that is, when status.EH = 1), a double TLB miss exception is generated.

- Page 85 The address of the general exception handler, specified with the Nios II Processor parameter editor in Qsys, is called the exception vector in the Nios II Processor parameter editor. At run time this address is fixed, and software cannot modify it.

- Page 86 ■ RNMI—The requested NMI flag specifies whether to treat the interrupt as nonmaskable. For further information about the RHA, RRS, RIL and RNMI, refer to “The Nios II/f Core” in the Nios II Core Implementation Details chapter of the Nios II Processor Reference Handbook.

- Page 87 ISR to be interrupted. Typically, the exception routine adjusts ienable so that IRQs of equal or lower priority are disabled before re-enabling interrupts. Refer to “Handling Nested Exceptions” on page 3–50 for more information. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 88 Exceptions and Processor Status Table 3–37 lists all changes to the Nios II processor state as a result of nonbreak exception processing actions performed by hardware. For systems with an MMU, status.EH indicates whether or not exception processing is already in progress. When status.EH = 1, exception processing is already in progress and the states of the...

- Page 89 (1) If the Nios II processor does not have an EIC interface, external interrupts do not occur. (2) If the Nios II processor does not have an MMU, this field is not implemented. Its value is always 0, and the processor behaves accordingly.

- Page 90 Exception Processing Without Extra Exception Information When you have not included the extra exception information in your Nios II system, your exception handler must determine the cause of exception itself. For this reason, Altera recommends always enabling the extra exception information.

- Page 91 Chapter 3: Programming Model 3–51 Exception Processing For details about when the Nios II processor takes exceptions, refer to “Exception Processing Flow” on page 3–45. For details about unimplemented instructions, refer to the Processor Architecture chapter of the Nios II Processor Reference Handbook. For details about MMU and MPU exceptions, refer to “Instruction-Related Exceptions”...

- Page 92 1 after registers are saved. When an ISR is running in a given register set, the processor takes an interrupt in the same register set if it has a higher interrupt level. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 93 In the case of ISRs, if the EIC interface and shadow register sets are implemented, and the ISR has a dedicated register set, no software action is required. The Nios II processor returns to the previous register set when it executes eret, which restores the register contents.

- Page 94 (or sstatus.NMI) is 1, after an eret, status.NMI is still 0. This restriction prevents the processor from accidentally entering NMI mode. When the EIC interface and shadow register sets are implemented on the Nios II core, you must ensure that your software, including ISRs, is built with the version of the GCC compiler included in Nios II EDS version 9.0 or later.

-

Page 95: Memory And Peripheral Access

Memory and Peripheral Access Nios II addresses are 32 bits, allowing access up to a 4-gigabyte address space. Nios II core implementations without MMUs restrict addresses to 31 bits or fewer. The MMU supports the full 32-bit physical address. - Page 96 The reverse is not true. If it is necessary for a program to work properly on multiple Nios II processor core implementations, the program must behave as if the instruction and data caches exist. In systems without cache memory, the cache management instructions perform no operation, and their effects are benign.

-

Page 97: Instruction Set Categories

The Nios II architecture is a load-store architecture. Load and store instructions handle all data movement between registers, memory, and peripherals. Memories and peripherals share a common address space. Some Nios II processor cores use memory caching and/or write buffering to improve memory bandwidth. The architecture provides instructions for both cached and uncached accesses. -

Page 98: Move Instructions

32 bits. movui and movhi move a 16-bit immediate value into the movi lower or upper 16-bits of a register, inserting zeros in the remaining bit positions. Use movia to load a movui register with an address. movia Nios II Processor Reference Handbook February 2014 Altera Corporation... -

Page 99: Comparison Instructions

Instruction Set Categories Comparison Instructions The Nios II architecture supports a number of comparison instructions. All of these compare two registers or a register and an immediate value, and write either one (if true) or zero to the result register. These instructions perform all the equality and relational operators of the C programming language. -

Page 100: Program Control Instructions

3–60 Chapter 3: Programming Model Instruction Set Categories Program Control Instructions The Nios II architecture supports the unconditional jump, branch, and call instructions. These instructions do not have delay slots. Table 3–46. Unconditional Jump and Call Instructions Instruction Description This instruction calls a subroutine using an immediate value as the subroutine's absolute address, and call stores the return address in register ra. - Page 101 Custom Instructions The custom instruction provides low-level access to custom instruction logic. The inclusion of custom instructions is specified with the Nios II Processor parameter editor in Qsys, and the function implemented by custom instruction logic is design dependent.

-

Page 102: Document Revision History

Document Revision History Potential Unimplemented Instructions Some Nios II processor cores do not support all instructions in hardware. In this case, the processor generates an exception after issuing an unimplemented instruction. Only the following instructions can generate an unimplemented instruction exception: ■... - Page 103 Maintenance release. Added details for new control register ctl5. ■ September 2004 Updated details of debug and break processing to reflect new behavior of the break ■ instruction. May 2004 Initial release. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 104 3–64 Chapter 3: Programming Model Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 105: Chapter 4. Instantiating The Nios Ii Processor

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. - Page 106 The following sections describe the configuration settings available. Core Selection The main purpose of the Core Nios II tab is to select the processor core. The core you select on this tab affects other options available on this and other tabs.

-

Page 107: Reset Vector

The Reset vector memory list, which includes all memory modules mastered by the Nios II processor, selects the reset vector memory module. In a typical system, select a nonvolatile memory module for the reset code. - Page 108 Nios II hardware system. Do not include an MMU in your Nios II system unless your operating system requires it. The MMU is only useful with software that takes advantage of it. Many Nios II ® systems involve simpler system software, such as Altera HAL or MicroC/OS-II.

-

Page 109: Caches And Memory Interfaces Tab

4–5 Caches and Memory Interfaces Tab The Nios II MMU is optional and mutually exclusive from the Nios II MPU. Nios II systems can include either an MMU or MPU, but cannot include both an MMU and MPU in the same design. - Page 110 (called burst adapters) which might decrease your f When the Nios II processor transfers execution to the first word of a cache line, the processor fills the line by executing a sequence of word transfers that have ascending addresses, such as 0, 4, 8, 12, 16, 20, 24, 28.

-

Page 111: Advanced Features Tab

For example, with a 32-byte Nios II data cache line, a cache miss to the address 8 results in a burst with the following address sequence: 0, 4, 8, 12, 16, 20, 24 and 28. - Page 112 When on, the Nios II processor includes processor-only reset request signals. These signals let another device individually reset the Nios II processor without resetting the entire system. The signals are exported to the top level of your system.

- Page 113 Division error—Division error detection is only available for the Nios II/f core, and only then when Hardware divide on the Core Nios II tab is on. When divide instructions are not supported by hardware, the Division error setting is disabled.

- Page 114 When the EIC interface and shadow register sets are implemented on the Nios II core, you must ensure that your software is built with the Nios II EDS version 9.0 or higher. For details about shadow register sets, refer to “Registers” in the Programming Model chapter of the Nios II Processor Reference Handbook.

-

Page 115: Mmu And Mpu Settings Tab

SECDED ECC algorithm is based on Hamming codes, which detect 1 or 2 bit errors and corrects 1 bit errors. If the Nios II processor does not attempt to correct any errors and only detects them, the ECC algorithm can detect 3 bit errors. - Page 116 Nios II Processor Reference Handbook. When Include MPU on the Core Nios II tab is on, the MPU settings on the MMU and MPU Settings tab provide the following options for the MPU in the Nios II/f core.

-

Page 117: Jtag Debug Module Tab

On-Chip Trace Stores trace data in on-chip memory. Stores trace data in an external debug probe. Off-chip trace instantiates a PLL inside the Nios II Off-Chip Trace core. Off-chip trace requires a debug probe from MIPS Technologies or Lauterbach GmbH. - Page 118 Level 4 The table is a detailed list of the characteristics of each debug level. Different levels consume different amounts of on-chip resources. Certain Nios II cores have restricted debug options, and certain options require debug tools provided by MIPS Technologies or Lauterbach GmbH.

-

Page 119: Custom Instruction Tab

When on, the Nios II processor includes debug request and acknowledge signals. These signals let another device temporarily suspend the Nios II processor for debug purposes. The signals are exported to the top level of your Qsys system. - Page 120 Table 2–3 on page 2–7 for details. To add the Floating Point Hardware 2 custom instruction to the Nios II processor in Qsys, select Floating Point Hardware 2 under Embedded Processors in the Component Library tab. Connect the two slave interfaces to the Nios II custom instruction master.

- Page 121 The Nios II processor core offers a bitswap custom instruction to reduce the time spent performing bit reversal operations. To add the bitswap custom instruction to the Nios II processor in Qsys, select Bitswap under Custom Instruction Modules on the Component Library tab, and click Add.

-

Page 122: The Quartus Ii Ip File

Added debugreq and debugack signal options to Advanced Features tab. ■ November 2008 8.1.0 Added cpuid manual override options to Advanced Features tab. ■ Added MMU options to Nios II Core and Advanced Features tabs. ■ May 2008 8.0.0 Added exception handling options Advanced Features tab. ■... - Page 123 6.0.0 Added section on Advanced Features tab. ■ October 2005 5.1.0 Maintenance release. Updates to reflect new GUI options in Nios II processor version 5.0. ■ May 2005 5.0.0 New details in “Caches and Tightly-Coupled Memory” section. ■ Updates to reflect new GUI options in Nios II processor version 1.1.

- Page 124 4–20 Chapter 4: Instantiating the Nios II Processor Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 125: Section Ii. Nios Ii Processor Implementation And Reference

® This section provides additional information about the Nios II processor. This section includes the following chapters: ■ Chapter 5, Nios II Core Implementation Details ■ Chapter 6, Nios II Processor Revision History ■ Chapter 7, Application Binary Interface Chapter 8, Instruction Set Reference ■... - Page 126 II–2 Section II: Nios II Processor Implementation and Reference Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 127: Chapter 5. Nios Ii Core Implementation Details

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. - Page 128 5–2 Chapter 5: Nios II Core Implementation Details Table 5–1. Nios II Processor Cores (Part 2 of 3) Core Feature Nios II/e Nios II/s Nios II/f Cache – – 512 bytes to 64 KB Pipelined Memory Access – – –...

-

Page 129: Device Family Support

Notes to Table 5–1: (1) DMIPS performance for the Nios II/s and Nios II/f cores depends on the hardware multiply option. ® (2) Using the fastest hardware multiply option, and targeting a Stratix II FPGA in the fastest speed grade. -

Page 130: Nios Ii/F Core

Nios II/f Core The Nios II/f fast core is designed for high execution performance. Performance is gained at the expense of core size. The base Nios II/f core, without the memory management unit (MMU) or memory protection unit (MPU), is approximately 25% larger than the Nios II/s core. - Page 131 5–5 Nios II/f Core Arithmetic Logic Unit The Nios II/f core provides several arithmetic logic unit (ALU) options to improve the performance of multiply, divide, and shift operations. Multiply and Divide Performance The Nios II/f core provides the following hardware multiplier options: ■...

-

Page 132: Memory Access

Avalon-MM master port. Otherwise, the data master port is not pipelined. The instruction and data master ports on the Nios II/f core are optional. A master port can be excluded, as long as the core includes at least one tightly-coupled memory to take the place of the missing master port. - Page 133 32 bits and the tag field always includes all the bits of the physical frame number (PFN). The instruction cache is optional. However, excluding instruction cache from the Nios II/f core requires that the core include at least one tightly-coupled instruction memory. Data Cache...

- Page 134 For example, the following sequence of events causes cache incoherency. 1. The Nios II core writes data to cache, creating a dirty data cache line. 2. The Nios II core reads data from the same address, but bypasses the cache.

- Page 135 Tightly-Coupled Memory The Nios II/f core provides optional tightly-coupled memory interfaces for both instructions and data. A Nios II/f core can use up to four each of instruction and data tightly-coupled memories. When a tightly-coupled memory interface is enabled, the Nios II core includes an additional memory interface master port.

-

Page 136: Execution Pipeline

Chapter 5: Nios II Core Implementation Details Nios II/f Core Memory Protection Unit The Nios II/f core provides options to improve the performance of the Nios II MPU. For information about the MPU architecture, refer to the Programming Model chapter of the Nios II Processor Reference Handbook. - Page 137 Instructions that require Avalon-MM transfers are stalled until any required Avalon-MM transfers (up to one write and one read) are completed. Table 5–10. Instruction Execution Performance for Nios II/f Core 4byte/line data cache (Part 1 of 2) Instruction Cycles Penalties Normal ALU instructions (e.g., add, cmplt)

-

Page 138: Exception Handling

(1) Depends on the hardware multiply or divide option. Refer to Table 5–4 on page 5–5 for details. (2) In the default Nios II/f configuration, these instructions require four clock cycles. If any of the following options are present, they require five clock cycles: ■... - Page 139 For an example of an EIC implementation, refer to the Vectored Interrupt Controller chapter in the Embedded Peripherals IP User Guide. The Nios II/f core has the option to add ECC support for the following Nios II internal RAM blocks. Instruction cache ■...

- Page 140 The ECC interface is an Avalon-ST source with the output signal ecc_event_bus. This interface allows external logic to monitor ECC errors in the Nios II processor. The ecc_event_bus contains the ECC error signals that are driven to 1 even if ECC checking is disabled in the Nios II processor (when CONFIG.ECCEN or CONFIG.ECCEXC is...

-

Page 141: Nios Ii/S Core

Nios II/s Core JTAG Debug Module The Nios II/f core supports the JTAG debug module to provide a JTAG interface to software debugging tools. The Nios II/f core supports an optional enhanced interface that allows real-time trace data to be routed out of the processor and stored in an external debug probe. - Page 142 None—Does not include multiply hardware. In this case, multiply operations are emulated in software. The Nios II/s core also provides a hardware divide option that includes LE-based divide circuitry in the ALU. Including an ALU option improves the performance of one or more arithmetic instructions.

- Page 143 The Nios II/s core provides instruction cache, but no data cache. The instruction cache size is user-definable, between 512 bytes and 64 KB. The Nios II/s core can address up to 2 GB of external memory. The Nios II architecture reserves the most-significant bit of data addresses for the bit-31 cache bypass method.

- Page 144 When tightly-coupled memory is present, the Nios II core decodes addresses internally to determine if requested instructions reside in tightly-coupled memory. If the address resides in tightly-coupled memory, the Nios II core fetches the instruction through the tightly-coupled memory interface. Software does not require awareness of whether code resides in tightly-coupled memory or not.

- Page 145 An M-stage multicycle custom instruction is asserting its stall signal. This only occurs if the design includes multicycle custom instructions. Branch Prediction The Nios II/s core performs static branch prediction to minimize the cycle penalty associated with taken branches. Instruction Performance All instructions take one or more cycles to execute.

-

Page 146: Nios Ii/E Core

Unimplemented instruction JTAG Debug Module The Nios II/s core supports the JTAG debug module to provide a JTAG interface to software debugging tools. The Nios II/s core supports an optional enhanced interface that allows real-time trace data to be routed out of the processor and stored in an external debug probe. - Page 147 Avalon-MM transfer. The Nios II/e core can address up to 2 GB of external memory. The Nios II architecture reserves the most-significant bit of data addresses for the bit-31 cache bypass method. In the Nios II/e core, bit 31 is always zero.

-

Page 148: Document Revision History

■ Unimplemented instruction JTAG Debug Module The Nios II/e core supports the JTAG debug module to provide a JTAG interface to software debugging tools. The JTAG debug module on the Nios II/e core does not support hardware breakpoints or trace. - Page 149 Chapter 5: Nios II Core Implementation Details 5–23 Document Revision History Table 5–18. Document Revision History (Part 2 of 2) Date Version Changes September 2004 Updates for Nios II 1.01 release. May 2004 Initial release. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 150 5–24 Chapter 5: Nios II Core Implementation Details Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 151: Chapter 6. Nios Ii Processor Revision History

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Page 152: Architecture Revisions

Architecture Revisions Architecture revisions augment the fundamental capabilities of the Nios II architecture, and affect all Nios II cores. A change in the architecture mandates a revision to all Nios II cores to accommodate the new architectural enhancement. For example, when Altera adds a new instruction to the instruction set, Altera consequently must update all Nios II cores to recognize the new instruction. -

Page 153: Core Revisions

Initial release of the Nios II processor architecture. Core Revisions Core revisions introduce changes to an existing Nios II core. Core revisions most commonly fix identified bugs, or add support for an architecture revision. Not every Nios II core is revised with every release of the Nios II architecture. - Page 154 May 2005 Made instruction and data caches optional (previously, cache memories were ■ always present). If the instruction cache is not present, the Nios II core does not have an instruction master port, and must use a tightly-coupled instruction memory.

- Page 155 Made instruction cache optional (previously instruction cache was always ■ May 2005 present). If the instruction cache is not present, the Nios II core does not have an instruction master port, and must use a tightly-coupled instruction memory. Support for HardCopy devices (previous versions required a workaround to ■...

- Page 156 6–6 Chapter 6: Nios II Processor Revision History Core Revisions Table 6–4. Nios II/s Core Revisions (Part 2 of 2) Version Release Date Notes Added user-configurable options affecting multiply and shift operations. Now ■ designers can choose one of three options: (1) Use embedded multiplier resources available in the target device family (previously available).

-

Page 157: Jtag Debug Module Revisions

Support for HardCopy devices (previous versions of the JTAG debug module did not May 2005 support HardCopy devices). Bug fix: When using the Nios II/s and Nios II/f cores, hardware breakpoints may have falsely December 2004 triggered when placed on the instruction sequentially following a jmp, trap, or any branch instruction. -

Page 158: Document Revision History

6–8 Chapter 6: Nios II Processor Revision History Document Revision History Document Revision History Table 6–7. Document Revision History Date Version Changes Added information on ECC support. ■ February 2014 13.1.0 Removed HardCopy information. ■ Removed references to SOPC Builder. -

Page 159: Data Types

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. -

Page 160: Register Usage

Chapter 7: Application Binary Interface Register Usage Register Usage The ABI adds additional usage conventions to the Nios II register file defined in the Programming Model chapter of the Nios II Processor Reference Handbook. Table 7–2. Nios II ABI Register Usage (Part 1 of 2) -

Page 161: Stacks

Chapter 7: Application Binary Interface 7–3 Stacks Table 7–2. Nios II ABI Register Usage (Part 2 of 2) Used by Callee Register Name Normal Usage Compiler Saved Return address Notes to Table 7–2: (1) A function can use one of these registers if it saves it first. The function must restore the register’s original value before exiting. - Page 162 The space allocated by alloca() replaces the outgoing arguments and the outgoing arguments get new space allocated at the bottom of the frame. The Nios II C/C++ compiler maintains a frame pointer for any function that calls alloca(), even if -fomit-frame-pointer is spec if ed Figure 7–2.

- Page 163 7–3. Function Prologues The Nios II C/C++ compiler generates function prologues that allocate the stack frame of a function for storage of stack temporaries and outgoing arguments. In addition, each prologue is responsible for saving the state of the calling function. This entails saving certain registers on the stack.

-

Page 164: Arguments And Return Values

An even better way to find out what the prologue has done is to use information stored in the DWARF-2 debugging fields of the executable and linkable format (.elf) file. The instructions found in a Nios II function prologue perform the following tasks: Adjust the stack pointer (to allocate the frame) ■... -

Page 165: Return Values

STRUCT b(int i, int j) return result; void a(...) value = b(i, j); Example 7–2, if the result type is no larger than 8 bytes, b() returns its result in r2 and r3. February 2014 Altera Corporation Nios II Processor Reference Handbook... -

Page 166: Dwarf-2 Definition

7–8 Chapter 7: Application Binary Interface DWARF-2 Definition If the return type is larger than 8 bytes, the Nios II C/C++ compiler treats this program as if a() had passed a pointer to b(). Example 7–3 shows how the Nios II... - Page 167 Chapter 7: Application Binary Interface 7–9 Relocation Table 7–4. Nios II Relocation Calculation (Part 2 of 3) Overflow Relocated Address Bit Mask Bit Shift Name Value check R_NIOS2_IMM6 (S + A) & 0x3F 0x00000FC0 R_NIOS2_IMM8 (S + A) & 0xFF...

-

Page 168: Abi For Linux Systems

7–10 Chapter 7: Application Binary Interface ABI for Linux Systems Table 7–4. Nios II Relocation Calculation (Part 3 of 3) Overflow Relocated Address Bit Mask Bit Shift Name Value check Refer to “Copy Relocation” on R_NIOS2_COPY page 7–12 R_NIOS2_GLOB_DAT 0xFFFFFFFF Refer to “Jump Slot Relocation”... - Page 169 Table 7–6. Table 7–6. Relocation Operator R_NIOS2_GOT16 %got R_NIOS2_CALL16 %call R_NIOS2_GOTOFF_LO %gotoff_hiadj R_NIOS2_GOTOFF_HA %gotoff_lo R_NIOS2_PCREL_LO %hiadj R_NIOS2_PCREL_HA R_NIOS2_TLS_GD16 %tls_gd R_NIOS2_TLS_LDM16 %tls_ldm R_NIOS2_TLS_LDO16 %tls_ldo R_NIOS2_TLS_IE16 %tls_ie R_NIOS2_TLS_LE16 %tls_le R_NIOS2_TLS_DTPREL %tls_ldo R_NIOS2_GOTOFF %gotoff February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 170 7–17. Thread-Local Storage The Nios II processor uses the Variant I model for thread-local storage. The end of the thread control block (TCB) is located 0x7000 bytes before the thread pointer. The TCB is eight bytes long. The first word is the dynamic thread pointer (DTV) pointer and the second word is reserved.

- Page 171 There is no GOT slot associated with the local exec model. Debug information uses the GNU extension DW_OP_GNU_push_tls_address, as shown in Example 7–11. Example 7–11. Debug Information .byte 0x03 # DW_OP_addr .word %tls_ldo(x) # R_NIOS2_TLS_DTPREL x .byte 0xe0 # DW_OP_GNU_push_tls_address February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 172 Illegal instruction SIGILL Break instruction SIGTRAP Supervisor-only data address SIGSEGV Misaligned data address SIGBUS Misaligned destination address SIGBUS Division error SIGFPE TLB Permission Violation (read) SIGSEGV TLB Permission Violation (write) SIGSEGV Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 173 If a caller-saved register is used the function must save and restore it around calls. If a callee-saved register is used it must be saved and restored around the current function. Examples in this document use r22 for the GOT pointer. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 174 Example 7–16. Accessing Function or Variable in Current Shared Object orhi r3, %gotoff_hiadj(x) # R_NIOS2_GOTOFF_HA x addi r3, r3, %gotoff_lo(x) # R_NIOS2_GOTOFF_LO x r3, r22, r3 # Address of x in r3 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 175 R_NIOS2_JUMP_SLOT. The dynamic linker may immediately resolve it, or may leave it unmodified for lazy binding. The link editor fills in an initial value pointing to the lazy binding stubs at the start of the PLT section. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 176 GOT[1] in r14, and the relocation index times four in r15. The resolver updates the corresponding PLT GOT entry so that the PLT entry transfers control directly to the target in the future, and then transfers control to the target. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 177 %lo(_GLOBAL_OFFSET_TABLE_+4)(r13) r13, %lo(_GLOBAL_OFFSET_TABLE_+8)(r13) Linux Program Interpreter The program interpreter is /lib/ld.so.1. Linux Initialization and Termination Functions The implementation is responsible for calling DT_INIT(), DT_INIT_ARRAY(), DT_PREINIT_ARRAY(), DT_FINI(), and DT_FINI_ARRAY(). February 2014 Altera Corporation Nios II Processor Reference Handbook...

-

Page 178: Document Revision History

Atomic Operations The Nios II architecture does not have atomic operations (such as load linked and store conditional). Atomic operations are emulated using a kernel system call via the trap instruction. The toolchain provides intrinsic functions which perform the system call. - Page 179 7.0.0 Maintenance release. November 2006 6.1.0 Maintenance release. May 2006 6.0.0 Maintenance release. October 2005 5.1.0 Maintenance release. May 2005 5.0.0 Maintenance release. September 2004 Maintenance release. May 2004 Initial release. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 180 7–22 Chapter 7: Application Binary Interface Document Revision History Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 181: Chapter 8. Instruction Set Reference

Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. - Page 182 ■ A 6-bit opcode field A 26-bit immediate data field ■ J-type instructions, such as call and jmpi, transfer execution anywhere within a 256-MB range. Table 8–3. J-Type Instruction Format IMM26 Nios II Processor Reference Handbook February 2014 Altera Corporation...

-

Page 183: Instruction Opcodes

Chapter 8: Instruction Set Reference 8–3 Instruction Opcodes Instruction Opcodes The OP field in the Nios II instruction word specifies the major class of an opcode as listed in Table 8–1 Table 8–2. Most values of OP are encodings for I-type instructions. -

Page 184: Assembler Pseudo-Instructions

IMMED orhi rB, r0, %hiadj(label) movia rB, label addi, rB, r0, %lo(label) movui rB, IMMED ori rB, r0, IMMED add r0, r0, r0 subi rB, rA, IMMED addi rB, rA, (-IMMED) Nios II Processor Reference Handbook February 2014 Altera Corporation... -

Page 185: Assembler Macros

8–4: (1) Refer to the Application Binary Interface chapter of the Nios II Processor Reference Handbook for more information about global pointers. Instruction Set Reference The following pages list all Nios II instruction mnemonics in alphabetical order. Table 8–5. Notation Conventions (Part 1 of 2) - Page 186 ■ TLB permission violation (execute) ■ MPU region violation (instruction) For information about these and all Nios II exceptions, refer to the Programming Model chapter of the Nios II Processor Reference Handbook. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 187 # Branch if overflow occurred Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x31 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

-

Page 188: Add Immediate

# Branch if overflow occurred Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x04 Nios II Processor Reference Handbook February 2014 Altera Corporation... - Page 189 Calculates the bitwise logical AND of rA and rB and stores the result in rC. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x0e 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 190 Calculates the bitwise logical AND of rA and (IMM16 : 0x0000) and stores the result in rB. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit unsigned immediate value IMM16 0x2c Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 191 Calculates the bitwise logical AND of rA and (0x0000 : IMM16) and stores the result in rB. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit unsigned immediate value IMM16 0x0c February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 192 Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x26 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 193 Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x0e February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 194 IMM16 are always zero, because instruction addresses must be word-aligned. Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x2e Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 195 Description: If (signed) rA > (signed) rB, then bgt transfers program control to the instruction at label. Pseudo-instruction: bgt is implemented with the blt instruction by swapping the register operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 196 Description: If (unsigned) rA > (unsigned) rB, then bgtu transfers program control to the instruction at label. Pseudo-instruction: bgtu is implemented with the bltu instruction by swapping the register operands. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 197 Description: If (signed) rA <= (signed) rB, then ble transfers program control to the instruction at label. Pseudo-instruction: ble is implemented with the bge instruction by swapping the register operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 198 Description: If (unsigned) rA <= (unsigned) rB, then bleu transfers program counter to the instruction at label. Pseudo-instruction: bleu is implemented with the bgeu instruction by swapping the register operands. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 199 Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x16 February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 200 IMM16 are always zero, because instruction addresses must be word-aligned. Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x36 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 201 Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x1e February 2014 Altera Corporation Nios II Processor Reference Handbook...

-

Page 202: Unconditional Branch

The two least-significant bits of IMM16 are always zero, because instruction addresses must be word-aligned. Exceptions: Misaligned destination address Instruction Type: Instruction Fields: IMM16 = 16-bit signed immediate value IMM16 0x06 Nios II Processor Reference Handbook February 2014 Altera Corporation... - Page 203 Some debuggers support break and break 0 instructions in source code. These debuggers treat the break instruction as a normal breakpoint. Exceptions: Break Instruction Type: Instruction Fields: IMM5 = Type of breakpoint 0x1e 0x34 IMM5 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 204 Exceptions: Misaligned destination address Supervisor-only instruction Instruction Type: Instruction Fields: None 0x1e 0x09 0x3a Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 205 Usage: call can transfer execution anywhere within the 256-MB range determined by PC . The 31..28 Nios II GNU linker does not automatically handle cases in which the address is out of this range. Exceptions: None Instruction Type: Instruction Fields:...

- Page 206 Usage: callr is used to dereference C-language function pointers. Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA 0x1f 0x1d 0x3a Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 207 # Implements rC = !rA Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x20 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 208 == operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x20 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 209 >= operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x08 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 210 >= operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x08 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 211 >= operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x28 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 212 >= operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit unsigned immediate value IMM16 0x28 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 213 If rA > rB, then stores 1 to rC; otherwise stores 0 to rC. Usage: cmpgt performs the signed > operation of the C programming language. Pseudo-instruction: cmpgt is implemented with the cmplt instruction by swapping its rA and rB operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 214 > operation of the C programming language. The maximum allowed value of IMMED is 32766. The minimum allowed value is –32769. Pseudo-instruction: cmpgti is implemented using a cmpgei instruction with an IMM16 immediate value of IMMED + 1. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 215 If rA > rB, then stores 1 to rC; otherwise stores 0 to rC. Usage: cmpgtu performs the unsigned > operation of the C programming language. Pseudo-instruction: cmpgtu is implemented with the cmpltu instruction by swapping its rA and rB operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 216 > operation of the C programming language. The maximum allowed value of IMMED is 65534. The minimum allowed value is 0. Pseudo-instruction: cmpgtui is implemented using a cmpgeui instruction with an IMM16 immediate value of IMMED + 1. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 217 If rA <= rB, then stores 1 to rC; otherwise stores 0 to rC. Usage: cmple performs the signed <= operation of the C programming language. Pseudo-instruction: cmple is implemented with the cmpge instruction by swapping its rA and rB operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 218 <= operation of the C programming language. The maximum allowed value of IMMED is 32766. The minimum allowed value is –32769. Pseudo-instruction: cmplei is implemented using a cmplti instruction with an IMM16 immediate value of IMMED + 1. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 219 If rA <= rB, then stores 1 to rC; otherwise stores 0 to rC. Usage: cmpleu performs the unsigned <= operation of the C programming language. Pseudo-instruction: cmpleu is implemented with the cmpgeu instruction by swapping its rA and rB operands. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 220 <= operation of the C programming language. The maximum allowed value of IMMED is 65534. The minimum allowed value is 0. Pseudo-instruction: cmpleui is implemented using a cmpltui instruction with an IMM16 immediate value of IMMED + 1. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 221 < operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x10 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 222 < operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x10 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 223 < operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x30 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 224 < operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit unsigned immediate value IMM16 0x30 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 225 != operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB C = Register index of operand rC 0x18 0x3a February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 226 != operation of the C programming language. Exceptions: None Instruction Type: Instruction Fields: A = Register index of operand rA B = Register index of operand rB IMM16 = 16-bit signed immediate value IMM16 0x18 Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 227 0, c6, r7, r8 Description: The custom opcode provides access to up to 256 custom instructions allowed by the Nios II architecture. The function implemented by a custom instruction is user-defined and is specified with the Nios_II Processor parameter editor in Qsys. The 8-bit immediate N field specifies which custom instruction to use.

- Page 228 There is no divide-by-zero exception. After dividing –2147483648 by –1, the value of rC is undefined (the number +2147483648 is not representable in 32 bits). There is no overflow exception. Nios II processors that do not implement the div instruction cause an unimplemented instruction exception. Usage:...

- Page 229 After attempted division by zero, the value of rC is undefined. There is no divide-by-zero exception. Nios II processors that do not implement the divu instruction cause an unimplemented instruction exception. Usage:...

- Page 230 Use eret to return from traps, external interrupts, and other exception handling routines. Note that before returning from hardware interrupt exceptions, the exception handler must adjust the ea register. Exceptions: Misaligned destination address Supervisor-only instruction Instruction Type: Instruction Fields: None 0x1d 0x1e 0x01 0x3a Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 231 Clear the valid bit for the line. ■ If the Nios II processor core does not have a data cache, the flushd instruction performs no operation. Usage: Use flushd to write dirty lines back to memory even if the addressed memory location is not in the cache, and then flush the cache line.

- Page 232 Clear the valid bit for the line. ■ If the Nios II processor core does not have a data cache, the flushda instruction performs no operation. Usage: Use flushda to write dirty lines back to memory only if the addressed memory location is currently in the cache, and then flush the cache line.

- Page 233 Ignoring the tag, flushi identifies the instruction cache line associated with the byte address in rA, and invalidates that line. If the Nios II processor core does not have an instruction cache, the flushi instruction performs no operation. For more information about the data cache, refer to the Cache and Tightly Coupled Memory chapter of the Nios II Software Developer’s Handbook.

- Page 234 Ensures that any instructions prefetched after the flushp instruction are removed from the pipeline. Usage: Use flushp before transferring control to newly updated instruction memory. Exceptions: None Instruction Type: Instruction Fields: None 0x04 0x3a Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 235 Clear the valid bit for the line. ■ If the Nios II processor core does not have a data cache, the initd instruction performs no operation. Usage: Use initd after processor reset and before accessing data memory to initialize the processor’s...

- Page 236 Clear the valid bit for the line. ■ If the Nios II processor core does not have a data cache, the initda instruction performs no operation. Usage: Use initda to skip writing dirty lines back to memory and to flush the cache line only if the addressed memory location is currently in the cache.

- Page 237 Ignoring the tag, initi identifies the instruction cache line associated with the byte address in ra, and initi invalidates that line. If the Nios II processor core does not have an instruction cache, the initi instruction performs no operation. Usage: This instruction is used to initialize the processor’s instruction cache.

- Page 238 It is illegal to jump to the address contained in register r31. To return from subroutines called by call or callr, use ret instead of jmp. Exceptions: Misaligned destination address Instruction Type: Instruction Fields: A = Register index of operand rA 0x0d 0x3a Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 239 Usage: jmpi is a low-overhead local jump. jmpi can transfer execution anywhere within the 256-MB range determined by PC . The Nios II GNU linker does not automatically handle cases in 31..28 which the address is out of this range.

- Page 240 16-bit immediate value. Loads register rB with the desired memory byte, sign extending the 8-bit value to 32 bits. In Nios II processor cores with a data cache, this instruction may retrieve the desired data from the cache instead of from memory.

- Page 241 In processors without a data cache, ldbuio acts like ldbu. For more information on data cache, refer to the Cache and Tightly Coupled Memory chapter of the Nios II Software Developer’s Handbook. Exceptions: Supervisor-only data address Misaligned data address...

- Page 242 For more information on data cache, refer to the Cache and Tightly Coupled Memory chapter of the Nios II Software Developer’s Handbook. Exceptions: Supervisor-only data address Misaligned data address TLB permission violation (read)

- Page 243 In processors without a data cache, ldhuio acts like ldhu. For more information on data cache, refer to the Cache and Tightly Coupled Memory chapter of the Nios II Software Developer’s Handbook. Exceptions: Supervisor-only data address Misaligned data address...

- Page 244 Avalon-MM data transfer. In processors without a data cache, ldwio acts like ldw. For more information on data cache, refer to the Cache and Tightly Coupled Memory chapter of the Nios II Software Developer’s Handbook. Exceptions: Supervisor-only data address Misaligned data address...

- Page 245 ← rA Operation: Assembler Syntax: mov rC, rA Example: mov r6, r7 Description: Moves the contents of rA to rC. Pseudo-instruction: mov is implemented as add rC, rA, r0. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 246 An alternative method to load a 32-bit constant into a register uses the %hiadj() macro and the addi instruction as shown in the following code: movhi rB, %hiadj(value) addi rB, rB, %lo(value) Pseudo-instruction: movhi is implemented as orhi rB, r0, IMMED. Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 247 The maximum allowed value of IMMED is 32767. The minimum allowed value is –32768. To load a 32-bit constant into a register, refer to the movhi instruction. Pseudo-instruction: movi is implemented as addi rB, r0, IMMED. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 248 Operation: Assembler Syntax: movia rB, label Example: movia r6, function_address Description: Writes the address of label to rB. Pseudo-instruction: movia is implemented as: orhi rB, r0, %hiadj(label) addi rB, rB, %lo(label) Nios II Processor Reference Handbook February 2014 Altera Corporation...

- Page 249 The maximum allowed value of IMMED is 65535. The minimum allowed value is 0. To load a 32-bit constant into a register, refer to the movhi instruction. Pseudo-instruction: movui is implemented as ori rB, r0, IMMED. February 2014 Altera Corporation Nios II Processor Reference Handbook...

- Page 250 Multiplies rA times rB and stores the 32 low-order bits of the product to rC. The result is the same whether the operands are treated as signed or unsigned integers. Nios II processors that do not implement the mul instruction cause an unimplemented instruction exception.

- Page 251 Stores the 32 low-order bits of the product to rB. The result is independent of whether rA is treated as a signed or unsigned number. Nios II processors that do not implement the muli instruction cause an unimplemented instruction exception.

- Page 252 Description: Treating rA and rB as signed integers, mulxss multiplies rA times rB, and stores the 32 high-order bits of the product to rC. Nios II processors that do not implement the mulxss instruction cause an unimplemented instruction exception. Usage: Use mulxss and mul to compute the full 64-bit product of two 32-bit signed integers.

- Page 253 Treating rA as a signed integer and rB as an unsigned integer, mulxsu multiplies rA times rB, and stores the 32 high-order bits of the product to rC. Nios II processors that do not implement the mulxsu instruction cause an unimplemented instruction exception.