Table of Contents

Advertisement

Quick Links

REJ09B0222-0130

16

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Technology Corp. without notice. Please review the latest information published

by Renesas Technology Corp. through various means, including the Renesas Technology

Corp. website (http://www.renesas.com).

Rev.1.30

Revision Date: Apr 14, 2006

R8C/18

, R8C/19

Group

RENESAS 16-BIT SINGLE-CHIP MCU

R8C FAMILY / R8C/1x SERIES

Group

Hardware Manual

www.renesas.com

Advertisement

Table of Contents

Summary of Contents for Renesas R8C/18 Series

- Page 1 All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Technology Corp. without notice. Please review the latest information published by Renesas Technology Corp. through various means, including the Renesas Technology Corp.

- Page 2 Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers con- tact Renesas Technology Corp.

- Page 3 General Precautions in the Handling of MPU/MCU Products The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

- Page 4 The following documents apply to the R8C/18 Group, R8C/19 Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site. Document Type...

- Page 5 Notation of Numbers and Symbols The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below. Register Names, Bit Names, and Pin Names Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word “register,”...

- Page 6 Register Notation The symbols and terms used in register diagrams are described below. XXX Register Symbol Address After Reset Bit Symbol Bit Name Function b1 b0 XXX bits XXX0 1 0: XXX 0 1: XXX 1 0: Do not set. XXX1 1 1: XXX Nothing is assigned.

- Page 7 List of Abbreviations and Acronyms Abbreviation Full Form ACIA Asynchronous Communication Interface Adapter bits per second Cyclic Redundancy Check Direct Memory Access DMAC Direct Memory Access Controller Global System for Mobile Communications Hi-Z High Impedance IEBus Inter Equipment bus Input/Output IrDA Infrared Data Association Least Significant Bit...

-

Page 8: Table Of Contents

Table of Contents SFR Page Reference B - 1 Overview Applications ....................1 Performance Overview................2 Block Diagram .....................4 Product Information ..................5 Pin Assignments..................7 Pin Functions.....................10 Central Processing Unit (CPU) Data Registers (R0, R1, R2, and R3)............14 Address Registers (A0 and A1)..............14 Frame Base Register (FB) ................14 Interrupt Table Register (INTB) ..............14 Program Counter (PC) ................14... - Page 9 Special Function Registers (SFRs) Resets Hardware Reset ..................24 5.1.1 When Power Supply is Stable ............24 5.1.2 Power On....................24 Power-On Reset Function .................26 Voltage Monitor 1 Reset ................27 Voltage Monitor 2 Reset................27 Watchdog Timer Reset................27 Software Reset..................27 Programmable I/O Ports Functions of Programmable I/O Ports ............28 Effect on Peripheral Functions ..............28 Pins Other than Programmable I/O Ports..........28 Port settings ....................35...

- Page 10 10.3 CPU Clock and Peripheral Function Clock..........62 10.3.1 System Clock..................62 10.3.2 CPU Clock ..................62 10.3.3 Peripheral Function Clock (f1, f2, f4, f8, and f32) .......62 10.3.4 fRING and fRING128................62 10.3.5 fRING-fast...................62 10.3.6 fRING-S ....................62 10.4 Power Control....................63 10.4.1 Standard Operating Mode ..............63 10.4.2 Wait Mode ..................64 10.4.3...

- Page 11 12.5 Notes on Interrupts..................94 12.5.1 Reading Address 00000h ..............94 12.5.2 SP Setting...................94 12.5.3 External Interrupt and Key Input Interrupt ..........94 12.5.4 Watchdog Timer Interrupt..............94 12.5.5 Changing Interrupt Sources..............95 12.5.6 Changing Interrupt Control Register Contents ........96 13. Watchdog Timer 13.1 Count Source Protection Mode Disabled ..........100 13.2 Count Source Protection Mode Enabled ..........101 14.

- Page 12 15.2 Clock Asynchronous Serial I/O (UART) Mode ........157 15.2.1 CNTR0 Pin Select Function..............160 15.2.2 Bit Rate.....................161 15.3 Notes on Serial Interface.................162 16. Comparator 16.1 One-Shot Mode ..................167 16.2 Repeat Mode...................169 16.3 Notes on Comparator ................171 17. Flash Memory Version 17.1 Overview ....................172 17.2 Memory Map ...................174...

- Page 13 19.2 Notes on Interrupts..................218 19.2.1 Reading Address 00000h ..............218 19.2.2 SP Setting..................218 19.2.3 External Interrupt and Key Input Interrupt ........218 19.2.4 Watchdog Timer Interrupt..............218 19.2.5 Changing Interrupt Sources..............219 19.2.6 Changing Interrupt Control Register Contents .........220 19.3 Notes on Timers ..................221 19.3.1 Notes on Timer X................221 19.3.2...

- Page 14 SFR Page Reference Address Register Symbol Page Address Register Symbol Page 0000h 0040h 0001h 0041h 0002h 0042h 0003h 0043h 0004h Processor Mode Register 0 0044h 0005h Processor Mode Register 1 0045h 0006h System Clock Control Register 0 0046h 0007h System Clock Control Register 1 0047h 0008h 0048h...

- Page 15 Address Register Symbol Page Address Register Symbol Page 0080h Timer Z Mode Register TZMR 00C0h A/D Register 0081h 00C1h 0082h 00C2h 0083h 00C3h 0084h Timer Z Waveform Output Control Register 00C4h 0085h Prescaler Z Register PREZ 00C5h 0086h Timer Z Secondary Register TZSC 00C6h 0087h...

-

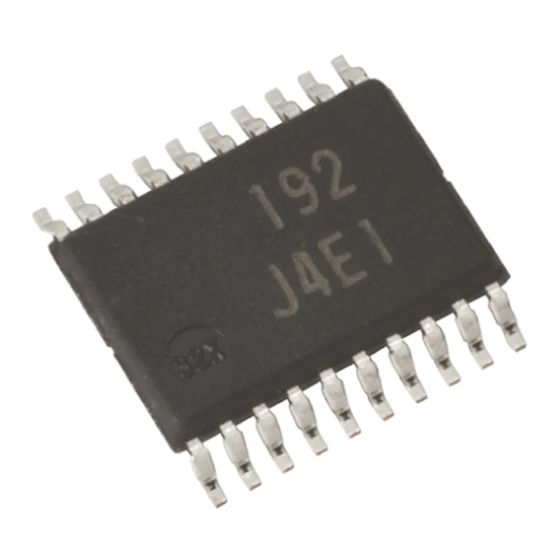

Page 16: Overview

R8C/18 Group, R8C/19 Group REJ09B0222-0130 SINGLE-CHIP 16-BIT CMOS MCU Rev.1.30 Apr 14, 2006 Overview These MCUs are fabricated using a high-performance silicon gate CMOS process, embedding the R8C/Tiny Series CPU core, and is packaged in a 20-pin molded-plastic LSSOP, SDIP or a 28-pin plastic molded-HWQFN. -

Page 17: Performance Overview

R8C/18 Group, R8C/19 Group 1. Overview Performance Overview Table 1.1 outlines the Functions and Specifications for R8C/18 Group and Table 1.2 outlines the Functions and Specifications for R8C/19 Group. Table 1.1 Functions and Specifications for R8C/18 Group Item Specification Number of fundamental 89 instructions instructions Minimum instruction execution... - Page 18 R8C/18 Group, R8C/19 Group 1. Overview Table 1.2 Functions and Specifications for R8C/19 Group Item Specification Number of fundamental 89 instructions instructions Minimum instruction 50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V) execution time 100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V) Operation mode Single-chip Address space...

-

Page 19: Block Diagram

R8C/18 Group, R8C/19 Group 1. Overview Block Diagram Figure 1.1 shows a Block Diagram. I/O ports Port P1 Port P3 Port P4 Peripheral Functions System clock generator Comparator Timers × XIN-XOUT (1 bit 4 channels) High-speed on-chip oscillator Timer X (8 bits) UART or Low-speed on-chip Timer Z (8 bits) -

Page 20: Product Information

2: 8 KB 3: 12 KB 4: 16 KB R8C/18 Group R8C/Tiny Series Memory type F: Flash memory Renesas MCU Renesas semiconductors Figure 1.2 Type Number, Memory Size, and Package of R8C/18 Group Rev.1.30 Apr 14, 2006 Page 5 of 233... - Page 21 2: 8 KB 3: 12 KB 4: 16 KB R8C/19 Group R8C/Tiny Series Memory type F: Flash memory Renesas MCU Renesas semiconductors Figure 1.3 Type Number, Memory Size, and Package of R8C/19 Group Rev.1.30 Apr 14, 2006 Page 6 of 233...

-

Page 22: Pin Assignments

R8C/18 Group, R8C/19 Group 1. Overview Pin Assignments Figure 1.4 shows Pin Assignments for PLSP0020JB-A Package (Top View), Figure 1.5 shows Pin Assignments for PRDP0020BA-A Package (Top View) and Figure 1.6 shows Pin Assignments for PWQN0028KA-B Package (Top View). PIN assignments (top view) P3_5/CMP1_2 P3_4/CMP1_1 P3_3/TCIN/INT3/CMP1_0... - Page 23 R8C/18 Group, R8C/19 Group 1. Overview PIN assignments (top view) P3_5/CMP1_2 P3_4/CMP1_1 P3_3/TCIN/INT3/CMP1_0 P3_7/CNTR0/TXD1 P1_0/KI0/AN8/CMP0_0 RESET P1_1/KI1/AN9/CMP0_1 XOUT/P4_7 P4_2/VREF VSS/AVSS P1_2/KI2/AN10/CMP0_2 XIN/P4_6 P1_3/KI3/AN11/TZOUT VCC/AVCC P1_4/TXD0 MODE P1_5/RXD0/CNTR01/INT11 P4_5/INT0/RXD1 P1_6/CLK0 P1_7/CNTR00/INT10 NOTE: 1. P4_7 is an input-only port. Package: PRDP0020BA-A(20P4B) Figure 1.5 Pin Assignments for PRDP0020BA-A Package (Top View) Rev.1.30 Apr 14, 2006...

- Page 24 R8C/18 Group, R8C/19 Group 1. Overview PIN Assignment (top view) 21 20 19 18 17 16 15 P1_1/AN9/KI1/CMP0_1 P1_4/TXD0 P1_5/RXD0/CNTR01/INT11 P1_0/AN8/KI0/CMP0_0 P1_6/CLK0 P3_3/TCIN/INT3/CMP1_0 R8C/18 Group P1_7/CNTR00/INT10 P3_4/CMP1_1 R8C/19 Group P4_5/INT0/RXD1 P3_5/CMP1_2 MODE P3_7/CNTR0/TXD1 VCC/AVCC RESET NOTES: 1. P4_7 is a port for the input. Package: PWQN0028KA-B(28PJW-B) Figure 1.6 Pin Assignments for PWQN0028KA-B Package (Top View)

-

Page 25: Pin Functions

R8C/18 Group, R8C/19 Group 1. Overview Pin Functions Table 1.5 lists Pin Functions, Table 1.6 lists Pin Name Information by Pin Number of PLSP0020JB-A, PRDP0020BA-A packages, and Table 1.7 lists Pin Name Information by Pin Number of PWQN0028KA- B package. Table 1.5 Pin Functions Type... - Page 26 R8C/18 Group, R8C/19 Group 1. Overview Table 1.6 Pin Name Information by Pin Number of PLSP0020JB-A, PRDP0020BA-A packages I/O Pin Functions for Peripheral Modules Control Port Number Interrupt Timer Serial Interface Comparator P3_5 CMP1_2 P3_7 TXD1 CNTR0 RESET XOUT P4_7 VSS/AVSS P4_6 VCC/AVCC...

- Page 27 R8C/18 Group, R8C/19 Group 1. Overview Table 1.7 Pin Name Information by Pin Number of PWQN0028KA-B package I/O Pin of Peripheral Function Control Port Number Interrupt Timer Serial Interface Comparator XOUT P4_7 VSS/AVSS P4_6 VCC/AVCC MODE P4_5 RXD1 INT0 P1_7 CNTR00 INT10 P1_6...

-

Page 28: Central Processing Unit (Cpu)

R8C/18 Group, R8C/19 Group 2. Central Processing Unit (CPU) Central Processing Unit (CPU) Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank. b8b7 R0H (high-order of R0) R0L (low-order of R0) -

Page 29: Data Registers (R0, R1, R2, And R3)

R8C/18 Group, R8C/19 Group 2. Central Processing Unit (CPU) Data Registers (R0, R1, R2, and R3) R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. -

Page 30: Interrupt Enable Flag (I)

R8C/18 Group, R8C/19 Group 2. Central Processing Unit (CPU) 2.8.7 Interrupt Enable Flag (I) The I flag enables maskable interrupts. Interrupts are disabled when the I flag is set to 0, and are enabled when the I flag is set to 1. The I flag is set to 0 when an interrupt request is acknowledged. -

Page 31: Memory

R8C/18 Group, R8C/19 Group 3. Memory Memory R8C/18 Group Figure 3.1 is a Memory Map of R8C/18 Group. The R8C/18 Group has 1 Mbyte of address space from addresses 00000h to FFFFFh. The internal ROM area is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM is allocated addresses 0C000h to 0FFFFh. -

Page 32: R8C/19 Group

R8C/18 Group, R8C/19 Group 3. Memory R8C/19 Group Figure 3.2 is a Memory Map of R8C/19 Group. The R8C/19 group has 1 Mbyte of address space from addresses 00000h to FFFFFh. The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM area is allocated addresses 0C000h to 0FFFFh. -

Page 33: Special Function Registers (Sfrs)

R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs) Special Function Registers (SFRs) An SFR (special function register) is a control register for a peripheral function. Tables 4.1 to 4.4 list the special function registers. Table 4.1 SFR Information (1) Address Register Symbol... - Page 34 R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs) Table 4.2 SFR Information (2) Address Register Symbol After reset 0040h 0041h 0042h 0043h 0044h 0045h 0046h 0047h 0048h 0049h 004Ah 004Bh 004Ch 004Dh Key Input Interrupt Control Register KUPIC XXXXX000b 004Eh Comparator Conversion Interrupt Control Register ADIC...

- Page 35 R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs) Table 4.3 SFR Information (3) Address Register Symbol After reset 0080h Timer Z Mode Register TZMR 0081h 0082h 0083h 0084h Timer Z Waveform Output Control Register 0085h Prescaler Z Register PREZ 0086h Timer Z Secondary Register TZSC...

- Page 36 R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs) Table 4.4 SFR Information (4) Address Register Symbol After reset 00C0h A/D Register 00C1h 00C2h 00C3h 00C4h 00C5h 00C6h 00C7h 00C8h 00C9h 00CAh 00CBh 00CCh 00CDh 00CEh 00CFh 00D0h 00D1h 00D2h 00D3h 00D4h A/D Control Register 2...

-

Page 37: Resets

R8C/18 Group, R8C/19 Group 5. Resets Resets The following resets are implemented: hardware reset, power-on reset, voltage monitor 1 reset, voltage monitor 2 reset, watchdog timer reset, and software reset. Table 5.1 lists the Reset Names and Sources. Table 5.1 Reset Names and Sources Reset Name Source... - Page 38 R8C/18 Group, R8C/19 Group 5. Resets Table 5.2 shows the Pin Functions after Reset, Figure 5.2 shows CPU Register Status after Reset and Figure 5.3 shows Reset Sequence. Table 5.2 Pin Functions after Reset Pin Name Pin Functions Input port P3_3 to P3_5, P3_7 Input port P4_2, P4_5...

-

Page 39: Hardware Reset

R8C/18 Group, R8C/19 Group 5. Resets Hardware Reset A reset is applied using the RESET pin. When an “L” signal is applied to the RESET pin while the supply voltage meets the recommended operating conditions, pins, CPU, and SFRs are reset (refer to Table 5.2 Pin Functions after Reset). - Page 40 R8C/18 Group, R8C/19 Group 5. Resets 2.7 V RESET RESET 0.2 VCC or below td(P-R) + 500 µs or more NOTE: 1. Refer to 18. Electrical Characteristics. Figure 5.4 Example of Hardware Reset Circuit and Operation Power supply voltage detection circuit 2.7 V RESET...

-

Page 41: Power-On Reset Function

R8C/18 Group, R8C/19 Group 5. Resets Power-On Reset Function When the RESET pin is connected to the VCC pin via a pull-up resistor of about 5 kΩ, and the VCC pin voltage level rises, the power-on reset function is enabled and the MCU resets its pins, CPU, and SFR. When a capacitor is connected to the RESET pin, always keep the voltage to the RESET pin 0.8VCC or more. -

Page 42: Voltage Monitor 1 Reset

R8C/18 Group, R8C/19 Group 5. Resets Voltage Monitor 1 Reset A reset is applied using the on-chip voltage detection 1 circuit. The voltage detection 1 circuit monitors the input voltage to the VCC pin. The voltage to monitor is Vdet1. When the input voltage to the VCC pin reaches the Vdet1 level or below, the pins, CPU, and SFR are reset. -

Page 43: Programmable I/O Ports

R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Programmable I/O Ports There are 13 programmable Input/Output ports (I/O ports) P1, P3_3 to P3_5, P3_7, and P4_5. P4_2 can be used as an input-only port. Also, P4_6 and P4_7 can be used as input-only ports if the main clock oscillation circuit is not used. - Page 44 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports P1_0 to P1_3 Pull-up selection Direction register Output from individual peripheral function Data bus Port latch (Note 1) Drive capacity selection Input to individual peripheral function Analog input P1_4 Pull-up selection Direction register Output from individual peripheral function Data bus...

- Page 45 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports P1_6, P1_7 Pull-up selection Direction register Output from individual peripheral function Data bus Port latch (Note 1) Input to individual peripheral function P3_3 Pull-up selection Direction register Output from individual peripheral function Data bus Port latch (Note 1)

- Page 46 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports P4_2 Vref of comparator (Note 4) Data bus P4_5 Pull-up selection Direction register Data bus Port latch (Note 4) Digital Input to individual peripheral function filter P4_6/XIN Data bus (Note 4) Clocked inverter (Note 2) P4_7/XOUT (Note 3)

- Page 47 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports MODE MODE signal input (Note 1) RESET RESET signal input (Note 1) NOTES : symbolizes a parasitic diode. Ensure the input voltage to each port does not exceed VCC. Figure 6.4 Configuration of I/O Pins Rev.1.30 Apr 14, 2006 Page 32 of 233...

- Page 48 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports (1, 2) Port Pi Direction Register (i = 1, 3, 4) b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 00E3h 00E7h 00EAh Bit Symbol Bit Name Function PDi_0 Port Pi0 direction bit 0 : Input mode (functions as an input port)

- Page 49 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Pull-Up Control Register 0 b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset 00FCh 00XX0000b PUR0 Bit Symbol Bit Name Function (b1-b0) Reserved bits Set to 0. PU02 P1_0 to P1_3 pull-up 0 : Not pulled up 1 : Pulled up PU03...

-

Page 50: Port Settings

R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Port Settings Tables 6.4 to 6.17 list the port settings. Table 6.4 Port P1_0/KI0/AN8/CMP0_0 Register PUR0 KIEN ADCON0 TCOUT Function PD1_0 PU02 DRR0 KI0EN CH2, CH1, CH0, ADGSEL0 TCOUT0 XXXX Input port (not pulled up) XXXX Input port (pulled up) XXXX... - Page 51 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Table 6.7 Port P1_3/KI3/AN11/TZOUT Register PUR0 KIEN ADCON0 TZMR TZOC Function CH2, CH1, CH0, TZMOD1, PD1_3 PU02 DRR3 KI3EN TZOCNT ADGSEL0 TZMOD0 XXXX Input port (not pulled up) XXXX Input port (pulled up) XXXX KI3 input 1111b...

- Page 52 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Table 6.10 Port P1_6/CLK0 Register PUR0 U0MR Function PD1_6 PU03 SMD2, SMD0, CKDIR Other than 010b Input port (not pulled up) Other than 010b Input port (pulled up) Setting CLK0 (external clock) input Value Other than 010b Output port...

- Page 53 R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Table 6.14 Port P3_5/CMP1_2 Register PUR0 TCOUT Function PD3_5 PU07 TCOUT5 Input port (not pulled up) Input port (pulled up) Setting Value Output port CMP1_2 output X: 0 or 1 Table 6.15 Port P3_7/CNTR0/TXD1 Register PUR0...

-

Page 54: Unassigned Pin Handling

R8C/18 Group, R8C/19 Group 6. Programmable I/O Ports Unassigned Pin Handling Table 6.18 lists Unassigned Pin Handling. Figure 6.9 shows Unassigned Pin Handling. Table 6.18 Unassigned Pin Handling Pin Name Connection Ports P1, P3_3 to P3_5, • After setting to input mode, connect each pin to VSS via a resistor (pull- P3_7, P4_5 down) or connect each pin to VCC via a resistor (pull-up). -

Page 55: Voltage Detection Circuit

R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Detection Circuit The voltage detection circuit monitors the input voltage to the VCC pin. This circuit can be used to monitor the VCC input voltage by a program. Alternately, voltage monitor 1 reset, voltage monitor 2 interrupt, and voltage monitor 2 reset can also be used. - Page 56 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit VCA27 Voltage detection 2 Noise filter signal Internal reference ≥ Vdet2 voltage VCA1 register VCA26 VCA13 bit Voltage detection 1 signal ≥ Vdet1 Figure 7.1 Block Diagram of Voltage Detection Circuit Voltage monitor 1 reset generation circuit VW1F1 to VW1F0 = 00b = 01b...

- Page 57 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage monitor 2 interrupt/reset generation circuit VW2F1 to VW2F0 = 00b = 01b Voltage detection 2 circuit = 10b VW2C2 bit is set to 0 (not detected) by writing 0 by a program. = 11b fRING-S When VCA27 bit is set to 0 (voltage...

- Page 58 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Detection Register 1 b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 Symbol Address After Reset 0031h 00001000b VCA1 Bit Symbol Bit Name Function — Reserved bits Set to 0. (b2-b0) Voltage detection 2 signal monitor 0 : VCC <...

- Page 59 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Monitor 1 Circuit Control Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After reset VW1C 0036h Hardw are reset : 0000X000b Pow er-on reset, voltage monitor 1 reset : 0100X001b Bit Symbol Bit Name...

- Page 60 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Monitor 2 Circuit Control Register b7 b6 b5 b4 b1 b0 Symbol Address After Reset VW2C 0037h Bit Symbol Bit Name Function Voltage monitor 2 interrupt/reset 0 : Disable VW2C0 (6, 10) enable bit 1 : Enable Voltage monitor 2 digital filter...

-

Page 61: Vcc Input Voltage

R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit VCC Input Voltage 7.1.1 Monitoring Vdet1 Vdet1 cannot be monitored. 7.1.2 Monitoring Vdet2 Set the VCA27 bit in the VCA2 register to 1 (voltage detection 2 circuit enabled). After td(E-A) has elapsed (refer to 18. Electrical Characteristics), Vdet2 can be monitored by the VCA13 bit in the VCA1 register. - Page 62 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage monitor 1 reset Vdet1 Sampling timing Internal reset signal Sampling clock of digital filter x 4 cycles Operation when the VW1C1 bit in the VW1C register is set to 0 (digital filter enabled). Voltage monitor 2 interrupt Vdet2 Sampling...

-

Page 63: Voltage Monitor 1 Reset

R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Monitor 1 Reset Table 7.2 lists the Setting Procedure of Voltage Monitor 1 Reset Associated Bits and Figure 7.8 shows an Operating Example of Voltage Monitor 1 Reset. To use voltage monitor 1 reset to exit stop mode, set the VW1C1 bit in the VW1C register to 1 (digital filter disabled). -

Page 64: Voltage Monitor 2 Interrupt And Voltage Monitor 2 Reset

R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset Table 7.3 lists the Setting Procedure of Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset Associated Bits. Figure 7.9 shows an Operating Example of Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset. - Page 65 R8C/18 Group, R8C/19 Group 7. Voltage Detection Circuit Vdet2 (Typ. 3.30 V) 2.7 V VCA13 bit Sampling clock of digital filter Sampling clock of digital filter × 4 cycles × 4 cycles VW2C2 bit Set to 0 by a program When the VW2C1 bit is set Set to 0 by interrupt request to 0 (digital filter enabled).

-

Page 66: Processor Mode

R8C/18 Group, R8C/19 Group 8. Processor Mode Processor Mode Processor Modes Single-chip mode can be selected as the processor mode. Table 8.1 lists Features of Processor Mode. Figure 8.1 shows the PM0 Register and Figure 8.2 shows the PM1 Register. Table 8.1 Features of Processor Mode Processor Mode... -

Page 67: Bus

R8C/18 Group, R8C/19 Group 9. Bus The bus cycles differ when accessing ROM/RAM, and when accessing SFR. Table 9.1 lists Bus Cycles by Access Space of the R8C/18 Group and Table 9.2 lists Bus Cycles by Access Space of the R8C/19 Group. ROM/RAM and SFR are connected to the CPU by an 8-bit bus. -

Page 68: 10. Clock Generation Circuit

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10. Clock Generation Circuit The clock generation circuit has: • Main clock oscillation circuit • On-chip oscillator (oscillation stop detection function) Table 10.1 lists Specifications of Clock Generation Circuit. Figure 10.1 shows a Clock Generation Circuit. Figures 9.2 to 10.5 show clock associated registers. - Page 69 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit HRA1 register HRA2 register On-chip oscillator clock Frequency adjustable High-speed fRING-fast HRA00 on-chip Watchdog oscillator timer UART1 fRING128 fRING HRA01 = 1 1/128 INT0 Timer C Timer X Timer Z Comparator UART0 HRA01 = 0 Low-speed Power-on...

- Page 70 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit System Clock Control Register 0 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0006h Bit Symbol Bit Name Function — Reserved bits Set to 0. (b1-b0) WAIT peripheral function clock stop 0 : Peripheral function clock does not stop in w ait mode.

- Page 71 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit System Clock Control Register 1 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0007h Bit Symbol Bit Name Function (4, 7, 8) All clock stop control bit 0 : Clock operates. CM10 1 : Stops all clocks (stop mode).

- Page 72 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit Oscillation Stop Detection Register b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 Symbol Address After Reset 000Ch Bit Symbol Bit Name Function Oscillation stop detection enable b1 b0 bits 0 0 : Oscillation stop detection function OCD0...

- Page 73 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit High-Speed On-Chip Oscillator Control Register 0 b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 0 0 Symbol Address After Reset 0020h HRA0 Bit Symbol Bit Name Function High-speed on-chip oscillator enable 0 : High-speed on-chip oscillator off HRA00 1 : High-speed on-chip oscillator on...

- Page 74 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit High-Speed On-Chip Oscillator Control Register 1 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0021h HRA1 When Shipping Function The frequency of the high-speed on-chip oscillator is adjusted w ith bits 0 to 7. High-speed on-chip oscillator frequency = 8 MHz (HRA1 register = value w hen shipping ;...

-

Page 75: Main Clock

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit The clocks generated by the clock generation circuits are described below. 10.1 Main Clock This clock is supplied by a main clock oscillation circuit. This clock is used as the clock source for the CPU and peripheral function clocks. -

Page 76: On-Chip Oscillator Clocks

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.2 On-Chip Oscillator Clocks These clocks are supplied by the on-chip oscillators (high-speed on-chip oscillator and a low-speed on- chip oscillator). The on-chip oscillator clock is selected by the HRA01 bit in the HRA0 register. 10.2.1 Low-Speed On-Chip Oscillator Clock The clock generated by the low-speed on-chip oscillator is used as the clock source for the CPU... -

Page 77: Cpu Clock And Peripheral Function Clock

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.3 CPU Clock and Peripheral Function Clock There are a CPU clock to operate the CPU and a peripheral function clock to operate the peripheral functions. Refer to Figure 10.1 Clock Generation Circuit. 10.3.1 System Clock The system clock is the clock source for the CPU and peripheral function clocks. -

Page 78: Power Control

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.4 Power Control There are three power control modes. All modes other than wait mode and stop mode are referred to as standard operating mode. 10.4.1 Standard Operating Mode Standard operating mode is further separated into four modes. In standard operating mode, the CPU clock and the peripheral function clock are supplied to operate the CPU and the peripheral function clocks. -

Page 79: Wait Mode

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.4.1.1 High-Speed Mode The main clock divided by 1 (no division) provides the CPU clock. If the CM14 bit is set to 0 (low- speed on-chip oscillator on) or the HRA00 bit in the HRA0 register is set to 1 (high-speed on-chip oscillator on), fRING and fRING128 can be used as timers X and C. - Page 80 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.4.2.4 Exiting Wait Mode The MCU exits wait mode by a hardware reset or a peripheral function interrupt. To use a hardware reset to exit wait mode, set bits ILVL2 to ILVL0 for the peripheral function interrupts to 000b (interrupts disabled) before executing the WAIT instruction.

-

Page 81: Stop Mode

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.4.3 Stop Mode Since the oscillator circuits stop in stop mode, the CPU clock and peripheral function clock stop and the CPU and peripheral functions that use these clocks stop operating. The least power required to operate the MCU is in stop mode. - Page 82 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit Figure 10.8 shows the State Transitions in Power Control. Reset Low-speed on-chip oscillator mode OCD2 = 1 HRA01 = 0 CM14 = 0 There are six power control modes. (1) High-speed mode (2) Medium-speed mode (3) High-speed on-chip oscillator mode High-speed mode,...

-

Page 83: Oscillation Stop Detection Function

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.5 Oscillation Stop Detection Function The oscillation stop detection function detects the stop of the main clock oscillation circuit. The oscillation stop detection function can be enabled and disabled by bits OCD1 to OCD0 in the OCD register. - Page 84 R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit Table 10.6 Determining Interrupt Source for Oscillation Stop Detection, Watchdog Timer, and Voltage Monitor 2 Interrupts Generated Interrupt Source Bit Showing Interrupt Cause Oscillation stop detection (a) OCD3 bit in OCD register = 1 ((a) or (b)) (b) Bits OCD1 to OCD0 in OCD register = 11b and OCD2 bit = 1 Watchdog timer...

-

Page 85: Notes On Clock Generation Circuit

R8C/18 Group, R8C/19 Group 10. Clock Generation Circuit 10.6 Notes on Clock Generation Circuit 10.6.1 Stop Mode and Wait Mode When entering stop mode or wait mode, an instruction queue pre-reads 4 bytes from the WAIT instruction or an instruction that sets the CM10 bit in the CM1 register to 1 (stops all clocks) before the program stops. -

Page 86: 11. Protection

R8C/18 Group, R8C/19 Group 11. Protection 11. Protection The protection function protects important registers from being easily overwritten when a program runs out of control. Figure 11.1 shows the PRCR Register. The registers protected by the PRCR register are listed below. -

Page 87: 12. Interrupts

R8C/18 Group, R8C/19 Group 12. Interrupts 12. Interrupts 12.1 Interrupt Overview 12.1.1 Types of Interrupts Figure 12.1 shows the types of Interrupts. Undefined instruction (UND instruction) Overflow (INTO instruction) Software BRK instruction (non-maskable interrupts) INT instruction Interrupt Watchdog timer Oscillation stop detection Special Voltage monitor 2 (non-maskable interrupts) -

Page 88: Software Interrupts

R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.2 Software Interrupts A software interrupt is generated when an instruction is executed. Software interrupts are non- maskable. 12.1.2.1 Undefined Instruction Interrupt The undefined instruction interrupt is generated when the UND instruction is executed. 12.1.2.2 Overflow Interrupt The overflow interrupt is generated when the O flag is set to 1 (arithmetic operation overflow) and the... -

Page 89: Special Interrupts

R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.3 Special Interrupts Special interrupts are non-maskable. 12.1.3.1 Watchdog Timer Interrupt The watchdog timer interrupt is generated by the watchdog timer. Reset the watchdog timer after the watchdog timer interrupt is generated. For details, refer to 13. Watchdog Timer. 12.1.3.2 Oscillation Stop Detection Interrupt The oscillation stop detection interrupt is generated by the oscillation stop detection function. -

Page 90: Interrupts And Interrupt Vectors

R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.5 Interrupts and Interrupt Vectors There are 4 bytes in each vector. Set the starting address of an interrupt routine in each interrupt vector. When an interrupt request is acknowledged, the CPU branches to the address set in the corresponding interrupt vector. - Page 91 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.5.2 Relocatable Vector Tables The relocatable vector tables occupy 256 bytes beginning from the starting address set in the INTB register. Table 12.2 lists the Relocatable Vector Tables. Table 12.2 Relocatable Vector Tables Software Vector Address Interrupt Source Reference...

-

Page 92: Interrupt Control

R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6 Interrupt Control The following describes enabling and disabling the maskable interrupts and setting the priority for acknowledgement. The explanation does not apply to nonmaskable interrupts. Use the I flag in the FLG register, IPL, and bits ILVL2 to ILVL0 in each interrupt control register to enable or disable maskable interrupts. - Page 93 R8C/18 Group, R8C/19 Group 12. Interrupts INT0 Interrupt Control Register b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset 005Dh XX00X000b INT01C Bit Symbol Bit Name Function b2 b1 b0 Interrupt priority level select bits 0 0 0 : Level 0 (interrupt disable) ILVL0 0 0 1 : Level 1 0 1 0 : Level 2...

- Page 94 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.1 I Flag The I flag enables or disables maskable interrupts. Setting the I flag to 1 (enabled) enables maskable interrupts. Setting the I flag to 0 (disabled) disables all maskable interrupts. 12.1.6.2 IR Bit The IR bit is set to 1 (interrupt requested) when an interrupt request is generated.

- Page 95 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.4 Interrupt Sequence An interrupt sequence is performed between an interrupt request acknowledgement and interrupt routine execution. When an interrupt request is generated while an instruction is being executed, the CPU determines its interrupt priority level after the instruction is completed. The CPU starts the interrupt sequence from the following cycle.

- Page 96 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.5 Interrupt Response Time Figure 12.6 shows the Interrupt Response Time. The interrupt response time is the period between an interrupt request generation and the execution of the first instruction in the interrupt routine. The interrupt response time includes the period between interrupt request generation and the completion of execution of the instruction (refer to (a) in Figure 12.6) and the period required to perform the interrupt sequence (20 cycles, refer to (b) in Figure 12.6).

- Page 97 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.7 Saving a Register In the interrupt sequence, the FLG register and PC are saved to the stack. After an extended 16 bits, 4 high-order bits in the PC and 4 high-order (IPL) and 8 low-order bits in the FLG register, are saved to the stack, the 16 low-order bits in the PC are saved.

- Page 98 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.8 Returning from an Interrupt Routine When the REIT instruction is executed at the end of an interrupt routine, the FLG register and PC, which have been saved to the stack, are automatically restored. The program, that was running before the interrupt request was acknowledged, starts running again.

- Page 99 R8C/18 Group, R8C/19 Group 12. Interrupts 12.1.6.10 Interrupt Priority Judgement Circuit The interrupt priority judgement circuit selects the highest priority interrupt, as shown in Figure 12.10. Priority level of each interrupt Highest Level 0 (default value) Compare 0 INT3 Timer Z Timer X INT0 Timer C...

-

Page 100: Int Interrupt

R8C/18 Group, R8C/19 Group 12. Interrupts 12.2 INT Interrupt 12.2.1 INT0 Interrupt The INT0 interrupt is generated by an INT0 input. When using the INT0 interrupt, the INT0EN bit in the INTEN register is set to 1 (enable). The edge polarity is selected using the INT0PL bit in the INTEN register and the POL bit in the INT0IC register. -

Page 101: Int0 Input Filter

R8C/18 Group, R8C/19 Group 12. Interrupts 12.2.2 INT0 Input Filter The INT0 input contains a digital filter. The sampling clock is selected by bits INT0F1 to INT0F0 in the INT0F register. The INT0 level is sampled every sampling clock cycle and if the sampled input level matches three times, the IR bit in the INT0IC register is set to 1 (interrupt requested). -

Page 102: Int1 Interrupt

R8C/18 Group, R8C/19 Group 12. Interrupts 12.2.3 INT1 Interrupt The INT1 interrupt is generated by an INT1 input. The edge polarity is selected by the R0EDG bit in the TXMR register. When the CNTRSEL bit in the UCON register is set to 0, the INT10 pin becomes the INT1 input pin. When the CNTRSEL bit is set to 1, the INT11 pin becomes the INT1 input pin. -

Page 103: Int3 Interrupt

R8C/18 Group, R8C/19 Group 12. Interrupts 12.2.4 INT3 Interrupt The INT3 interrupt is generated by an INT3 input. Set the TCC07 bit in the TCC0 register to 0 (INT3). When the TCC06 bit in the TCC0 register is set to 0, an INT3 interrupt request is generated in synchronization with the count source of timer C. - Page 104 R8C/18 Group, R8C/19 Group 12. Interrupts Timer C Control Register 1 b7 b6 b5 b4 b3 b2 Symbol Address After Reset 009Bh TCC1 Bit Symbol Bit Name Function _____ INT3 filter select bits b1b0 TCC10 0 0 : No filter 0 1 : Filter w ith f1 sampling 1 0 : Filter w ith f8 sampling TCC11...

-

Page 105: Key Input Interrupt

R8C/18 Group, R8C/19 Group 12. Interrupts 12.3 Key Input Interrupt A key input interrupt request is generated by one of the input edges of pins K10 to K13. The key input interrupt can be used as a key-on wake-up function to exit wait or stop mode. The KIiEN (i = 0 to 3) bit in the KIEN register can select whether or not the pins are used as KIi input. - Page 106 R8C/18 Group, R8C/19 Group 12. Interrupts Key Input Enable Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0098h KIEN Bit Symbol Bit Name Function KI0 input enable bit 0 : Disable KI0EN 1 : Enable KI0 input polarity select bit 0 : Falling edge KI0PL...

-

Page 107: Address Match Interrupt

R8C/18 Group, R8C/19 Group 12. Interrupts 12.4 Address Match Interrupt An address match interrupt request is generated immediately before execution of the instruction at the address indicated by the RMADi register (i = 0, 1). This interrupt is used as a break function by the debugger. - Page 108 R8C/18 Group, R8C/19 Group 12. Interrupts Address Match Interrupt Enable Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0009h AIER Bit Symbol Bit Name Function Address match interrupt 0 enable bit 0 : Disable AIER0 1 : Enable Address match interrupt 1 enable bit 0 : Disable...

-

Page 109: Notes On Interrupts

R8C/18 Group, R8C/19 Group 12. Interrupts 12.5 Notes on Interrupts 12.5.1 Reading Address 00000h Do not read address 00000h by a program. When a maskable interrupt request is acknowledged, the CPU reads interrupt information (interrupt number and interrupt request level) from 00000h in the interrupt sequence. -

Page 110: Changing Interrupt Sources

R8C/18 Group, R8C/19 Group 12. Interrupts 12.5.5 Changing Interrupt Sources The IR bit in the interrupt control register may be set to 1 (interrupt requested) when the interrupt source changes. When using an interrupt, set the IR bit to 0 (no interrupt requested) after changing the interrupt source. -

Page 111: Changing Interrupt Control Register Contents

R8C/18 Group, R8C/19 Group 12. Interrupts 12.5.6 Changing Interrupt Control Register Contents (a) The contents of an interrupt control register can only be changed while no interrupt requests corresponding to that register are generated. If interrupt requests may be generated, disable interrupts before changing the interrupt control register contents. -

Page 112: 13. Watchdog Timer

R8C/18 Group, R8C/19 Group 13. Watchdog Timer 13. Watchdog Timer The watchdog timer is a function that detects when a program is out of control. Use of the watchdog timer is recommended to improve the reliability of the system. The watchdog timer contains a 15-bit counter and allows selection of count source protection mode enable or disable. - Page 113 R8C/18 Group, R8C/19 Group 13. Watchdog Timer Option Function Select Register b7 b6 b5 b4 b3 b2 b1 b0 1 1 1 Symbol Address Before Shipment 0FFFFh Bit Symbol Bit Name Function Watchdog timer start 0 : Starts w atchdog timer automatically after reset. WDTON select bit 1 : Watchdog timer is inactive after reset.

- Page 114 R8C/18 Group, R8C/19 Group 13. Watchdog Timer Watchdog Timer Reset Register Symbol Address After Reset 000Dh Undefined WDTR Function When 00h is w ritten before w riting FFh, the w atchdog timer is reset. The default value of the w atchdog timer is 7FFFh w hen count source protection mode is disabled and 0FFFh w hen count source protection mode is enabled.

-

Page 115: Count Source Protection Mode Disabled

R8C/18 Group, R8C/19 Group 13. Watchdog Timer 13.1 Count Source Protection Mode Disabled The count source of the watchdog timer is the CPU clock when count source protection mode is disabled. Table 13.2 lists the Watchdog Timer Specifications (with Count Source Protection Mode Disabled). -

Page 116: Count Source Protection Mode Enabled

R8C/18 Group, R8C/19 Group 13. Watchdog Timer 13.2 Count Source Protection Mode Enabled The count source of the watchdog timer is the low-speed on-chip oscillator clock when count source protection mode is enabled. If the CPU clock stops when a program is out of control, the clock can still be supplied to the watchdog timer. -

Page 117: 14. Timers

R8C/18 Group, R8C/19 Group 14. Timers 14. Timers The MCU has two 8-bit timers with 8-bit prescalers, and a 16-bit timer. The two 8-bit timers with 8-bit prescalers are timer X and timer Z. These timers contain a reload register to store the default value of the counter. -

Page 118: Timer X

R8C/18 Group, R8C/19 Group 14. Timers 14.1 Timer X Timer X is an 8-bit timer with an 8-bit prescaler. The prescaler and timer each consist of a reload register and counter. The reload register and counter are allocated at the same address, and can be accessed when accessing registers PREX and TX (refer to Tables 14.2 to 14.6 the Specifications of Each Modes). - Page 119 R8C/18 Group, R8C/19 Group 14. Timers Timer X Mode Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 008Bh TXMR Bit Symbol Bit Name Function Operating mode select bits 0, 1 b1 b0 0 0 : Timer mode or pulse period measurement TXMOD0 mode 0 1 : Pulse output mode...

- Page 120 R8C/18 Group, R8C/19 Group 14. Timers Prescaler X Register Symbol Address After Reset 008Ch PREX Mode Function Setting Range Timer mode Counts internal count source. 00h to FFh Pulse output mode Counts internal count source. 00h to FFh Counts input pulses from external clock. Event counter mode 00h to FFh Pulse w idth...

-

Page 121: Timer Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.1.1 Timer Mode Timer mode, the internally generated count source is counted (refer to Table 14.2 Timer Mode Specifications). Figure 14.4 shows the TXMR Register in Timer Mode. Table 14.2 Timer Mode Specifications Item Specification Count sources f1, f2, f8, fRING... -

Page 122: Pulse Output Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.1.2 Pulse Output Mode In pulse output mode, the internally generated count source is counted, and a pulse with inverted polarity is output from the CNTR0 pin each time the timer underflows (refer to Table 14.3 Pulse Output Mode Specifications). - Page 123 R8C/18 Group, R8C/19 Group 14. Timers Timer X Mode Register b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 Symbol Address After Reset 008Bh TXMR Bit Symbol Bit Name Function Operating mode select bits 0, 1 b1 b0 TXMOD0 0 1 : Pulse output mode TXMOD1...

-

Page 124: Event Counter Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.1.3 Event Counter Mode In event counter mode, external signal inputs to the INT1/CNTR0 pin are counted (refer to Table 14.4 Event Counter Mode Specifications). Figure 14.6 shows the TXMR Register in Event Counter Mode. -

Page 125: Pulse Width Measurement Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.1.4 Pulse Width Measurement Mode In pulse width measurement mode, the pulse width of an external signal input to the INT1/CNTR0 pin is measured (refer to Table 14.5 Pulse Width Measurement Mode Specifications). Figure 14.7 shows the TXMR Register in Pulse Width Measurement Mode. - Page 126 R8C/18 Group, R8C/19 Group 14. Timers Timer X Mode Register b7 b6 b5 b4 b3 b2 b1 b0 0 0 0 0 Symbol Address After Reset 008Bh TXMR Bit Symbol Bit Name Function TXMOD0 Operating mode select bits 0, 1 b1 b0 1 1 : Pulse w idth measurement mode TXMOD1...

- Page 127 R8C/18 Group, R8C/19 Group 14. Timers n = high level: the contents of TX register, low level: the contents of PREX register FFFFh Count start Underflow Count stop Count stop Count start 0000h Period Set to 1 by program TXS bit in TXMR register Measured pulse (CNTR0i pin input)

-

Page 128: Pulse Period Measurement Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.1.5 Pulse Period Measurement Mode In pulse period measurement mode, the pulse period of an external signal input to the INT1/CNTR0 pin is measured (refer to Table 14.6 Pulse Period Measurement Mode Specifications). Figure 14.9 shows the TXMR Register in Pulse Period Measurement Mode. - Page 129 R8C/18 Group, R8C/19 Group 14. Timers Timer X Mode Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 008Bh TXMR Bit Symbol Bit Name Function Operating mode select bits 0, 1 b1 b0 TXMOD0 0 0 : Timer mode or pulse period measurement mode TXMOD1 _____...

- Page 130 R8C/18 Group, R8C/19 Group 14. Timers Underflow signal of prescaler X Set to 1 by program TXS bit in TXMR register Starts counting CNTR0i pin input Timer X Timer X Timer X reloads reloads reloads Contents of timer X 0Fh 0Eh 0Dh 0Ch 0Bh 0Ah 09h 08h 0Fh 0Eh 0Dh 01h 00h 0Fh 0Eh Retained Retained...

-

Page 131: Notes On Timer X

R8C/18 Group, R8C/19 Group 14. Timers 14.1.6 Notes on Timer X • Timer X stops counting after a reset. Set the values in the timer and prescaler before the count starts. • Even if the prescaler and timer are read out in 16-bit units, these registers are read 1 byte at a time by the MCU. -

Page 132: Timer Z

R8C/18 Group, R8C/19 Group 14. Timers 14.2 Timer Z Timer Z is an 8-bit timer with an 8-bit prescaler. The prescaler and timer each consist of a reload register and counter. The reload register and counter are allocated at the same address. Refer to the Tables 14.7 to 14.10 for the Specifications of Each Mode. - Page 133 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Mode Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 0080h TZMR Bit Symbol Bit Name Function — Reserved bits Set to 0. (b3-b0) Timer Z operating mode b5 b4 bits 0 0 : Timer mode...

- Page 134 R8C/18 Group, R8C/19 Group 14. Timers Prescaler Z Register Symbol Address After Reset 0085h PREZ Mode Function Setting Range Counts internal count source or timer X 00h to FFh Timer mode underflow s. Programmable w aveform Counts internal count source or timer X 00h to FFh generation mode underflow s.

- Page 135 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Output Control Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 008Ah TZOC Bit Symbol Bit Name Function Timer Z one-shot start bit 0 : One-shot stops. TZOS 1 : One-shot starts.

- Page 136 R8C/18 Group, R8C/19 Group 14. Timers Timer Count Source Setting Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 008Eh TCSS Bit Symbol Bit Name Function Timer X count source select bits b1 b0 TXCK0 0 0 : f1 0 1 : f8 1 0 : fRING TXCK1...

-

Page 137: Timer Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.2.1 Timer Mode In timer mode, a count source which is internally generated or timer X underflow is counted (refer to Table 14.7 Timer Mode Specifications). The TZSC register is not used in timer mode. Figure 14.16 shows Registers TZMR and PUM in Timer Mode. - Page 138 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Mode Register b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset 0080h TZMR Bit Symbol Bit Name Function — Reserved bits Set to 0. (b3-b0) TZMOD0 Timer Z operating mode b5 b4 0 0 : Timer mode bits...

-

Page 139: Programmable Waveform Generation Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.2.2 Programmable Waveform Generation Mode In programmable waveform generation mode, the signal output from the TZOUT pin is inverted each time the counter underflows, while the values in registers TZPR and TZSC are counted alternately (refer to Table 14.8 Programmable Waveform Generation Mode Specifications). - Page 140 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Mode Register b7 b6 b5 b4 b3 b2 b1 b0 1 0 1 0 0 0 0 Symbol Address After Reset 0080h TZMR Bit Symbol Bit Name Function — Reserved bits Set to 0. (b3-b0) b5 b4 TZMOD0...

- Page 141 R8C/18 Group, R8C/19 Group 14. Timers Set to 1 by program TZS bit in TZMR register Count source Prescaler Z underflow signal Timer Z Timer Z secondary primary reloads reloads Contents of timer Z Set to 0 when interrupt request is acknowledged, or set by program IR bit in...

-

Page 142: Programmable One-Shot Generation Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.2.3 Programmable One-shot Generation Mode In programmable one-shot generation mode, one-shot pulse is output from the TZOUT pin by a program or an external trigger input (input to the INT0 pin) (refer to Table 14.9 Programmable One- Shot Generation Mode Specifications). - Page 143 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Mode Register b7 b6 b5 b4 b3 b2 b1 1 1 0 Symbol Address After Reset 0080h TZMR Bit Symbol Bit Name Function — Reserved bits Set to 0. (b3-b0) TZMOD0 Timer Z operating mode b5 b4 bits 1 0 : Programmable one-shot generation mode...

- Page 144 R8C/18 Group, R8C/19 Group 14. Timers Set to 1 by program TZS bit in TZMR register Set to 0 when Set to 1 by INT0 pin Set to 1 by program counting ends input trigger TZOS bit in TZOC register Count source Prescaler Z underflow signal...

-

Page 145: Programmable Wait One-Shot Generation Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.2.4 Programmable Wait One-Shot Generation Mode In programmable wait one-shot generation mode, one-shot pulse is output from the TZOUT pin by a program or an external trigger input (input to the INT0 pin) (refer to Table 14.10 Programmable Wait One-Shot Generation Mode Specifications). - Page 146 R8C/18 Group, R8C/19 Group 14. Timers Table 14.10 Programmable Wait One-Shot Generation Mode Specifications Item Specification Count sources f1, f2, f8, Timer X underflow Count operations • Decrement the value set in Timer Z primary • When the count of TZPR register underflows, the timer reloads the contents of the TZSC register before the count is continued.

- Page 147 R8C/18 Group, R8C/19 Group 14. Timers Timer Z Mode Register b7 b6 b5 b4 b3 b2 Symbol Address After Reset 0080h TZMR Bit Symbol Bit Name Function — Reserved bits Set to 0. (b3-b0) Timer Z operating mode b5 b4 TZMOD0 bits 1 1 : Programmable w ait one-shot generation mode...

- Page 148 R8C/18 Group, R8C/19 Group 14. Timers Set to 1 by program TZS bit in TZMR register Set to 0 when Set to 1 by program, or set to 1 by INT0 pin counting ends input trigger TZOS bit in TZOC register Count source Prescaler Z underflow...

-

Page 149: Notes On Timer Z

R8C/18 Group, R8C/19 Group 14. Timers 14.2.5 Notes on Timer Z • Timer Z stops counting after a reset. Set the values in the timer and prescaler before the count starts. • Even if the prescaler and timer are read out in 16-bit units, these registers are read 1 byte at a time by the MCU. -

Page 150: Timer C

R8C/18 Group, R8C/19 Group 14. Timers 14.3 Timer C Timer C is a 16-bit timer. Figure 14.23 shows a Block Diagram of Timer C. Figure 14.24 shows a Block Diagram of CMP Waveform Generation Unit. Figure 14.25 shows a Block Diagram of CMP Waveform Output Unit. - Page 151 R8C/18 Group, R8C/19 Group 14. Timers TCC14 TCC15 Compare 0 interrupt signal Compare 1 interrupt signal TCC16 TCC17 TCC17 to TCC16 “H” CMP output = 11b “L” Latch (internal signal) = 10b Reverse = 01b Reset TCC15 to TCC14 Reverse = 01b “L”...

- Page 152 R8C/18 Group, R8C/19 Group 14. Timers Timer C Register (b15) (b8) Symbol Address After Reset 0091h-0090h 0000h Function Counts internal count source. 0000h can be read w hen the TCC00 bit is set to 0 (count stops). Count value can be read w hen the TCC00 bit is set to 1 (count starts). Capture and Compare 0 Register (b15) (b8)

- Page 153 R8C/18 Group, R8C/19 Group 14. Timers Timer C Control Register 0 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 009Ah TCC0 Bit Symbol Bit Name Function Timer C count start bit 0 : Stops counting. TCC00 1 : Starts counting.

- Page 154 R8C/18 Group, R8C/19 Group 14. Timers Timer C Control Register 1 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 009Bh TCC1 Bit Symbol Bit Name Function _____ INT3 filter select bits b1 b0 TCC10 0 0 : No filter 0 1 : Filter w ith f1 sampling 1 0 : Filter w ith f8 sampling TCC11...

- Page 155 R8C/18 Group, R8C/19 Group 14. Timers Timer C Output Control Register b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 00FFh TCOUT Bit Symbol Bit Name Function CMP output enable bit 0 0 : Disables CMP output from CMP0_0. TCOUT0 1 : Enables CMP output from CMP0_0.

-

Page 156: Input Capture Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.3.1 Input Capture Mode In input capture mode, the edge of the TCIN pin input signal or the fRING128 clock is used as a trigger to latch the timer value and generate an interrupt request. The TCIN input contains a digital filter, and this prevents errors caused by noise or the like from occurring. - Page 157 R8C/18 Group, R8C/19 Group 14. Timers FFFFh Overflow Count starts ← Measurement value 2 ← ← Measurement Measurement value1 value 3 0000h Period Set to 0 by Set to 1 by program program TCC00 bit in TCC0 register The delay caused by digital filter and one count source cycle delay (max.) Measured pulse (TCIN pin input)

-

Page 158: Output Compare Mode

R8C/18 Group, R8C/19 Group 14. Timers 14.3.2 Output Compare Mode In output compare mode, an interrupt request is generated when the value of the TC register matches the value of the TM0 or TM1 register. Table 14.12 shows the Output Compare Mode Specifications. Figure 14.31 shows an Operating Example in Output Compare Mode. - Page 159 R8C/18 Group, R8C/19 Group 14. Timers Match Value set in TM1 register Count starts Match Match Value set in TM0 register 0000h Time Set to 1 by program TCC00 bit in TCC0 register Set to 0 when interrupt request is acknowledged, or set by program IR bit in CMP0IC register Set to 0 when interrupt request is...

-

Page 160: Notes On Timer C

R8C/18 Group, R8C/19 Group 14. Timers 14.3.3 Notes on Timer C Access registers TC, TM0, and TM1 in 16-bit units. The TC register can be read in 16-bit units. This prevents the timer value from being updated between when the low-order bytes and high-order bytes are being read. Example of reading timer C: MOV.W 0090H,R0... -

Page 161: 15. Serial Interface

R8C/18 Group, R8C/19 Group 15. Serial Interface 15. Serial Interface The serial interface consists of two channels (UART0 and UART1). Each UARTi (i = 0 or 1) has an exclusive timer to generate the transfer clock and operates independently. Figure 15.1 shows a UARTi (i = 0 or 1) Block Diagram. Figure 15.2 shows a UARTi Transmit/Receive Unit. UART0 has two modes: clock synchronous serial I/O mode and clock asynchronous serial I/O mode (UART mode). - Page 162 R8C/18 Group, R8C/19 Group 15. Serial Interface Clock synchronous type PRYE = 0 Clock UART (7 bits) synchronous disabled UART (7 bits) UARTi receive register UART (8 bits) type RXDi Clock UART UART (9 bits) enabled synchronous type PRYE = 1 UART (8 bits) UART (9 bits) UiRB register...

- Page 163 R8C/18 Group, R8C/19 Group 15. Serial Interface (1, 2) UARTi Transmit Buffer Register (i = 0 or 1) (b15) (b8) Symbol Address After Reset 00A3h-00A2h Undefined U0TB 00ABh-00AAh Undefined U1TB Bit Symbol Function — Transmit data (b8-b0) — Nothing is assigned. If necessary, set to 0. —...

- Page 164 R8C/18 Group, R8C/19 Group 15. Serial Interface UARTi Transmit/Receive Mode Register (i = 0 or 1) b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset U0MR 00A0h U1MR 00A8h Bit Symbol Bit Name Function Serial interface mode select b2 b1 b0 SMD0 bits...

- Page 165 R8C/18 Group, R8C/19 Group 15. Serial Interface UARTi Transmit/Receive Control Register 0 (i = 0 or 1) b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 00A4h U0C0 00ACh U1C0 Bit Symbol Bit Name Function BRG count source select b1 b0 bits 0 0 : Selects f1.

- Page 166 R8C/18 Group, R8C/19 Group 15. Serial Interface UARTi Transmit/Receive Control Register 1 (i = 0 or 1) b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset U0C1 00A5h U1C1 00ADh Bit Symbol Bit Name Function Transmit enable bit 0 : Disables transmission.

-

Page 167: Clock Synchronous Serial I/O Mode

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.1 Clock Synchronous Serial I/O Mode In clock synchronous serial I/O mode, data is transmitted and received using a transfer clock. Table 15.1 lists the Clock Synchronous Serial I/O Mode Specifications. Table 15.2 lists the Registers Used and Settings in Clock Synchronous Serial I/O Mode Table 15.1 Clock Synchronous Serial I/O Mode Specifications... - Page 168 R8C/18 Group, R8C/19 Group 15. Serial Interface Table 15.2 Registers Used and Settings in Clock Synchronous Serial I/O Mode Register Function U0TB 0 to 7 Set data transmission. U0RB 0 to 7 Data reception can be read. Overrun error flag U0BRG 0 to 7 Set bit rate.

- Page 169 R8C/18 Group, R8C/19 Group 15. Serial Interface • Example of transmit timing (when internal clock is selected) Transfer clock TE bit in U0C1 register Set data in U0TB register TI bit in U0C1 register Transfer from U0TB register to UART0 transmit register TCLK Stop pulsing because the TE bit is set to 0 CLK0...

-

Page 170: Polarity Select Function

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.1.1 Polarity Select Function Figure 15.8 shows the Transfer Clock Polarity. Use the CKPOL bit in the U0C0 register to select the transfer clock polarity. • When the CKPOL bit in the U0C0 register = 0 (output transmit data at the falling edge and input the receive data at the rising edge of the transfer clock) CLK0 TXD0... -

Page 171: Continuous Receive Mode

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.1.3 Continuous Receive Mode Continuous receive mode is selected by setting the U0RRM bit in the UCON register to 1 (enables continuous receive mode). In this mode, reading the U0RB register sets the TI bit in the U0C1 register to 0 (data in the U0TB register). -

Page 172: Clock Asynchronous Serial I/O (Uart) Mode

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.2 Clock Asynchronous Serial I/O (UART) Mode The UART mode allows data transmission and reception after setting the desired bit rate and transfer data format. Table 15.4 lists the UART Mode Specifications. Table 15.5 lists the Registers Used and Settings for UART Mode. - Page 173 R8C/18 Group, R8C/19 Group 15. Serial Interface Table 15.5 Registers Used and Settings for UART Mode Register Function UiTB 0 to 8 Set transmit data UiRB 0 to 8 Receive data can be read OER,FER,PER,SUM Error flag UiBRG 0 to 7 Set a bit rate.

- Page 174 R8C/18 Group, R8C/19 Group 15. Serial Interface • Transmit timing when transfer data is 8 bits long (parity enabled, 1 stop bit) Transfer clock TE bit in UiC1 register Write data to UiTB register TI bit in UiC1 register Stop pulsing Transfer from UiTB register to UARTi transmit register because the TE bit is set to 0 Start bit...

-

Page 175: Cntr0 Pin Select Function

R8C/18 Group, R8C/19 Group 15. Serial Interface • Example of receive timing when transfer data is 8 bits long (parity disabled, one stop bit) UiBRG output UiC1 register RE bit Stop bit Start bit RXDi Determined to be “L” Receive data taken in Transfer clock Reception triggered when transfer clock Transferred from UARTi receive... -

Page 176: Bit Rate

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.2.2 Bit Rate In UART mode, the bit rate is the frequency divided by the UiBRG (i = 0 or 1) register. UART Mode • Internal clock selected UiBRG register setting value = Bit Rate ×... -

Page 177: Notes On Serial Interface

R8C/18 Group, R8C/19 Group 15. Serial Interface 15.3 Notes on Serial Interface • When reading data from the U0RB register either in the clock asynchronous serial I/O mode or in the clock synchronous serial I/O mode. Ensure the data is read in 16-bit units. When the high-order byte of the U0RB register is read, bits PER and FER in the U0RB register and the RI bit in the U0C1 register are set to 0. -

Page 178: 16. Comparator

R8C/18 Group, R8C/19 Group 16. Comparator 16. Comparator The comparator compares the electric potential input from the VREF pin with analog input. The analog input shares pins P1_0 to P1_3. Therefore, when using these pins, ensure the corresponding port direction bits are set to 0 (input mode). The result of comparator conversion is stored in the AD register. - Page 179 R8C/18 Group, R8C/19 Group 16. Comparator Comparator conversion rate selection CKS0 = 1 fRING-fast CKS1 = 1 CKS0 = 0 φAD CKS0 = 1 CKS1 = 0 CKS0 = 0 VREF ADCON0 Vref AD register Decoder Comparator Data bus ADCAP = 0 ADGSEL0 = 0 Software trigger Trigger...

- Page 180 R8C/18 Group, R8C/19 Group 16. Comparator A/D Control Register 0 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset ADCON0 00D6h 00000XXXb Bit Symbol Bit Name Function Analog input pin select b2 b1 b0 bits 1 0 0 : AN8 1 0 1 : AN9 1 1 0 : AN10 1 1 1 : AN11...

- Page 181 R8C/18 Group, R8C/19 Group 16. Comparator A/D Control Register 2 b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset ADCON2 00D4h Bit Symbol Bit Name Function — Reserved bit Set to 0. (b0) Comparator function select bit 0 : Not used CMPSEL 1 : Used —...

-

Page 182: One-Shot Mode

R8C/18 Group, R8C/19 Group 16. Comparator 16.1 One-Shot Mode In one-shot mode, the input voltage on one selected pin is comparator converted once. Table 16.2 lists the One-Shot Mode Specifications. Figure 16.4 shows Registers ADCON0 and ADCON1 in One-Shot Mode. Table 16.2 One-Shot Mode Specifications Item... - Page 183 R8C/18 Group, R8C/19 Group 16. Comparator A/D Control Register 0 b7 b6 b5 b4 b3 b2 b1 Symbol Address After Reset ADCON0 00D6h 00000XXXb Bit Symbol Bit Name Function Analog input pin select b2 b1 b0 bits 1 0 0 : AN8 1 0 1 : AN9 1 1 0 : AN10 1 1 1 : AN11...

-

Page 184: Repeat Mode

R8C/18 Group, R8C/19 Group 16. Comparator 16.2 Repeat Mode In repeat mode, the input voltage on one selected pin is comparator converted repeatedly. Table 16.3 lists the Repeat Mode Specifications. Figure 16.5 shows Registers ADCON0 and ADCON1 in Repeat Mode. Table 16.3 Repeat Mode Specifications Item... - Page 185 R8C/18 Group, R8C/19 Group 16. Comparator A/D Control Register 0 b7 b6 b5 b4 b3 b2 Symbol Address After Reset ADCON0 00D6h 00000XXXb Bit Symbol Bit Name Function Analog input pin select b2 b1 b0 bits 1 0 0 : AN8 1 0 1 : AN9 1 1 0 : AN10 1 1 1 : AN11...

-

Page 186: Notes On Comparator

R8C/18 Group, R8C/19 Group 16. Comparator 16.3 Notes on Comparator • Write to each bit (other than bit 6) in the ADCON0 register, each bit in the ADCON1 register, or the CMPSEL bit in the ADCON2 register when the comparator conversion stops (before a trigger occurs). -

Page 187: 17. Flash Memory Version

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17. Flash Memory Version 17.1 Overview In the flash memory version, rewrite operations to the flash memory can be performed in three modes; CPU rewrite, standard serial I/O, and parallel I/O. Table 17.1 lists the Flash Memory Version Performance (refer to Table 1.1 Functions and Specifications for R8C/18 Group and Table 1.2 Functions and Specifications for R8C/19 Group for items not listed in Table 17.1). - Page 188 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Table 17.2 Flash Memory Rewrite Modes Flash Memory CPU Rewrite Mode Standard Serial I/O Mode Parallel I/O Mode Rewrite Mode Function User ROM area is rewritten by User ROM area is rewritten User ROM area is executing software commands by a dedicated serial...

-

Page 189: Memory Map

0 (rewrite enabled), block 0 is rewritable. When the FMR16 bit is set to 0 (rewrite enabled), block 1 is rewritable (only for CPU rewrite mode). This area is for storing the boot program provided by Renesas Technology. Figure 17.1 Flash Memory Block Diagram for R8C/18 Group Rev.1.30... - Page 190 FMR1 register to 0 (rewrite enabled), block 0 is rewritable. When the FMR16 bit is set to 0 (rewrite enabled), block 1 is rewritable (only for CPU rewrite mode). 2. This area is for storing the boot program provided by Renesas Technology. Figure 17.2 Flash Memory Block Diagram for R8C/19 Group Rev.1.30...

-

Page 191: Functions To Prevent Rewriting Of Flash Memory

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.3 Functions to Prevent Rewriting of Flash Memory Standard serial I/O mode has an ID code check function, and parallel I/O mode has a ROM code protect function to prevent the flash memory from being read or rewritten easily. 17.3.1 ID Code Check Function This function is used in standard serial I/O mode. -

Page 192: Rom Code Protect Function

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.3.2 ROM Code Protect Function The ROM code protect function disables reading or changing the contents of the on-chip flash memory by the OFS register in parallel I/O mode. Figure 17.4 shows the OFS Register. The ROM code protect function is enabled by writing 0 to the ROMCP1 bit and 1 to the ROMCR bit. -

Page 193: Cpu Rewrite Mode

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4 CPU Rewrite Mode In CPU rewrite mode, the user ROM area can be rewritten by executing software commands from the CPU. Therefore, the user ROM area can be rewritten directly while the MCU is mounted on a board without using a ROM programmer. -

Page 194: Ew0 Mode

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.1 EW0 Mode The MCU enters CPU rewrite mode and software commands can be acknowledged by setting the FMR01 bit in the FMR0 register to 1 (CPU rewrite mode enabled). In this case, since the FMR11 bit in the FMR1 register is set to 0, EW0 mode is selected. - Page 195 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Figure 17.5 shows the FMR0 Register. Figure 17.7 shows the FMR4 Register. 17.4.2.1 FMR00 Bit This bit indicates the operating status of the flash memory. The bits value is 0 during programming, erasure, or erase-suspend mode;...

- Page 196 R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.2.10 FMR40 Bit The suspend function is enabled by setting the FMR40 bit to 1 (enable). 17.4.2.11 FMR41 Bit In EW0 mode, the MCU enters erase-suspend mode when the FMR41 bit is set to 1 by a program. The FMR41 bit is automatically set to 1 (request erase-suspend) when an interrupt request of an enabled interrupt is generated in EW1 mode, and then the MCU enters erase-suspend mode.

- Page 197 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Flash Memory Control Register 0 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 01B7h 00000001b FMR0 Bit Symbol Bit Name Function 0 : Busy (w riting or erasing in progress) RY/BY status flag FMR00...

- Page 198 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Flash Memory Control Register 1 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 01B5h 1000000Xb FMR1 Bit Symbol Bit Name Function — Reserved bit When read, the content is undefined. (b0) (1, 2) EW1 mode select bit...

- Page 199 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Flash Memory Control Register 4 b7 b6 b5 b4 b3 b2 b1 b0 Symbol Address After Reset 01B3h 01000000b FMR4 Bit Symbol Bit Name Function Erase-suspend function 0 : Disable FMR40 enable bit 1 : Enable Erase-suspend request bit 0 : Erase restart...

- Page 200 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Figure 17.8 shows the Timing of Suspend Operation. Erasure Erasure Programming Programming Programming Programming Erasure Erasure starts suspends starts suspends restarts ends restarts ends During During During During programming programming erasure erasure FMR00 bit in FMR0 register FMR46 bit in...

- Page 201 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Figure 17.9 shows How to Set and Exit EW0 Mode. Figure 17.10 shows How to Set and Exit EW1 Mode. EW0 Mode Operating Procedure Rewrite control program Set the FMR01 bit by writing 0 and then 1 (CPU rewrite mode enabled) Set registers CM0 and CM1 Execute software commands...

- Page 202 R8C/18 Group, R8C/19 Group 17. Flash Memory Version On-chip oscillator mode (main clock stops) program Transfer an on-chip oscillator mode (main clock stops) Write 0 to the FMR01 bit before writing 1 program to an area other then the flash memory. (CPU rewrite mode enabled) Write 1 to the FMSTP bit (flash memory stops.

-

Page 203: Software Commands

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.3 Software Commands The software commands are described below. Read or write commands and data in 8-bit units. Table 17.4 Software Commands First Bus Cycle Second Bus Cycle Command Data Data Mode Address Mode Address... - Page 204 R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.3.4 Program Command The program command writes data to the flash memory in 1-byte units. By writing 40h in the first bus cycle and data to the write address in the second bus cycle, an auto-program operation (data program and verify) will start.

- Page 205 R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.3.5 Block Erase When 20h is written in the first bus cycle and D0h is written to a given address of a block in the second bus cycle, an auto-erase operation (erase and verify) of the specified block starts. The FMR00 bit in the FMR0 register can be used to determine whether auto-erasure has completed.

- Page 206 R8C/18 Group, R8C/19 Group 17. Flash Memory Version EW0 Mode (1, 2) Start Maskable interrupt FMR40 = 1 FMR41 = 1 Write the command code 20h FMR46 = 1 ? Write D0h to any block Access flash memory address FMR41 = 0 FMR00 = 1? REIT Full status check...

-

Page 207: Status Register

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.4 Status Register The status register indicates the operating status of the flash memory and whether an erase or program operation has completed normally or in error. Status of the status register can be read by bits FMR00, FMR06, and FMR07 in the FMR0 register. -

Page 208: Full Status Check

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.4.5 Full Status Check When an error occurs, bits FMR06 to FMR07 in the FMR0 register are set to 1, indicating the occurrence of an error. Therefore, checking these status bits (full status check) can be used to determine the execution result. - Page 209 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Command sequence error Full status check Execute the clear status register command (set these status flags to 0) FMR06 = 1 Command sequence error FMR07 = 1? Check if command is properly input Re-execute the command Erase error FMR07 = 0?

-

Page 210: Standard Serial I/O Mode

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.5 Standard Serial I/O Mode In standard serial I/O mode, the user ROM area can be rewritten while the MCU is mounted on-board by using a serial programmer which is suitable for the MCU. Standard serial I/O mode is used to connect with a serial programmer using a special clock asynchronous serial I/O. - Page 211 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Table 17.8 Pin Functions (Flash Memory Standard Serial I/O Mode 3) Name Description VCC,VSS Power input Apply the voltage guaranteed for programming and erasure to the VCC pin and 0 V to the VSS pin. Reset input Reset input pin.

- Page 212 R8C/18 Group, R8C/19 Group 17. Flash Memory Version RESET Connect oscillator circuit MODE Package: PLSP0020JB-A NOTE: 1. It is not necessary to connect an oscillating circuit when operating with the on-chip oscillator clock. Mode Setting Signal Value Voltage from programmer MODE VSS →...

- Page 213 R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.5.1.1 Example of Circuit Application in the Standard Serial I/O Mode Figure 17.17 shows an example of Pin Processing in Standard Serial I/O Mode 2, and Figure 17.18 shows Pin Processing in Standard Serial I/O Mode 3. Since the controlled pins vary depending on the programmer, refer to the manual of your serial programmer for details.

-

Page 214: Parallel I/O Mode

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.6 Parallel I/O Mode Parallel I/O mode is used to input and output software commands, addresses, and data necessary to control (read, program, and erase) the on-chip flash memory. Use a parallel programmer which supports this MCU. -

Page 215: Notes On Flash Memory Version

R8C/18 Group, R8C/19 Group 17. Flash Memory Version 17.7 Notes on Flash Memory Version 17.7.1 CPU Rewrite Mode 17.7.1.1 Operating Speed Before entering CPU rewrite mode (EW0 mode), select 5 MHz or below for the CPU clock using the CM06 bit in the CM0 register and bits CM16 to CM17 in the CM1 register. This does note apply to EW1 mode. - Page 216 R8C/18 Group, R8C/19 Group 17. Flash Memory Version Table 17.10 EW1 Mode Interrupts When Watchdog Timer, Oscillation When Maskable Interrupt Request is Mode Status Stop Detection and Voltage Monitor 2 Acknowledged Interrupt Request are Acknowledged EW1 During Auto-erasure is suspended after Once an interrupt request is auto-erasure td(SR-ES) and interrupt handing is...

-

Page 217: 18. Electrical Characteristics

R8C/18 Group, R8C/19 Group 18. Electrical Characteristics 18. Electrical Characteristics Table 18.1 Absolute Maximum Ratings Symbol Parameter Condition Rated Value Unit Supply voltage = AV -0.3 to 6.5 Analog supply voltage = AV -0.3 to 6.5 Input voltage -0.3 to V +0.3 Output voltage -0.3 to V... - Page 218 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.3 Comparator Characteristics Standard Symbol Parameter Conditions Unit Min. Typ. Max. − − − Resolution − − − φ Absolute accuracy ±20 = 10 MHz − − µ s φ Conversion time = 10 MHz conv −...

- Page 219 6. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur. 7. Customers desiring programming/erasure failure rate information should contact their Renesas technical support representative.

- Page 220 6. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur. 7. Customers desiring programming/erasure failure rate information should contact their Renesas technical support representative.

- Page 221 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.6 Voltage Detection 1 Circuit Electrical Characteristics Standard Symbol Parameter Condition Unit Min. Typ. Max. 2.70 2.85 3.00 Voltage detection level det1 − − − Voltage detection circuit self power consumption VCA26 = 1, V = 5.0 V −...

- Page 222 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.8 Reset Circuit Electrical Characteristics (When Using Voltage Monitor 1 Reset) Symbol Parameter Condition Standard Unit Min. Typ. Max. -20 ° C ≤ Topr ≤ 85 ° C − − Power-on reset valid voltage por2 det1 -20 °...

- Page 223 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.10 High-speed On-Chip Oscillator Circuit Electrical Characteristics Standard Symbol Parameter Condition Unit Min. Typ. Max. − = 25 ° C − − High-speed on-chip oscillator frequency when the = 5.0 V, T reset is deasserted −...

- Page 224 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.12 Electrical Characteristics (1) [V = 5 V] Standard Symbol Parameter Condition Unit Min. Typ. Max. − 2.0 − Output “H” voltage Except X = -5 mA = -200 µ A − 0.3 −...

- Page 225 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Electrical Characteristics (2) [Vcc = 5 V] (Topr = -40 to 85 °C, unless otherwise specified.) Table 18.13 Standard Symbol Parameter Condition Unit Min. Typ. Max. − Power supply current High-speed XIN = 20 MHz (square wave) = 3.3 to 5.5 V) mode High-speed on-chip oscillator off...

- Page 226 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Timing Requirements = 0 V at Ta = 25 °C) [V (Unless Otherwise Specified: V = 5 V, V = 5 V] Table 18.14 XIN Input Standard Symbol Parameter Unit Min. Max. − XIN input cycle time c(XIN) −...

- Page 227 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.17 Serial Interface Standard Symbol Parameter Unit Min. Max. − CLKi input cycle time c(CK) − CLKi input “H” width W(CKH) − CLKi input “L” width W(CKL) − TXDi output delay time d(C-Q) −...

- Page 228 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Table 18.19 Electrical Characteristics (3) [V = 3V] Standard Symbol Parameter Condition Unit Min. Typ. Max. − 0.5 − Output “H” voltage Except X = -1 mA − 0.5 − Drive capacity = -0.1 mA HIGH = -50 µ...

- Page 229 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Electrical Characteristics (4) [Vcc = 3V] (Topr = -40 to 85 °C, unless otherwise specified.) Table 18.20 Standard Symbol Parameter Condition Unit Min. Typ. Max. − Power supply current High-speed XIN = 20 MHz (square wave) = 2.7 to 3.3 V) mode High-speed on-chip oscillator off...

- Page 230 R8C/18 Group, R8C/19 Group 18. Electrical Characteristics Timing requirements = 0 V at Ta = 25 °C) [V (Unless Otherwise Specified: V = 3 V, V = 3 V] Table 18.21 XIN Input Standard Symbol Parameter Unit Min. Max. − XIN input cycle time c(XIN) −...