Table of Contents

Advertisement

Quick Links

Analog Peripherals

-

10 or 12-bit SAR ADC

± 1 LSB INL

•

Programmable throughput up to 100 ksps

•

Up to 8 external inputs; programmable as single-

•

ended or differential

Programmable amplifier gain: 16, 8, 4, 2, 1, 0.5

•

Data-dependent windowed interrupt generator

•

Built-in temperature sensor

•

-

8-bit SAR ADC ('F12x Only)

Programmable throughput up to 500 ksps

•

8 external inputs (single-ended or differential)

•

Programmable amplifier gain: 4, 2, 1, 0.5

•

-

Two 12-bit DACs ('F12x Only)

Can synchronize outputs to timers for jitter-free wave-

•

form generation

-

Two Analog Comparators

-

Voltage Reference

V

-

Monitor/Brown-Out Detector

DD

On-Chip JTAG Debug & Boundary Scan

-

On-chip debug circuitry facilitates full-speed, non-

intrusive in-circuit/in-system debugging

-

Provides breakpoints, single-stepping, watchpoints,

stack monitor; inspect/modify memory and registers

-

Superior performance to emulation systems using

ICE-chips, target pods, and sockets

-

IEEE1149.1 compliant boundary scan

-

Complete development kit

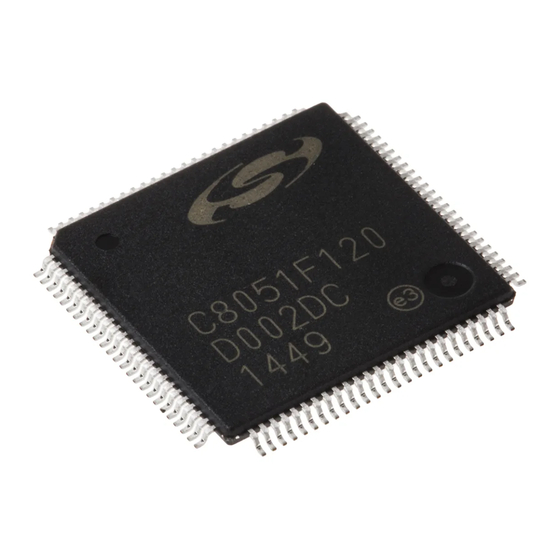

100-Pin TQFP or 64-Pin TQFP Packaging

-

Temperature Range: –40 to +85 °C

-

RoHS Available

Rev. 1.4 12/03

ANALOG PERIPHERALS

VREF

PGA

+

+

-

-

VOLTAGE

COMPARATORS

8-bit

500ksps

PGA

ADC

C8051F12x Only

HIGH-SPEED CONTROLLER CORE

8051 CPU

128/64 kB

(50 or 100MIPS)

ISP FLASH

20

INTERRUPTS

CIRCUITRY

Copyright © 2003 by Silicon Laboratories

C8051F120/1/2/3/4/5/6/7

8K ISP FLASH MCU Family

High Speed 8051 µC Core

-

Pipelined instruction architecture; executes 70% of

instruction set in 1 or 2 system clocks

-

100 MIPS or 50 MIPS throughput with on-chip PLL

-

2-cycle 16 x 16 MAC engine (C8051F120/1/2/3 and

C8051F130/1/2/3 only)

Memory

-

8448 bytes internal data RAM (8 k + 256)

-

128 or 64 kB Banked Flash; in-system programma-

ble in 1024-byte sectors

-

External 64 kB data memory interface (programma-

ble multiplexed or non-multiplexed modes)

Digital Peripherals

-

8 byte-wide port I/O (100TQFP); 5 V tolerant

-

4 Byte-wide port I/O (64TQFP); 5 V tolerant

-

Hardware SMBus™ (I2C™ Compatible), SPI™, and

two UART serial ports available concurrently

-

Programmable 16-bit counter/timer array with

6 capture/compare modules

-

5 general purpose 16-bit counter/timers

-

Dedicated watchdog timer; bi-directional reset pin

Clock Sources

-

Internal precision oscillator: 24.5 MHz

-

Flexible PLL technology

-

External Oscillator: Crystal, RC, C, or clock

Voltage Supples

-

Range: 2.7–3.6 V (50 MIPS) 3.0–3.6 V (100 MIPS)

-

Power saving sleep and shutdown modes

DIGITAL I/O

UART0

10/12-bit

UART1

100ksps

SMBus

ADC

SPI Bus

PCA

TEMP

Timer 0

SENSOR

Timer 1

Timer 2

Timer 3

12-Bit

DAC

Timer 4

12-Bit

DAC

64 pin

8448 B

16 x 16 MAC

SRAM

('F120/1/2/3, 'F13x)

DEBUG

CLOCK / PLL

CIRCUIT

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

100 pin

JTAG

Advertisement

Table of Contents

Summary of Contents for Silicon Laboratories C8051F12 Series

- Page 1 HIGH-SPEED CONTROLLER CORE 8051 CPU 128/64 kB 8448 B 16 x 16 MAC (50 or 100MIPS) ISP FLASH SRAM ('F120/1/2/3, 'F13x) DEBUG CLOCK / PLL JTAG INTERRUPTS CIRCUITRY CIRCUIT Rev. 1.4 12/03 Copyright © 2003 by Silicon Laboratories C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3...

- Page 2 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 OTES Rev. 1.4...

-

Page 3: Table Of Contents

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table of Contents 1. System Overview....................19 1.1. CIP-51™ Microcontroller Core................27 1.1.1. Fully 8051 Compatible................27 1.1.2. Improved Throughput ................27 1.1.3. Additional Features .................. 28 1.2. On-Chip Memory....................29 1.3. JTAG Debug and Boundary Scan..............30 1.4. - Page 4 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 8. DACs, 12-Bit Voltage Mode (C8051F12x Only) ..........105 8.1. DAC Output Scheduling.................. 105 8.1.1. Update Output On-Demand ..............106 8.1.2. Update Output Based on Timer Overflow ..........106 8.2. DAC Output Scaling/Justification ..............106 9. Voltage Reference ....................113 9.1.

- Page 5 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 13. Reset Sources....................... 177 13.1.Power-on Reset....................178 13.2.Power-fail Reset ..................... 178 13.3.External Reset ....................179 13.4.Missing Clock Detector Reset ................ 179 13.5.Comparator0 Reset ..................179 13.6.External CNVSTR0 Pin Reset ................ 179 13.7.Watchdog Timer Reset................... 179 13.7.1.Enable/Reset WDT ................180 13.7.2.Disable WDT ..................

- Page 6 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 17.5.3.Split Mode with Bank Select..............225 17.5.4.External Only..................225 17.6.EMIF Timing ....................225 17.6.1.Non-multiplexed Mode ................227 17.6.2.Multiplexed Mode ................... 230 18. Port Input/Output....................235 18.1.Ports 0 through 3 and the Priority Crossbar Decoder........238 18.1.1.Crossbar Pin Assignment and Allocation ..........238 18.1.2.Configuring the Output Modes of the Port Pins........

- Page 7 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 20.2.SPI0 Master Mode Operation ................. 275 20.3.SPI0 Slave Mode Operation ................277 20.4.SPI0 Interrupt Sources ................... 277 20.5.Serial Clock Timing..................278 20.6.SPI Special Function Registers ..............280 21. UART0........................287 21.1.UART0 Operational Modes ................288 21.1.1.Mode 0: Synchronous Mode ..............288 21.1.2.Mode 1: 8-Bit UART, Variable Baud Rate..........

- Page 8 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 25. JTAG (IEEE 1149.1) ....................341 25.1.Boundary Scan ....................342 25.1.1.EXTEST Instruction................343 25.1.2.SAMPLE Instruction ................343 25.1.3.BYPASS Instruction ................343 25.1.4.IDCODE Instruction................343 25.2.Flash Programming Commands..............344 25.3.Debug Support ....................347 Document Change List..................... 349 Contact Information....................350 Rev.

- Page 9 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 List of Figures 1. System Overview Figure 1.1. C8051F120/124 Block Diagram ............. 21 Figure 1.2. C8051F121/125 Block Diagram ............. 22 Figure 1.3. C8051F122/126 Block Diagram ............. 23 Figure 1.4. C8051F123/127 Block Diagram ............. 24 Figure 1.5. C8051F130/132 Block Diagram ............. 25 Figure 1.6.

- Page 10 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 6. ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only) Figure 6.1. 10-Bit ADC0 Functional Block Diagram ..........73 Figure 6.2. Typical Temperature Sensor Transfer Function........74 Figure 6.3. ADC0 Track and Conversion Example Timing........76 Figure 6.4. ADC0 Equivalent Input Circuits.............. 77 Figure 6.5.

- Page 11 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 13. Reset Sources Figure 13.1. Reset Sources..................177 Figure 13.2. Reset Timing ..................178 14. Oscillators Figure 14.1. Oscillator Diagram................185 Figure 14.2. PLL Block Diagram................191 15. Flash Memory Figure 15.1. Flash Memory Map for MOVC Read and MOVX Write Operations ... 201 Figure 15.2.

- Page 12 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Figure 20.4. 4-Wire Single Master and Slave Mode Connection Diagram ..... 276 Figure 20.5. Master Mode Data/Clock Timing ............278 Figure 20.6. Slave Mode Data/Clock Timing (CKPHA = 0) ........279 Figure 20.7. Slave Mode Data/Clock Timing (CKPHA = 1) ........279 Figure 20.8.

- Page 13 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 List Of Tables 1. System Overview Table 1.1. Product Selection Guide ................. 20 2. Absolute Maximum Ratings Table 2.1. Absolute Maximum Ratings ..............38 3. Global DC Electrical Characteristics Table 3.1. Global DC Electrical Characteristics (C8051F120/1/2/3 and C8051F130/1/2/3) ..........39 Table 3.2.

- Page 14 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 18. Port Input/Output Table 18.1. Port I/O DC Electrical Characteristics ..........236 19. System Management Bus / I2C Bus (SMBus0) Table 19.1. SMB0STA Status Codes and States ..........270 20. Enhanced Serial Peripheral Interface (SPI0) Table 20.1. SPI Slave Timing Parameters ............285 21.

- Page 15 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 List of Registers SFR Definition 5.1. AMX0CF: AMUX0 Configuration ......60 SFR Definition 5.2. AMX0SL: AMUX0 Channel Select ......61 SFR Definition 5.3.

- Page 16 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.4. SFRNEXT: SFR Next Register ......143 SFR Definition 11.5. SFRLAST: SFR Last Register ......143 SFR Definition 11.6.

- Page 17 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 16.5. FLSTAT: Flash Status ....... 217 SFR Definition 17.1.

- Page 18 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 23.6. TH0: Timer 0 High Byte ....... 316 SFR Definition 23.7.

-

Page 19: System Overview

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 System Overview The C8051F12x and C8051F13x device families are fully integrated mixed-signal System-on-a-Chip MCUs with 64 digital I/O pins (100-pin TQFP) or 32 digital I/O pins (64-pin TQFP). Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection. •... -

Page 20: Table 1.1. Product Selection Guide

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 1.1. Product Selection Guide C8051F120 100 128 k 8448 12 2 100TQFP C8051F120-GQ 100 128 k 8448 12 2 100TQFP ... -

Page 21: Figure 1.1. C8051F120/124 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND UART0 P0.0 DGND DGND SFR Bus UART1 P0.7 SMBus Analog Power AGND P1.0/AIN2.0 AGND SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8 kB Reset P2.7 XRAM... -

Page 22: Figure 1.2. C8051F121/125 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND UART0 P0.0 DGND DGND SFR Bus UART1 P0.7 SMBus Analog Power AGND P1.0/AIN2.0 SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8 kB Reset P2.7 XRAM... -

Page 23: Figure 1.3. C8051F122/126 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND UART0 P0.0 DGND DGND SFR Bus UART1 P0.7 SMBus Analog Power AGND P1.0/AIN2.0 AGND SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8 kB Reset P2.7 Timer 3/... -

Page 24: Figure 1.4. C8051F123/127 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND P0.0 UART0 DGND DGND SFR Bus P0.7 UART1 SMBus Analog Power AGND P1.0/AIN2.0 SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8 kb Reset P2.7 XRAM... -

Page 25: Figure 1.5. C8051F130/132 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND P0.0 UART0 DGND DGND SFR Bus P0.7 UART1 SMBus Analog Power AGND P1.0/AIN2.0 AGND SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8kbyte Reset P2.7 XRAM... -

Page 26: Figure 1.6. C8051F131/133 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Port I/O Config. Digital Power DGND UART0 P0.0 DGND DGND SFR Bus UART1 P0.7 SMBus Analog Power AGND P1.0/AIN2.0 SPI Bus 256 byte P1.7/AIN2.7 Boundary Scan JTAG Logic Timers 0, Debug HW P2.0 1, 2, 4 8kbyte Reset P2.7 Timer 3/ XRAM... -

Page 27: Microcontroller Core

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.1. CIP-51™ Microcontroller Core 1.1.1. Fully 8051 Compatible The C8051F12x and C8051F13x utilize Silicon Labs’ proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including five 16-bit counter/timers, two full-duplex UARTs, 256 bytes of internal RAM, 128 byte Special Function Regis- ter (SFR) address space, and 8/4 byte-wide I/O Ports. -

Page 28: Additional Features

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.1.3. Additional Features Several key enhancements are implemented in the CIP-51 core and peripherals to improve overall perfor- mance and ease of use in end applications. The extended interrupt handler provides 20 interrupt sources into the CIP-51 (as opposed to 7 for the stan- dard 8051), allowing the numerous analog and digital peripherals to interrupt the controller. -

Page 29: On-Chip Memory

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.2. On-Chip Memory The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. -

Page 30: Jtag Debug And Boundary Scan

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.3. JTAG Debug and Boundary Scan JTAG boundary scan and debug circuitry is included which provides non-intrusive, full speed, in-circuit debugging using the production part installed in the end application, via the four-pin JTAG interface. The JTAG port is fully compliant to IEEE 1149.1, providing full boundary scan for test and manufacturing pur- poses. -

Page 31: 16 X 16 Mac (Multiply And Accumulate) Engine

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.4. 16 x 16 MAC (Multiply and Accumulate) Engine The C8051F120/1/2/3 and C8051F130/1/2/3 devices include a multiply and accumulate engine which can be used to speed up many mathematical operations. MAC0 contains a 16-by-16 bit multiplier and a 40-bit adder, which can perform integer or fractional multiply-accumulate and multiply operations on signed input values in two SYSCLK cycles. -

Page 32: Programmable Digital I/O And Crossbar

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.5. Programmable Digital I/O and Crossbar The standard 8051 8-bit Ports (0, 1, 2, and 3) are available on the MCUs. The devices in the larger (100- pin TQFP) packaging have 4 additional ports (4, 5, 6, and 7) for a total of 64 general-purpose port I/O. The Port I/O behave like the standard 8051 with a few enhancements. -

Page 33: Programmable Counter Array

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.6. Programmable Counter Array An on-board Programmable Counter/Timer Array (PCA) is included in addition to the five 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with 6 program- mable capture/compare modules. The timebase is clocked from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflow, an External Clock Input (ECI pin), the sys- tem clock, or the external oscillator source divided by 8. -

Page 34: Or 10-Bit Analog To Digital Converter

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.8. 12 or 10-Bit Analog to Digital Converter All devices include either a 12 or 10-bit SAR ADC (ADC0) with a 9-channel input multiplexer and program- mable gain amplifier. With a maximum throughput of 100 ksps, the 12 and 10-bit ADCs offer true 12-bit lin- earity with an INL of ±1LSB. -

Page 35: 8-Bit Analog To Digital Converter

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.9. 8-Bit Analog to Digital Converter The C8051F12x devices have an on-board 8-bit SAR ADC (ADC2) with an 8-channel input multiplexer and programmable gain amplifier. This ADC features a 500 ksps maximum throughput and true 8-bit linearity with an INL of ±1LSB. Eight input pins are available for measurement. The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. -

Page 36: 12-Bit Digital To Analog Converters

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.10. 12-bit Digital to Analog Converters The C8051F12x devices have two integrated 12-bit Digital to Analog Converters (DACs). The MCU data and control interface to each DAC is via the Special Function Registers. The MCU can place either or both of the DACs in a low power shutdown mode. -

Page 37: Analog Comparators

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 1.11. Analog Comparators Two analog comparators with dedicated input pins are included on-chip. The comparators have software programmable hysteresis and response time. Each comparator can generate an interrupt on a rising edge, falling edge, or both. The interrupts are capable of waking up the MCU from sleep mode, and Comparator 0 can be used as a reset source. -

Page 38: Absolute Maximum Ratings

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Absolute Maximum Ratings Table 2.1. Absolute Maximum Ratings Parameter Conditions Units Ambient temperature under bias –55 — °C Storage Temperature –65 — °C Voltage on any Pin (except V and Port I/O) with –0.3 — Respect to DGND Voltage on any Port I/O Pin or RST with Respect to –0.3 —... -

Page 39: Global Dc Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Global DC Electrical Characteristics Table 3.1. Global DC Electrical Characteristics (C8051F120/1/2/3 and C8051F130/1/2/3) –40 to +85 °C, 100 MHz System Clock unless otherwise specified. Parameter Conditions Units SYSCLK = 0 to 50 MHz Analog Supply Voltage SYSCLK > 50 MHz Analog Supply Current Internal REF, ADCs, DACs, Com- —... -

Page 40: Table 3.2. Global Dc Electrical Characteristics (C8051F124/5/6/7)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 3.2. Global DC Electrical Characteristics (C8051F124/5/6/7) –40 to +85 °C, 50 MHz System Clock unless otherwise specified. Parameter Conditions Units Analog Supply Voltage Analog Supply Current Internal REF, ADC, DAC, Com- — — parators all active Analog Supply Current with Internal REF, ADC, DAC, Com- —... -

Page 41: Pinout And Package Definitions

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Pinout and Package Definitions Table 4.1. Pin Definitions Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 Digital Supply Voltage. Must be tied to +2.7 to 64, 90 41, 57 64, 90 41, 57 +3.6 V. - Page 42 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 VREF A I/O Bandgap Voltage Reference Output (all devices). DAC Voltage Reference Input (C8051F121/3/5/7 only). VREFA A In ADC0 and ADC2 Voltage Reference Input.

- Page 43 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 DAC1 A Out Digital to Analog Converter 1 Voltage Output. (See DAC Specification for complete descrip- tion).

- Page 44 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 AIN2.2/A10/P1.2 A In Port 1.2. See Port Input/Output section for com- D I/O plete description. AIN2.3/A11/P1.3 A In Port 1.3.

- Page 45 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 AD0/D0/P3.0 D I/O Bit 0 External Memory Address/Data bus (Multi- plexed mode) Bit 0 External Memory Data bus (Non-multi- plexed mode) Port 3.0 See Port Input/Output section for complete...

- Page 46 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 ALE/P4.5 D I/O ALE Strobe for External Memory Address bus (multiplexed mode) Port 4.5 See Port Input/Output section for complete description.

- Page 47 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 A8m/A0/P6.0 D I/O Bit 8 External Memory Address bus (Multiplexed mode) Bit 0 External Memory Address bus (Non-multi- plexed mode) Port 6.0 See Port Input/Output section for complete...

- Page 48 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 4.1. Pin Definitions (Continued) Pin Numbers ‘F120 ‘F121 ‘F130 ‘F131 Name Type Description ‘F122 ‘F123 ‘F132 ‘F133 ‘F124 ‘F125 ‘F126 ‘F127 AD5/D5/P7.5 D I/O Port 7.5. See Port Input/Output section for com- plete description. AD6/D6/P7.6 D I/O Port 7.6. See Port Input/Output section for com- plete description.

-

Page 49: Figure 4.1. C8051F120/2/4/6 Pinout Diagram (Tqfp-100)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 A13m/A5/P6.5 A14m/A6/P6.6 A15m/A7/P6.7 AD0/D0/P7.0 /RST AD1/D1/P7.1 CP1- AD2/D2/P7.2 CP1+ AD3/D3/P7.3 CP0- AD4/D4/P7.4 CP0+ AD5/D5/P7.5 AGND AD6/D6/P7.6 C8051F120 AD7/D7/P7.7 C8051F122 VREF AGND DGND C8051F124 P0.0 VREFD P0.1 C8051F126 VREF0 P0.2 VREF2 P0.3 AIN0.0 P0.4 AIN0.1 ALE/P0.5 AIN0.2 /RD/P0.6 AIN0.3 /WR/P0.7 AIN0.4 AD0/D0/P3.0... -

Page 50: Figure 4.2. C8051F130/2 Pinout Diagram (Tqfp-100)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 A13m/A5/P6.5 A14m/A6/P6.6 A15m/A7/P6.7 AD0/D0/P7.0 /RST AD1/D1/P7.1 CP1- AD2/D2/P7.2 CP1+ AD3/D3/P7.3 CP0- AD4/D4/P7.4 CP0+ AD5/D5/P7.5 AGND AD6/D6/P7.6 AD7/D7/P7.7 C8051F130 VREF AGND DGND C8051F132 P0.0 P0.1 VREF0 P0.2 P0.3 AIN0.0 P0.4 AIN0.1 ALE/P0.5 AIN0.2 /RD/P0.6 AIN0.3 /WR/P0.7 AIN0.4 AD0/D0/P3.0 AIN0.5 AD1/D1/P3.1 AIN0.6 AD2/D2/P3.2... -

Page 51: Figure 4.3. Tqfp-100 Package Drawing

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 (mm) (mm) (mm) 1.20 0.05 0.15 0.95 1.00 1.05 0.17 0.22 0.27 16.00 14.00 0.50 16.00 14.00 0.45 0.60 0.75 PIN 1 DESIGNATOR Figure 4.3. TQFP-100 Package Drawing Rev. 1.4... -

Page 52: Figure 4.4. C8051F121/3/5/7 Pinout Diagram (Tqfp-64)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 CP1- /WR/P0.7 CP1+ AD0/D0/P3.0 CP0- AD1/D1/P3.1 CP0+ AD2/D2/P3.2 AGND AD3/D3/P3.3 AD4/D4/P3.4 C8051F121 VREF AD5/D5/P3.5 C8051F123 VREFA C8051F125 AIN0.0 DGND AIN0.1 AD6/D6/P3.6 C8051F127 AIN0.2 AD7/D7/P3.7 AIN0.3 A8m/A0/P2.0 AIN0.4 A9m/A1/P2.1 AIN0.5 A10m/A2/P2.2 AIN0.6 A11m/A3/P2.3 AIN0.7 A12m/A4/P2.4 Figure 4.4. C8051F121/3/5/7 Pinout Diagram (TQFP-64) Rev. -

Page 53: Figure 4.5. C8051F131/3 Pinout Diagram (Tqfp-64)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 CP1- /WR/P0.7 CP1+ AD0/D0/P3.0 CP0- AD1/D1/P3.1 CP0+ AD2/D2/P3.2 AGND AD3/D3/P3.3 AD4/D4/P3.4 VREF AD5/D5/P3.5 C8051F131 VREF0 C8051F133 AIN0.0 DGND AIN0.1 AD6/D6/P3.6 AIN0.2 AD7/D7/P3.7 AIN0.3 A8m/A0/P2.0 AIN0.4 A9m/A1/P2.1 AIN0.5 A10m/A2/P2.2 AIN0.6 A11m/A3/P2.3 AIN0.7 A12m/A4/P2.4 Figure 4.5. C8051F131/3 Pinout Diagram (TQFP-64) Rev. -

Page 54: Figure 4.6. Tqfp-64 Package Drawing

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 (mm) (mm) (mm) 1.20 0.05 0.15 0.95 1.00 1.05 0.17 0.22 0.27 12.00 10.00 0.50 PIN 1 DESIGNATOR 12.00 10.00 0.45 0.60 0.75 Figure 4.6. TQFP-64 Package Drawing Rev. 1.4... -

Page 55: Adc0 (12-Bit Adc, C8051F120/1/4/5 Only)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 ADC0 (12-Bit ADC, C8051F120/1/4/5 Only) The ADC0 subsystem for the C8051F120/1/4/5 consists of a 9-channel, configurable analog multiplexer (AMUX0), a programmable gain amplifier (PGA0), and a 100 ksps, 12-bit successive-approximation-regis- ter ADC with integrated track-and-hold and Programmable Window Detector (see block diagram in Figure 5.1). -

Page 56: Figure 5.2. Typical Temperature Sensor Transfer Function

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 The Temperature Sensor transfer function is shown in Figure 5.2. The output voltage (V ) is the PGA TEMP input when the Temperature Sensor is selected by bits AMX0AD3-0 in register AMX0SL; this voltage will be amplified by the PGA according to the user-programmed PGA settings. Typical values for the Slope and Offset parameters can be found in Table 5.1. -

Page 57: Adc Modes Of Operation

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 5.2. ADC Modes of Operation ADC0 has a maximum conversion speed of 100 ksps. The ADC0 conversion clock is derived from the sys- tem clock divided by the value held in the ADCSC bits of register ADC0CF. 5.2.1. Starting a Conversion A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1, AD0CM0) in ADC0CN. -

Page 58: Tracking Modes

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 5.2.2. Tracking Modes The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked when a conversion is not in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. -

Page 59: Settling Time Requirements

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 5.2.3. Settling Time Requirements A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the ADC0 MUX resistance, the ADC0 sampling capacitance, any external source resis- tance, and the accuracy required for the conversion. Figure 5.4 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. -

Page 60: Sfr Definition 5.1. Amx0Cf: Amux0 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.1. AMX0CF: AMUX0 Configuration SFR Page: 0xBA SFR Address: Reset Value AIN67IC AIN45IC AIN23IC AIN01IC 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–4: UNUSED. Read = 0000b; Write = don’t care. Bit3: AIN67IC: AIN0.6, AIN0.7 Input Pair Configuration Bit. 0: AIN0.6 and AIN0.7 are independent single-ended inputs. -

Page 61: Sfr Definition 5.2. Amx0Sl: Amux0 Channel Select

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.2. AMX0SL: AMUX0 Channel Select SFR Page: 0xBB SFR Address: Reset Value AMX0AD3 AMX0AD2 AMX0AD1 AMX0AD0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–4: UNUSED. Read = 0000b; Write = don’t care. Bits3–0: AMX0AD3–0: AMX0 Address Bits. 0000-1111b: ADC Inputs selected per chart below. -

Page 62: Sfr Definition 5.3. Adc0Cf: Adc0 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.3. ADC0CF: ADC0 Configuration SFR Page: 0xBC SFR Address: Reset Value AD0SC4 AD0SC3 AD0SC2 AD0SC1 AD0SC0 AMP0GN2 AMP0GN1 AMP0GN0 11111000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–3: AD0SC4–0: ADC0 SAR Conversion Clock Period Bits. The SAR Conversion clock is derived from system clock by the following equation, where AD0SC refers to the 5-bit value held in AD0SC4-0, and CLK refers to the desired ADC0... -

Page 63: Sfr Definition 5.4. Adc0Cn: Adc0 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.4. ADC0CN: ADC0 Control SFR Page: 0xE8 (bit addressable) SFR Address: Reset Value AD0EN AD0TM AD0INT AD0BUSY AD0CM1 AD0CM0 AD0WINT AD0LJST 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7: AD0EN: ADC0 Enable Bit. 0: ADC0 Disabled. ADC0 is in low-power shutdown. 1: ADC0 Enabled. -

Page 64: Sfr Definition 5.5. Adc0H: Adc0 Data Word Msb

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.5. ADC0H: ADC0 Data Word MSB SFR Page: 0xBF SFR Address: Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: ADC0 Data Word High-Order Bits. For AD0LJST = 0: Bits 7–4 are the sign extension of Bit3. Bits 3–0 are the upper 4 bits of the 12-bit ADC0 Data Word. -

Page 65: Figure 5.5. Adc0 Data Word Example

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12-bit ADC0 Data Word appears in the ADC0 Data Word Registers as follows: ADC0H[3:0]:ADC0L[7:0], if AD0LJST = 0 (ADC0H[7:4] will be sign-extension of ADC0H.3 for a differential reading, otherwise 0000b). ADC0H[7:0]:ADC0L[7:4], if AD0LJST = 1 (ADC0L[3:0] = 0000b). Example: ADC0 Data Word Conversion Map, AIN0.0 Input in Single-Ended Mode (AMX0CF = 0x00, AMX0SL = 0x00) AIN0.0–AGND... -

Page 66: Adc0 Programmable Window Detector

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 5.3. ADC0 Programmable Window Detector The ADC0 Programmable Window Detector continuously compares the ADC0 output to user-programmed limits, and notifies the system when an out-of-bound condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. -

Page 67: Sfr Definition 5.9. Adc0Lth: Adc0 Less-Than Data High Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte SFR Page: 0xC7 SFR Address: Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: High byte of ADC0 Less-Than Data Word. SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte SFR Page: 0xC6 SFR Address:... -

Page 68: Figure 5.6. 12-Bit Adc0 Window Interrupt Example: Right Justified Single-Ended Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage Input Voltage ADC Data ADC Data (AD0.0 - AGND) (AD0.0 - AGND) Word Word REF x (4095/4096) 0x0FFF REF x (4095/4096) 0x0FFF AD0WINT AD0WINT=1 not affected 0x0201 0x0201 REF x (512/4096) 0x0200 ADC0LTH:ADC0LTL REF x (512/4096) 0x0200 ADC0GTH:ADC0GTL 0x01FF... -

Page 69: Figure 5.7. 12-Bit Adc0 Window Interrupt Example: Right Justified Differential Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage ADC Data Input Voltage ADC Data (AD0.0 - AD0.1) (AD0.0 - AD0.1) Word Word REF x (2047/2048) 0x07FF REF x (2047/2048) 0x07FF AD0WINT AD0WINT=1 not affected 0x0101 0x0101 REF x (256/2048) 0x0100 ADC0LTH:ADC0LTL REF x (256/2048) 0x0100 ADC0GTH:ADC0GTL 0x00FF... -

Page 70: Figure 5.8. 12-Bit Adc0 Window Interrupt Example: Left Justified Single-Ended Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage ADC Data Input Voltage ADC Data (AD0.0 - AGND) (AD0.0 - AGND) Word Word REF x (4095/4096) 0xFFF0 REF x (4095/4096) 0xFFF0 AD0WINT AD0WINT=1 not affected 0x2010 0x2010 REF x (512/4096) 0x2000 ADC0LTH:ADC0LTL REF x (512/4096) 0x2000 ADC0GTH:ADC0GTL 0x1FF0... -

Page 71: Figure 5.9. 12-Bit Adc0 Window Interrupt Example: Left Justified Differential Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage ADC Data Input Voltage ADC Data (AD0.0 - AD0.1) (AD0.0 - AD0.1) Word Word REF x (2047/2048) 0x7FF0 REF x (2047/2048) 0x7FF0 AD0WINT AD0WINT=1 not affected 0x1010 0x1010 REF x (256/2048) 0x1000 ADC0LTH:ADC0LTL REF x (256/2048) 0x1000 ADC0GTH:ADC0GTL 0x0FF0... -

Page 72: Table 5.1. 12-Bit Adc0 Electrical Characteristics (C8051F120/1/4/5)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 5.1. 12-Bit ADC0 Electrical Characteristics (C8051F120/1/4/5) = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), PGA Gain = 1, –40 to +85 °C unless otherwise specified. Parameter Conditions Units DC Accuracy Resolution bits Integral Nonlinearity —... -

Page 73: Adc0 (10-Bit Adc, C8051F122/3/6/7 And C8051F13X Only)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 ADC0 (10-Bit ADC, C8051F122/3/6/7 and C8051F13x Only) The ADC0 subsystem for the C8051F122/3/6/7 and C8051F13x consists of a 9-channel, configurable ana- log multiplexer (AMUX0), a programmable gain amplifier (PGA0), and a 100 ksps, 10-bit successive- approximation-register ADC with integrated track-and-hold and Programmable Window Detector (see block diagram in Figure 6.1). -

Page 74: Figure 6.2. Typical Temperature Sensor Transfer Function

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 The Temperature Sensor transfer function is shown in Figure 6.2. The output voltage (V ) is the PGA TEMP input when the Temperature Sensor is selected by bits AMX0AD3-0 in register AMX0SL; this voltage will be amplified by the PGA according to the user-programmed PGA settings. Typical values for the Slope and Offset parameters can be found in Table 6.1. -

Page 75: Adc Modes Of Operation

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 6.2. ADC Modes of Operation ADC0 has a maximum conversion speed of 100 ksps. The ADC0 conversion clock is derived from the sys- tem clock divided by the value held in the ADCSC bits of register ADC0CF. 6.2.1. Starting a Conversion A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1, AD0CM0) in ADC0CN. -

Page 76: Tracking Modes

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 6.2.2. Tracking Modes The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked when a conversion is not in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. -

Page 77: Settling Time Requirements

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 6.2.3. Settling Time Requirements A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the ADC0 MUX resistance, the ADC0 sampling capacitance, any external source resis- tance, and the accuracy required for the conversion. Figure 6.4 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. -

Page 78: Sfr Definition 6.1. Amx0Cf: Amux0 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.1. AMX0CF: AMUX0 Configuration SFR Page: 0xBA SFR Address: Reset Value AIN67IC AIN45IC AIN23IC AIN01IC 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–4: UNUSED. Read = 0000b; Write = don’t care. Bit3: AIN67IC: AIN0.6, AIN0.7 Input Pair Configuration Bit. 0: AIN0.6 and AIN0.7 are independent single-ended inputs. -

Page 79: Sfr Definition 6.2. Amx0Sl: Amux0 Channel Select

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.2. AMX0SL: AMUX0 Channel Select SFR Page: 0xBB SFR Address: Reset Value AMX0AD3 AMX0AD2 AMX0AD1 AMX0AD0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–4: UNUSED. Read = 0000b; Write = don’t care. Bits3–0: AMX0AD3–0: AMX0 Address Bits. 0000-1111b: ADC Inputs selected per chart below. -

Page 80: Sfr Definition 6.3. Adc0Cf: Adc0 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.3. ADC0CF: ADC0 Configuration SFR Page: 0xBC SFR Address: Reset Value AD0SC4 AD0SC3 AD0SC2 AD0SC1 AD0SC0 AMP0GN2 AMP0GN1 AMP0GN0 11111000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–3: AD0SC4–0: ADC0 SAR Conversion Clock Period Bits. SAR Conversion clock is derived from system clock by the following equation, where AD0SC refers to the 5-bit value held in AD0SC4-0, and CLK refers to the desired ADC0... -

Page 81: Sfr Definition 6.4. Adc0Cn: Adc0 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.4. ADC0CN: ADC0 Control SFR Page: 0xE8 (bit addressable) SFR Address: Reset Value AD0EN AD0TM AD0INT AD0BUSY AD0CM1 AD0CM0 AD0WINT AD0LJST 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7: AD0EN: ADC0 Enable Bit. 0: ADC0 Disabled. ADC0 is in low-power shutdown. 1: ADC0 Enabled. -

Page 82: Sfr Definition 6.5. Adc0H: Adc0 Data Word Msb

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.5. ADC0H: ADC0 Data Word MSB SFR Page: 0xBF SFR Address: Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: ADC0 Data Word High-Order Bits. For AD0LJST = 0: Bits 7–4 are the sign extension of Bit3. Bits 3–0 are the upper 4 bits of the 10-bit ADC0 Data Word. -

Page 83: Figure 6.5. Adc0 Data Word Example

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 10-bit ADC0 Data Word appears in the ADC0 Data Word Registers as follows: ADC0H[1:0]:ADC0L[7:0], if AD0LJST = 0 (ADC0H[7:2] will be sign-extension of ADC0H.1 for a differential reading, otherwise 000000b). ADC0H[7:0]:ADC0L[7:6], if AD0LJST = 1 (ADC0L[5:0] = 00b). Example: ADC0 Data Word Conversion Map, AIN0.0 Input in Single-Ended Mode (AMX0CF = 0x00, AMX0SL = 0x00) AIN0.0–AGND... -

Page 84: Adc0 Programmable Window Detector

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 6.3. ADC0 Programmable Window Detector The ADC0 Programmable Window Detector continuously compares the ADC0 output to user-programmed limits, and notifies the system when an out-of-bound condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. -

Page 85: Sfr Definition 6.9. Adc0Lth: Adc0 Less-Than Data High Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 6.9. ADC0LTH: ADC0 Less-Than Data High Byte SFR Page: 0xC7 SFR Address: Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: High byte of ADC0 Less-Than Data Word. SFR Definition 6.10. ADC0LTL: ADC0 Less-Than Data Low Byte SFR Page: 0xC6 SFR Address:... -

Page 86: Figure 6.6. 10-Bit Adc0 Window Interrupt Example: Right Justified Single-Ended Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage Input Voltage ADC Data ADC Data (AD0.0 - AGND) (AD0.0 - AGND) Word Word REF x (1023/1024) 0x03FF REF x (1023/1024) 0x03FF ADWINT ADWINT=1 not affected 0x0201 0x0201 REF x (512/1024) 0x0200 ADC0LTH:ADC0LTL REF x (512/1024) 0x0200 ADC0GTH:ADC0GTL 0x01FF... -

Page 87: Figure 6.7. 10-Bit Adc0 Window Interrupt Example: Right Justified Differential Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage ADC Data Input Voltage ADC Data (AD0.0 - AD0.1) (AD0.0 - AD0.1) Word Word REF x (511/512) 0x01FF REF x (511/512) 0x01FF ADWINT ADWINT=1 not affected 0x0101 0x0101 REF x (256/512) 0x0100 ADC0LTH:ADC0LTL REF x (256/512) 0x0100 ADC0GTH:ADC0GTL 0x00FF... -

Page 88: Figure 6.8. 10-Bit Adc0 Window Interrupt Example: Left Justified Single-Ended Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage Input Voltage ADC Data ADC Data (AD0.0 - AGND) (AD0.0 - AGND) Word Word REF x (1023/1024) 0xFFC0 REF x (1023/1024) 0xFFC0 ADWINT ADWINT=1 not affected 0x8040 0x8040 REF x (512/1024) 0x8000 ADC0LTH:ADC0LTL REF x (512/1024) 0x8000 ADC0GTH:ADC0GTL 0x7FC0... -

Page 89: Figure 6.9. 10-Bit Adc0 Window Interrupt Example: Left Justified Differential Data

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Input Voltage ADC Data Input Voltage ADC Data (AD0.0 - AD0.1) (AD0.0 - AD0.1) Word Word REF x (511/512) 0x7FC0 REF x (511/512) 0x7FC0 ADWINT ADWINT=1 not affected 0x2040 0x2040 REF x (128/512) 0x2000 ADC0LTH:ADC0LTL REF x (128/512) 0x2000 ADC0GTH:ADC0GTL 0x1FC0... -

Page 90: Table 6.1. 10-Bit Adc0 Electrical Characteristics (C8051F122/3/6/7 And C8051F13X)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 6.1. 10-Bit ADC0 Electrical Characteristics (C8051F122/3/6/7 and C8051F13x) = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), PGA Gain = 1, –40 to +85 °C unless otherwise specified. Parameter Conditions Units DC Accuracy Resolution bits Integral Nonlinearity... -

Page 91: Adc2 (8-Bit Adc, C8051F12X Only)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 ADC2 (8-Bit ADC, C8051F12x Only) The C8051F12x devices include a second ADC peripheral (ADC2), which consists of an 8-channel, config- urable analog multiplexer, a programmable gain amplifier, and a 500 ksps, 8-bit successive-approximation- register ADC with integrated track-and-hold (see block diagram in Figure 7.1). ADC2 is fully configurable under software control via the Special Function Registers shown in Figure 7.1. -

Page 92: Adc2 Modes Of Operation

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 7.2. ADC2 Modes of Operation ADC2 has a maximum conversion speed of 500 ksps. The ADC2 conversion clock (SAR2 clock) is a divided version of the system clock, determined by the AD2SC bits in the ADC2CF register. The maximum ADC2 conversion clock is 6 MHz. -

Page 93: Figure 7.2. Adc2 Track And Conversion Example Timing

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 A. ADC Timing for External Trigger Source CNVSTR2 (AD2CM[2:0]=010) SAR Clocks Low Power AD2TM=1 Track Convert Low Power Mode or Convert AD2TM=0 Track or Convert Convert Track B. ADC Timing for Internal Trigger Source Write '1' to AD2BUSY, Timer 3 Overflow, Timer 2 Overflow, Write '1' to AD0BUSY... -

Page 94: Settling Time Requirements

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 7.2.3. Settling Time Requirements A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the ADC2 MUX resistance, the ADC2 sampling capacitance, any external source resis- tance, and the accuracy required for the conversion. Figure 7.3 shows the equivalent ADC2 input circuit. The required ADC2 settling time for a given settling accuracy (SA) may be approximated by Equation 7.1. -

Page 95: Sfr Definition 7.1. Amx2Cf: Amux2 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.1. AMX2CF: AMUX2 Configuration SFR Page: 0xBA SFR Address: Reset Value PIN67IC PIN45IC PIN23IC PIN01IC 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–4: UNUSED. Read = 0000b; Write = don’t care. Bit3: PIN67IC: AIN2.6, AIN2.7 Input Pair Configuration Bit. 0: AIN2.6 and AIN2.7 are independent single-ended inputs. -

Page 96: Sfr Definition 7.2. Amx2Sl: Amux2 Channel Select

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.2. AMX2SL: AMUX2 Channel Select SFR Page: 0xBB SFR Address: Reset Value AMX2AD2 AMX2AD1 AMX2AD0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–3: UNUSED. Read = 00000b; Write = don’t care. Bits2–0: AMX2AD2–0: AMX2 Address Bits. 000-111b: ADC Inputs selected per chart below. -

Page 97: Sfr Definition 7.3. Adc2Cf: Adc2 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.3. ADC2CF: ADC2 Configuration SFR Page: 0xBC SFR Address: Reset Value AD2SC4 AD2SC3 AD2SC2 AD2SC1 AD2SC0 AMP2GN1 AMP2GN0 11111000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–3: AD2SC4–0: ADC2 SAR Conversion Clock Period Bits. SAR Conversion clock is derived from system clock by the following equation, where AD2SC refers to the 5-bit value held in AD2SC4–0, and CLK refers to the desired SAR2... -

Page 98: Sfr Definition 7.4. Adc2Cn: Adc2 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.4. ADC2CN: ADC2 Control SFR Page: 0xE8 (bit addressable) SFR Address: Reset Value AD2EN AD2TM AD2INT AD2BUSY AD2CM2 AD2CM1 AD2CM0 AD2WINT 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7: AD2EN: ADC2 Enable Bit. 0: ADC2 Disabled. ADC2 is in low-power shutdown. 1: ADC2 Enabled. -

Page 99: Figure 7.4. Adc2 Data Word Example

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.5. ADC2: ADC2 Data Word SFR Page: 0xBE SFR Address: Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: ADC2 Data Word. Single-Ended Example: 8-bit ADC Data Word appears in the ADC2 Data Word Register as follows: Example: ADC2 Data Word Conversion Map, Single-Ended AIN2.0 Input (AMX2CF = 0x00;... -

Page 100: Adc2 Programmable Window Detector

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 7.3. ADC2 Programmable Window Detector The ADC2 Programmable Window Detector continuously compares the ADC2 output to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an inter- rupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in register ADC2CN) can also be used in polled mode. -

Page 101: Window Detector In Differential Mode

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 7.3.2. Window Detector In Differential Mode Figure 7.6 shows two example window comparisons for differential mode, with ADC2LT = 0x10 (+16d) and ADC2GT = 0xFF (-1d). Notice that in Differential mode, the codes vary from -VREF to VREF*(127/128) and are represented as 8-bit 2’s complement signed integers. -

Page 102: Sfr Definition 7.6. Adc2Gt: Adc2 Greater-Than Data Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 7.6. ADC2GT: ADC2 Greater-Than Data Byte SFR Page: 0xC4 SFR Address: Reset Value 11111111 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–0: ADC2 Greater-Than Data Word. SFR Definition 7.7. ADC2LT: ADC2 Less-Than Data Byte SFR Page: 0xC6 SFR Address: Reset Value... -

Page 103: Table 7.1. Adc2 Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 7.1. ADC2 Electrical Characteristics = 3.0 V, AV+ = 3.0 V, VREF2 = 2.40 V (REFBE = 0), PGA gain = 1, –40 to +85 °C unless otherwise specified. Parameter Conditions Units DC Accuracy Resolution bits Integral Nonlinearity —... - Page 104 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 OTES Rev. 1.4...

-

Page 105: Dacs, 12-Bit Voltage Mode (C8051F12X Only)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 DACs, 12-Bit Voltage Mode (C8051F12x Only) The C8051F12x devices include two on-chip 12-bit voltage-mode Digital-to-Analog Converters (DACs). Each DAC has an output swing of 0 V to (VREF-1LSB) for a corresponding input code range of 0x000 to 0xFFF. The DACs may be enabled/disabled via their corresponding control registers, DAC0CN and DAC1CN. -

Page 106: Update Output On-Demand

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 8.1.1. Update Output On-Demand In its default mode (DAC0CN.[4:3] = ‘00’) the DAC0 output is updated “on-demand” on a write to the high- byte of the DAC0 data register (DAC0H). It is important to note that writes to DAC0L are held, and have no effect on the DAC0 output until a write to DAC0H takes place. -

Page 107: Sfr Definition 8.1. Dac0H: Dac0 High Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 8.1. DAC0H: DAC0 High Byte Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xD3 SFR Page: Bits7–0: DAC0 Data Word Most Significant Byte. SFR Definition 8.2. DAC0L: DAC0 Low Byte Reset Value 00000000 Bit7 Bit6... -

Page 108: Sfr Definition 8.3. Dac0Cn: Dac0 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 8.3. DAC0CN: DAC0 Control Reset Value DAC0EN DAC0MD1 DAC0MD0 DAC0DF2 DAC0DF1 DAC0DF0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xD4 SFR Page: Bit7: DAC0EN: DAC0 Enable Bit. 0: DAC0 Disabled. DAC0 Output pin is disabled; DAC0 is in low-power shutdown mode. 1: DAC0 Enabled. -

Page 109: Sfr Definition 8.4. Dac1H: Dac1 High Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 8.4. DAC1H: DAC1 High Byte Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xD3 SFR Page: Bits7–0: DAC1 Data Word Most Significant Byte. SFR Definition 8.5. DAC1L: DAC1 Low Byte Reset Value 00000000 Bit7 Bit6... -

Page 110: Sfr Definition 8.6. Dac1Cn: Dac1 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 8.6. DAC1CN: DAC1 Control Reset Value DAC1EN DAC1MD1 DAC1MD0 DAC1DF2 DAC1DF1 DAC1DF0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xD4 SFR Page: Bit7: DAC1EN: DAC1 Enable Bit. 0: DAC1 Disabled. DAC1 Output pin is disabled; DAC1 is in low-power shutdown mode. 1: DAC1 Enabled. -

Page 111: Table 8.1. Dac Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 8.1. DAC Electrical Characteristics = 3.0 V, AV+ = 3.0 V, VREF = 2.40 V (REFBE = 0), No Output Load unless otherwise specified Parameter Conditions Units Static Performance Resolution bits Integral Nonlinearity — ±1.5 — Differential Nonlinearity —... - Page 112 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 OTES Rev. 1.4...

-

Page 113: Voltage Reference

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Voltage Reference The voltage reference options available on the C8051F12x and C8051F13x device families vary according to the device capabilities. All devices include an internal voltage reference circuit, consisting of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins. -

Page 114: Figure 9.1. Voltage Reference Functional Block Diagram (C8051F120/2/4/6)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 REF0CN ADC2 VREF2 External Voltage Reference Circuit ADC0 DGND VREF0 DAC0 VREFD DAC1 BIASE Bias to ADCs, VREF DACs 1.2V Band-Gap 4.7μF 0.1μF REFBE Recommended Bypass Capacitors Figure 9.1. Voltage Reference Functional Block Diagram (C8051F120/2/4/6) SFR Definition 9.1. REF0CN: Reference Control (C8051F120/2/4/6) SFR Page: 0xD1 SFR Address:... -

Page 115: Reference Configuration On The C8051F121/3/5/7

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 9.2. Reference Configuration on the C8051F121/3/5/7 On the C8051F121/3/5/7 devices, the REF0CN register also allows selection of the voltage reference source for ADC0 and ADC2, as shown in SFR Definition 9.2. Bits AD0VRS and AD2VRS in the REF0CN register select the ADC0 and ADC2 voltage reference sources, respectively. -

Page 116: Sfr Definition 9.2. Ref0Cn: Reference Control (C8051F121/3/5/7)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 9.2. REF0CN: Reference Control (C8051F121/3/5/7) SFR Page: 0xD1 SFR Address: Reset Value AD0VRS AD2VRS TEMPE BIASE REFBE 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–5: UNUSED. Read = 000b; Write = don’t care. Bit4: AD0VRS: ADC0 Voltage Reference Select. -

Page 117: Reference Configuration On The C8051F130/1/2/3

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 9.3. Reference Configuration on the C8051F130/1/2/3 On the C8051F130/1/2/3 devices, the VREF0 pin provides a voltage reference input for ADC0, which can be connected to an external precision reference or the internal voltage reference, as shown in Figure 9.3. The REF0CN register for the C8051F130/1/2/3 is described in SFR Definition 9.3. -

Page 118: Table 9.1. Voltage Reference Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 9.1. Voltage Reference Electrical Characteristics = 3.0 V, AV+ = 3.0 V, –40 to +85 °C unless otherwise specified. Parameter Conditions Units Analog Bias Generator Power — — µA BIASE = 1 Supply Current Internal Reference (REFBE = 1) Output Voltage 25 °C ambient 2.36... -

Page 119: Comparators

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 10. Comparators Two on-chip programmable voltage comparators are included, as shown in Figure 10.1. The inputs of each comparator are available at dedicated pins. The output of each comparator is optionally available at the package pins via the I/O crossbar. When assigned to package pins, each comparator output can be pro- grammed to operate in open drain or push-pull modes. - Page 120 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Comparator interrupts can be generated on rising-edge and/or falling-edge output transitions. (For inter- rupt enable and priority control, see Section “11.3. Interrupt Handler” on page 154 ). The CP0FIF flag is set upon a Comparator0 falling-edge interrupt, and the CP0RIF flag is set upon the Comparator0 rising- edge interrupt.

-

Page 121: Figure 10.2. Comparator Hysteresis Plot

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 CP0+ VIN+ CP0- VIN- CIRCUIT CONFIGURATION Positive Hysteresis Voltage (Programmed with CP0HYP Bits) VIN- INPUTS Negative Hysteresis Voltage (Programmed by CP0HYN Bits) VIN+ OUTPUT Negative Hysteresis Maximum Disabled Negative Hysteresis Positive Hysteresis Maximum Disabled Positive Hysteresis Figure 10.2. Comparator Hysteresis Plot Rev. -

Page 122: Sfr Definition 10.1. Cpt0Cn: Comparator0 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 10.1. CPT0CN: Comparator0 Control SFR Page: 0x88 SFR Address: Reset Value CP0EN CP0OUT CP0RIF CP0FIF CP0HYP1 CP0HYP0 CP0HYN1 CP0HYN0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7: CP0EN: Comparator0 Enable Bit. 0: Comparator0 Disabled. 1: Comparator0 Enabled. -

Page 123: Sfr Definition 10.2. Cpt0Md: Comparator0 Mode Selection

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 10.2. CPT0MD: Comparator0 Mode Selection SFR Page: 0x89 SFR Address: Reset Value CP0RIE CP0FIE CP0MD1 CP0MD0 00000010 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–6: UNUSED. Read = 00b, Write = don’t care. Bit 5: CP0RIE: Comparator 0 Rising-Edge Interrupt Enable Bit. -

Page 124: Sfr Definition 10.3. Cpt1Cn: Comparator1 Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 10.3. CPT1CN: Comparator1 Control SFR Page: 0x88 SFR Address: Reset Value CP1EN CP1OUT CP1RIF CP1FIF CP1HYP1 CP1HYP0 CP1HYN1 CP1HYN0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7: CP1EN: Comparator1 Enable Bit. 0: Comparator1 Disabled. 1: Comparator1 Enabled. -

Page 125: Sfr Definition 10.4. Cpt1Md: Comparator1 Mode Selection

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 10.4. CPT1MD: Comparator1 Mode Selection SFR Page: 0x89 SFR Address: Reset Value CP1RIE CP1FIE CP1MD1 CP1MD0 00000010 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bits7–6: UNUSED. Read = 00b, Write = don’t care. Bit 5: CP1RIE: Comparator 1 Rising-Edge Interrupt Enable Bit. -

Page 126: Table 10.1. Comparator Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 10.1. Comparator Electrical Characteristics = 3.0 V, AV+ = 3.0 V, –40 to +85 °C unless otherwise specified. Parameter Conditions Units CPn+ – CPn- = 100 mV — — Response Time: Mode 0, V = 1.5 V CPn+ –... -

Page 127: Microcontroller

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11. CIP-51 Microcontroller The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be used to develop soft- ware. The MCU family has a superset of all the peripherals included with a standard 8051. Included are five 16-bit counter/timers (see description in Section 23 ), two full-duplex UARTs (see description in... -

Page 128: Figure 11.1. Cip-51 Block Diagram

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 DATA BUS ACCUMULATOR B REGISTER STACK POINTER TMP1 TMP2 SRAM SRAM ADDRESS (256 X 8) REGISTER DATA BUS SFR_ADDRESS BUFFER SFR_CONTROL SFR_WRITE_DATA DATA POINTER INTERFACE SFR_READ_DATA PC INCREMENTER MEM_ADDRESS PROGRAM COUNTER (PC) MEM_CONTROL MEMORY PRGM. ADDRESS REG. MEM_WRITE_DATA INTERFACE MEM_READ_DATA PIPELINE... -

Page 129: Instruction Set

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.1. Instruction Set The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51™ instruc- tion set; standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51™ counterparts, including opcodes, addressing modes and effect on PSW flags. - Page 130 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.1. CIP-51 Instruction Set Summary (Continued) Clock Mnemonic Description Bytes Cycles DEC A Decrement A DEC Rn Decrement register DEC direct Decrement direct byte DEC @Ri Decrement indirect RAM INC DPTR Increment Data Pointer MUL AB Multiply A and B DIV AB Divide A by B DA A...

- Page 131 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.1. CIP-51 Instruction Set Summary (Continued) Clock Mnemonic Description Bytes Cycles MOV direct, @Ri Move indirect RAM to direct byte MOV direct, #data Move immediate to direct byte MOV @Ri, A Move A to indirect RAM MOV @Ri, direct Move direct byte to indirect RAM MOV @Ri, #data Move immediate to indirect RAM...

- Page 132 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.1. CIP-51 Instruction Set Summary (Continued) Clock Mnemonic Description Bytes Cycles JZ rel Jump if A equals zero 2/3* JNZ rel Jump if A does not equal zero 2/3* CJNE A, direct, rel Compare direct byte to A and jump if not equal 3/4* CJNE A, #data, rel Compare immediate to A and jump if not equal...

-

Page 133: Memory Organization

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.2. Memory Organization The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. There are 256 bytes of internal data memory and 128k bytes (C8051F12x and C8051F130/1) or 64k bytes (C8051F132/3) of internal program memory address space implemented within the CIP-51. -

Page 134: Figure 11.3. Address Memory Map For Instruction Fetches (128 Kb Flash Only)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.1. PSBANK: Program Space Bank Select Reset Value COBANK IFBANK 00010001 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xB1 SFR Page: All Pages – Bits 7 6: Reserved. – Bits 5 4: COBANK: Constant Operations Bank Select. These bits select which Flash bank is targeted during constant operations (MOVC and Flash MOVX) involving addresses 0x8000 to 0xFFFF. -

Page 135: Data Memory

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.2.2. Data Memory The CIP-51 implements 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. -

Page 136: Special Function Registers

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 and a RET pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the debug software even with the MCU running at speed. 11.2.6. Special Function Registers The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFR’s). -

Page 137: Figure 11.4. Sfr Page Stack

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFRPGCN Bit Interrupt Logic SFRPAGE CIP-51 SFRNEXT SFRLAST Figure 11.4. SFR Page Stack Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFRPGCN). This function defaults to ‘enabled’... -

Page 138: Figure 11.5. Sfr Page Stack While Using Sfr Page 0X0F To Access Port 5

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.2.6.3.SFR Page Stack Example The following is an example that shows the operation of the SFR Page Stack during interrupts. In this example, the SFR Page Control is left in the default enabled state (i.e., SFRPGEN = 1), and the CIP-51 is executing in-line code that is writing values to Port 5 (SFR “P5”, located at address 0xD8 on SFR Page 0x0F). -

Page 139: Figure 11.6. Sfr Page Stack After Adc2 Window Comparator Interrupt Occurs

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Page 0x02 Automatically pushed on stack in SFRPAGE on ADC2 interrupt 0x02 SFRPAGE (ADC2) SFRPAGE pushed to 0x0F SFRNEXT SFRNEXT (Port 5) SFRLAST Figure 11.6. SFR Page Stack After ADC2 Window Comparator Interrupt Occurs While in the ADC2 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the ADC2 interrupt is configured as a low priority interrupt. -

Page 140: Figure 11.7. Sfr Page Stack Upon Pca Interrupt Occurring During An Adc2 Isr

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Page 0x00 Automatically pushed on stack in SFRPAGE on PCA interrupt 0x00 SFRPAGE (PCA) SFRPAGE pushed to 0x02 SFRNEXT SFRNEXT (ADC2) SFRNEXT pushed to 0x0F SFRLAST SFRLAST (Port 5) Figure 11.7. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR On exit from the PCA interrupt service routine, the CIP-51 will return to the ADC2 Window Comparator ISR. -

Page 141: Figure 11.9. Sfr Page Stack Upon Return From Adc2 Window Interrupt

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 On the execution of the RETI instruction in the ADC2 Window Comparator ISR, the value in SFRPAGE register is overwritten with the contents of SFRNEXT. The CIP-51 may now access the Port 5 SFR bits as it did prior to the interrupts occurring. See Figure 11.9 below. SFR Page 0x02 Automatically popped off of the... -

Page 142: Sfr Definition 11.2. Sfrpgcn: Sfr Page Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.2. SFRPGCN: SFR Page Control Reset Value SFRPGEN 00000001 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0x96 SFR Page: Bits7–1: Reserved. Bit0: SFRPGEN: SFR Automatic Page Control Enable. Upon interrupt, the C8051 Core will vector to the specified interrupt service routine and auto- matically switch the SFR page to the corresponding peripheral or function’s SFR page. -

Page 143: Sfr Definition 11.4. Sfrnext: Sfr Next Register

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.4. SFRNEXT: SFR Next Register Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0x85 SFR Page: All Pages Bits7–0: SFR Page Stack Bits: SFR page context is retained upon interrupts/return from interrupts in a 3 byte SFR Page Stack: SFRPAGE is the first entry, SFRNEXT is the second, and SFR- LAST is the third entry. -

Page 144: Table 11.2. Special Function Register (Sfr) Memory Map

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.2. Special Function Register (SFR) Memory Map 0(8) 1(9) 2(A) 3(B) 4(C) 5(D) 6(E) 7(F) SPI0CN PCA0L PCA0H PCA0CPL0 PCA0CPH0 PCA0CPL1 PCA0CPH1 WDTCN (ALL PAGES) EIP1 EIP2 (ALL (ALL (ALL PAGES) PAGES) PAGES) ADC0CN PCA0CPL2 PCA0CPH2 PCA0CPL3 PCA0CPH3 PCA0CPL4 PCA0CPH4 RSTSRC ADC2CN PCA0CPL5... - Page 145 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.2. Special Function Register (SFR) Memory Map (Continued) SADEN0 AMX0CF AMX0SL ADC0CF ADC0L ADC0H (ALL AMX2CF AMX2SL ADC2CF ADC2 PAGES) FLSCL PSBANK (ALL (ALL PAGES) PAGES) FLACL SADDR0 (ALL PAGES) P1MDIN EMI0TC EMI0CN EMI0CF (ALL PAGES) CCH0CN CCH0TN CCH0LC P0MDOUT...

-

Page 146: Table 11.3. Special Function Registers

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.3. Special Function Registers SFRs are listed in alphabetical order. All undefined SFR locations are reserved. Register Address Description Page No. Page 0xE0 All Pages Accumulator page 153 ADC0CF 0xBC ADC0 Configuration page 62 , page 80 ADC0CN 0xE8 ADC0 Control... - Page 147 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.3. Special Function Registers (Continued) SFRs are listed in alphabetical order. All undefined SFR locations are reserved. Register Address Description Page No. Page EIE1 0xE6 All Pages Extended Interrupt Enable 1 page 159 EIE2 0xE7 All Pages Extended Interrupt Enable 2 page 160 EIP1 0xF6...

- Page 148 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.3. Special Function Registers (Continued) SFRs are listed in alphabetical order. All undefined SFR locations are reserved. Register Address Description Page No. Page 0xE8 Port 6 Latch page 256 P6MDOUT 0x9E Port 6 Output Mode Configuration page 256 0xF8 Port 7 Latch page 257...

- Page 149 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.3. Special Function Registers (Continued) SFRs are listed in alphabetical order. All undefined SFR locations are reserved. Register Address Description Page No. Page page 114 REF0CN 0xD1 Voltage Reference Control page 116 page 117 RSTSRC 0xEF Reset Source page 182 SADDR0 0xA9...

- Page 150 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.3. Special Function Registers (Continued) SFRs are listed in alphabetical order. All undefined SFR locations are reserved. Register Address Description Page No. Page TMR4L 0xCC Timer/Counter 4 Low Byte page 323 WDTCN 0xFF All Pages Watchdog Timer Control page 181 XBR0 0xE1...

-

Page 151: Register Descriptions

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.2.7. Register Descriptions Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic l. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. -

Page 152: Sfr Definition 11.9. Psw: Program Status Word

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.9. PSW: Program Status Word Reset Value PARITY 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0xD0 SFR Page: All Pages Bit7: CY: Carry Flag. This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow (subtraction). -

Page 153: Sfr Definition 11.10. Acc: Accumulator

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.10. ACC: Accumulator Reset Value ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0xE0 SFR Page: All Pages Bits7–0: ACC: Accumulator. This register is the accumulator for arithmetic operations. SFR Definition 11.11. -

Page 154: Interrupt Handler

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.3. Interrupt Handler The CIP-51 includes an extended interrupt system supporting a total of 20 interrupt sources with two prior- ity levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt- pending flag(s) located in an SFR. -

Page 155: External Interrupts

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.3.2. External Interrupts Two of the external interrupt sources (/INT0 and /INT1) are configurable as active-low level-sensitive or active-low edge-sensitive inputs depending on the setting of bits IT0 (TCON.0) and IT1 (TCON.2). IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flag for the /INT0 and /INT1 external interrupts, respectively. -

Page 156: Interrupt Priorities

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 11.4. Interrupt Summary (Continued) Interru Priority Enable Priority Interrupt Source Pending Flags Order Flag Control Vector ECP1R PCP1F Comparator 1 Rising Edge 0x006B CP1RIF (CPT1CN.5) (EIE1.7) (EIP1.7) TF3 (TMR3CN.7) Timer 3 0x0073 EXF3 (TMR3CN.6) (EIE2.0) (EIP2.0) EADC0 PADC0 ADC0 End of Conversion 0x007B... -

Page 157: Interrupt Register Descriptions

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.3.5. Interrupt Register Descriptions The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s). SFR Definition 11.12. -

Page 158: Sfr Definition 11.13. Ip: Interrupt Priority

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.13. IP: Interrupt Priority Reset Value 11000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0xB8 SFR Page: All Pages Bits7–6: UNUSED. Read = 11b, Write = don't care. Bit5: PT2: Timer 2 Interrupt Priority Control. This bit sets the priority of the Timer 2 interrupt. -

Page 159: Sfr Definition 11.14. Eie1: Extended Interrupt Enable 1

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.14. EIE1: Extended Interrupt Enable 1 Reset Value ECP1R ECP1F ECP0R ECP0F EPCA0 EWADC0 ESMB0 ESPI0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xE6 SFR Page: All Pages Bit7: ECP1R: Enable Comparator1 (CP1) Rising Edge Interrupt. This bit sets the masking of the CP1 rising edge interrupt. -

Page 160: Sfr Definition 11.15. Eie2: Extended Interrupt Enable 2

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.15. EIE2: Extended Interrupt Enable 2 Reset Value EADC2 EWADC2 EADC0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xE7 SFR Page: All Pages Bit7: UNUSED. Read = 0b, Write = don't care. Bit6: ES1: Enable UART1 Interrupt. -

Page 161: Sfr Definition 11.16. Eip1: Extended Interrupt Priority 1

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.16. EIP1: Extended Interrupt Priority 1 Reset Value PCP1R PCP1F PCP0R PCP0F PPCA0 PWADC0 PSMB0 PSPI0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xF6 SFR Page: All Pages Bit7: PCP1R: Comparator1 (CP1) Rising Interrupt Priority Control. This bit sets the priority of the CP1 interrupt. -

Page 162: Sfr Definition 11.17. Eip2: Extended Interrupt Priority 2

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 11.17. EIP2: Extended Interrupt Priority 2 Reset Value PADC2 PWADC2 PADC0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xF7 SFR Page: All Pages Bit7: UNUSED. Read = 0b, Write = don't care. Bit6: ES1: UART1 Interrupt Priority Control. -

Page 163: Power Management Modes

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.4. Power Management Modes The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the external peripherals and internal clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the system clock is stopped. -

Page 164: Stop Mode

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 11.4.2. Stop Mode Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruc- tion that sets the bit completes. In Stop mode, the CPU and oscillators are stopped, effectively shutting down all digital peripherals. -

Page 165: Multiply And Accumulate (Mac0)

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12. Multiply And Accumulate (MAC0) The C8051F120/1/2/3 and C8051F130/1/2/3 devices include a multiply and accumulate engine which can be used to speed up many mathematical operations. MAC0 contains a 16-by-16 bit multiplier and a 40-bit adder, which can perform integer or fractional multiply-accumulate and multiply operations on signed input values in two SYSCLK cycles. -

Page 166: Integer And Fractional Math

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12.2. Integer and Fractional Math MAC0 is capable of interpreting the 16-bit inputs stored in MAC0A and MAC0B as signed integers or as signed fractional numbers. When the MAC0FM bit (MAC0CF.1) is cleared to ‘0’, the inputs are treated as 16-bit, 2’s complement, integer values. -

Page 167: Operating In Multiply And Accumulate Mode

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12.3. Operating in Multiply and Accumulate Mode MAC0 operates in Multiply and Accumulate (MAC) mode when the MAC0MS bit (MAC0CF.0) is cleared to ‘0’. When operating in MAC mode, MAC0 performs a 16-by-16 bit multiply on the contents of the MAC0A and MAC0B registers, and adds the result to the contents of the 40-bit MAC0 accumulator. -

Page 168: Rounding And Saturation

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12.6. Rounding and Saturation A Rounding Engine is included, which can be used to provide a rounded result when operating on frac- tional numbers. MAC0 uses an unbiased rounding algorithm to round the data stored in bits 31 – 16 of the accumulator, as shown in Table 12.1. -

Page 169: Multiply Only Example

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 12.7.2. Multiply Only Example The example below implements the equation: × 4660 – – 1360720 MAC0CF, #01h ; Use integer numbers, and multiply only mode (add to zero) MAC0AH, #12h ; Load MAC0A register with 1234 hex = 4660 decimal MAC0AL, #34h MAC0BH, #FEh ;... -

Page 170: Sfr Definition 12.1. Mac0Cf: Mac0 Configuration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.1. MAC0CF: MAC0 Configuration Reset Value MAC0SC MAC0SD MAC0CA MAC0SAT MAC0FM MAC0MS 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xC3 SFR Page: 3 Bits 7 – 6: UNUSED: Read = 00b, Write = don’t care. Bit 5: MAC0SC: Accumulator Shift Control. -

Page 171: Sfr Definition 12.2. Mac0Sta: Mac0 Status

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.2. MAC0STA: MAC0 Status Reset Value MAC0HO MAC0Z MAC0SO MAC0N 00000100 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0xC0 SFR Page: 3 Bits 7 – 4: UNUSED: Read = 0000b, Write = don’t care. Bit 3: MAC0HO: Hard Overflow Flag. -

Page 172: Sfr Definition 12.4. Mac0Al: Mac0 A Low Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.4. MAC0AL: MAC0 A Low Byte Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xC1 SFR Page: 3 Bits 7 – 0: Low Byte (bits 7 – 0) of MAC0 A Register. SFR Definition 12.5. -

Page 173: Sfr Definition 12.7. Mac0Acc3: Mac0 Accumulator Byte 3

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.7. MAC0ACC3: MAC0 Accumulator Byte 3 Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0x96 SFR Page: 3 Bits 7 – 0: Byte 3 (bits 31 – 24) of MAC0 Accumulator. *Note: The contents of this register should not be changed by software during the first two MAC0 pipeline stages. -

Page 174: Sfr Definition 12.10. Mac0Acc0: Mac0 Accumulator Byte 0

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.10. MAC0ACC0: MAC0 Accumulator Byte 0 Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0x93 SFR Page: 3 Bits 7 – 0: Byte 0 (bits 7 – 0) of MAC0 Accumulator. *Note: The contents of this register should not be changed by software during the first two MAC0 pipeline stages. -

Page 175: Sfr Definition 12.13. Mac0Rndl: Mac0 Rounding Register Low Byte

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 12.13. MAC0RNDL: MAC0 Rounding Register Low Byte Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xCE SFR Page: 3 Bits 7 – 0: Low Byte (bits 7 – 0) of MAC0 Rounding Register. Rev. - Page 176 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Rev. 1.4...

-

Page 177: Reset Sources

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 13. Reset Sources Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur: • CIP-51 halts program execution. • Special Function Registers (SFRs) are initialized to their defined reset values. •... -

Page 178: Power-On Reset

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 13.1. Power-on Reset The C8051F120/1/2/3/4/5/6/7 family incorporates a power supply monitor that holds the MCU in the reset state until V rises above the V level during power-up. See Figure 13.2 for timing diagram, and refer to Table 13.1 for the Electrical Characteristics of the power supply monitor circuit. The RST pin is asserted low until the end of the 100 ms V Monitor timeout in order to allow the V supply to stabilize. -

Page 179: External Reset

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 13.3. External Reset The external RST pin provides a means for external circuitry to force the MCU into a reset state. Asserting the RST pin low will cause the MCU to enter the reset state. It may be desirable to provide an external pul- lup and/or decoupling of the RST pin to avoid erroneous noise-induced resets. -

Page 180: Enable/Reset Wdt

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in SFR Definition 13.1. 13.7.1. Enable/Reset WDT The watchdog timer is both enabled and reset by writing 0xA5 to the WDTCN register. -

Page 181: Sfr Definition 13.1. Wdtcn: Watchdog Timer Control

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 13.1. WDTCN: Watchdog Timer Control Reset Value xxxxx111 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xFF SFR Page: All Pages Bits7 – 0: WDT Control Writing 0xA5 both enables and reloads the WDT. Writing 0xDE followed within 4 system clocks by 0xAD disables the WDT. -

Page 182: Sfr Definition 13.2. Rstsrc: Reset Source

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 13.2. RSTSRC: Reset Source Reset Value CNVRSEF C0RSEF SWRSEF WDTRSF MCDRSF PORSF PINRSF 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0xEF SFR Page: Bit7: Reserved. Bit6: CNVRSEF: Convert Start 0 Reset Source Enable and Flag Write: 0: CNVSTR0 is not a reset source. -

Page 183: Table 13.1. Reset Electrical Characteristics

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Table 13.1. Reset Electrical Characteristics –40 to +85 °C unless otherwise specified. Parameter Conditions Units = 8.5 mA, V = 2.7 to 3.6 V RST Output Low Voltage — — 0.7 x V RST Input High Voltage — —... - Page 184 C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 OTES Rev. 1.4...

-

Page 185: Oscillators

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 14. Oscillators The devices include a programmable internal oscillator and an external oscillator drive circuit. The internal oscillator can be enabled, disabled, and calibrated using the OSCICN and OSCICL registers, as shown in Figure 14.1. The system clock can be sourced by the external oscillator circuit, the internal oscillator, or the on-chip phase-locked loop (PLL). -

Page 186: Sfr Definition 14.1. Oscicl: Internal Oscillator Calibration

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 Electrical specifications for the precision internal oscillator are given in Table 14.1. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. SFR Definition 14.1. -

Page 187: External Oscillator Drive Circuit

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 14.2. External Oscillator Drive Circuit The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/ resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 14.1. -

Page 188: Sfr Definition 14.3. Clksel: System Clock Selection

C8051F120/1/2/3/4/5/6/7 C8051F130/1/2/3 SFR Definition 14.3. CLKSEL: System Clock Selection Reset Value CLKDIV1 CLKDIV0 CLKSL1 CLKSL0 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: 0x97 SFR Page: Bits 7–6: Reserved. Bits 5–4: CLKDIV1–0: Output SYSCLK Divide Factor. These bits can be used to pre-divide SYSCLK before it is output to a port pin through the crossbar. -

Page 189: Sfr Definition 14.4. Oscxcn: External Oscillator Control