Subscribe to Our Youtube Channel

Summary of Contents for Realtek Ameba-D RTL872 D Series

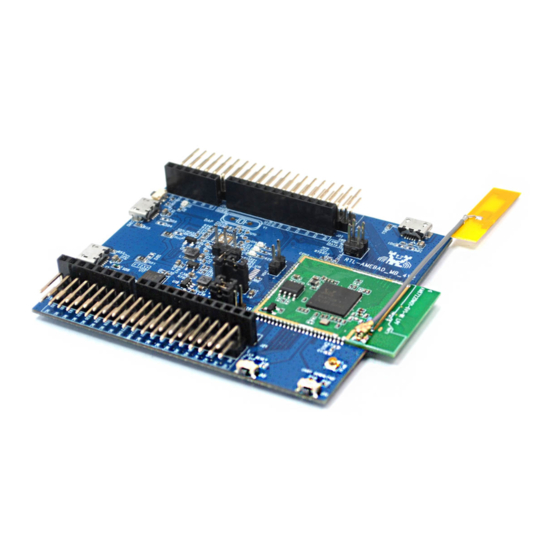

- Page 1 UM0400 Ameba-D User Manual Realtek Semiconductor Corp. No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211. Fax: +886-3-577-6047 www.realtek.com...

- Page 2 Realtek products, reference designs or services are used. Information published by Realtek regarding third party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the Realtek’s reference designs or other items may require a license from a third party under the patents or other intellectual property of the third party, or a license from Realtek under the patents or other intellectual property of Realtek.

- Page 3 Ameba-D User Manual TRADEMARKS Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners. USING THIS DOCUMENT Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide.

-

Page 4: Table Of Contents

ISER0 and ISER1 ................................39 4.4.2 ICER0 and ICER1 ................................40 4.4.3 ISPR0 and ISPR1 ................................40 4.4.4 ICPR0 and ICPR1 ................................40 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 5 Data and Control Flow ..............................59 8.2.2 Interrupts ..................................61 Registers ....................................69 8.3.1 Bus Interface ................................. 69 8.3.2 Register Memory Map ..............................70 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 6 Functional Description ..............................196 10.3 PWM Mode Timer ................................198 10.3.1 Introduction ................................198 10.3.2 Features ..................................198 10.3.3 Block Diagram ................................199 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 7 C) Interface ........................... 245 13.1 Introduction ................................... 245 13.2 Functional Description ..............................245 13.2.1 Overview ..................................245 13.2.2 C Terminology ................................246 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 8 Infrared Radiation (IR) ..............................302 15.1 Overall Description ................................ 302 15.1.1 Introduction ................................302 15.1.2 Features ..................................303 15.2 Architecture ................................... 303 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 9 Audio Output ................................333 17.5.2 Audio Input ................................. 334 17.6 Registers ..................................337 17.6.1 Analog Part ................................. 337 17.6.2 Digital Part.................................. 341 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 10 RGB DMA Auto-mode ..............................451 20.4.2 MCU DMA Trigger-mode ............................452 20.4.3 MCU I/O Mode ................................452 Quadrature Decoder (Q-Decoder) ..........................453 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 11 22.5.10 Rx Page Own Bit Register (IS_RX_PAGE_OWNx) ....................489 22.5.11 Version ID (IS_VERSION_ID) ............................ 489 Abbreviations ..................................490 Revision History..................................494 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 12: List Of Tables

Fig 9-21 Channel FIFO contents at times indicated in Fig 9-20 ......................106 Fig 9-22 Breakdown of block transfer where max_abrst = 2, Case 2 ....................107 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 13 Fig 10-13 Counter timing diagram, update event when ARPE=1 (TIMx_ARR preloaded) ............... 204 Fig 10-14 Edge-aligned PWM waveforms (ARR=8, CCxP=0) ......................205 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 14 Fig 16-9 Shadow key condition ................................ 320 Fig 16-10 Correct three-key condition ............................. 321 Fig 17-1 Audio codec diagram ................................329 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 15 Fig 20-20 RGB I/F 16-bit output ............................... 430 Fig 20-21 LED interface ..................................431 Fig 20-22 LED control timing ................................432 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 16 Fig 22-18 FIFO allocation of 5.1 channel (sample bit = 24-bit) ......................482 Fig 22-19 FIFO allocation of 5.1 channel (sample bit = 32-bit) ......................482 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 17: List Of Figures

Fig 9-21 Channel FIFO contents at times indicated in Fig 9-20 ......................106 Fig 9-22 Breakdown of block transfer where max_abrst = 2, Case 2 ....................107 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 18 Fig 10-13 Counter timing diagram, update event when ARPE=1 (TIMx_ARR preloaded) ............... 204 Fig 10-14 Edge-aligned PWM waveforms (ARR=8, CCxP=0) ......................205 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 19 Fig 16-9 Shadow key condition ................................ 320 Fig 16-10 Correct three-key condition ............................. 321 Fig 17-1 Audio codec diagram ................................329 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 20 Fig 20-20 RGB I/F 16-bit output ............................... 430 Fig 20-21 LED interface ..................................431 Fig 20-22 LED control timing ................................432 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 21 Fig 22-18 FIFO allocation of 5.1 channel (sample bit = 24-bit) ......................482 Fig 22-19 FIFO allocation of 5.1 channel (sample bit = 32-bit) ......................482 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 22: Conventions

Hardware will automatically clear to 0 when software has written to this bit. Used for the reserved bit which should not be concerned by users. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 23: Product Overview

KM0 CPU SGPIO (One Wire Communication) HS_TIM x4 @ 32KHz RSIP (Flash Decryption) HS_WDT Low Power Peripherals Timer Fig 1-1 System architecture User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 24 CPU and the DMA controller, and also for peripherals on the asynchronous bridge to have a fixed clock that doesn't track the system clock. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 25: Memory Organization

IDAU 0x0200_0000 0x07FF_FFFF 96MB HS_SYSON Non-Secure 0x4000_0000 0x4000_0FFF Secure 0x5000_0000 0x5000_0FFF HS_TIM0 ~ 3/4/5 Non-Secure 0x4000_2000 0x4000_2FFF HS_UART0 Non-Secure 0x4000_4000 0x4000_4FFF User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 26: Km0 Memory Map And Register Boundary Addresses

RXI300_KM0 0x4801_8000 0x4801_8FFF SGPIO 0x4801_A000 0x4801_AFFF Cap-Touch/ADC/Comparator 0x4801_C000 0x4801_CFFF Q-Decoder 0x4801_E000 0x4801_EFFF Flash Controller 0x4808_0000 0x4808_0FFF Flash Memory 0x0800_0000 0x0FFF_FFFF 128MB User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 27: Km4 Embedded Sram

It accelerates code execution with a system of instruction prefetch and cache lines. PSRAM 4MB 8IO DDR PSRAM is included in Ameba-D, up to 50MHz DDR. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 28: Memory Protection Unit (Mpu)

Privileged access is permitted only. Unprivileged access generates a BusFault. This register is word accessible only. Half-word and byte accesses are unpredictable. Configurations: This register is always implemented. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 29: Mpu_Ctrl

MPU enabled or disabled. This applies to HardFaults, NMIs, and exception handlers when FAULTMASK is set to 1. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 30: Mpu_Rnr

Preface: This register provides access to the configuration of the MPU region selected by MPU_RNR.REGION for the appropriate security state. The field description applies to the currently selected region. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 31: Mpu_Rlar

Enable. Region enable. 0: Region is disabled. 1: Region is enabled. This bit resets to 0 on a Warm reset. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 32: Mpu_Rbar_A

This register is word accessible only. Half-word and byte accesses are unpredictable. Configurations: Present only if the Main Extension is implemented. Reserved if the Main Extension is not implemented. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 33: Mpu_Mair0

This field resets to an unknown value on a Warm reset. 23:16 ATTR2 Memory attributes encoding for MPU regions with an AttrIndx of 2. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 34: Mpu_Mair1

Purpose: Defines the memory attribute encoding for use in the MPU_MAIR0 and MPU_MAIR1 register. Usage constraints: None. Configurations: All. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 35: Outer

11RW: Normal memory, Inner Write-Back Non-transient. Note: R and W specify the outer read and write allocation policy. 0: Don’t allocate 1: Allocate User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 36: Nested Vectored Interrupt Controller (Nvic)

Do not call RTOS _ISR functions from any interrupt that has a higher priority than this macro. Table 4-1 NVIC table User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 37 KM0 LGDMA0_Channel0 interrupt LGDMA0_Channel1 KM4 USB interrupt KM0 LGDMA0_Channel1 interrupt SDIO_DEV LGDMA0_Channel2 KM4 SDIO_DEV interrupt KM0 LGDMA0_Channel2 interrupt User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 38: Nvic Register Description

This register allows disabling interrupts and reading back the interrupt enabled state for peripheral functions. ICER1 0x184 Interrupt Clear Enable Register 1. See ICER0 description. ISPR0 0x200 Interrupt Set Pending Register 0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 39: Iser0 And Iser1

Write: Writing 0 has no effect, writing 1 enables the interrupt. Read: 0 indicates that the interrupt is disabled, 1 indicates that the interrupt is enabled. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 40: Icer0 And Icer1

The interrupt number to be programmed in the STIR register is listed in Table 4-3. Table 4-3 Software trigger interrupt register Address Offset Name Description User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 41 Reserved. Read value is undefined, only 0 should be written. INTID Writing a value to this field generates an interrupt for the specified interrupt number. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 42: Cpu System Tick (Systick) Timer

This register contains control information for the SysTick timer and provides a status flag. It is a part of the CPU, and determines the clock source for the SysTick timer. … COUNTFLAG RSVD User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 43: Syst_Rvr

This register returns the current count from the SysTick counter when it is read by software. … … CURRENT RSVD Name Access Reset Description 31:24 RSVD Reserved. Read value is undefined, only zero should be written. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 44: Syst_Calib

23:0 TENMS This field is loaded 0 from the SYST_CALIB register in SYSCON, and always RAZ/WI (read as zero, write ignored). User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 45: Pad Control And Pinmux

Fig 6-1 Pad diagram 6.2.1 Pad Types The pad types of Ameba-D are listed in Table 6-1. Table 6-1 Pad types User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 46: Pad Pull Resistor Control

PUPDC = x and PU = 0 and PD = 0 No pull PUPDC = 0 and PU = 1 10k pull-up PUPDC = 1 and PU = 1 4.7k pull-up User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 47: Pad Schmitt Trigger

When audio function is not used, it is necessary to set AVCC to 3V above and use these pins as normal GPIO, as Table 6-5 shows. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 48: Pin Multiplexing Function

Each I/O pin has a multiplexer with up to 32 alternate function inputs (AF0 to AF31) that can be configured through the PADCTRL register. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 49: Register − Padctrl

Each I/O pin has one PADCTRL register assigned to control the pin’s electrical characteristics. RSVD RSVD PAD_BIT_SHUT_ PAD_BIT_SDIO_ PAD_BIT_SCHMI PAD_BIT_PULL_DO PAD_BIT_PULL_UP PAD_BIT_DRIVING_STRENGTH DOWN H3L1 RSVD TT_TRIGGER_EN WN_RESISTOR_EN _RESISTOR_EN PAD_BIT_FUNCTION_ID RSVD Address Name Access Description User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 50 Controls “PD” signal, pull-down resistor enable, resister is 50kohm. PAD_BIT_PULL_UP_RESISTOR_EN Controls “PU” signal, pull-up resistor enable, resister is 50kohm. RSVD Reserved for function ID extension PAD_BIT_FUNCTION_ID Function ID User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 51: Inter Processor Communication (Ipc)

IPC1_ISR register, the KM0 CPU is acknowledged by writing a ‘1’ to bit[2] of the IPC1_ICR register, which in turn, clears bit[2] of the IPC1_ISR register, enables KM4 to send another message. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 52: Hardware Semaphore

KM4 writes a ‘1’ to IPC0_SEM[0], hardware helps to clear the CPUID and ‘Free’ bit, so that another CPU can get this semaphore if needed. you can give interrupt (IPCx_IRR) to peer CPU for the semaphore free. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 53: Ipc Registers

IPC_IERx Writing a ‘1’ to a bit of this register enables the corresponding interrupt. Writing a ‘0’ has no effect. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 54: Ipcx_Idr

IPC_ICRx Writing a ‘1’ to a bit of this register clears the corresponding interrupt. Writing a ‘0’ has no effect. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 55: Ipc0_Cpuid

Refer to the description of the IPC_SEM_CPUID0 bit. IPC_SEM_FREEF Refer to the description of the IPC_SEM_FREE0 bit. IPC_SEM_CPUIDE Refer to the description of the IPC_SEM_CPUID0 bit. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 56: Ipcx_Ier_R

Access Default Description 31:0 IPC_IERx_R 1: Interrupt is enabled for this bit. 0: Interrupt is disabled for this bit. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 57: Ipc_Usr

These are user-defined register, and can be used for H2L/L2H command defined by user. … User-defined Name Access Default Description 31:0 User-defined These registers can be used for H2L/L2H command defined by user. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 58: General Purpose Input/Output (Gpio)

Configurable reset values on output signals Configurable synchronization of interrupt signals Functional Description This chapter describes the functional operation of the GPIO. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 59: Data And Control Flow

When a signal is configured for software control, the data and direction control for the signal are sourced from the data register (gpio_swportx_dr) and direction control register (gpio_swportx_ddr), where x is a. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 60 APB. The assumption is that the APB bridge does not lose ownership of the AHB during consecutive accesses when PCLK=HCLK. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 61: Interrupts

Fig 8-4 illustrates how the interrupts are generated and how the data flows. The signal names in the diagram correspond to either I/O signals or memory-mapped registers. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 62: Fig 8-4 Interrupt Rtl Block Diagram

Fig 8-5 Debounce RTL diagram User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 63: Fig 8-6 Debounce Timing With Asynchronous Reset Flip-Flops

Single Edge Fig 8-7 shows an RTL diagram of the synchronization and edge detection of interrupt sources on gpio_ext_portaN signals, when GPIO_INT_BOTH_EDGE=0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 64: Fig 8-7 Synchronization And Edge Detect Interrupt Generation When Gpio_Int_Both_Edge=0

It also shows how an interrupt is cleared by a write to the interrupt clear register. Fig 8-8 Interrupt edge detection and interrupt clear timing when GPIO_SYNC_PA_INTERRPUTS = 1 (metastability included) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 65: Fig 8-9 Interrupt Edge Detection And Interrupt Clear Timing When Gpio_Sync_Pa_Interrputs = 0 (Metastability Removed)

In this example, the write to the interrupt clear register does not clear the second interrupt, and the gpio_intr{_n} signal is not de-asserted. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 66: Fig 8-10 Write To Interrupt Clear Register, Coincident With Detection Of New Interrupt

Fig 8-11 shows the synchronization and edge detect interrupt generation of the interrupt sources on gpio_ext_portaN signals when GPIO_INT_BOTH_EDGE = 1. Fig 8-11 Synchronization and edge detect interrupt generation when GPIO_INT_BOTH_EDGE=0 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 67: Fig 8-12 Interrupt Edge Detection And Interrupt Clear Timing When Gpio_Sync_Pa_Interrputs = 1 And Gpio_Int_Both_Edge=1 (Metastability Included)

(metastability included) Fig 8-13 shows a timing diagram similar to Fig 8-12, except that in this scenario, metastability registers are removed. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 68: Fig 8-13 Interrupt Edge Detection And Interrupt Clear Timing When Gpio_Sync_Pa_Interrputs = 0 And

Fig 8-14 shows the generation of level-sensitive interrupts. As for edge-detect interrupts, the user can configure GPIO with or without debounce logic. Fig 8-14 Level-sensitive interrupt RTL diagram User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 69: Registers

Fig 8-16 shows the read/write busses between the APB and the APB slave. Fig 8-16 Relationship between APB and APB slave data widths User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 70: Register Memory Map

Interrupt mask register Width: GPIO_PWIDTH_A Reset Value: 0x0 gpio_inttype_level 0x38 Interrupt level register Width: GPIO_PWIDTH_A Reset Value: 0x0 gpio_int_polarity 0x3c Interrupt polarity register User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 71: Register And Field Descriptions

The following sections contain the memory diagrams and field descriptions for the individual registers. 8.3.3.1 gpio_swporta_dr Name: Port A Data Register Size: GPIO_PWIDTH_A Address offset: 0x00 Read/write access: read/write User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 72 The default source is configurable 0:GPIO_PWIDTH_A-1 through the GPIO_DFLT_SRC_A configuration parameter. (See above) 0 – Software mode (default) 1 – Hardware mode User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 73 GPIO_DFLT_DIR_B parameter. 0 – Input (default) 1 – Output Reset Value: GPIO_DFLT_DIR_B 8.3.3.6 gpio_swportb_ctl Name: Port B Data Source Size: User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 74 Reset Value: GPIO_SWPORTC_RESET 8.3.3.8 gpio_swportc_ddr Name: Port C Data Direction Size: GPIO_PWIDTH_C Address offset: 0x1C Read/write access: read/write User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 75 {GPIO_PWIDTH_C{GPIO_DFLT_SRC_C in each bit}}. 8.3.3.10 gpio_swportd_dr Name: Port D Data Register Size: GPIO_PWIDTH_D Address offset: 0x24 Read/write access: read/write User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 76 1 bit wide if GPIO_PORTD_SINGLE_CTL = 1 GPIO_PWIDTH_D bits wide if GPIO_PORTD_SINGLE_CTL = 0 Address offset: 0x2C Read/write access: read/write Name Access Description User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 77 Read/write access: read/write This register is available only if Port A is configured to generate interrupts (GPIO_PORTA_INTR = Include (1)). User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 78 Port A. Whenever a 0 is written to a bit of this register, it configures the interrupt type to falling-edge or active-low sensitive; otherwise, it is rising-edge or active-high sensitive. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 79 This register is available only if Port A is configured to generate interrupts (GPIO_PORTA_INTR = Include (1)) and when the debounce logic is included (GPIO_DEBOUNCE = Include (1)). User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 80 Name: External Port A Size: GPIO_PWIDTH_A Address offset: 0x50 Read/write access: read Name Access Description 31:GPIO_PWIDTH_A Reserved Read as zero Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 81 Name: External Port D Size: GPIO_PWIDTH_D Address offset: 0x5C Read/write access: read Name Access Description 31:GPIO_PWIDTH_D Reserved Read as zero Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 82 This register is available only if Port A is configured to generate interrupts (GPIO_PORTA_INTR = Include (1)) and interrupt detection is configured to generate on both rising and falling edges of external input signal (GPIO_INT_BOTH_EDGE=Include (1)). Interrupt bothedge User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 83 The value of this register is derived from the GPIO_ID configuration parameter. 0 = Exclude 1 = Include ADD_ENCODED_PARAMS The value of this register is derived from the GPIO_ADD_ENCODED_PARAMS configuration parameter. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 84 The value of this register is derived from the GPIO_APB_DATA_WIDTH configuration parameter. 0x0 = 8 bits 0x1 = 16 bits 0x2 = 32 bits 0x3 = Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 85: Programming The Gpio

When reading back registers that are no longer present due to configuration parameters settings, then 0 is read back. For example, if APB_DATA_WITDH = 32 bits and GPIO_PWIDTH_A = 8, then the top 24 bits read back 0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 86: Direct Memory Access Controller (Dmac)

B is handled by the DMAC. The channel source and destination arbitrate independently for the AHB master interface, along with other channels. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 87: Fig 9-2 Peripheral-To-Peripheral Dma Transfer On The Same Ahb Layer

DMA transfer between a source and destination on different AHB layers. Peripheral B uses a hardware handshaking interface. The memory does not use any handshaking interface to the DMAC in order to initiate DMA transfers. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 88: Basic Definitions

This interface is used to request, User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 89: Fig 9-4 Dma Transfer Hierarchy For Non-Memory Peripherals

Note: For memory peripherals, there is no DMA Transaction Level. Fig 9-4 DMA Transfer Hierarchy for Non-Memory Peripherals Fig 9-5 DMA transfer hierarchy for memory User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 90: Features

Up to eight channels, one per source and destination pair Unidirectional channels – data transfers in one direction only User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 91 Handshaking interfaces for source and destination peripherals (up to16) Hardware handshaking interface (software handshaking interface not supported) Peripheral interrupt handshaking interface User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 92: Functional Description

DMAC Memory to Peripheral DMAC Memory to Peripheral Peripheral Peripheral to Memory DMAC Peripheral to Memory Peripheral Peripheral to Peripheral DMAC User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 93: Handshaking Interface

(block size) of source transfer width (CTLx.SRC_TR_WIDTH) to be transferred by the DMAC in a block transfer; this is programmed into the CTLx.BLOCK_TS field. Therefore, the total number of bytes to be transferred in a block is: User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 94: Memory Peripherals

If: blk_size_bytes/src_burst_size_bytes = integer then the source never enters this region, and the source block uses only burst transactions. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 95 Fig 9-6 illustrates the hardware handshaking interface between a peripheral – whether a destination or source – and the DMAC when the peripheral is not the flow controller. Fig 9-6 Hardware handshaking interface User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 96: Fig 9-7 Burst Transaction - Pclk = Hclk

Single Transaction Region, and therefore the DMAC does not sample dma_single[0]. The handshaking loop is as follows: Fig 9-7 Burst transaction – pclk = hclk User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 97 The dma_req signal should be de-asserted when dma_ack is asserted, even if the condition that generates dma_req in the peripheral is True. Fig 9-9 shows a single transaction that occurs in the Single Transaction Region. The handshaking loop is as follows: User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 98: Fig 9-10 Burst Followed By Back-To-Back Single Transactions

In Fig 9-11, an active level on dma_req[0] after time T4 takes precedence over the active level on dma_single[0] after time T3. Fig 9-11 Early-Terminated burst transaction User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 99: Fig 9-12 Burst Transaction Ignored During Active Single Transaction

13 is asserted when the destination FIFO has at least one free location. The burst_flag signal in Fig 9-13 is asserted when the destination FIFO contains free locations greater than or equal to some watermark-level number. Fig 9-13 Generation of dma_req and dma_single by source User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 100: Handshaking Interface - Peripheral Is Flow Controller

Fig 9-14 shows the hardware handshaking interface between a destination or source peripheral and the DMAC when the peripheral is the flow controller. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 101: Fig 9-15 Burst Transaction Followed By Single Transaction That Terminates Block

Fig 9-15 Burst transaction followed by single transaction that terminates block User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 102: Setting Up Transfers

Source burst transaction length CTLx.DEST_MSIZE Destination burst transaction length CFGx.MAX_ABRST Maximum AMBA burst length CFGx.FIFO_MODE FIFO mode select CFGx.FCMODE Flow-control mode User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 103 4 from the source, interleaved with three bursts, again of length 4, to the destination. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 104: Fig 9-17 Breakdown Of Block Transfer

With the DMAH_CHx_FIFO_DEPTH parameter set to 8 bytes instead of 16 bytes, the block transfer would look like that shown in Fig 9-19. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 105 Scenario: Effect of the maximum AMBA burst length, CFGx. MAX_ABRST. If the CFGx. MAX_ABRST = 2 parameter and all other parameters are left unchanged from Example 1, Table 9-5, then the block transfer would look like that shown in Fig 9-20. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 106 FIFO locations are redundant for this block transfer. However, this is not the general case. The block transfer could proceed as indicated in Fig 9-22. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 107 Early-Terminated Burst Transaction. Table 9-6 lists the parameters used in this example. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 108: Fig 9-24 Breakdown Of Block Transfer

Fig 9-24 Breakdown of block transfer Fig 9-25 shows the status of the source FIFO at various times throughout the source block transfer. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 109: Fig 9-26 Source Fifo Contents Where Watermark Level Is Dynamically Adjusted

Under the same conditions, it is possible for software to complete a source block transfer without initiating single transactions from the source. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 110: Fig 9-27 Block Transfer To Destination

12 - 8) left to transfer in the destination block. However, CTLx.DST_TR_WIDTH implies 64-bit AHB transfers to the destination (dst_single_size_bytes = 8 byte); therefore, the DMAC cannot form a single word of the specified CTLx.DST_TR_WIDTH. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 111 32 bits CTLx.DST_TR_WIDTH = 3’b010 32 bits CTLx.SRC_MSIZE = 3’b010 Decode value = 8 CTLx.DEST_MSIZE = 3’b001 Decode value = 4 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 112: Fig 9-28 Block Transfer Up To Time 'T4

At time ‘t4’, a source burst transaction is requested, and the DMAC attempts a burst of length 4. Suppose that this burst is early-burst terminated after three AHB transfers. The FIFO status after this burst might look like that shown in Fig 9-30. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 113: Fig 9-30 Fifo Status After Early-Terminated Burst

Table 9-9 Parameters in transfer operation – Example 7 Parameter Description CTLx.TT_FC = 3’b111 Peripheral-to-peripheral transfer with DMAC as flow controller CTLx.BLOCK_TS = x – User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 114: Fig 9-31 Data Loss When Pre-Fetching Is Enabled

Consider the block transfer shown in Fig 9-31, where the destination is the flow controller and data pre-fetching is enabled (CFGx.FCMODE = 0). Fig 9-31 Data loss when pre-fetching is enabled User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 115: Fig 9-32 Timing Exception On Dma_Finish To Source Peripheral

FIFO that are effectively lost. Case 2a – Data pre-fetching enabled but no data loss. Source enters Single Transaction Region when destination signals last transaction User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 116: Fig 9-33 Case Of No Data Loss When Pre-Fetching Is Enabled

Therefore, the source enters the Single Transaction Region at time T6. At time T7, the DMAC samples that dma_single[0] from the source peripheral is asserted and initiates a single transaction. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 117 T1 and completes this burst request at time T4. Fig 9-35 Case where source does not enter single transaction region when destination asserts dma_last[1] User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 118 CTLx.DST_TR_WIDTH = 3’b010 32 bits CTLx.TT_FC = 3’b111 Peripheral to Peripheral transfer with destination as flow controller DMAH_CHx_FIFO_DEPTH = 32 bytes – User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 119: Fig 9-36 Data Loss When Data Pre-Fetching Is Disabled

All other interface signals are ignored. This interface can be used where the slave peripheral does not have hardware handshaking signals. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 120: Flow Control Configurations

Fig 9-38 indicates five different flow control configurations using hardware handshaking interfaces – a simplified version of the interface is shown. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 121: Peripheral Burst Transaction Requests

For demonstration purposes, a receive SSI is used as a source peripheral, and a transmit SSI is used as a destination peripheral. Note: Throughout this section, SSI-related parameters are prefixed with “SSI”. DMAC-related parameters are prefixed with “DMA”. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 122 FIFO. This occurs because the DMAC has not had time to service the DMAC request before the SSI transmit FIFO becomes empty. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 123 Therefore, for optimal operation, DMA.CTLx.DEST_MSIZE should be set at the FIFO level that triggers a transmit DMAC request; that is: DMA.CTLx.DEST_MSIZE = SSI_TX_FIFO_DEPTH - SSI.DMATDLR (14) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 124: Fig 9-41 Ssi Receive Fifo

Note: The SSI receive FIFO is not empty at the end of the source burst transaction if the SSI has successfully received one data item or more on the SSI serial receive line before the end of the burst, as illustrated in Fig 9-41. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 125: Generating Requests For The Ahb Master Bus Interface

There is no handshaking mechanism employed between a memory peripheral and the DMAC. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 126 The destination is on the same AHB layer, but the channel is not currently in the middle of a transaction to the destination peripheral. The same rules apply when an end-of-destination transaction is signalled. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 127: Arbitration For Ahb Master Interface

AHB bus, then AHB transfers can proceed between the peripheral and DMAC. Fig 9-42 illustrates the arbitration flow of the master bus interface. Fig 9-42 Arbitration flow for master bus interface User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 128: Scatter/Gather

(SGRx.SGC) and destination scatter count (DSC), respectively, at the start of each block transfer. Fig 9-43 shows an example of a destination scatter transfer. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 129: Fig 9-43 Example Of Destination Scatter Transfer

SARx = A0 (starting source address) Fig 9-44 shows a source gather when SGR.SGI = 0x01. Fig 9-44 Source gather when SGR.SGI = 0x1 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 130: Endianness

User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 131: Registers

Reg Exist: dnc ≥ 2 DAR1 0x060 Channel 1 Destination Address Register Reg Exist: dnc ≥ 2 LLP1 0x068 Channel 1 Linked List Pointer Register User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 132 Channel 3 Destination Status Address Register Reg Exist: dnc ≥ 4 and dstat3 = True CFG3 0x148 0x0000000400000e40 Channel 3 Configuration Register User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 133 Channel 6 Linked List Pointer Register Reg Exist: dnc ≥ 7 and llp6_hc = False CTL6 0x228 Configuration dependent Channel 6 Control Register User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 134 Reg Exist: Yes StatusBlock 0x2f0 Status for IntBlock Interrupt Reg Exist: Yes StatusSrcTran 0x2f8 Status for IntSrcTran Interrupt Reg Exist: Yes User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 135 The register exists when this parameter is set to True. DMA_COMP_P 0x3e0 Depends on user Refer to the bit table in the description for ARAMS_3 configuration DMA_COMP_PARAMS_3. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 136: Registers And Field Descriptions

This is the DMAC Channel Enable Register. If software needs to set up a new channel, then it can read this register in order to find out which channels are currently inactive; it can then enable an inactive channel with the required priority. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 137 For information on how the SARx is updated at the start of each DMA block for multi-block transfers, refer to Table 9-19. dnc = DMAH_NUM_CHANNELS If dnc = 8, then this field is not present. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 138 (BLOCK_TS * SRC_TR_WIDTH)/DST_TR_WIDTH != integer (where SRC_TR_WIDTH, DST_TR_WIDTH is byte width of transfer) 9.3.2.2.4 LLPx Name: Linked List Pointer Register for Channel x Size: 64 bits (upper 32 bits are reserved) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 139 The CTLx register is part of the block descriptor (linked list item – LLI) when block chaining is enabled. It can be varied on a block-by-block basis within a DMA transfer when block chaining is enabled. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 140 00 = AHB master 1 01 = AHB master 2 10 = AHB master 3 11 = AHB master 4 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 141 Dependencies: This field does not exist if DMAH_CHx_SRC_GAT_EN is not selected; in this case, the read-back value is always 0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 142 This value must be less than or equal to DMAH_Mk_HDATA_WIDTH, where k is the AHB layer 1 to 4 where the destination resides. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 143 SSTAT3 – 0x128 SSTAT4 – 0x180 SSTAT5 – 0x1d8 SSTAT6 – 0x230 SSTAT7 – 0x288 Read/write access: read/write User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 144 Size: 64 bits (upper 32 bits are reserved) Address offset: for x = 0 to 7: SSTATAR0 – 0x030 SSTATAR1 – 0x088 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 145 LLI before the start of the next block. 9.3.2.2.10 CFGx Name: Configuration Register for Channel x Size: 64 bits (upper 32 bits are reserved) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 146 DSTATARx register, stored in the DSTATx register and written out to the DSTATx location of the LLI if DS_UPD_EN is high. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 147 This field does not exist if the configuration parameter DMAH_CHx_LOCK_EN is set to False; in this case, the read-back value is always 0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 148 A programmed value outside this range will cause erroneous behavior. RSVD Reserved Table 9-18 PROTCTL field to HPROT mapping 1’b1 HPROT[0] User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 149 DSR5 – 0x208 DSR6 – 0x260 DSR7 – 0x2b8 Read/write access: read/write Destination Scatter register contains two fields: User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 150 Writing to the appropriate bit in the Clear registers clears an interrupt in the Raw Status registers and the Status registers on the same clock cycle. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 151 Access Reset Description 63:DMAH_NUM_CHANNELS RSVD Reserved DMAH_NUM_CHANNELS-1:0 STATUS Interrupt status. 9.3.2.3.3 MaskBlock, MaskDstTran, MaskErr, MaskSrcTran, MaskTfr Name: Interrupt Mask Registers User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 152 ClearTfr[2] is the clear bit for the Channel 2 transfer complete interrupt. Writing a 0 has no effect. These registers are not readable. Name Access Reset Description 63:DMAH_NUM_CHANNELS RSVD Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 153 DMAC configuration has not optimized the same registers. In normal operation, the readback value of some registers is a function of the DMAC state and does not match the value written. Name Access Reset Description User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 154 The value of this register is derived from the DMAH_CH7_MULT_SIZE coreConsultant parameter. 0x0 = 4 0x1 = 8 0x2 = 16 0x3 = 32 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 155 The value of this register is derived from the DMAH_CH7_DTW coreConsultant parameter. 0x0 = NO_HARDCODE 0x1 = 8 0x2 = 16 0x3 = 32 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 156 The value of this register is derived from the DMAH_CH5_MULT_SIZE coreConsultant parameter. 0x0 = 4 0x1 = 8 0x2 = 16 0x3 = 32 0x4 = 64 0x5 = 128 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 157 0x1 = 8 0x2 = 16 0x3 = 32 0x4 = 64 0x5 = 128 0x6 = 256 0x7 = reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 158 0x1 = TRUE CH6_LOCK_EN The value of this register is derived from the DMAH_CH6_LOCK_EN coreConsultant parameter. 0x0 = FALSE 0x1 = TRUE User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 159 Reserved 62:60 CH3_FIFO_DEPTH The value of this register is derived from the DMAH_CH3_FIFO_DEPTH coreConsultant parameter. 0x0 = 8 0x1 = 16 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 160 The value of this register is derived from the DMAH_CH3_SRC_GAT_EN coreConsultant parameter. 0x0 = FALSE 0x1 = TRUE CH3_DST_SCA_EN The value of this register is derived from the DMAH_CH3_DST_SCA_EN coreConsultant parameter. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 161 0x4 = NO_HARDCODE 18:16 CH4_MAX_MULT_SIZE The value of this register is derived from the DMAH_CH4_MULT_SIZE coreConsultant parameter. 0x0 = 4 0x1 = 8 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 162 The value of this register is derived from the DMAH_CH4_DTW coreConsultant parameter. 0x0 = NO_HARDCODE 0x1 = 8 0x2 = 16 0x3 = 32 0x4 = 64 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 163 0x1 = 8 0x2 = 16 0x3 = 32 0x4 = 64 0x5 = 128 0x6 = 256 0x7 = reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 164 0x6 = 256 0x7 = reserved RSVD Reserved 30:28 CH2_FIFO_DEPTH The value of this register is derived from the DMAH_CH2_FIFO_DEPTH coreConsultant parameter. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 165 0x1 = TRUE CH2_SRC_GAT_EN The value of this register is derived from the DMAH_CH2_SRC_GAT_EN coreConsultant parameter. 0x0 = FALSE 0x1 = TRUE User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 166 0x2 = RELOAD_CONT 47:44 CH7_MULTI_BLK_TYPE 0x3 = RELOAD_RELOAD 43:40 CH7_MULTI_BLK_TYPE 0x4 = CONT_LLP 39:36 CH7_MULTI_BLK_TYPE 0x5 = RELOAD_LLP 35:32 CH7_MULTI_BLK_TYPE 0x6 = LLP_CONT User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 167 0x1 = TRUE CH0_MULTI_BLK_EN The value of this register is derived from the DMAH_CH0_MULT_BLK_EN coreConsultant parameter. 0x0 = FALSE 0x1 = TRUE User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 168 Bits 63:32 include the top-level parameter for DMAC. Bits 31:0 include the maximum block size parameters for Channel 0 to Channel 7. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 169 The value of this register is derived from the DMAH_NUM_ CHANNELS coreConsultant parameter. 0x00 = 1 0x10 = 8 39:36 RSVD Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 170: Programming The Dmac

Shipped with the DMAC component is an address definition (memory map) C header file. This can be used when the DMAC is programmed in a C environment. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 171: Register Access

Note: Multi-block transfers—in which the source and destination are swapped during the transfer—are not supported. In a multi-block transfer, the direction must not change for the duration of the transfer. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 172: Fig 9-45 Multi-Block Transfer Using Linked Lists When Dmah_Chx_Stat_Src Set To True

False. If this parameter is False, then the order of a Linked List item is as follows: SARx DARx LLPx CTLx DSTATx User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 173: Fig 9-46 Multi-Block Transfer Using Linked Lists When Dmah_Chx_Stat_Src Set To False

Table 9-19 row number, the LLI.SARx/LLI.DARx address may or may not be used to reprogram the DMAC SARx/DARx registers. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 174 This column assumes that the configuration parameter DMAH_CHx_CTL_WB_EN = True. If DMAH_CHx_CTL_WB_EN = False, then there is never writeback of the control and status registers regardless of transfer type, and all rows of this column are “No”. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 175 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 176: Programing Example

`AHB_MASTER.write(0, (llp_addr + 12), ctlx[31:0], AhbWord32Attrb, handle[0]); `AHB_MASTER.write(0, (llp_addr + 16), ctlx[63:32], AhbWord32Attrb, handle[0]); // update pointers llp_addr = llp_addr + 20; // start of next LLI User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 177: Fig 9-49 Flowchart For Dma Programming Example

Finally, enable the channel by writing a 1 to the ChEnReg.CH_EN bit; the transfer is performed. Fig 9-49 Flowchart for DMA programming example User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 178: Programming A Channel

This step requires programming the HS_SEL_SRC/HS_SEL_DST bits, respectively. Writing a 0 activates the hardware handshaking interface to handle source/destination requests. Writing a 1 activates the software handshaking interface to handle source and destination requests. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 179 DSTATARx register so that the destination status information can be fetched from the location pointed to by the User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 180 Table 9-19 (as discussed earlier). The DMAC then knows that the previously transferred block was the last block in the DMA transfer. The DMA transfer might look like that shown in Fig 9-50. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 181: Fig 9-50 Multi-Block With Linked Address For Source And Destination

Fig 9-51 Multi-block with linked address for source and destination where SARx and DARx between successive blocks are contiguous The DMA transfer flow is shown in Fig 9-52. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 182: Fig 9-52 Dma Transfer Flow For Source And Destination Linked List Address

Transfer width for the destination in the DST_TR_WIDTH field; Table 9-16 lists the decoding for this field. Source master layer in the SMS field where the source resides. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 183: Fig 9-53 Multi-Block Dma Transfer With Source And Destination Address Auto-Reloaded

The transfer is similar to that shown in Fig 9-53. Fig 9-53 Multi-block DMA transfer with source and destination address auto-reloaded User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 184: Fig 9-54 Dma Transfer Flow For Source And Destination Address Auto-Reloaded

Write the channel configuration information into the CFGx register for channel x. Designate the handshaking interface type (hardware or software) for the source and destination peripherals; this is not required for memory. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 185 Table 9-19. If the DMAC is in Row 1 or Row 5, then the DMA transfer has completed. Hardware sets the transfer User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 186: Fig 9-55 Multi-Block Dma Transfer With Source Address Auto-Reloaded And Linked List Destination Address

Fig 9-55 Multi-block DMA transfer with source address auto-reloaded and linked list destination address The DMA transfer flow is shown in Fig 9-56. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 187: Fig 9-56 Dma Transfer Flow For Source Address Auto-Reloaded And Linked List Destination Address

Write the control information for the DMA transfer in the CTLx register for channel x. For example, in the register, you can program the following: User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 188 Row 1 of Table 9-19 before the last block of the DMA transfer has completed. The transfer is similar to that shown in Fig 9-57. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 189: Fig 9-57 Multi-Block Dma Transfer With Source Address Auto-Reloaded And Contiguous Destination Address

Note: This type of multi-block transfer can only be enabled when either of the following parameters is set: DMAH_CHx_MULTI_BLK_TYPE = 0 DMAH_CHx_MULTI_BLK_TYPE = LLP_CONT User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 190 DMAH_CHx_CTL_WB_EN = True, DMAH_CHx_STAT_DST = True, and CFGx.DS_UPD_EN is enabled. For conditions under which the destination status information is fetched from system memory, refer to the Write Back column of Table 9-19. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 191: Fig 9-59 Multi-Block Dma Transfer With Linked List Source Address And Contiguous Destination Address

Fig 9-59 Multi-block DMA transfer with linked list source address and contiguous destination address The DMA transfer flow is shown in Fig 9-60. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 192: Disabling A Channel Prior To Transfer Completion

If the DMAC is configured to use defined length bursts (DMAH_INCR_BURSTS = 0), disabling the channel via software prior to completing a transfer is not supported. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 193: Defined-Length Burst Support On Dmac

INCR16 are required. The DMAC can be configured to use defined-length bursts by setting the configuration parameter DMAH_INCR_BURSTS to 0. In this mode, the DMAC will select the largest valid defined-length burst to complete the transfer. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 194: General Timers

10.1.4 Functional Description 10.1.4.1 Upcounting Mode This timer is a 32-bit counter with its related auto-reload register. The counter can count up. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 195: Pulse Mode Timer

One pulse mode PWM mode with polarity selection Statistic pulse width ● ● Statistic pulse number ● ● Interrupt generation ● ● User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 196: Block Diagram

0, as well as the counter of the prescaler, but the prescale rate doesn’t change. In addition, if the URS bit in the TIMx_CR register is set, User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 197: Fig 10-3 Statistic Pulse Width Mode Diagram (Positive Edge Of Trgi Is Active For Capture)

Fig 10-4 gives an example of statistic pulse number mode when prescaler division is 1, positive edge of TRGI is active for capture, and the ARR field equals to E6. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 198: Pwm Mode Timer

Input pin 2 input capture 2 input capture Output pin 18 PWM out 6 PWM out Sleep mode ● 0%/100% ● ● User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 199: Block Diagram

The counter, also the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running. The time-base unit includes: Counter register (TIMx_CNT) Prescaler register (TIMx_PSC) Auto-reload register (TIMx_ARR) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 200 Write a new value in TIMx_PSC Prescaler buffer Prescaler counter Fig 10-6 Counter timing diagram with prescaler division change from 1 to 2 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 201 Fig 10-8 to Fig 10-13 show some examples of the counter behavior for different clock frequencies when the ARR field equals to 0x36. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 202: Fig 10-8 Counter Timing Diagram (Internal Clock Divided By 1)

0000 0001 Counter overflow Update event (UEV) Update interrupt flag (UIF) Fig 10-10 Counter timing diagram (internal clock divided by 4) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 203: Fig 10-11 Counter Timing Diagram (Internal Clock Divided By N)

(UIF) Auto-reload register Write a new value in TIMx_ARR Fig 10-12 Counter timing diagram, update event when ARPE=0 (TIMx_ARR not preloaded) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 204: Fig 10-13 Counter Timing Diagram, Update Event When Arpe=1 (Timx_Arr Preloaded)

The timer is only able to generate PWM in edge-aligned mode. Fig 10-14 shows some edge-aligned PWM waveforms in an example where TIMx_ARR=8. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 205: Fig 10-14 Edge-Aligned Pwm Waveforms (Arr=8, Ccxp=0)

Note: Since the 18 channels are independent with each other, when TRGI is used to trigger one channel to output PWM signal, it can also be used as capture source in input capture mode of another channel. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 206: Registers

1: Counter is working. 15:9 RSVD Reserved CNT_RUN Counter run status 0: Counter is disabled. 1: Counter is enabled. RSVD Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 207 Access Reset Description 31:1 RSVD Reserved Update interrupt enable 0: Update interrupt is disabled. 1: Update interrupt is enabled. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 208 Counter value 10.4.1.7 TIMx Auto-reload Register (TIMx_ARR) Name: TIMx auto-reload register (x = {0, 1, 2, 3}) Address offset: 0x1C User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 209: Tim4 Registers

Counter run status 0: Counter is disabled 1: Counter is enabled RSVD Reserved CNT_STOP Counter stop 0: No action. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 210 1: CC0 interrupt is enabled. Update interrupt enable 0: Update interrupt is disabled. 1: Update interrupt is enabled. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 211 10.4.2.6 TIMx Counter Register (TIMx_CNT) Name: TIM4 counter register Address offset: 0x14 Reset value: 0x00000000 Read/write access: read/write User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 212 ARPE bit in the TIMx_CR register. 10.4.2.9 TIMx Capture/Compare Register 0 (TIMx_CCR0) Name: TIM4 capture/compare register 0 Address offset: 0x20 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 213: Tim5 Registers

TIM5 capture/compare register 7 TIMx_CCR8 0x40 TIM5 capture/compare register 8 TIMx_CCR9 0x44 TIM5 capture/compare register 9 TIMx_CCR10 0x48 TIM5 capture/compare register 10 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 214 Reset value: 0x00000000 Read/write access: read/write … ARPE UDIS RSVD RSVD RSVD Name Access Reset Description 31:9 RSVD Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 215 1: CC13 interrupt is enabled CC12IE Capture/compare 12 interrupt enable 0: CC12 interrupt is disabled 1: CC12 interrupt is enabled User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 216 CC5IF CC4IF CC3IF CC2IF CC1IF R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1 R/W1C User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 217 Access Reset Description 31:19 RSVD Reserved CC17G Refer to CC0G description CC16G Refer to CC0G description CC15G Refer to CC0G description User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 218 10.4.3.7 TIMx Prescaler Register (TIMx_PSC) Name: TIM5 prescaler register Address offset: 0x18 Reset value: 0x00000000 Read/write access: read/write … … User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 219 CC0 channel configured as input 0: Positive edge of TRGI is active for capture. 1: Negative edge of TRGI is active for capture. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 220 Name: TIM5 capture/compare register 2 Address offset: 0x28 Reset value: 0x00000000 Read/write access: read/write CC2M CC2P OC2PE CC2E RSVD RSVD CCR2 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 221 Refer to OC0PE description in TIMx_CCR0 CC4E Refer to CC0E description in TIMx_CCR0 23:16 RSVD Reserved 15:0 CCR4 Refer to CCR0 description in TIMx_CCR0 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 222 Name: TIM5 capture/compare register 7 Address offset: 0x3C Reset value: 0x00000000 Read/write access: read/write RSVD CC7M CC7P OC7PE CC7E RSVD User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 223 Name Access Reset Description 31:28 RSVD Reserved CC9M Refer to CC0M description in TIMx_CCR0 CC9P Refer to CC0P description in TIMx_CCR0 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 224 Refer to CCR0 description in TIMx_CCR0 10.4.3.21 TIMx Capture/Compare Register 12 (TIMx_CCR12) Name: TIM5 capture/compare register 12 Address offset: 0x50 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 225 Name: TIM5 capture/compare register 14 Address offset: 0x58 Reset value: 0x00000000 Read/write access: read/write CC14M CC14P OC14PE CC14E RSVD RSVD CCR14 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

- Page 226 Refer to OC0PE description in TIMx_CCR0 CC16E Refer to CC0E description in TIMx_CCR0 23:16 RSVD Reserved 15:0 CCR16 Refer to CCR0 description in TIMx_CCR0 User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 227: Design Implementation

TIM4 TIM0/1/2/3 timer_pwm_ch18 TIM5 Fig 10-16 Block diagram User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 228: Synchronous Data From Fast Clock To Slow Clock

Check whether the timer is running Poll CNT_RUN in TIMx_EN Optional Change ARR on the fly Configure TIMx_ARR Recommend to set ARPE bit in TIMx_CR User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 229: Pulse Mode

10.6.3 PWM Mode PWM mode: support TIM5. 10.6.3.1 Repeated Mode The PWM repeated mode configuration flow is illustrated in Table 10-11. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 230: Input Capture Mode

In input capture mode, different channels can be used to capture the double edge of TRGI, thus to get the width of TRGI. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 231: Real-Time Clock (Rtc)

The RTC is connected under APB buses. The total block diagram is shown in Fig 11-1. APB Bus rtc_apbslv_wrapper rtc_reg rtc_clk_rst_gen rtc_ctrl rtc_alarm rtc_clk_div_spre rtc_clk_div_apre rtc_counter Fig 11-1 RTC block diagram User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 232: Rtc Clock Select Diagram

A 9-bit asynchronous prescaler configured through the PREDIV_A bits of the RTC_PRER register. A 9-bit synchronous prescaler configured through the PREDIV_S bits of the RTC_PRER register. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 233: Auto-Trigger Calibration Circuit

ACAL_SEL[1:0] = 11 and the ACAL_THES[5:0] is set, the ACAL_CNT[5:0] updates once per day. ACAL_SEL[1:0] Minute_udp Hour_udp ACAL_CNT[5:0] Day_udp xtal_req_32k ACAL_THES[5:0] Fig 11-5 xtal_req_32k block diagram User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 234: Programmable Alarm

If RECALPF is set to 0, write a new value to RTC_CALIBR if necessary, RECALPF is then automatically set to 1. Within three clk_apre cycles after the write operation to RTC_CALIBR, the new calibration settings take effect. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 235: Day Threshold Program

Second tens in BCD format SU[3:0] Second units in BCD format 11.3.2 RTC Control Register (RTC_CR) Name: RTC control register User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. - Page 236 1: Adds 1 hour to the current time. This can be used for summer time change. This bit is always read as 0. User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

-

Page 237: Rtc Initialization And Status Register (Rtc_Isr)

It is cleared by hardware when ALME bit has been set to 1 in RTC_CR register. 0: Alarm update isn’t allowed 1: Alarm update is allowed User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 238: Rtc Prescaler Register (Rtc_Prer)

0: Positive calibration: time update frequency is increased 1: Negative calibration: time update frequency is decreased 13:7 RSVD Reserved Digital calibration User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 239: Rtc Alarm 1 Register Low (Rtc_Almr1L)

This register is write protected, and can be written only when ALMWF is set to 1 in RTC_ISR register, or in initialization mode. RSVD MSK3 DAY[8:0] RSVD Name Access Reset Description 31:10 RSVD Reserved User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 240: Rtc Write Protection Register (Rtc_Wpr)

01: 32K auto calibration once every ACAL_THRES[5:0] minutes 10: 32K auto calibration once every ACAL_THRES[5:0] hours 11: 32K auto calibration once every ACAL_THRES[5:0] days User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 241: Operation Flow

The calibration configure flow is shown in Table 11-5. Table 11-5 Calibration configure flow Step What to do How to do Comments User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 242: Daylight Saving Time

It is early enough that the entire continental U.S. switches by daybreak, and the changeover occurs before most early shift workers and early churchgoers are affected. (http://www.webexhibits.org/daylightsaving/b.html) User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved. -

Page 243: Watchdog Timer (Wdt)