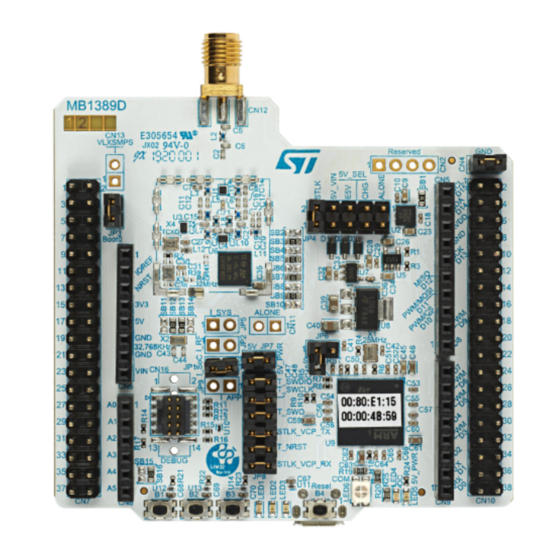

ST STM32WL5 Series Manuals

Manuals and User Guides for ST STM32WL5 Series. We have 2 ST STM32WL5 Series manuals available for free PDF download: Reference Manual

ST STM32WL5 Series Reference Manual (1461 pages)

Advanced Arm-based 32-bit MCUs with sub-GHz radio solution

Brand: ST

|

Category: Microcontrollers

|

Size: 17 MB

Table of Contents

-

-

CPU2 Boot64

-

SRAM Erase65

-

-

-

Interrupts84

-

-

-

-

Empty Check98

-

-

Introduction116

-

RSSLIB Functions116

-

-

-

FLASH Interrupts126

-

FLASH Registers128

-

-

(Flash_Srrvr)149

-

-

-

-

Transmitter156

-

Receiver157

-

Rf-Pll158

-

-

Lora Modem160

-

Lora Framing162

-

FSK Modem164

-

MSK Modem165

-

Generic Framing165

-

BPSK Modem167

-

BPSK Framing167

-

-

-

-

-

(Subghz_Gsyncr7)210

-

-

-

(Subghz_Gsyncr5)210

-

-

-

(Subghz_Gsyncr4)211

-

(Subghz_Gsyncr3)211

-

(Subghz_Gsyncr2)211

-

(Subghz_Gsyncr1)211

-

-

-

(Subghz_Gsyncr0)212

-

-

-

(Subghz_Lsyncrh)212

-

-

-

(Subghz_Lsyncrl)212

-

-

-

(Subghz_Paocpr)214

-

-

-

Power Supplies219

-

CPU2 Boot230

-

Low-Power Modes232

-

Run Mode240

-

Table 47. Lprun241

-

Sleep Mode243

-

Stop 0 Mode245

-

Stop 1 Mode247

-

Stop 2 Mode248

-

Standby Mode250

-

Shutdown Mode252

-

PWR Registers254

-

PWR Register Map275

-

-

-

Reset277

-

Clocks279

-

HSI16 Clock285

-

MSI Clock285

-

Pll286

-

LSE Clock287

-

LSI Clock288

-

SPI2S2 Clock290

-

ADC Clock291

-

RTC Clock291

-

Timer Clock291

-

Watchdog Clock292

-

True RNG Clock292

-

Low-Power Modes296

-

RCC Registers298

-

-

(Rcc_Apb1Smenr1)328

-

-

-

(Rcc_Apb1Smenr2)330

-

-

-

(Rcc_Ccipr)333

-

-

-

(Rcc_C2Apb1Enr1)345

-

-

-

(Rcc_C2Apb1Enr2)346

-

-

RCC Register Map357

-

-

-

Introduction365

-

Main Features365

-

-

HSEM Interrupts369

-

HSEM Registers372

-

-

-

-

IPCC Interrupts386

-

IPCC Registers386

-

-

-

GPIO Registers402

-

-

SYSCFG Registers428

-

-

(Syscfg_Exticr1)430

-

-

-

(Syscfg_Exticr2)431

-

(Syscfg_Exticr3)432

-

-

-

(Syscfg_Exticr4)434

-

-

-

Introduction446

-

-

-

(Lptim1/Lptim2)450

-

-

-

-

Introduction454

-

-

DMA Transfers457

-

DMA Arbitration458

-

DMA Channels459

-

DMA Interrupts466

-

DMA Registers466

-

DMA Register Map477

-

Advertisement

ST STM32WL5 Series Reference Manual (1454 pages)

Advanced Arm-based 32-bit MCUs with sub-GHz radio solution

Brand: ST

|

Category: Microcontrollers

|

Size: 29 MB

Table of Contents

-

-

Glossary61

-

CPU2 Boot66

-

SRAM Erase67

-

Introduction72

-

Interrupts86

-

Empty Check100

Advertisement