Table of Contents

Advertisement

Quick Links

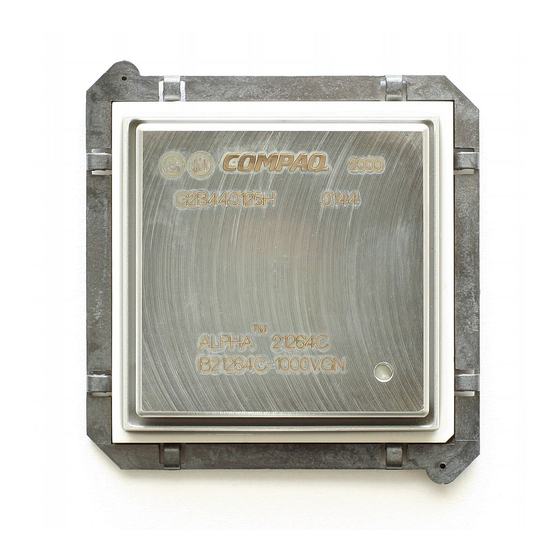

Alpha 21264/EV67

Microprocessor Hardware

Reference Manual

Order Number:

DS–0028B–TE

This manual is directly derived from the internal 21264/EV67 Specifications, Revi-

sion 1.4. You can access this hardware reference manual in PDF format from the

following site:

ftp://ftp.compaq.com/pub/products/alphaCPUdocs

Revision/Update Information:

This is a revised document. It supercedes

the Alpha 21264A Microprocessor

Hardware Reference Manual

(DS–0028A–TE).

Compaq Computer Corporation

Shrewsbury, Massachusetts

Advertisement

Table of Contents

Summary of Contents for Compaq 21264

-

Page 1: Reference Manual

Alpha 21264/EV67 Microprocessor Hardware Reference Manual Order Number: DS–0028B–TE This manual is directly derived from the internal 21264/EV67 Specifications, Revi- sion 1.4. You can access this hardware reference manual in PDF format from the following site: ftp://ftp.compaq.com/pub/products/alphaCPUdocs Revision/Update Information: This is a revised document. It supercedes... - Page 2 © Compaq Computer Corporation 2000. All rights reserved. Printed in the U.S.A. COMPAQ, the Compaq logo, the Digital logo, and VAX Registered in United States Patent and Trademark Office. Pentium is a registered trademark of Intel Corporation. Other product names mentioned herein may be trademarks and/or registered trademarks of their respective compa- nies.

-

Page 3: Table Of Contents

21264/EV67 Microprocessor Features ........ - Page 4 21264/EV67 Microprocessor Logic Symbol ........

- Page 5 21264/EV67-to-System Commands........

- Page 6 IPR Scoreboard Bits........... . Alpha 21264/EV67 Hardware Reference Manual 5–4...

- Page 7 Differential Reference Clocks..........Alpha 21264/EV67 Hardware Reference Manual 6–8...

- Page 8 Differential 21264/EV67 Clocks ........

- Page 9 Opcodes Reserved for Compaq........

- Page 10 D.40 Restriction 44: Not Applicable to the 21264/EV67 ....... .

- Page 11 21264/EV67 Microprocessor Logic Symbol ........

- Page 12 7–5 21264/EV67 Reset State Machine State Diagram ....... . 10–1 Type 1 Heat Sink.

- Page 13 21264/EV67-Supported Cache Block States ........

- Page 14 ProfileMe Mode PCTR_CTL Input Select Fields ........7–1 21264/EV67 Reset State Machine Major Operations ......7–2 Signal Pin Reset State .

- Page 15 21264/EV67 Error Detection Mechanisms ........

-

Page 17: Internal Architecture

Audience This manual is for system designers and programmers who use the Alpha 21264/EV67 microprocessor (referred to as the 21264/EV67). Content This manual contains the following chapters and appendixes: Chapter 1, Introduction, introduces the 21264/EV67 and provides an overview of the Alpha architecture. - Page 18 PALcode. Appendix E, 21264/EV67-to-Bcache Pin Interconnections, provides the pin interface between the 21264/EV67 and Bcache SSRAMs. The Glossary lists and defines terms associated with the 21264/EV67. An Index is provided at the end of the document. Documentation Included by Reference...

-

Page 19: Terminology And Conventions

Bits and fields are cleared when read. Unless otherwise specified, such bits cannot be written. Reserved Bits and fields are reserved by Compaq and should not be used; however, zeros can be written to reserved fields that cannot be masked. Read Only The value may be read by software. - Page 20 [:]. For example, [9:7,5,2:0] specifies bits 9,8,7,5,2,1, and 0. Similarly, single bits are frequently indicated with square brackets. For example, [27] specifies bit 27. See also Field Notation. Caution Cautions indicate potential damage to equipment or loss of data. Alpha 21264/EV67 Hardware Reference Manual...

- Page 21 The bit range may, but need not necessarily, correspond to the bit Extent in the register. See the explanation above Table 5–1 for more information. Signal Names The following examples describe signal-name conventions used in this document. Alpha 21264/EV67 Hardware Reference Manual Words Bytes ½...

- Page 22 Boldface, mixed-case type denotes signal names that are assigned internal and external to the 21264/EV67 (that is, the signal traverses a chip interface pin). When a signal has high and low assertion states, a lower- case italic x represents the assertion states.

- Page 23 Do not care. A capital X represents any valid value. Alpha 21264/EV67 Hardware Reference Manual xxiii...

-

Page 25: Introduction

This use of resources makes it easy to build implementations that issue multiple instructions every CPU cycle. The 21264/EV67 uses a set of subroutines, called privileged architecture library code (PALcode), that is specific to a particular Alpha operating system implementation and hardware platform. -

Page 26: Addressing

1.1.1 Addressing The basic addressable unit in the Alpha architecture is the 8-bit byte. The 21264/EV67 supports a 48-bit or 43-bit virtual address (selectable under IPR control). Virtual addresses as seen by the program are translated into physical memory addresses by the memory-management mechanism. -

Page 27: 21264/Ev67 Microprocessor Features

The 21264/EV67 can issue four Alpha instructions in a single cycle, thereby minimiz- ing the average cycles per instruction (CPI). A number of low-latency and/or high- throughput features in the instruction issue unit and the onchip components of the mem- ory subsystem further reduce the average CPI. - Page 28 Chip and module level test support, including an instruction cache test interface to support chip and module level testing. • A 2.0-V external interface. Refer to Chapter 9 for 21264/EV67 dc and ac electrical characteristics. Refer to the Alpha Architecture Handbook, Version 4 implementation-dependent information. Introduction 1–4...

-

Page 29: Internal Architecture

This chapter provides both an overview of the 21264/EV67 microarchitecture and a sys- tem designer’s view of the 21264/EV67 implementation of the Alpha architecture. The combination of the 21264/EV67 microarchitecture and privileged architecture library code (PALcode) defines the chip’s implementation of the Alpha architecture. If a certain piece of hardware seems to be “architecturally incomplete,”... -

Page 30: Instruction Fetch, Issue, And Retire Unit

There can be up to 80 instructions, in 20 successive fetch slots, in flight between the register rename mappers and the end of the pipeline. The VPC logic contains a 20-entry table to store these fetched VPC addresses. Internal Architecture 2–2 Alpha 21264/EV67 Hardware Reference Manual... -

Page 31: Ev67 Block Diagram

Figure 2–1 21264/EV67 Block Diagram Ibox Virtual Address Fetch Unit Next Address Queue Branch Predictor Integer Issue Queue (20 Entries) Ebox Address ALU 0 UNIT UNIT (L0) (U0) (U1) Integer Registers 0 Integer Registers 1 (80 Registers) (80 Registers) Mbox... -

Page 32: Branch Predictor

4K entry table of 2-bit saturating counters. The value of the saturating counter determines the predication, taken/not-taken, of the cur- rent branch. Internal Architecture 2–4 Choice Predictor Branch Address FM-05810.AI4 Local Index Predictor 1K x 3 Local Branch Prediction FM-05811.AI4 Alpha 21264/EV67 Hardware Reference Manual... -

Page 33: Global Predictor

The ITB supports an 8-bit ASN and contains an ASM bit. The Icache is virtually addressed and contains the access-check information, so the ITB is accessed only for Istream references that miss in the Icache. Istream transactions to I/O address space are UNDEFINED. Alpha 21264/EV67 Hardware Reference Manual 21264/EV67 Microarchitecture Global Predictor 4K x 2 FM-05812.AI4... -

Page 34: Integer Issue Queue

2.1.1.6 Integer Issue Queue The 20-entry integer issue queue (IQ), associated with the integer execution units (Ebox), issues the following types of instructions at a maximum rate of four per cycle: Internal Architecture 2–6 Alpha 21264/EV67 Hardware Reference Manual... -

Page 35: Floating-Point Issue Queue

The add and multiply arbiters pick one requester per cycle, while the store pipeline arbiter picks two requesters per cycle, one for each store pipeline. Alpha 21264/EV67 Hardware Reference Manual 21264/EV67 Microarchitecture Internal Architecture... -

Page 36: Exception And Interrupt Logic

“subclusters”, named upper (U) and lower (L). Fig- ure 2–6 shows the integer execution unit. In the figure, iop_wr is the cross-cluster bus for moving integer result values between clusters. Internal Architecture 2–8 Alpha 21264/EV67 Hardware Reference Manual... -

Page 37: Integer Execution Unit-Clusters 0 And 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 Floating-Point Execution Units

• One fully-pipelined unit (located in U0), with 3-cycle latency, that executes the fol- lowing instructions: – CTLZ, CTPOP, CTTZ – PERR, MINxxx, MAXxxx, UNPKxx, PKxx Alpha 21264/EV67 Hardware Reference Manual 21264/EV67 Microarchitecture iop_wr iop_wr Register iop_wr iop_wr Load/Store Data Load/Store Data FM-05643.AI4... -

Page 38: Floating-Point Execution Unit

The 72 Fbox register file entries contain storage for the values of the 31 Alpha floating- point registers (F31 is not stored) and 41 values written by instructions that have not been retired. Internal Architecture 2–10 LK98-0004A Alpha 21264/EV67 Hardware Reference Manual... -

Page 39: External Cache And System Interface Unit

The duplicate Dcache tag (DTAG) array holds a duplicate copy of the Dcache tags and is used by the Cbox when processing Dcache fills, Icache fills, and system port probes. 2.1.5 Onchip Caches The 21264/EV67 contains two onchip primary-level caches. 2.1.5.1 Instruction Cache The instruction cache (Icache) is a 64KB virtual-addressed, 2-way set-predict cache. -

Page 40: Data Cache

The Dcache contains two sets, each with 512 rows containing 64-byte blocks per row (that is, 32K bytes of data per set). The 21264/EV67 requires two additional bits of vir- tual address beyond the bits that specify an 8KB page, in order to specify a Dcache row index. -

Page 41: Load Queue

The 7-stage pipeline provides an optimized environment for executing Alpha instruc- tions. The pipeline stages (0 to 6) are shown in Figure 2–8 and described in the follow- ing paragraphs. Alpha 21264/EV67 Hardware Reference Manual Pipeline Organization Internal Architecture 2–13... - Page 42 ALU Shifter Multiplier Integer Register File Address Address 64KB Data Cache Floating-Point Add, Divide, Floating- and Square Root Point Register Floating-Point File Multiply Alpha 21264/EV67 Hardware Reference Manual System (64 Bits) Interface Unit Cache (128 Bits) Physical Address (44 Bits) FM-05575.AI4...

-

Page 43: Pipeline Organization

IQ or FQ two cycles after they are issued. For example, if an instruction is issued in cycle n, it remains in the FQ or IQ in cycle n+1 but does not request service, and is deleted in cycle n+2. Alpha 21264/EV67 Hardware Reference Manual Internal Architecture 2–15... -

Page 44: Pipeline Abort Delay (Gclk Cycles)

2–16 Penalty (Cycles) Comments Integer or floating-point conditional branch misprediction. Memory format JSR or HW_RET. Load-load order or store-load order. — — — — 13+latency Add latency of instruction. See Section 2.3.3 for instruction latencies. Alpha 21264/EV67 Hardware Reference Manual... -

Page 45: Instruction Group Definitions

L0, U0, L1, U1 imul imisc fadd fmul fcmov1 fcmov2 fdiv fsqrt None Alpha 21264/EV67 Hardware Reference Manual Instruction Issue Rules Instruction Type All integer load instructions All floating-point load instructions All integer store instructions LDA, LDAH WH64, ECB, WMB RPCC RS, RC... -

Page 46: Ebox Slotting

U E E E U L U L U E E L U L U L U E E U Alpha 21264/EV67 Hardware Reference Manual Slotting 3 2 1 0 L L L L L L L U L L U U... - Page 47 L E U U L L E E L L E L L L E U L L L E — Alpha 21264/EV67 Hardware Reference Manual Slotting Instruction Class 3 2 1 0 3 2 1 0 L L U U...

-

Page 48: Instruction Latencies

Consumer fst or ftoi. Measured from when an fadd is issued from the FQ to when an fst or ftoi is issued from the IQ. Internal Architecture 2–20 Ebox IPRs = 1. Ibox and Mbox IPRs = 3. Alpha 21264/EV67 Hardware Reference Manual... -

Page 49: Instruction Retire Rules

Instruction Class Retire Stage Integer conditional branch Integer multiply 7/13 Integer operate Memory Floating-point add Floating-point multiply Alpha 21264/EV67 Hardware Reference Manual Instruction Retire Rules Comments — Latency is 13 cycles for the MUL/V instruction. — — — — Internal Architecture... -

Page 50: Floating-Point Divide/Square Root Early Retire

11 plus 9 from Table 2–4. Latency is 11 if hardware detects that no exception is possible (see Section 2.4.1). Branch instruction mispredict is reported in stage 7. JSR instruction mispredict is reported in stage 8. ) OR (EXP <= 2 ) OR (EXP <= 382 Alpha 21264/EV67 Hardware Reference Manual... -

Page 51: Load Instructions To R31 And F31

See Table 6–3. 2.6.2 Prefetch with Modify Intent: LDS Instruction The 21264/EV67 processes an LDS instruction, with F31 as the destination, as a prefetch with modify intent transaction (ReadBlkMod command). If the transaction hits a dirty Dcache block, the instruction is dismissed. Otherwise, the addressed cache block is allocated into the Dcache for write access, with its dirty and modified bits set. -

Page 52: Prefetch, Evict Next: Ldq And Hw_Ldq Instructions

2.7 Special Cases of Alpha Instruction Execution This section describes the mechanisms that the 21264/EV67 uses to process irregular instructions in the Alpha instruction set, and cases in which the 21264/EV67 processes instructions in a non-intuitive way. 2.7.1 Load Hit Speculation The latency of integer load instructions that hit in the Dcache is three cycles. -

Page 53: Pipeline Timing For Integer Load Instructions

Dcache, even if they are not dependent on the load data. However, if software misses are likely, the 21264/EV67 can still benefit from scheduling the instruction stream for Dcache miss latency. The 21264/EV67 includes a saturating counter that is incremented when load instructions hit and is decremented when load instructions miss. -

Page 54: Floating-Point Store Instructions

IQ. 2.7.3 CMOV Instruction For the 21264/EV67, the Alpha CMOV instruction has three operands, and so presents a special case. The required operation is to move either the value in register Rb or the value from the old physical destination register into the new destination register, based upon the value in Ra. -

Page 55: Memory And I/O Address Space Instructions

The Fbox add pipeline executes floating-point CMOV instructions as two distinct 4-cycle latency operations. 2.8 Memory and I/O Address Space Instructions This section provides an overview of the way the 21264/EV67 processes memory and I/ O address space instructions. The 21264/EV67 supports, and internally recognizes, a 44-bit physical address space that is divided equally between memory address space and I/O address space. -

Page 56: I/O Address Space Load Instructions

Mbox. Internal Architecture 2–28 Load Byte/Word Load Longword No merge No merge No merge Merge up to 32 bytes No merge No merge Alpha 21264/EV67 Hardware Reference Manual Load Quadword No merge No merge Merge up to 64 bytes... -

Page 57: Memory Address Space Store Instructions

Table 2–8 Rules for I/O Address Space Store Instruction Data Merging Merge Register/ Replayed Instruction Byte/Word Longword Quadword Table 2–8 shows some of the following rules: Alpha 21264/EV67 Hardware Reference Manual Memory and I/O Address Space Instructions Store Byte/Word Store Longword No merge No merge... -

Page 58: Maf Memory Address Space Merging Rules

Because all memory transactions are to 64-byte blocks, efficiency is improved by merg- ing several small data transactions into a single larger data transaction. Table 2–9 lists the rules the 21264/EV67 uses when merging memory transactions into 64-byte natu- rally aligned data block transactions. Rows represent the merged instruction in the MAF and columns represent the new issued transaction. -

Page 59: Mbox Order Traps

Load memory to address X Store memory to address X Store memory to address X The 21264/EV67 maintains the default I/O instruction ordering as shown in Table 2–11 (assume address X and address Y are different). Table 2–11 I/O Reference Ordering... -

Page 60: Load-Load Order Trap

When the SYSBUS_MB_ENABLE bit equals 0, the Cbox CSR MB_CNT[3:0] field contains the number of pending uncommitted transac- tions. The counter will increment for each of the following commands: • RdBlk, RdBlkMod, RdBlkI Internal Architecture 2–32 Alpha 21264/EV67 Hardware Reference Manual... -

Page 61: Mb Instruction Processing

When all of the above have occurred and a probe response has been sent to the sys- tem for the marked probe queue entry, instruction execution continues with the instruction after the MB. Alpha 21264/EV67 Hardware Reference Manual I/O Write Buffer and the WMB Instruction Internal Architecture... -

Page 62: Wmb Instruction Processing

Load instructions (HW_LDs) to a virtual page table entry (VPTE) are processed by the 21264/EV67 to avoid litmus test problems associated with the ordering of memory transactions from another processor against loading of a page table entry and the subse- quent virtual-mode load from this processor. -

Page 63: Tb Fill Flow Example Sequence

SYSBUS_MB_ENABLE), the Cbox sig- nals the Ibox to clear IPR scoreboard bit [0]. The 21264/EV67 uses a similar mechanism to process Istream TB misses and fills to the PTE for the Istream. 1. The integer queue issues a HW_LD instruction with VPTE. -

Page 64: Performance Measurement Support-Performance Counters

Performance Measurement Support—Performance Counters 2.13 Performance Measurement Support—Performance Counters The 21264/EV67 provides hardware support for two methods of obtaining program performance feedback information. The two methods do not require program modifica- tion. The first method offers similar capabilities to earlier microprocessor performance counters. -

Page 65: Floating-Point Control Register

UNDZ [60] Underflow to zero. When UNDZ is set together with UNFD, underflow traps are disabled and the 21264/EV67 places a true zero in the destination register. See UNFD, above. [59:58] Dynamic rounding mode. Indicates the rounding mode to be used by an IEEE... -

Page 66: Amask And Implver Instruction Values

Denormal operand. Reserved [47:0] — — Alpha architecture FPCR bit 47 (DNOD) is not implemented by the 21264/EV67. 2.15 AMASK and IMPLVER Instruction Values The AMASK and IMPLVER instructions return processor type and supported architec- ture extensions, respectively. 2.15.1 AMASK The 21264/EV67 returns the AMASK instruction values provided in Table 2–15. -

Page 67: Design Examples

2.16 Design Examples The 21264/EV67 can be designed into many different uniprocessor and multiprocessor system configurations. Figures 2–12 and 2–13 illustrate two possible configurations. These configurations employ additional system/memory controller chipsets. Figure 2–12 shows a typical uniprocessor system with a second-level cache. This sys- tem configuration could be used in standalone or networked workstations. -

Page 68: Typical Multiprocessor Configuration

Internal Architecture 2–40 21272 Core Logic Chipset Control Chip Data Slice Chips Host PCI Host PCI Bridge Chip Bridge Chip 64-bit PCI Bus 64-bit PCI Bus Alpha 21264/EV67 Hardware Reference Manual DRAM Arrays Address Data DRAM Arrays Address Data FM-05574-EV67... -

Page 69: Hardware Interface

This chapter contains the 21264/EV67 microprocessor logic symbol and provides infor- mation about signal names, their function, and their location. This chapter also describes the mechanical specifications of the 21264/EV67. It is organized as follows: • The 21264/EV67 logic symbol •... -

Page 70: 21264/Ev67 Microprocessor Logic Symbol

21264/EV67 Microprocessor Logic Symbol Figure 3–1 21264/EV67 Microprocessor Logic Symbol System Interface SysAddIn_L[14:0] SysAddInClk_L SysAddOut_L[14:0] SysAddOutClk_L SysVref SysData_L[63:0] SysCheck_L[7:0] SysDataInClk_H[7:0] SysDataOutClk_L[7:0] SysDataInValid_L SysDataOutValid_L SysFillValid_L ClkIn_x FrameClk_x EV6Clk_x 3.3 V PLL_VDD Miscellaneous IRQ_H[5:0] ClkFwdRst_H SromData_H Tms_H Trst_L Tck_H Tdi_H PllBypass_H MiscVref... -

Page 71: 21264/Ev67 Signal Names And Functions

3.2 21264/EV67 Signal Names and Functions Table 3–1 defines the 21264/EV67 signal types referred to in this section. Table 3–1 Signal Pin Types Definitions Signal Type Inputs I_DC_REF I_DA I_DA_CLK Outputs O_OD O_OD_TP O_PP O_PP_CLK Bidirectional B_DA_OD B_DA_PP Other Spare... - Page 72 BcDataOutClk_x[3:0] clocks. Tag parity state bit. Tag shared state bit. The 21264/EV67 will write a 1 on this sig- nal line if another agent has a copy of the cache line. Tag valid state bit. If set, this line indicates that the cache line is valid.

- Page 73 Count Description A skew-controlled differential 50% duty cycle copy of the sys- tem clock. It is used by the 21264/EV67 as a reference, or framing, clock. These six interrupt signal lines may be asserted by the system. The response of the 21264/EV67 is determined by the system software.

-

Page 74: Ev67 Signal Descriptions By Function

BiST. If the Icache BiST passes, the pin is deasserted at the end of the BiST operation; otherwise, it remains high. The 21264/EV67 generates a timeout reset signal if an instruc- tion is not retired within one billion cycles. The 21264/EV67 signals the timeout reset event by outputting a 256 GCLK cycle wide pulse on TestStat_H. - Page 75 Provides an external test point to measure phase alignment of the PLL. A skew-controlled differential 50% duty cycle copy of the system clock. It is used by the 21264/EV67 as a reference, or framing, clock. 3.3-V dedicated power supply for the 21264/EV67 PLL.

-

Page 76: Pin Assignments

I_DA Pin Assignments The 21264/EV67 package has 587 pins aligned in a pin grid array (PGA) design. There are 380 functional signal pins, 1 dedicated 3.3-V pin for the PLL, 112 ground VSS pins, and 94 VDD pins. Table 3–4 lists the signal pins and their corresponding pin grid array (PGA) locations in alphabetical order for the signal type. - Page 77 BcData_H_54 AP44 BcData_H_57 AU41 BcData_H_6 BcData_H_62 BB38 BcData_H_65 BcData_H_68 BcData_H_70 BcData_H_73 BcData_H_76 BcData_H_79 BcData_H_81 BcData_H_84 BcData_H_87 Alpha 21264/EV67 Hardware Reference Manual PGA Location Signal Name BcData_H_107 BcData_H_11 BcData_H_112 AC43 BcData_H_115 AG45 BcData_H_118 AM42 BcData_H_120 AP40 BcData_H_123 BB44 BcData_H_126 BA37 BcData_H_14...

- Page 78 NoConnect Reset_L BD16 Spare Spare Spare Spare BC21 SromOE_L BE17 SysAddIn_L_10 BB24 SysAddIn_L_13 BE23 SysAddIn_L_3 BE29 Alpha 21264/EV67 Hardware Reference Manual PGA Location BcData_H_91 BcData_H_94 BcData_H_97 BcDataInClk_H_0 BcDataInClk_H_3 BcDataInClk_H_6 AH44 BcDataOutClk_H_0 J5 BcDataOutClk_H_3 AR43 BcDataOutClk_L_2 BcLoad_L BcTag_H_22 BcTag_H_25 BcTag_H_28 BcTag_H_31...

- Page 79 SysData_L_52 AH38 SysData_L_55 AK38 SysData_L_58 AR39 SysData_L_60 AY38 SysData_L_63 AV34 SysData_L_9 SysDataInClk_H_2 SysDataInClk_H_5 SysDataInValid_L BD22 SysDataOutClk_L_2 AG7 Alpha 21264/EV67 Hardware Reference Manual PGA Location Signal Name SysAddIn_L_6 BD28 SysAddIn_L_9 BC25 SysAddOut_L_1 BE39 SysAddOut_L_12 BC31 SysAddOut_L_2 BD36 SysAddOut_L_5 AY32 SysAddOut_L_8 BB32...

-

Page 80: Pin List Sorted By Pga Location

AJ43 Spare BcData_H_20 AK42 BcData_H_52 BcData_H_21 SysData_L_23 AM40 SysCheck_L_6 ClkIn_H AN41 BcData_H_55 BcData_H_23 AP44 BcData_H_54 Alpha 21264/EV67 Hardware Reference Manual PGA Location SysDataOutClk_L_7 AW39 SysVref BA25 Tdo_H BB20 Trst_L AY20 PGA Location Signal Name BcTag_H_33 BcAdd_H_6 BcData_H_96 BcData_H_65 AA43 BcData_H_111... - Page 81 SysAddIn_L_5 BA33 SysAddOut_L_4 BA43 BcData_H_59 BB10 BcData_H_30 BcData_H_25 BB24 SysAddIn_L_10 BB32 SysAddOut_L_8 BcData_H_27 BcData_H_28 BC17 SromData_H Alpha 21264/EV67 Hardware Reference Manual PGA Location Signal Name Spare AR45 BcData_H_119 AT38 SysData_L_59 AT44 BcCheck_H_14 AU41 BcData_H_57 AV10 SysData_L_28 AV18 IRQ_H_3 AV28 SysAddOut_L_13...

- Page 82 BcDataWr_L BcData_H_97 BcData_H_101 BcTag_H_20 BcTag_H_39 BcData_H_5 SysDataInClk_H_4 BcCheck_H_12 SysData_L_0 BcTag_H_37 SysData_L_32 SysData_L_36 Spare SysData_L_1 BcTagShared_H BcData_H_32 Alpha 21264/EV67 Hardware Reference Manual PGA Location Signal Name BcData_H_91 BC37 BcCheck_H_7 BcDataInClk_H_3 BD12 PllBypass_H NoConnect BD28 SysAddIn_L_6 BD36 SysAddOut_L_2 BD42 BcData_H_61 BE13 IRQ_H_1...

- Page 83 BcData_H_106 BcCheck_H_4 SysData_L_8 SysData_L_41 BcData_H_74 SysData_L_42 BcDataInClk_H_1 BcData_H_12 BcData_H_108 BcData_H_77 BcData_H_109 Spare SysData_L_13 SysData_L_46 BcData_H_78 SysData_L_47 Alpha 21264/EV67 Hardware Reference Manual PGA Location Signal Name BcData_H_38 SysData_L_5 BcTag_H_21 BcTagOE_L SysData_L_34 BcData_H_102 BcData_H_8 BcDataOutClk_H_0 BcDataOutClk_L_0 SysData_L_7 SysCheck_L_4 SysCheck_L_0 SysData_L_40 BcCheck_H_8 BcData_H_41...

-

Page 84: Ground And Power (Vss And Vdd) Pin List

Pin Assignments Table 3–6 lists the 21264/EV67 ground and power (VSS and VDD, respectively) pin list. Table 3–6 Ground and Power (VSS and VDD) Pin List Signal PGA Location AA45 AG43 AR41 AW37 AW41 BA35 BA41 BC45 AB40 AH42 AK40... -

Page 85: Mechanical Specifications

Mechanical Specifications This section shows the 21264/EV67 mechanical package dimensions without a heat sink. For heat sink information and dimensions, refer to Chapter 10. Figure 3–2 shows the package physical dimensions without a heat sink. Figure 3–2 Package Dimensions 04 06 08 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 27.94 mm... -

Page 86: 21264/Ev67 Packaging

21264/EV67 Packaging 21264/EV67 Packaging Figure 3–3 shows the 21264/EV67 pinout from the top view with pins facing down. Figure 3–3 21264/EV67 Top View (Pin Down) 42 40 38 36 34 32 30 28 26 24 22 20 18 16 14 12 10 08 06 04 02 Hardware Interface 3–18... -

Page 87: Ev67 Bottom View (Pin Up)

Figure 3–4 shows the 21264/EV67 pinout from the bottom view with pins facing up. Figure 3–4 21264/EV67 Bottom View (Pin Up) 04 06 08 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44... -

Page 89: Cache And External Interfaces

Bcache port • Interrupts Chapter 3 lists and defines all 21264/EV67 hardware interface signal pins. Chapter 9 describes the 21264/EV67 hardware interface electrical requirements. 4.1 Introduction to the External Interfaces A 21264/EV67-based system can be divided into three major sections: •... - Page 90 GCLK. The period of BcDataOutClk_x[3:0] is a programmable mul- tiple of GCLK. – The Bcache turns the BcDataOutClk_x[3:0] clocks around and returns them to the 21264/EV67 as BcDataInClk_H[7:0]. Likewise, BcTagOutClk_x returns as BcTagInClk_H. – The Bcache interface supports a 64-byte block size.

-

Page 91: System Interface

Figure 4–1 21264/EV67 System and Bcache Interfaces SysAddIn_L[14:0] SysAddInClk_L SysAddOut_L[14:0] SysAddOutClk_L SysVref SysData_L[63:0] SysCheck_L[7:0] SysDataInClk_H[7:0] SysDataOutClk_L[7:0] SysDataInValid_L SysDataOutValid_L SysFillValid_L BcAdd_H[23:4] [23:4] 21264 BcLoad_L BcData_H[127:0] BcCheck_H[15:0] BcDataInClk_H[7:0] BcDataOutClk_ x [3:0] BcDataOE_L BcDataWr_L BcTag_H[42:20] BcTagInClk_H BcTagOutClk_ x BcVref BcTagWr_L BcTagOE_L BcTagValid_H BcTagDir ty_H... -

Page 92: Commands And Addresses

The Cbox contains an 8-entry miss buffer (MAF) and an 8-entry victim buffer (VAF). A miss occurs when the 21264/EV67 probes the Bcache but does not find the addressed block. The 21264/EV67 can queue eight cache misses to the system in its MAF. -

Page 93: Translation Of Internal References To External Interface Reference

WH64 Memory WH64 Memory WH64 I/O ECB Memory ECB I/O MB/WMB TB Fill Flows Alpha 21264/EV67 Hardware Reference Manual Physical Address Considerations BcHit Status and Action Dcache hit, done. Bcache hit, done. Miss, generate RdBlk command. RdBytes, RdLWs, or RdQWs based on size. - Page 94 Note that whenever ENABLE_EVICT[0] is true (in the write-many chain), BC_CLEAN_VICTIM must also be true (in the write-once chain). Otherwise, the 21264/EV67 could respond miss to a probe, rather than hit, before an Evict command has been sent off chip, but after the Evict command has removed a (clean) block from the internal caches and the Bcache.

-

Page 95: Bcache Interface Signals

The 21264/EV67 Cbox provides control signals and an interface for a second-level cache (Bcache). The 21264/EV67 supports a Bcache from 1MB to 16MB, with 64-byte blocks. A 128- bit bidirectional data bus is used for transfers between the 21264/EV67 and the Bcache. -

Page 96: Victim Data Buffer

• Filtering out all probe misses from the 21264/EV67 cache system If a probe misses in the 21264/EV67 cache system (Bcache miss and VAF miss), the 21264/EV67 stalls probe processing with the expectation that a SysDc fill will allocate this block. Because of this, in duplicate tag mode, the 21264/EV67 can never generate a probe miss response. -

Page 97: Ev67-Supported Cache Block States

The 21264/EV67 requires the system to allow only one change to a block at a time. This means that if the 21264/EV67 gains the bus to read or write a block, no other node on the bus should be allowed to access that block until the data has been moved. -

Page 98: Cache Block State Transitions

State Name Description Clean/Shared This 21264/EV67 holds a read-only copy of the block, and at least one other agent in the sys- tem may hold a copy of the block. Upon eviction, the block is not written to memory. Dirty This 21264/EV67 holds a read-write copy of the block, and must write it to memory after it is evicted from the cache. -

Page 99: Using Sysdc Commands

Rdiox commands are noncached references to I/O address space. • Evict and STCChangeToDirty commands are generated by ECB and STx_C instructions, respectively. Table 4–5 shows the system responses to 21264/EV67 commands and 21264/EV67 reactions. Table 4–5 System Responses to 21264/EV67 Commands and 21264/EV67 Reactions 21264/EV67... - Page 100 The original data in the Dcache is replaced with the filled data. The block is not writable, so the 21264/EV67 will retry the store instruc- tion and generate another ChxToDirty class command. To avoid a potential livelock situation, the STC_ENABLE CSR bit must be set.

-

Page 101: Dcache States And Duplicate Tags

Both commands allocate buffers in the VAF (victim address file). This buffer is a coherent part of the 21264/EV67 cache system. Write data control and deallocation of the VAF can be directly controlled by using the SysDc WriteData and ReleaseBuffer commands. -

Page 102: Lock Mechanism

Dcache without interrupting load/store instruction processing in the processor core. 4.6 Lock Mechanism The 21264/EV67 does not contain a dedicated lock register, nor are system components required to do so. When a load-lock (LDx_L) instruction executes, data is accessed from the Dcache or Bcache. -

Page 103: In-Order Processing Of Ldx_L/Stx_C Instructions

4.6.1 In-Order Processing of LDx_L/STx_C Instructions The 21264/EV67 uses the stWait logic in the IQ to ensure that LDx_L/STx_C pairs are issued in order. The stWait logic treats an Ldx_L instruction like Stx instructions. STx_C instructions are always loaded into the IQ with their associate stWait bit set. -

Page 104: Managing Speculative Store Issues With Multiprocessor Systems

0 by clearing a previously set M_CTL[SMC], allowing synchronization between processors. 4.7 System Port The system port is the 21264/EV67’s connection to either a memory or I/O controller or to a shared multiprocessor system controller. System port interface signals are shown in Figure 4–4. -

Page 105: System Port Pins

SysFillValid_L IRQ_H[5:0] 4.7.1 System Port Pins Table 3–1 defines the 21264/EV67 signal types referred to in this section. Table 4–6 lists the system port pin groups along with their type, number, and functional descrip- tion. Table 4–6 System Port Pins... -

Page 106: Programming The System Interface Clocks

System Port 4.7.2 Programming the System Interface Clocks The system forwarded clocks are free running and derived from the 21264/EV67 GCLK. The period of the system forwarded clocks is controlled by three Cbox CSRs, based on the bit-rate ratio (similar to the Bcache bit-rate ratio) except that all transfers are dual-data. -

Page 107: 21264/Ev67-To-System Commands

This section describes the 21264/EV67-to-system commands format and operation. The command, address, ID, and mask bits are transmitted in four consecutive cycles on SysAddOut_L[14:0]. The 21264/EV67 sends the command information in one of the two following modes as selected by the Cbox CSR bit. -

Page 108: Page Hit Mode

M1 and M2 are not asserted simultaneously. Reporting probe results as soon as possible is critical to high-speed operation, so when a result is known the 21264/EV67 uses the earli- est opportunity to send an M signal to the system. M bit assertion can occur either in a valid command or a NZNOP. -

Page 109: 21264/Ev67-To-System Commands Descriptions

Illegal combination Page hit mode + both SysAddOut_L[1:0] are unused Function The 21264/EV67 drives this command on idle cycles during reset. After the clock forward reset period, the first NZNOP is generated and this command is no longer generated. Returns probe status and ID number of the VDB entry holding the requested cache block. - Page 110 System Port Table 4–14 21264/EV67-to-System Commands Descriptions (Continued) Command Command [4:0] ReadBlkMod 10001 ReadBlkI 10010 FetchBlk 10011 ReadBlkSpec 10100 ReadBlkModSpec 10101 ReadBlkSpecI 10110 FetchBlkSpec 10111 ReadBlkVic 11000 ReadBlkModVic 11001 ReadBlkVicI 11010 WrVictimBlk 00100 CleanVictimBlk 00101 Evict 00110 ReadBytes 01000 ReadLWs...

-

Page 111: Programming Inval_To_Dirty_Enable[1:0]

Dcache with a status of dirty/shared, clean/ shared, or clean respectively. Table 4–15 Programming INVAL_TO_DIRTY_ENABLE[1:0] INVAL_TO_DIRTY_ENABLE[1:0] Alpha 21264/EV67 Hardware Reference Manual Cbox Action WH64 instructions are converted to RdModx commands at the interface. Beyond this point, no other agent sees the WH64 instruction. This mode is useful for microprocessors that do not want to support InvalToDirty transac- tions. -

Page 112: Proberesponse Commands (Command[4:0] = 00001)

LDx_L/STx_C sequence. 4.7.5 ProbeResponse Commands (Command[4:0] = 00001) The 21264/EV67 responds to system probes that did not miss with a 4-cycle transfer on SysAddOut_L[14:0]. As shown in Table 4–14, the Command[4:0] field for a ProbeRe- sponse command equals 00001. -

Page 113: Sysack And 21264/Ev67-To-System Commands Flow Control

4.7.6 SysAck and 21264/EV67-to-System Commands Flow Control Controlling the flow of 21264/EV67-to-system commands is a joint task of the 21264/ EV67 and the system. The flow is controlled using the A bit, which is asserted by the system, and the Cbox CSR SYSBUS_ACK_LIMIT[4:0] counter. -

Page 114: System-To-21264/Ev67 Commands

System Port • There is no mechanism for the system to reject a 21264/EV67-to-system command. ProbeResponse, VDBFlushReq, NOP, NZNOP, and RdBlkxSpec (with a clear RV bit) commands do not require a response from the system. Systems must provide adequate resources for responses to all probes sent to the 21264/EV67. -

Page 115: System-To-21264/Ev67 Probe Commands Fields Descriptions

Probe type and next tag state (see Tables 4–21 and 4–22). SysDc[4:0] Controls data movement in and out of the 21264/EV67. See Table 4–24 for a list of data movement types. Clears the victim or I/O write buffer (IOWB) valid bit specified in ID[3:0]. -

Page 116: Data Transfer Commands (Two Cycles)

21264/EV67 queue. The 21264/EV67 removes probes from the internal probe queue when the probe response is sent. The 21264/EV67 expects to hit in cache on a probe response, so it always fetches a cache block from the Bcache on system probes. This can become a performance prob- lem for systems that do not monitor the Bcache tags, so the 21264/EV67 provides Cbox CSR PRB_TAG_ONLY[0], which only accesses Bcache tags for system probes. -

Page 117: Sysdc[4:0] Field Description

SysDc command. If the SysDc command allows the 21264/EV67 to retire an instruction before an MB, or allows the 21264/EV67 itself to retire an MB (SysDc is MBDone), that MB will not complete until the probe is exe- cuted. -

Page 118: Data Movement In And Out Of The 21264/Ev67

(the last cycle) to the delivery of the SysDc command to the processor. 4.7.8 Data Movement In and Out of the 21264/EV67 There are two modes of operation for data movement in and out of the 21264/EV67: fast mode and fast mode disable. The data movement mode is selected using Cbox CSR FAST_MODE_DISABLE[0]. -

Page 119: Fast Data Mode

Because there is a bandwidth difference between address (4 cycles) and data (8 cycles) transfers, the 21264/EV67 tries to fully use fast data mode by delaying the next SysAddOut write command until a fast data mode slot is available on the SysDataOut bus. -

Page 120: Fast Transfer Timing Example

2. The 21264/EV67 drivers stay off until the last piece of fill data is received, or a new SysDc write command overrides the current SysDc fill command. It is the responsi- bility of the external system to schedule SysDc fill or write commands so that there is no conflict on the SysData bus. -

Page 121: Fast Data Disable Mode

21264/EV67 is preceded by a SysDc command. The 21264/EV67 drivers are only enabled for the duration of an 8-cycle transfer of data from the 21264/ EV67 to the system. Systems must ensure that there is no overlap of enabled drivers and that there is adequate settle time on the SysData bus. -

Page 122: Sysdatainvalid_L And Sysdataoutvalid_L

BPHASE, before the start of a write transfer, and disabled on the succeeding GCLK BPHASE at the end of the write transfer. The write data is enveloped by the 21264/ EV67 drivers to guarantee that every data transfer has the same data valid window. -

Page 123: Sysfillvalid_L

21264/EV67. The system designer may tie this pin to the asserted state (validating all fills), or use it to enable or cancel fills as they progress. The 21264/EV67 samples SysFillValid_L at D1 time (when the 21264/EV67 samples the second data cycle). -

Page 124: Data Wrapping

SysAddOut_L[5:3] STByte/Word The order in which data is provided to the 21264/EV67 (for a memory or I/O fill) or moved from the 21264/EV67 (write victims or probe reads) can be determined by the system. The system chooses to reflect back the same low-order address bits and the cor- responding octaword found in the SysAddOut field or the system chooses any other starting point within the block. -

Page 125: System Wrap And Deliver Data

QW pointed to by the 21264/EV67; however, some systems may find it more beneficial to begin the transfer elsewhere. The system must always indicate the starting point to the 21264/EV67. The wrap order for subsequent QWs is interleaved. -

Page 126: Nonexistent Memory Processing

I/O space. However, unlike the earlier Alpha microprocessor implementa- tions, the 21264/EV67 can generate speculative references to memory space. To accom- modate the speculative nature of the 21264/EV67, the system must not generate or lock error registers because of speculative references. The 21264/EV67 translates all mem-... -

Page 127: Ev67 Commands With Nxm Addresses And System Response

21264/EV67 provides an all ones pattern as a signature for this bug. The NXM block is not cached in the Dcache or Bcache. -

Page 128: Ordering Of System Port Transactions

21264/EV67 Command NXM Address System/21264/EV67 Response CleanToDirty ChangeToDirty commands to NXM space are impossible in the 21264/EV67 because all SharedToDirty NXM references to memory space are atomically filled with an Invalid cache status. STCChangeToDirty InvalToDirty InvalToDirty commands are not speculative, so InvalToDirty commands to NXM space InvalToDirtyVic indicate an operating system error. -

Page 129: 21264/Ev67 Response To System Probe And In-Flight Command Interaction

This case assumes that a SetDirty command has been sent to the system environment SharedToDirty because of a store instruction that hit in the 21264/EV67 caches and that another processor has performed a load/store instruction to the same address. The 21264/EV67 provides MAF hit information so that the system can correctly respond to the Set/Dirty command. -

Page 130: System Probes And Sysdc Commands

Bcache size can be 1MB, 2MB, 4MB, 8MB, or 16MB. The Bcache port has a 144-bit data bus that is used for data transfers between the 21264/EV67 and the Bcache. All Bcache control and address signal lines are clocked synchronously on Bcache clock cycle boundaries. -

Page 131: Bcache Port Pins

The Bcache supports the following multiples of the GCLK period: 1.5X (dual-data mode only), 2X, 2.5X, 3X, 3.5X, 4X, 5X, 6X, 7X, and 8X. However, the 21264/EV67 imposes a maximum Bcache clock period based on the SYSCLK ratio. Table 4–35 lists the range of maximum Bcache clock periods. -

Page 132: Bcache Clocking

Int_Data_BcClk output Bcache tag parity bit BcTagInClk_H input Int_Data_BcClk output Bcache tag shared bit BcTagInClk_H input Int_Data_BcClk output Bcache tag valid bit BcTagInClk_H input Input reference voltage for tag data Int_Index_BcClk Bcache data write enable Alpha 21264/EV67 Hardware Reference Manual... -

Page 133: Setting The Period Of The Cache Clock

Table 4–37 BC_CPU_CLK_DELAY[1:0] Values BC_CPU_CLK_DELAY[1:0] Value In the 21264/EV67 topology, the index pins are loaded by all the SSRAMs, while the clock and data pins see a limit load. This arrangement requires a relatively large amount of delay between the index pins and the Bcache clock pins to meet the setup constraints at the SSRAMs. -

Page 134: Program Values To Set The Cache Clock Period (Single-Data)

With the exception of the 2.5X-SD and 3.5X-SD cases, the clock waveform generated by the 21264/EV67 for the forwarded clocks has a 50-50 duty cycle. In the 2.5X-SD case, the 21264/EV67 produces an asymmetric clock that is high for two GCLK phases and low for three phases. -

Page 135: Bcache Transactions

The following three sections describe these Bcache transactions. 4.8.3.1 Bcache Data Read and Tag Read Transactions The 21264/EV67 always reads four pieces of data (64 bytes) from the Bcache during a data read transaction, and always interrogates the tag array on the first cycle. Once started, data read transactions are never cancelled. -

Page 136: Bcache Data Write Transactions

SSRAM setup/hold Bcache address latch requirements, a Bcache read command proceeds through the 21264/EV67 Cbox as follows: 1. When the 21264/EV67 clocks out the first address value on the Bcache index pins with the appropriate Int_Add_BcClk value, the Cbox loads the values of Cbox CSR... -

Page 137: Bubbles On The Bcache Data Bus

3. The difference between the data delivery (Int_Data_BcClk) and forwarded clocks out provides the setup for the data at the Bcache data flip-flop. 4. For Bcache writes, the 21264/EV67 drivers are enabled on the GCLK BPHASE preceding the start of a write transfer, and disabled on the succeeding GCLK BPHASE at the end of a write transfer. - Page 138 The minimum spacing required between the read and write indices at the data/tag pins, expressed as GCLK cycles. wr_rd The minimum spacing required between the write and read indices at the data/tag pins, expressed as GCLK cycles. Cache and External Interfaces 4–50 Alpha 21264/EV67 Hardware Reference Manual...

-

Page 139: Pin Descriptions

4.8.4.1 BcAdd_H[23:4] The BcAdd_H[23:4] pins are high drive outputs that provides the index for the Bcache. The 21264/EV67 supports Bcache sizes of 1MB, 2MB, 4MB, 8MB, and 16MB. Table 4–42 lists the values to be programmed into Cbox CSRs BC_ENABLE[0] and BC_SIZE[3:0] to support each size of the Bcache. -

Page 140: Bcache Control Pins

Bcache Port When the Cbox CSR BC_BANK_ENABLE[0] is not set, the unused BcAdd_H[23:4] pins are tied to zero. For example, when configured as a 4MB cache, the 21264/EV67 never changes BcAdd_H[23:22] from logic zero, and when BC_BANK_ENABLE[0] is asserted, the 21264/EV67 drives the complement of the MSB index on the next higher BcAdd_H pin. -

Page 141: Bcdatainclk_H And Bctaginclk_H

The 21264/EV67 internally synchronizes the data to its GCLK with clock forward receive circuitry similar to that in the system interface. -

Page 142: Bcache Banking

Bcache banking is possible by decoding the index MSB (as determined by Cbox CSR BC_SIZE[3:0]) and asserting Cbox CSR BC_BANK_ENABLE[0]. To facilitate bank- ing, the 21264/EV67 provides the complement of the MSB bit in the next higher unused index bit. For example, when configured as an 8MB cache with banking enabled, the 21264/EV67 drives the inversion of PA[22] on BcAdd_H[23] for use as a chip enable in a banked configuration. -

Page 143: Internal Processor Registers

This chapter describes 21264/EV67 internal processor registers (IPRs). They are sepa- rated into the following circuit logic groups: Ebox, Ibox, Mbox, and Cbox. The gray areas in register figures indicate reserved fields. Bit ranges that are coupled with the field name specify those bits in that named field that are included in the IPR. - Page 144 1010 0100 DTB_ASN0 0010 0101 DTB_ASN1 1010 0101 MM_STAT 0010 0111 — M_CTL 0010 1000 DC_CTL 0010 1001 DC_STAT 0010 1010 Alpha 21264/EV67 Hardware Reference Manual MT/MF Latency Issued from Ebox MFPR Access Pipe (Cycles) — — — — —...

-

Page 145: Ebox Iprs

CC register may be written and its associated counter enabled and dis- abled. Figure 5–2 shows the cycle counter control register. Figure 5–2 Cycle Counter Control Register CC_ENA COUNTER[31:4] Alpha 21264/EV67 Hardware Reference Manual Score- Index Board (Binary) -

Page 146: Virtual Address Register - Va

When set, this bit allows the cycle counter to increment. CC[31:4] may be written by way of this field. Write transactions to CC_CTL result in CC[3:0] being cleared. — — Alpha 21264/EV67 Hardware Reference Manual LK99-0010A 3 2 1 LK99-0014A... -

Page 147: Virtual Address Format Register - Va_Form

Figure 5–5 Virtual Address Format Register (VA_48 = 0, VA_FORM_32 = 0) VPTB[63:33] VA[42:13] Figure 5–6 shows VA_FORM when VA_CTL(VA_48) equals 1 and VA_CTL(VA_FORM_32) equals 0. Alpha 21264/EV67 Hardware Reference Manual Type Description Virtual Page Table Base. See the VA_FORM register section for details. -

Page 148: Ibox Iprs

ITB_TAG and ITB_PTE registers are written into the ITB entry. The specific ITB entry that is written is determined by a round-robin algorithm; the algorithm writes to entry number 0 as the first entry after the 21264/EV67 is reset. Figure 5–8 shows the ITB tag array write register. -

Page 149: Itb Invalidate All Process (Asm=0) Register - Itb_Iap

Because the Icache is virtually indexed and tagged, it is normally not nec- essary to flush the Icache when paging. Therefore, a write to ITB_IS will not flush the Icache. Alpha 21264/EV67 Hardware Reference Manual Ibox IPRs 12 11 10... -

Page 150: Profileme Pc Register - Pmpc

Figure 5–12 Exception Address Register PC[63:2] Internal Processor Registers 5–8 Type Description Address of the profiled instruction Read as zero Indicates that the PC field contains a physical-mode PALmode address Alpha 21264/EV67 Hardware Reference Manual 2 1 0 LK99-0018A 2 1 0 LK99-0018A... -

Page 151: Instruction Virtual Address Format Register - Iva_Form

IER field and bit[0] corresponds to the processor mode field. A HW_MFPR instruction to this register returns the values in both fields. Figure 5–16 shows the interrupt enable and current processor mode register. Alpha 21264/EV67 Hardware Reference Manual 38 37 Internal Processor Registers... -

Page 152: Software Interrupt Request Register - Sirr

Performance Counter Interrupt Enables Software Interrupt Enables AST Interrupt Enable When set, enables those AST interrupt requests that are also enabled by the value in ASTER. — — Current Mode Kernel Executive Supervisor User — — Alpha 21264/EV67 Hardware Reference Manual LK99-0022A... -

Page 153: Interrupt Summary Register - Isum

Usage of ISUM in performance monitoring is described in Section 6.10. Figure 5–18 shows the interrupt summary register. Figure 5–18 Interrupt Summary Register EI[5:0] PC[1:0] SI[15:1] ASTU ASTS ASTE ASTK Alpha 21264/EV67 Hardware Reference Manual 29 28 Type Description — — Software Interrupt Requests — — Internal Processor Registers... -

Page 154: Hardware Interrupt Clear Register - Hw_Int_Clr

ASTRR bits and whether the processor mode value held in the IER_CM register is greater than or equal to the value for the mode. — — 33 32 31 30 29 28 27 26 25 Alpha 21264/EV67 Hardware Reference Manual LK99-0025A... -

Page 155: Exception Summary Register - Exc_Sum

Dstream exceptions: The REG field contains the register number of either the source specifier (for stores) or the destination specifier (for loads) of the instruction that triggered the trap. Figure 5–20 shows the exception summary register. Alpha 21264/EV67 Hardware Reference Manual Type Description —... -

Page 156: Exception Summary Register

I-stream virtual address is latched in the EXC_ADDR register or the VA register. If BAD_IVA is clear, EXC_ADDR contains the address; if BAD_IVA is set, VA con- tains the address. Alpha 21264/EV67 Hardware Reference Manual LK99-0026A... -

Page 157: Pal Base Register - Pal_Base

The Ibox control register (I_CTL) is a read-write register that controls various Ibox functions. Its contents are cleared by chip reset. Figure 5–22 shows the Ibox control register. Alpha 21264/EV67 Hardware Reference Manual Type Description Destination register of load or operate instruction that triggered the trap OR source register of store that triggered the trap. -

Page 158: Ibox Control Register

Virtual Page Table Base. See Section 5.1.5 for details. This is a read-only field that supplies the revision ID number for the 21264/EV67 part. 21264/EV67 pass 2.2.2 ID is 001110 21264/EV67 pass 2.2.3 ID is 001111 21264/EV67 pass 2.4 ID is 001100 21264/EV67 pass 2.5 ID is 000111... - Page 159 SL_RCV [14] SL_XMIT [13] [12] BP_MODE[1:0] [11:10] Alpha 21264/EV67 Hardware Reference Manual Type Description RW,0 Machine check enable — set to enable machine checks. RW,0 The stWait table is used to reduce load/store order traps. When set, the stWait table is cleared after 64K cycles. When clear, the stWait table is cleared after 16K cycles.

-

Page 160: Ibox Status Register - I_Stat

PALshadow Register Enable. Enables access to the PALshadow registers. If SDE[1] is set, R4-R7 and R20-R23 are used as PALshadow registers. SDE[0] does not affect 21264/EV67 operation. RW,0 Super Page Mode Enable. Identical to the SPE bits in the Mbox M_CTL SPE[2:0]. See Section 5.3.9. -

Page 161: Ibox Status Register

Extent Type Reserved [63:41] [40] [39] [38] Alpha 21264/EV67 Hardware Reference Manual 41 40 34 33 32 Description Reserved for Compaq. ProfileMe Mispredict Trap. If the I_STAT[TRP] bit is set, this bit indicates that the profiled instruc- tion caused a mispredict trap. JSR/JMP/RET/COR or HW_JSR/... - Page 162 This bit indicates that the Icache encountered a parity error on instruction fetch. When a parity error is detected, the Icache is flushed, a replay trap back to the address of the error instruction is generated, and a correctable read interrupt is requested. Reserved for Compaq. Alpha 21264/EV67 Hardware Reference Manual...

-

Page 163: Icache Flush Register - Ic_Flush

IPR Index Bit A HW_MFPR from this register returns the values in all of its component bit fields. Figure 5–24 shows the process context register. Alpha 21264/EV67 Hardware Reference Manual , this register is selected. Bits [4:0] of the Register Field... -

Page 164: Process Context Register

Kernel Mode AST enable register—used to individually enable each of the four AST interrupt requests. The bit order with this field is: User Mode Supervisor Mode Executive Mode Kernel Mode — — Alpha 21264/EV67 Hardware Reference Manual 2 1 0 LK99-0032A... -

Page 165: Performance Counter Control Register - Pctr_Ctl

Figure 5–25 Performance Counter Control Register SEXT(PCTR0_CTL[47]) PCTR0[19:0] PM_STALLED PM_KILLED_BM PCTR1[19:0] SL1[1:0] Alpha 21264/EV67 Hardware Reference Manual Type Description RW,1 Floating-point enable—if clear, floating-point instructions generate FEN exceptions. This bit is set by hardware on reset. Process performance counting enable. -

Page 166: Performance Counter Control Register Fields Description

Reads to this field return zero. Writes to this field are ignored. Selector 0. 0 = Aggregate counting mode 1 = ProfileMe mode See Table 5–16 for more information. Selector 1. Selects counter PCTR0 and PCTR1 modes. See Table 5–16 for more information. Alpha 21264/EV67 Hardware Reference Manual... -

Page 167: Mbox Iprs

Figure 5–26 shows the DTB tag array write registers 0 and 1. Figure 5–26 DTB Tag Array Write Registers 0 and 1 48 47 VA[47:13] Alpha 21264/EV67 Hardware Reference Manual Profiled instruction valid. When set, indicates a nontrapping profiled instruction retired valid. When clear, indicates that a nontrapping profiled instruction was killed after the cycle in which it was mapped. -

Page 168: Dtb Pte Array Write Registers 0 And 1 - Dtb_Pte0, Dtb_Pte1

HW_LD and HW_ST instructions. Figure 5–28 shows the DTB alternate processor mode register. Figure 5–28 DTB Alternate Processor Mode Register ALT_MODE[1:0] Internal Processor Registers 5–26 Alpha 21264/EV67 Hardware Reference Manual 9 8 7 LK99-0036A 2 1 0 LK99-0037A... -

Page 169: Dstream Tb Invalidate All Process (Asm=0) Register - Dtb_Iap

The DTB entry’s virtual page number matches DTB_IS[47:13] and its ASM bit is set. Figure 5–29 shows the Dstream translation buffer invalidate single registers. Figure 5–29 Dstream Translation Buffer Invalidate Single Registers 48 47 VA[47:13] Alpha 21264/EV67 Hardware Reference Manual Type Description — — Alt_Mode:... -

Page 170: Dstream Tb Address Space Number Registers 0 And 1 - Dtb_Asn0,1

Opcode of the instruction that caused the error. HW_LD is displayed as 3 and HW_ST is displayed as 7. This bit is set when a fault-on-write error occurs during a write transaction and PTE[FOW] was set. Alpha 21264/EV67 Hardware Reference Manual LK99-0038A 4 3 2 LK99-0039A... -

Page 171: Mbox Control Register - M_Ctl

Figure 5–32 shows the Mbox control register. Figure 5–32 Mbox Control Register SMC[1:0] SPE[2:0] Alpha 21264/EV67 Hardware Reference Manual Type Description This bit is set when a fault-on-read error occurs during a read transaction and PTE[FOR] was set. -

Page 172: Dcache Control Register - Dc_Ctl

(see Section 2.6.2) to behave like normal prefetches. Place 21264/EV67 in periodic conservative mode by using an 8-bit counter to add by 4 each time a branch mispredict happens and sub- tract by one each time a conditional branch retires. Enter conserva- tive mode if the MSB of the counter is set. -

Page 173: Dcache Status Register – Dc_Stat

The Dcache status register (DC_STAT) is a read-write register. If a Dcache tag parity error or data ECC error occurs, information about the error is latched in this register. Figure 5–34 shows the Dcache status register. Alpha 21264/EV67 Hardware Reference Manual Type Description —... -

Page 174: Cbox Csrs And Iprs

The Cbox configuration registers are split into three shift register chains: • The hardware allocates 367 bits for the WRITE_ONCE chain, of which the 21264/ EV67 uses 304 bits. During hardware reset (after BiST), 367 bits are always shifted into the WRITE_ONCE chain from the SROM, MSB first, so that the unused bits are shifted out the end of the WRITE_ONCE chain. -

Page 175: Cbox Data Register - C_Data

Many CSRs are duplicated for ease of hardware implementation. These CSRs are indicated in italics. They must be written with values that are identical to the values written to the original CSRs. Alpha 21264/EV67 Hardware Reference Manual Description — Cbox data register. A HW_MTPR instruction to this register causes six bits of data to be placed into a serial shift register. -

Page 176: Cbox Write_Once Chain Order

2.0X 0100 2.5X 1000 3.0X Enable duplicate tag mode in the 21264/EV67. Enable probe-tag only mode in the 21264/EV67. When asserted, disables fast data movement mode. Enables RdVictim mode on the pins. Duplicate CSR. Enable inhibition of incrementing acknowledge counter for RdVic commands. - Page 177 Asserted when (BC_LATE_WRITE_NUM > 3) or ((BC_LATE_WRITE_NUM = 3) and (BC_CPU_LATE_WRITE_NUM > 1)). Enables the update of the 21264/EV67 Bcache tag outputs based on the falling edge of the forwarded clock. Internal Processor Registers Cbox CSRs and IPRs 5–35...

- Page 178 Internal Processor Registers 5–36 Description Enables the update of the 21264/EV67 Bcache tag outputs based on the rising edge of the forwarded clock. Enable clock forwarding on the Bcache interface. Initial value for the Bcache clock forwarding unload pointer FIFO.

- Page 179 BC_DDM_RISE_EN BC_CLKFWD_ENABLE BC_RCV_MUX_CNT_PRESET[1:0] SYS_CLK_DELAY[0:1] SYS_DDMR_ENABLE SYS_DDMF_ENABLE SYS_DDM_FALL_EN SYS_DDM_RISE_EN SYS_CLKFWD_ENABLE SYS_RCV_MUX_CNT_PRESET[0:1] CFR_GCLK_DELAY[0:3] CFR_EV6CLK_DELAY[0:2] Alpha 21264/EV67 Hardware Reference Manual Description Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR. Duplicate CSR.

-

Page 180: Cbox Write_Many Chain Description

CSR to program the system forwarded clock shift register load val- ues. CSR to program the system forwarded clock b-phase enables. CSR to program the ratio between frame clock and system for- warded clock. Fifth SYSDC_DELAY bit. Alpha 21264/EV67 Hardware Reference Manual... -

Page 181: Write_Many Chain Write Transaction Example

; Initialize the Bcache configuration in the Cbox BC_ENABLE = 1 INIT_MODE = 0 BC_SIZE = 0xF INVALID_TO_DIRTY_ENABLE = 3 ENABLE_EVICT = 1 Alpha 21264/EV67 Hardware Reference Manual Description Enable the Bcache Enable initialize mode Bcache size Duplicate CSR Duplicate CSR... - Page 182 ; shift in 6 bits ; decrement R0 ; done if R0 is zero ; align next 6 bits ; continue shifting ; wait until last shift ; predicts fall thru ; predict infinite loop ; nop ; nop Alpha 21264/EV67 Hardware Reference Manual...

-

Page 183: Cbox Read Register (Ipr) Description

DSTREAM_DC_ERR, only bits 6:19 are valid. If C_STAT value is DOUBLE_BIT_ERROR and SKEWED_FILL_MODE[0] is set, then C_ADDR is X. Alpha 21264/EV67 Hardware Reference Manual Error Status Either no error, or error on a speculative load, or a Bcache vic- tim read due to a Dcache/Bcache miss... -

Page 185: Privileged Architecture Library Code

Privileged Architecture Library Code This chapter describes the 21264/EV67 privileged architecture library code (PALcode). The chapter is organized as follows: • PALcode description • PALmode environment • Required PALcode function codes • Opcodes reserved for PALcode • Internal processor register access mechanisms •... -

Page 186: Palmode Environment

There are a few extra instructions that are only available in PALmode, and will cause a dispatch to the OPCDEC PALcode entry point if attempted while not in PALmode. The Alpha architecture allows some flexibility in what these special PALmode instructions do. In the 21264/EV67, the special PALmode-only instructions perform the following func- tions: •... -

Page 187: Required Palcode Function Codes

When executing in PALmode, there are certain restrictions for using the privileged instructions because PALmode gives the programmer complete access to many of the internal details of the 21264/EV67. Refer to Section 6.4 for information on these spe- cial PALmode instructions. -

Page 188: Hw_St Instruction

Access checks for FOR, FOW, read and write protection. Access checks use DTB_ ALT_MODE IPR. Access length is longword. Access length is quadword. Holds a 12-bit signed byte displacement. 26 25 21 20 16 15 Alpha 21264/EV67 Hardware Reference Manual DISP FM-05654.AI4 DISP FM-05654.AI4... -

Page 189: Hw_Ret Instruction

JSR_COROUTINE, the stack can be managed by setting the HINT bits accordingly. See Section D.25 for more information about the HW_RET instruction. Figure 6–3 shows the HW_RET instruction format. Alpha 21264/EV67 Hardware Reference Manual Opcodes Reserved for PALcode Description The opcode value. -

Page 190: Hw_Mfpr And Hw_Mtpr Instructions

Stall until the HW_RET instruction is retired or aborted If instructions beyond the HW_RET have been issued out of order, they will be killed and refetched. Holds a 13-bit signed longword displacement. 16 15 INDEX SCBD_MASK FM-05657.AI4 Alpha 21264/EV67 Hardware Reference Manual DISP FM-05656.AI4... -

Page 191: Internal Processor Register Access Mechanisms

Implicit writers are instructions that may write a value into the IPR as a side effect of execution. For example, a load instruction that generates an access violation is an implicit writer of the VA, MM_STAT, and EXC_ADDR IPRs. In the 21264/ EV67, only instructions that generate an exception will act as implicit IPR writers. -

Page 192: Ipr Scoreboard Bits

Software was required to schedule HW_MTPR and HW_MFPR instructions for each machine’s pipeline organization in order to ensure correct behavior. This software scheduling task is more difficult in the 21264/EV67 because the Ibox performs dynamic scheduling. Hence, eight extra scoreboard bits are used within the IQ to help maintain correct IPR access order. -

Page 193: Hardware Structure Of Implicitly Written Iprs

PALcode routine reordered. invoked by the exception associated with the writer, then ordering is guaran- teed. Alpha 21264/EV67 Hardware Reference Manual Internal Processor Register Access Mechanisms First Instruction Explicit Reader Explicit Writer A variety of mechanisms are be reordered. used to ensure order: scoreboard bits to stall issue of reader;... -

Page 194: Correct Ordering Of Explicit Writers Followed By Implicit Readers

See Appendix D for a listing of cases where this method is recommended. Privileged Architecture Library Code 6–10 First Instruction Reader reads second Scoreboard bits stall second register. Writer cannot writer in map stage until first write second register writer is retired. until it is retired. Alpha 21264/EV67 Hardware Reference Manual... -

Page 195: Correct Ordering Of Explicit Readers Followed By Implicit Writers

HW_MFPR and the LD. 6.6 PALshadow Registers The 21264/EV67 contains eight extra virtual integer registers, called shadow registers, which are available to PALcode for use as scratch space and storage for commonly used values. These registers are made available under the control of the SDE[1] field of the I_CTL IPR. -

Page 196: Status Flags

6.7.1 Status Flags The FPCR status bits in the 21264/EV67 are set with PALcode assistance. Floating- point exceptions, for which the associated FPCR status bit is clear or for which the associated trap is enabled, result in a hardware trap to the ARITH PALcode routine. The EXC_SUM register contains information to allow this routine to update the FPCR appropriately, and to decide whether to report the exception to the operating system. -

Page 197: Palcode Exception Entry Points

DTBM_SINGLE Fault DFAULT Fault OPCDEC Fault IACV Fault Alpha 21264/EV67 Hardware Reference Manual to 7F inclusive and 3F inclusive, and IER_CM[CM] is not equal to the kernel Offset Description Dstream TB miss on virtual page table entry fetch. Use three- level flow. -

Page 198: Translation Buffer (Tb) Fill Flows

Interrupt 6.9 Translation Buffer (TB) Fill Flows This section shows the expected PALcode flows for DTB miss and ITB miss. Familiar- ity with 21264/EV67 IPRs is assumed. 6.9.1 DTB Fill Figure 6–5 shows single-miss DTB instructions flow. Figure 6–5 Single-Miss DTB Instructions Flow Example Figure 6–5 shows single-miss DTB instructions flow. - Page 199 PTE from (I) it will see the new data. Processor I Wr Data Wr PTE Alpha 21264/EV67 Hardware Reference Manual Translation Buffer (TB) Fill Flows ; (0,4,2,6) (0L) write pte0 ; (3,7,1,5) (1L) write pte1 ;...

-

Page 200: Itb Fill

This behavior is functionally correct because DTB loads that tag-match an existing DTB entry are ignored by the 21264/EV67 and the second DTB miss execution will load exactly the same entry as the first. 6.9.2 ITB Fill Figure 6–6 shows the ITB miss instructions flow. -

Page 201: Performance Counter Support

6.10 Performance Counter Support The 21264/EV67 provides hardware support for two methods of obtaining program performance feedback information. The two methods do not require program modifica- tion. Instead, performance monitoring utilities make calls to the PALcode to set up the counters and contain interrupt handlers that call PALcode to retrieve the collected data. -

Page 202: Aggregate Mode Programming Guidelines

Relevant Fields PMPC All fields IER_CM PCEN[1:0] ISUM PC[1:0] I_CTL SPCE, PCT0_EN, PCT1_EN I_STAT OVR, ICM, TRAP-TYPE, LSO, TRP, MIS PCTX PPCE PCTR_CTL All fields Alpha 21264/EV67 Hardware Reference Manual Described in Section 5.2.6 5.2.9 5.2.11 5.2.15 5.2.16 5.2.21 5.2.22... -

Page 203: Operation

The handler may also choose to write the counters to control the frequency of inter- rupts. Table 6–10 Aggregate Mode Returned IPR Contents PCTR_CTL Alpha 21264/EV67 Hardware Reference Manual Performance Counter Support Field Contents PCTR0[19:0]... -

Page 204: Aggregate Counting Mode Description

I_CTL[PCT0_EN] and either I_CTL[SPCE] or PCTX[PPCE]. On overflow, an inter- rupt is triggered as ISUM[PC0] if enabled via IER_CM[PCEN0]. The 21264/EV67 can retire up to 11 instructions per cycle, which exceeds PCTR0’s maximum increment of 8 per cycle. However, no retires go uncounted because the 21264/EV67 cannot sustain 11 retires per cycle, and the 21264/EV67 corrects PCTR0 in subsequent cycles. -

Page 205: Operation

SL0 & SL1. 4. End window The last cycle of the window depends on whether the instruction traps, retires, aborts, and/or is squashed by the fetcher. Alpha 21264/EV67 Hardware Reference Manual Performance Counter Support New Instructions CMOV1 Ra, oldRc CMOV2 newRc1, Rb... -

Page 206: Profileme Mode Returned Ipr Contents

Branch direction if instruction is a conditional branch. Instruction stalled for at least one cycle between fetch and map stages of pipeline. Instruction killed during or before cycle in which it was mapped. Counter 0 value. Counter 1 value. Alpha 21264/EV67 Hardware Reference Manual... -

Page 207: Profileme Counting Mode Description

Counts cycles that a profiled instruction delayed the retire pointer advance during the ProfileMe window. The 21264/EV67 tracks instructions in the pipeline by allocating them "inums" near the front of the pipeline. All inums are retired in the order in which they were allocated at the end of the pipeline. -

Page 208: Counter Modes For Profileme Mode

Table 6–14 ProfileMe Mode PCTR_CTL Input Select Fields SL0[4] SL1[3:2] PCTR0 Privileged Architecture Library Code 6–24 PCTR1 Retired instructions Cycle counting Cycle counting Inum retire delay Retired instructions Bcache miss or long latency probes Cycle counting Mbox replay traps Alpha 21264/EV67 Hardware Reference Manual... -

Page 209: Initialization And Configuration

GCLK frequency during sleep mode. 7.1 Power-Up Reset Flow and the Reset_L and DCOK_H Pins The 21264/EV67 reset sequence is triggered using the two input signals Reset_L and DCOK_H in a sequence that is described in Section 7.1.1. After Reset_L is deasserted,... -

Page 210: Power-Up Reset Flow And The Reset_L And Dcok_H Pins

Enough time for Reset_L to propagate through 5 stages of RESET synchronizer (clocked by the inter- nal framing clock, which is driven by EV6Clk_x). Worst case through Pass 3 of the 21264/EV67 would be 5x8x8 = 320 GCLK cycles, because Y Min = 1 FrameClk cycle. -

Page 211: Power Sequencing And Reset State For Signal Pins

BcDataWr_L Tristated BcLoad_L Tristated BcTag_H[42:20] Tristated BcTagDirty_H Tristated System Interface IRQ_H[5:0] NA (input) SysAddIn_L[14:0] NA (input) SysAddInClk_L NA (input) Alpha 21264/EV67 Hardware Reference Manual RAMP1 RAMP2 WAIT_ClkFwdRst0 no min Signal BcTagInClk_H BcTagOE_L BcTagOutClk_x BcTagParity_H BcTagShared_H BcTagValid_H BcTagWr_L BcVref SysDataInClk_H[7:0] SysDataInValid_L... -

Page 212: Clock Forwarding And System Clock Ratio Configuration

Prior to DCOK_H being asserted, the logic internal to the 21264/EV67 is being reset and the internal clock network is running (either clocked by the PLL VCO, which is at a nomi- nal speed, or by ClkIn_H, if the PLL is bypassed). -

Page 213: Pin Signal Names And Initialization State

IRQ_H pins. The IRQ_H pins are sampled on the rising edge of DCOK_H, during which time the 21264/EV67 is in reset and is not generating any sys- tem activity. During normal operation, the IRQ_H pins supply interrupt requests to the 21264/EV67. -

Page 214: Pll Ramp Up

PLL ramp up sequence. Ramping up of the PLL is required to guarantee that the dynamic change in frequency will not cause the supply on the 21264/ EV67 to fall due to the supply loop inductance. Clock control circuitry steps GCLK from power-up/reset clocking to 1/16 and finally normal operating frequency. -

Page 215: Clock Forward Reset And System Interface Initialization

As BiST completes, the TestStat_H pin is held low for 16 GCLK cycles. Then, if BiST succeeds, the pin remains low. Otherwise, it is asserted. After successfully completing BiST, the 21264/EV67 then performs the SROM load sequence (described in Chapter 11). After the SROM load sequence is finished, the 21264/EV67 deasserts SromOE_L. -

Page 216: Fault Reset Flow

RUN state. ClkFwdRst_H is asserted by the system, which causes the state machine to transition to the WAIT_FAULT_RESET state. The 21264/EV67 internally resets a minimum amount of internal state. Note the effects of that reset on the IPRs in Table 7–5 Table 7–5 Effect on IPRs After Fault Reset... -

Page 217: Energy Star Certification And Sleep Mode Flow

Clks 7.3 Energy Star Certification and Sleep Mode Flow The 21264/EV67 is Energy Star compliant. Energy Star is a program administered by the Environmental Protection Agency to reduce energy consumption. For compliance, a computer must automatically enter a low power sleep mode using 30 watts or less after a specified period of inactivity. -

Page 218: Effect On Iprs After Transition Through Sleep Mode

WRITE_MANY Cleared (That is, the WRITE_MANY chain is initialized and the Bcache is Note that Interrupt enables are maintained during sleep mode, enabling the 21264/ EV67 to wake up. The 21264/EV67 waits for either an unmasked clock interrupt or an unmasked device interrupt from the system. -

Page 219: Warm Reset Flow

The warm reset sequence of operation is triggered by the assertion of the Reset_L sig- nal line. The reset state machine is initially in RUN state. The 21264/EV67 then, by default, ramps down the PLL (similar to the sleep flow sequence) and the reset state machine ends up in the WAIT_RESET state. -

Page 220: Array Initialization

Array Initialization The 21264/EV67 waits until Reset_L is deasserted before transitioning from the WAIT_RESET state. The 21264/EV67 ramps up the PLL until the state machine enters the WAIT_ClkFwdRst0 state. Note that the system must assert ClkFwdRst_H before the state machine enters the WAIT_ClkFwdRst0 state. Then, similarly to the other flows, SromOE_L is asserted and the system waits for the deassertion of ClkFwdRst_H. -

Page 221: Example For Initializing Bcache

WrVictimBlk command generation to the system interface are squashed. Using the INVAL_TO_DIRTY_ENABLE and INIT_MODE registers, initialization code loaded from the SROM can generate and delete blocks inside the 21264/EV67 without system interaction. This behavior is very useful for initialization and startup processing, when the system interfaces are not fully functional. -

Page 222: External Interface Initialization

;bc_bank_enable_a ;This loop generates legal ECC data, and ;invalidate tags which are written to the ;Bcache for all but the final 64KB of address. ;and cleans up the Dcache also. Reset State Comments — — Alpha 21264/EV67 Hardware Reference Manual... - Page 223 DTB alternate processor mode DTB_IAP DTB invalidate all process ASM = 0 DTB_IA DTB invalidate all process Alpha 21264/EV67 Hardware Reference Manual Internal Processor Register Power-Up Reset State Reset State Comments — Must be written to in PALcode. — —...

-

Page 224: Ieee 1149.1 Test Port Reset

Cbox shift control 7.9 IEEE 1149.1 Test Port Reset Signal Trst_L must be asserted when powering up the 21264/EV67. Trst_L must not be deasserted prior to assertion of DCOK_H. Trst_L can remain asserted during nor- mal operation of the 21264/EV67. -

Page 225: Ev67 Reset State Machine State Diagram

Figure 7–5 21264/EV67 Reset State Machine State Diagram PLL Ramp Up Reset_L deasserted WAIT_ DCOK_H NOMINAL asserted [16,32] WAIT_ SETTLE [16,32] Reset_L asserted Enabled COLD Interrupt Reset_L asserted WAIT_ WAIT_ RESET INTERRUPT Counter Counter finished & finished & Sleep Mode... - Page 226 PAL_BASE + 0x780. DOWN1 21264/EV67 was in a state in which GCLK was at its highest speed and Reset_L was asserted. Internal chip functions are reset and the internal duration counter is set to 8205 cycles. The purpose of this sequence is to down-ramp the clocks in anticipation of power being removed.

-

Page 227: Phase-Lock Loop (Pll) Functional Description

The PLL multiplies the clock frequency of a differential input reference clock and aligns the phase of its output to that differential input clock. Thus, the 21264/EV67 can communicate synchronously on clock boundaries with clock periods that are defined by the system. -

Page 228: Power-Up/Reset Clocking

769.2 833.3 Dividers 11 through 16 are out of range for the 21264/EV67 and reserved for future use. Valid refer- ence clock (ClkIn_x) frequencies for the 21264/EV67 are specified in the range from 80 to 200. Divider values that are out of that range are displayed as a dash “—”. -

Page 229: Error Detection And Error Handling

Error Detection and Error Handling This chapter gives an overview of the 21264/EV67 error detection and error handling mechanisms, and is organized as follows: • Data error correction code • Icache data or tag parity error • Dcache tag parity error •... -

Page 230: Data Error Correction Code

Data Error Correction Code 8.1 Data Error Correction Code The 21264/EV67 supports a quadword error correction code (ECC) for the system data bus. ECC is generated by the 21264/EV67 for all memory write transactions (WrVictimBlk) emitted from the 21264/EV67 and for all probe data. ECC is also checked on every memory read transaction for single-bit correction and double-bit error detection. -

Page 231: Dcache Data Single-Bit Correctable Ecc Error

Cbox scrubs the block in the Dcache by evicting the block into the victim buffer (thereby scrubbing it) and writing it back into the Dcache as follows: – C_STAT[DSTREAM_DC_ERR] is set. Alpha 21264/EV67 Hardware Reference Manual Dcache Data Single-Bit Correctable ECC Error Error Detection and Error Handling 8–3... -

Page 232: Store Instruction (Quadword Or Smaller)

The Dcache duplicate tag has the correct version of the Dcache coherence state for the 21264/EV67, allowing it to be used for correct tag/status data when the Dcache tags generate a parity error. These tags are parity protected also; however, the Dcache dupli- cate tag cell is designed to be much more tolerant of soft errors. -

Page 233: Bcache Tag Parity Error

MCHK is removed. The CRD PALcode reads the status, to detect this condition, and scrubs the block. In the normal MCHK flow, the PALcode clears the pending CRD error. Alpha 21264/EV67 Hardware Reference Manual Bcache Tag Parity Error Error Detection and Error Handling... -

Page 234: Dcache Fill From Bcache

The Ibox will invoke a replay trap at an instruction that is older than (or equal to) any instruction that consumes the load instruction’s data. The 21264/ EV67 then stalls the replayed Istream in the map stage of the pipeline, until the error is corrected. -

Page 235: Bcache Victim Read During An Ecb Instruction

If the error is not corrected by PAL- code at the time, the error will be detected and corrected by a load/victim operation. Alpha 21264/EV67 Hardware Reference Manual Error Detection and Error Handling... -

Page 236: Bcache Data Single-Bit Correctable Ecc Error On A Probe

A CRD error interrupt is posted, when enabled. • The PALcode on the probed processor may choose to scrub the error, though it will probably be scrubbed by the requesting processor. Error Detection and Error Handling 8–8 Alpha 21264/EV67 Hardware Reference Manual... -

Page 237: Double-Bit Fill Errors

8.11 Double-Bit Fill Errors Double-bit errors for fills are detected, but not corrected, in the 21264/EV67. The fol- lowing events may cause a double-bit fill error: • Icache fill from Bcache • Dcache fill from Bcache • Icache fill from memory •... -

Page 238: Error Case Summary