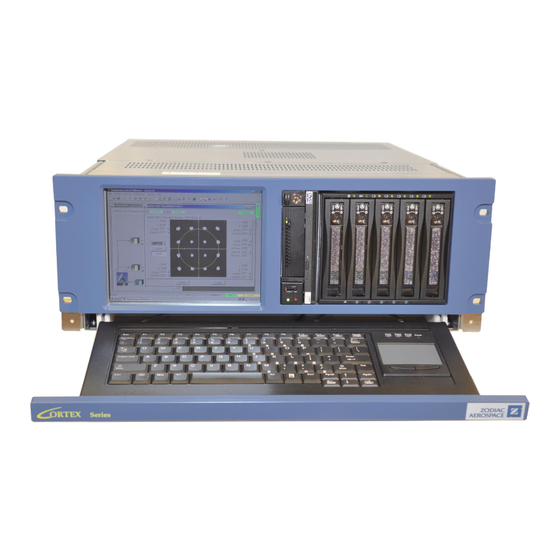

User Manuals: Safran CORTEX Series Satellite Control

Manuals and User Guides for Safran CORTEX Series Satellite Control. We have 1 Safran CORTEX Series Satellite Control manual available for free PDF download: User Manual

Safran CORTEX Series User Manual (382 pages)

HIGH DATA RATE RECEIVER

Table of Contents

-

Ce Marking23

-

Caution24

-

General25

-

Scope29

-

Introduction31

-

IF Reception43

-

Demodulation44

-

Filtering47

-

Viterbi ½48

-

Viterbi ¼48

-

Scrambler49

-

Data Output52

-

Data Storage53

-

Playback54

-

Noise Source54

-

Modulation54

-

Supply57

-

Overview59

-

Monitoring77

-

Control77

-

Logging77

-

Demodulation78

-

General79

-

General80

-

General86

-

PCM Decoding91

-

Introduction95

-

Digital Outputs109

-

Introduction110

-

Sampling Rate111

-

Warning118

-

Data Processing123

-

LDPC Decoding130

-

Introduction130

-

Implementation130

-

Performances131

-

Data Storage131

-

Generality133

-

Overview133

-

Operating Modes138

-

Generality139

-

BER Measurements145

-

Data Output146

-

General152

-

Data Path152

-

Test Modulation155

-

Data Generation155

-

Data Sources155

-

Data from File156

-

File Format156

-

Cycle Length156

-

Playback157

-

Framing Features157

-

Encoding158

-

Scrambling158

-

Fecf159

-

Modulation Unit159

-

Main Features159

-

DNRZ Coding164

-

Dvb-S2 & Sccc167

-

IF1 and IF2167

-

Doppler173

-

Principle173

-

BER Estimation177

-

MCS Preset Files177

-

Constraints178

-

Data Logging181

-

Standard Loging181

-

Extended Logging182

-

System Logging184

-

Operating Manual185

-

First Steps185

-

Screen Saver186

-

CTX Documents187

-

General189

-

XXL with 4G198

-

Common Data202

-

CORTEX Station203

-

Last Used Menu203

-

RAC Port Number203

-

Global HDR209

-

DMX Table210

-

General211

-

MCS Documents211

-

MCS Login Window215

-

Upper Toolbar217

-

Common Data217

-

Lower Toolbar219

-

Common Data219

-

Standard Mode222

-

Protected Mode223

-

Automatic Mode223

-

Monitoring227

-

Monitoring Rate227

-

MCS Auto-Connect227

-

MCS Preferences228

-

Introduction229

-

Other Files230

-

Cortex Hdr Gui232

-

Global" Window234

-

Time" Window238

-

Control239

-

Monitoring239

-

Config" Window244

-

Control244

-

Monitoring247

-

Project" Window248

-

Control248

-

Monitoring248

-

Mod" Window250

-

Modcnf" Window251

-

Global" Window252

-

Control260

-

IF Processing260

-

Flow ID. (Hex)265

-

Matched Filter265

-

Monitoring266

-

Upper Banner266

-

Control269

-

Monitoring270

-

Monitoring271

-

BER" Window272

-

Control273

-

Monitoring273

-

Upper Banner273

-

Decoding" Window275

-

Control278

-

Monitoring280

-

Upper Banner280

-

Spectrum" Window281

-

Vector" Window283

-

Filter" Window287

-

CADU" Window290

-

Control290

-

Monitoring294

-

Upper Banner294

-

LDPC Status295

-

CRC Status295

-

BER" Windows297

-

Control298

-

Monitoring298

-

Control299

-

Monitoring300

-

TCP-IP Status300

-

Upper Banner300

-

Control301

-

Monitoring303

-

Upper Banner303

-

Global" Window304

-

Control304

-

Monitoring305

-

BER" Window306

-

Decoding" Window306

-

Vector" Window306

-

Control308

-

Monitoring311

-

Control312

-

Monitoring314

-

Upper Banner314

-

Recorder Status314

-

FTP" Window315

-

Control316

-

Monitoring318

-

Session Status318

-

Upper Banner318

-

Control319

-

Monitoring319

-

Upper Banner319

-

Data" Window320

-

PRN Selection320

-

File Selection321

-

Control322

-

Control323

-

Control324

-

Bpsk/Qpsk/Gmsk325

-

Oqpsk326

-

Uqpsk326

-

8Psk327

-

16Qam327

-

16Apsk328

-

64Apsk329

-

Viterbi Mode329

-

TCM Mode330

-

Control330

-

SCCC Mode332

-

DVB-S2 Mode332

-

Control333

-

IF Unit" Windows335

-

IF" Window335

-

Control335

-

Control337

-

Control343

-

Error Insertion344

-

Playback Windows345

-

Global" Window345

-

Status346

-

File" Window349

-

Configuration352

-

File Selection353

-

Logging Windows355

-

Control355

-

Status355

-

General359

-

Software Loading359

-

Viterbi Check360

-

LED Indicators366

-

CPU Board366

Advertisement

Advertisement