Motorola MVME2600 Series Reference Manual

Mvme2600/2700 series single board computer

Hide thumbs

Also See for MVME2600 Series:

- Installation and use manual (198 pages) ,

- Installation and use manual (20 pages) ,

- Programmer's reference manual (20 pages)

Summary of Contents for Motorola MVME2600 Series

- Page 1 MVME2600/2700 Series Single Board Computer Programmer’s Reference Guide V2600A/PG2...

- Page 2 While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

- Page 3 Preface The MVME2600/2700 Series Single Board Computer Programmer’s Reference Guide provides brief board level information, complete memory maps, and detailed ASIC chip information including register bit descriptions for the MVME2600 and MVME2700 series Single Board Computers. The information contained in this manual applies to the single board computers built from some of the plug-together components in the following list: Table 1: MVME2603-11X1...

- Page 4 The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola’s Terms and Conditions of Sale, Rev.

-

Page 5: Ground The Instrument

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment. -

Page 6: Table Of Contents

Contents CHAPTER 1 Board Description and Memory Maps Revision Note......................1-1 Introduction........................1-1 Manual Terminology....................1-2 Overview........................1-3 Feature Summary .......................1-4 System Block Diagram ....................1-5 Functional Description....................1-7 Overview......................1-7 Programming Model ....................1-8 Memory Maps.....................1-8 Processor Memory Maps ................1-8 PCI Memory Maps ..................1-14 VMEbus Mapping ..................1-21 Falcon-Controlled System Registers ..............1-27 System Configuration Register (SYSCR) ..........1-28 Memory Configuration Register (MEMCR) ..........1-30... - Page 7 Z85230 ESCC and Z8536 CIO Registers and Port Pins ........1-44 Z8536/Z85230 Registers ................1-45 Z8536 CIO Port Pins ................. 1-46 ISA DMA Channels ..................1-49 CHAPTER 2 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Introduction ....................... 2-1 Overview ......................

- Page 8 MPC Error Enable Register ...............2-30 MPC Error Status Register ................2-32 MPC Error Address Register ..............2-34 MPC Error Attribute Register - MERAT ..........2-34 PCI Interrupt Acknowledge Register ............2-36 MPC Slave Address (0,1 and 2) Registers ..........2-37 MPC Slave Address (3) Register...............2-38 MPC Slave Offset/Attribute (0,1 and 2) Registers ........2-39 MPC Slave Offset/Attribute (3) Registers..........2-40 General Purpose Registers.................2-41...

- Page 9 MPIC Registers ....................2-61 RavenMPIC Registers ................2-61 Feature Reporting Register ............... 2-65 Global Configuration Register ..............2-66 Vendor Identification Register ..............2-67 Processor Init Register ................2-67 IPI Vector/Priority Registers..............2-68 Spurious Vector Register ................2-69 Timer Frequency Register................. 2-69 Timer Current Count Registers ..............

- Page 10 Performance ......................3-6 Four-beat Reads/Writes ................3-6 Single-beat Reads/Writes ................3-7 DRAM Speeds .....................3-7 ROM/Flash Speeds ..................3-11 PowerPC 60x Bus Interface................3-12 Responding to Address Transfers..............3-12 Completing Data Transfers................3-12 Cache Coherency ..................3-12 Cache Coherency Restrictions..............3-13 L2 Cache Support ..................3-13 ECC........................3-13 Cycle Types ....................3-13 Error Reporting..................3-13 Error Logging ....................3-15 DRAM Tester....................3-15 ROM/Flash Interface ..................3-16...

- Page 11 PCI Reset Problems Associated with the Initial Version of the Universe Chip ..4-14 Problem Description..................4-14 Examples ......................4-16 Example 1: MVME2600 Series Board Exhibits Problem......4-16 Example 2: MVME3600 Series Board Acts Differently ......4-18 Example 3: Universe Chip is Checked at Tundra ........4-20...

- Page 12 PCI-Ethernet ....................5-15 PCI-Graphics .....................5-15 Universe’s Involvement ..................5-15 VMEbus Domain ....................5-15 ROM/Flash Initialization ..................5-16 APPENDIX A Related Documentation Overview........................A-1 MCG Customer Services ..................A-2 Motorola Computer Group Documents ..............A-3 Manufacturers’ Documents..................A-5 Related Specifications.....................A-10 GLOSSARY Abbreviations, Acronyms, and Terms to Know............. GL-1 INDEX xiii...

- Page 14 List of Figures Figure 1-1. MVME2600 Series System Block Diagram ...........1-6 Figure 1-2. VMEbus Master Mapping..............1-22 Figure 1-3. VMEbus Slave Mapping ...............1-24 Figure 2-1. Raven Block Diagram ................2-4 Figure 2-2. PCI Spread I/O Cycle Mapping ............2-14 Figure 2-3. Big to Little Endian Data Swap ............2-17 Figure 2-4.

- Page 16 List of Tables Table 1-1. MVME2600 Series Features Summary ...........1-4 Table 1-2. Default Processor Memory Map ..............1-9 Table 1-3. CHRP Memory Map Example..............1-10 Table 1-4. Raven MPC Register Values for CHRP Memory Map......1-11 Table 1-5. PREP Memory Map Example..............1-12 Table 1-6. Raven MPC Register Values for PREP Memory Map ......1-13 Table 1-7.

- Page 17 Table 5-4. Reset Sources and Devices Affected ............5-9 Table 5-5. Error Notification and Handling ............5-10 Table 5-6. ROM/FLASH Bank Default..............5-16 Table A-1. Motorola Computer Group Documents ..........A-3 Table A-2. Manufacturers’ Documents ..............A-5 Table A-3. Related Specifications ................ A-10...

-

Page 18: Revision Note

This chapter briefly describes the board level hardware features of the MVME2600 series Single Board Computers. The chapter begins with a board level overview and features list. Memory maps are next, and are the... -

Page 19: Manual Terminology

Board Description and Memory Maps Programmable registers in the MVME2600/2700 series that reside in ASICs are covered in the chapters on those ASICs. Chapter 2 covers the Raven chip, Chapter 3 covers the Falcon chip set, Chapter 4 covers the Universe chip, and Chapter 5 covers certain programming features, such as interrupts and exceptions. -

Page 20: Overview

Overview A byte is eight bits, numbered 0 through 7, with bit 0 being the least significant. A half-word is 16 bits, numbered 0 through 15, with bit 0 being the least significant. A word or single word is 32 bits, numbered 0 through 31, with bit 0 being the least significant. -

Page 21: Feature Summary

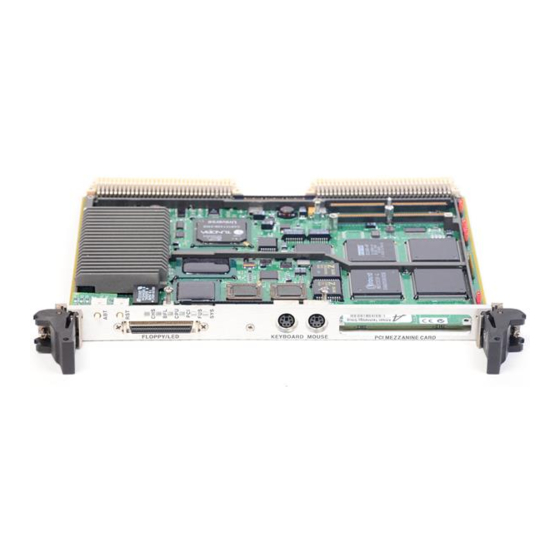

Board Description and Memory Maps Feature Summary There are many models based on the MVME2600/2700 series architecture. The following table summarizes the major features of the MVME2600 series: Table 1-1. MVME2600 Series Features Summary Feature Description Processors Single Supports BGA processors only: MVME2600: MPC603, MPC604. -

Page 22: System Block Diagram

System Block Diagram Table 1-1. MVME2600 Series Features Summary (Continued) Feature Description PMC Slots One 32/64-bit Slot Miscellaneous RESET/ABORT Switch Status LEDs System Block Diagram The MVME2600/2700 series provides the 256KB look-aside external cache option. The Falcon chip set controls the boot Flash and the ECC DRAM. -

Page 23: Figure 1-1. Mvme2600 Series System Block Diagram

33MHz 32/64-BIT PCI LOCAL BUS ETHERNET SCSI VME BRIDGE W83C553 DEC21140 53C825A UNIVERSE REGISTERS AUI/10BT/100BTX BUFFERS RTC/NVRAM/WD MK48T559 SUPER I/O ESCC PC87308 85230 Z8536 712/761 P2 I/O OPTIONS VME P2 VME P1 11536.00 9611 Figure 1-1. MVME2600 Series System Block Diagram... -

Page 24: Functional Description

Functional Description Functional Description Overview The MVME2600/2700 series is a family of single-slot SBCs. The MVME2600 family consists of the MPC603/604 processor, the Raven PCI Bridge & Interrupt Controller, the ECC Memory Controller Falcon chipset, 5MB or 9MB of Flash memory, 16MB to 256MB of ECC- protected DRAM, and a rich set of features of I/O peripherals. -

Page 25: Programming Model

Board Description and Memory Maps The MVME2600/2700 series contains one IEEE1386.1 PCI Mezzanine Card (PMC) slot. This PMC slot is 64-bit capable and supports both front and rear I/O. Pins 1 through 30 of the PMC connector J14 are routed to pins D1 through D30 of the 5-row DIN P2 connector. -

Page 26: Table 1-2. Default Processor Memory Map

Programming Model Default Processor Memory Map After a reset, the Raven ASIC and the Falcon chipset provide the default processor memory map as shown in the following table. Table 1-2. Default Processor Memory Map Processor Address Size Definition Start 0000 0000 7FFF FFFF Not mapped 8000 0000... -

Page 27: Table 1-3. Chrp Memory Map Example

Board Description and Memory Maps Processor CHRP Memory Map The following table shows a recommended CHRP memory map from the point of view of the processor. Table 1-3. CHRP Memory Map Example Processor Address Size Definition Start 0000 0000 top_dram dram_size System Memory (onboard DRAM) 1, 2... -

Page 28: Table 1-4. Raven Mpc Register Values For Chrp Memory Map

Programming Model 4. CHRP requires the starting address for the PCI memory space to be 256MB-aligned. 5. Programmable via Raven ASIC for either contiguous or spread-I/O mode. 6. The actual size of each ROM/FLASH bank may vary. 7. The first one Mbyte of ROM/FLASH Bank A appears at this range after a reset if the rom_b_rv control bit is cleared. -

Page 29: Table 1-5. Prep Memory Map Example

Board Description and Memory Maps Processor PREP Memory Map The Raven/Falcon chipset can be programmed for PREP-compatible memory map. The following table shows the PREP memory map of the MVME2600/2700 series from the point of view of the processor. Table 1-5. PREP Memory Map Example Processor Address Size Definition... -

Page 30: Table 1-6. Raven Mpc Register Values For Prep Memory Map

Programming Model control bit is set then this address range maps to ROM/FLASH Bank 5. This range can be mapped to the VMEbus by programming the Universe ASIC accordingly. 6. The only method to generate a PCI Interrupt Acknowledge cycle (8259 IACK) is to perform a read access to the Raven’s PIACK register at 0xFEFF0030. -

Page 31: Pci Memory Maps

Board Description and Memory Maps PCI Memory Maps The PCI memory map is controlled by the Raven ASIC and the Universe ASIC. The Raven ASIC and the Universe ASIC have flexible programming Map Decoder registers to customize the system to fit many different applications. - Page 32 Programming Model Table 1-7. PCI CHRP Memory Map (Continued) PCI Address Size Definition Notes Start FC04 0000 FCFF FFFF 16M - 256K PCI Memory Space FD00 0000 FDFF FFFF PCI Memory Space or System Memory Alias Space (mapped to 00000000 to 00FFFFFF) FE00 0000 FFFF FFFF Reserved...

-

Page 33: Table 1-8. Raven Pci Register Values For Chrp Memory Map

Board Description and Memory Maps The following table shows the programmed values for the associated Raven PCI registers for the PCI CHRP memory map. Table 1-8. Raven PCI Register Values for CHRP Memory Map Configuration Configuration Register Value Register Value Address Offset Register Name (Aliasing OFF) - Page 34 Programming Model Table 1-9. Universe PCI Register Values for CHRP Memory Map (Continued) Configuration Configuration Register Value Address Offset Register Name $120 LSI1_TO XXXX 0000 $128 LSI2_CTL 0000 0000 $12C LSI2_BS XXXX XXXX $130 LSI2_BD XXXX XXXX $134 LSI2_TO XXXX XXXX $13C LSI3_CTL 0000 0000...

-

Page 35: Table 1-10. Pci Prep Memory Map

Board Description and Memory Maps PCI PREP Memory Map The following table shows a PCI memory map of the MVME2600/2700 series that is PREP-compatible from the point of view of the PCI local bus. Table 1-10. PCI PREP Memory Map PCI Address Size Definition... -

Page 36: Table 1-11. Raven Pci Register Values For Prep Memory Map

Programming Model 3. Programmable mapping via the four PCI Slave Images in the Universe ASIC. 4. Programmable mapping via the Special Slave Image (SLSI) in the Universe ASIC. The following table shows the programmed values for the associated Raven PCI registers for the PREP-compatible memory map. Table 1-11. -

Page 37: Table 1-12. Universe Pci Register Values For Prep Memory Map

Board Description and Memory Maps The next table shows the programmed values for the associated Universe PCI registers for the PCI PREP memory map. Table 1-12. Universe PCI Register Values for PREP Memory Map Configuration Configuration Register Value Address Offset Register Name $100 LSI0_CTL... -

Page 38: Vmebus Mapping

Programming Model VMEbus Mapping VMEbus Master Map The processor can access any address range in the VMEbus with the help from the address translation capabilities of the Universe ASIC. The recommended mapping is shown in the Processor Memory Map section. The following figure illustrates how the VMEbus master mapping is accomplished. -

Page 39: Figure 1-2. Vmebus Master Mapping

Board Description and Memory Maps VMEBUS PROCESSOR PCI MEMORY ONBOARD MEMORY PROGRAMMABLE SPACE NOTE 2 NOTE 1 PCI MEMORY SPACE VME A24 VME A16 NOTE 3 VME A24 VME A16 NOTE 1 VME A24 PCI/ISA MEMORY SPACE VME A16 VME A24 I/O SPACE VME A16 RESOURCES... - Page 40 Programming Model 2. Programmable mapping via the four PCI Slave Images in the Universe ASIC. 3. Programmable mapping via the Special Slave Image (SLSI) in the Universe ASIC. VMEbus Slave Map The four programmable VME Slave Images in the Universe ASIC allow other VMEbus masters to get to any devices on the MVME2600/2700 series.

-

Page 41: Figure 1-3. Vmebus Slave Mapping

Board Description and Memory Maps PCI Memory VMEbus Processor NOTE 2 Onboard Memory NOTE 1 NOTE 1 ISA Space PCI I/O Space NOTE3 Software INT Registers 1896 9609 Figure 1-3. VMEbus Slave Mapping Notes: 1. Programmable mapping via the four VME Slave Images in the Universe ASIC. -

Page 42: Table 1-13. Universe Pci Register Values For Vmebus Slave Map Example

Programming Model The following table shows the programmed values for the associated Universe registers for the VMEbus slave function. Table 1-13. Universe PCI Register Values for VMEbus Slave Map Example Configuration Configuration Register Value Register Value Address Offset Register Name (CHRP) (PREP) $F00... -

Page 43: Table 1-14. Vmebus Slave Map Example

Board Description and Memory Maps Table 1-14. VMEbus Slave Map Example VMEbus Address Size CHRP Map PREP Map Range Mode 4000 0000 - A32 U/S/P/D PCI/ISA I/O Space: PCI/ISA I/O Space: 4000 0FFF D08/16/32 0000 1000 - 0000 1FFF 0000 1000 - 0000 1FFF 1000 0000 - A32 U/S/P/D 256M... -

Page 44: Falcon-Controlled System Registers

Programming Model Falcon-Controlled System Registers The Falcon chipset latches the states of the DRAM data lines onto the PR_STAT1 and PR_STAT2 registers. The MVME2600/2700 series use these status registers to provide the system configuration information. In addition, the Falcon chipset performs the decode and control for an external register port. -

Page 45: System Configuration Register (Syscr)

Board Description and Memory Maps System Configuration Register (SYSCR) The states of the RD[0:31] DRAM data pins, which have weak internal pull-ups, are latched by the upper Falcon chip at a rising edge of the power- up reset and stored in this System Configuration Register to provide some information about the system. - Page 46 Programming Model SYSXC Value External Look-aside Cache Size 0b1100 0b1101 512K 0b1110 256K 0b1111 None P0/1STAT Processor 0/1 Status. This field is encoded as follows: External In-line Cache P0/1STAT Value Processor 0/1 Present Size 0b0000 to 0b0011 Reserved Reserved 0b0100 0b0101 512K 0b0110...

-

Page 47: Memory Configuration Register (Memcr)

Board Description and Memory Maps Memory Configuration Register (MEMCR) The states of the RD[00:31] DRAM data pins, which have weak internal pull-ups, are latched by the lower Falcon chip at a rising edge of the power- up reset and stored in this Memory Configuration Register to provide some information about the system memory. -

Page 48: System External Cache Control Register (Sxccr)

Programming Model These two bits reflect the combined status of the four blocks of DRAM. Initialization software uses this information to program the ram_spd0 and ram_spd1 control bits in the Falcon’s Chip Revision Register. R_A/B_TYP[0:1] ROM/Flash Type. This field is encoded as follows: ROM_A/B_TYP[0:2] ROM/FLASH Type... - Page 49 Board Description and Memory Maps SXC_FLSH_System External Cache Flush. When this bit is pulsed true for at least 8 clock periods, it causes the system external cache to write back dirty cache lines out to system memory and clears all the tag valid bits. This operation causes the Glance pair to request and hold the MPC bus until it has completed the flush operation (approximately 4100 clock cycles).

-

Page 50: Cpu Control Register

Programming Model CPU Control Register The CPU Control Register is accessed via the RD[32:39] data lines of the upper Falcon device. This 8-bit register is defined as follows: CPU Control Register - $FEF88300 FIELD OPER RESET LEMODE Little Endian Mode. This bit must be set in conjunction with the LEND bit in the Raven for little-endian mode. -

Page 51: Isa Local Resource Bus

Board Description and Memory Maps ISA Local Resource Bus W83C553 PIB Registers The PIB contains ISA Bridge I/O registers for various functions. These registers are actually accessible from the PCI bus. Refer to the W83C553 Data Book for details. PC87308VUL Super I/O (ISASIO) Strapping The PC87308VUL Super I/O (ISASIO) provides the following functions to the MVME2600/2700 series: a keyboard interface, a PS/2 mouse interface, a PS/2 floppy port, two async serial ports and a parallel port. -

Page 52: Module Configuration And Status Registers

ISA Local Resource Bus Strobe 1 Register, and the NVRAM/RTC Data Port Register. The NVRAM/RTC Address Strobe 0 Register latches the lower 8 bits of the address and the NVRAM/RTC Address Strobe 1 Register latches the upper 5 bits of the address. Table 1-17. -

Page 53: Cpu Configuration Register

Board Description and Memory Maps Table 1-18. Module Configuration and Status Registers PCI I/O Address Function 0000 0800 CPU Configuration Register 0000 0802 Base Module Feature Register 0000 0803 Base Module Status Register 0000 08C0 - 0000 08C1 Seven-Segment Display Register The following sub sections describe these registers in detail. - Page 54 ISA Local Resource Bus Base Module Feature Register The Base Module Feature Register is an 8-bit register providing the configuration information about the Genesis Single Board Computer. This read-only register is located at ISA I/O address x0802. Base Module Feature Register - Offset $0802 FIELD OPER RESET...

-

Page 55: Base Module Status Register (Bmsr)

Board Description and Memory Maps SCSIP_ SCSI Present. If set, there is no on-board SCSI interface. If cleared, on-board SCSI is supported. Base Module Status Register (BMSR) The Base Module Status Register is an 8-bit read-only register located at ISA I/O address x0803. Base Module Status Register - Offset $0803 FIELD BASE_TYPE... -

Page 56: Seven-Segment Display Register

ISA Local Resource Bus Seven-Segment Display Register This 16-bit register allows data to be sent to the 4-digit hexadecimal diagnostic display. The register also allows the data to be read back. 7-Segment Display Register - Offset $08C0 FIELD DIG3[3:0] DIG2[3:0] DIG1[3:0] DIG0[3:0] OPER... -

Page 57: Lm/Sig Control Register

Board Description and Memory Maps Table 1-19. VME Registers PCI I/O Address Function 0000 1000 SIG/LM Control Register 0000 1001 SIG/LM Status Register 0000 1002 VMEbus Location Monitor Upper Base Address 0000 1003 VMEbus Location Monitor Lower Base Address 0000 1004 VMEbus Semaphore Register 1 0000 1005 VMEbus Semaphore Register 2... -

Page 58: Lm/Sig Status Register

ISA Local Resource Bus SET_LM1 Writing a 1 to this bit will set the LM1 status bit. SET_LM0 Writing a 1 to this bit will set the LM0 status bit. CLR_SIG1Writing a 1 to this bit will clear the SIG1 status bit. CLR_SIG0Writing a 1 to this bit will clear the SIG0 status bit. -

Page 59: Location Monitor Upper Base Address Register

Board Description and Memory Maps SIG1 SIG1 status bit. This bit can only be set by the SET_LM1 control bit. It can only be cleared by a reset or by writing a 1 to the CLR_LM1 control bit. SIG0 SIG0 status bit. This bit can only be set by the SET_LM0 control bit. -

Page 60: Location Monitor Lower Base Address Register

ISA Local Resource Bus Location Monitor Lower Base Address Register The Location Monitor Lower Base Address Register is an 8-bit register located at ISA I/O address x1003. The Universe ASIC is programmed so that this register can be accessed from the VMEbus to provide VMEbus location monitor function. -

Page 61: Semaphore Register 2

Board Description and Memory Maps Semaphore Register 2 The Semaphore Register 2 is an 8-bit register located at ISA I/O address x1005. The Universe ASIC is programmed so that this register can be accessible from the VMEbus. This register can only be updated if bit 7 is low or if the new value has the most significant bit cleared. -

Page 62: Z8536/Z85230 Registers

ISA Local Resource Bus The Z8536 CIO is used to provide the modem control lines not provided by the Z85230 ESCC and a method to inquire the module ID of the two sync/async serial ports that reside on the MVME761 module. Refer to the Z8536 Data Sheet for programming information. -

Page 63: Z8536 Cio Port Pins

Board Description and Memory Maps Z8536 CIO Port Pins The assignment for the Port pins of the Z8536 CIO is as follows: Table 1-21. Z8536 CIO Port Pins Assignment Port Signal Direction Descriptions Name TM3_ Input Port 3 Test Mode when IDREQ_ = 1; MID0 Module ID Bit 0 when IDREQ_ = 0. - Page 64 ISA Local Resource Bus Table 1-21. Z8536 CIO Port Pins Assignment (Continued) Port Signal Direction Descriptions Name Reserved Reserved Reserved Reserved Reserved Reserved Reserved NOTE: The direction and the polarity of the Z8536’s port pins are software programmable. 1-47...

-

Page 65: Table 1-22. Interpretation Of Mid3-Mid0

Board Description and Memory Maps The module ID signals, which are only valid when IDREQ_ is asserted, indicate the type of the serial module that is installed on either Port 3 or Port 4. The following table shows how to interpret the MID3-MID0 signals: Table 1-22. -

Page 66: Isa Dma Channels

ISA Local Resource Bus ISA DMA Channels There are seven ISA DMA channels in the PIB. Channels 0 through 3 support only 8-bit DMA devices while Channels 5 through 7 support only 16-bit DMA devices. These DMA channels are assigned as follows: Table 1-23. - Page 67 Board Description and Memory Maps 1-50...

-

Page 68: Introduction

2Raven PCI Host Bridge & Multi- Processor Interrupt Controller Chip Introduction Overview This document describes the architecture and usage of the Raven, a PowerPC to PCI Local Bus Bridge ASIC. The Raven is intended to provide MPC60x compliant devices access to devices residing on the PCI Local Bus in a very efficient manner. -

Page 69: Requirements

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Requirements The Raven must provide a high throughput interface between multiple MPC60x processors and 32/64-bit PCI local bus. It must be capable of supporting up to two MPC60x processors and contain a multiprocessing interrupt structure to efficiently distribute interrupts dynamically between these processors. - Page 70 Introduction – Four 31 bit tick timers. Two 64-bit general purpose registers for cross-processor messaging.

-

Page 71: Block Diagram

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Block Diagram 1914 9610 Figure 2-1. Raven Block Diagram... -

Page 72: Functional Description

Functional Description Functional Description MPC Bus Interface The MPC Bus Interface is designed to be coupled directly to up to two MPC601, MPC603, or MPC604 microprocessors as well as a memory/cache subsystem. It uses a subset of the capabilities of the MPC60x bus protocol. - Page 73 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Each external request can be individually enabled or disabled using control bits in the MPC Arbiter Control Register (MARB). Following reset, all requests will be enabled. The MPC Arbiter supports optional bus parking in order to reduce arbitration latency.

-

Page 74: Mpc Map Decoders

Functional Description MPC Map Decoders The Raven address decoders have been designed to be as flexible as possible to provide a wide range of addressing possibilities. There are five address map decoders in the Raven which determine the MPC bus addresses to which the Raven will respond: the MPC Register File Decoder, and four programmable decoders. -

Page 75: Mpc Write Posting

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip released. If the EXT01 pin is sampled in the low state, the MPC register file will start at address $FEFE0000. If the EXT01 pin is sampled in the high state, the MPC register file will start at address $FEFF0000. All references to the MPC register file within this specification will assume a base address of FEFF0000. -

Page 76: Mpc Master

Functional Description All write posted transfers will be completed before a non-write posted read or write is begun to assure that all transfers are completed in the order issued. All write posted transfers will also be completed before any access to the Raven’s registers is begun. -

Page 77: Mpc Bus Timer

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Table 2-2. MPC Transfer Types MPC Transfer PCI Command Code MPC Transfer Size TT0-TT4 Type Memory Read, Read Burst/Single Beat 01010 Memory Read Multiple, Memory Read Line Memory Read, Read With Intent to Burst/Single Beat 01110 Memory Read... -

Page 78: Pci Interface

Functional Description The bus timer starts ticking at the beginning of an address transfer (TS* asserted), and if the address transfer is not terminated (AACK* asserted) before the time-out period has passed, the Raven will assert the MATO bit in the MPC Error Status Register, latch the MPC address in the MPC Error Address Register, and then immediately assert AACK*. -

Page 79: Pci Configuration Space

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Decoder Priority PCI Slave 0 highest PCI Slave 1 PCI Slave 2 PCI Slave 3 lowest PCI Configuration Space The Raven does not have an IDSEL pin. An internal connection is made within the Raven that logically associates the assertion of IDSEL with the assertion of either AD30 or AD31. -

Page 80: Pci Master

Functional Description PCI Master The PCI master, in conjunction with the capabilities of the MPC slave, will attempt to move data in either single beat or burst transactions. All single beat transactions will be subdivided into one or two 32-bit transfers, depending on the alignment and size of the transaction. -

Page 81: Figure 2-2. Pci Spread I/O Cycle Mapping

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip PCI Cycle Type Memory Contiguous I/O Spread I/O The IBM CHRP specification describes two approaches for handling PCI I/O addressing: contiguous or spread address modes. When the MEM bit is cleared, the IOM bit is used to select between these two modes whenever a PCI I/O cycle is to be performed. -

Page 82: Generating Pci Configuration Cycles

Functional Description All I/O accesses must be performed within natural word boundaries. Any I/O access that is not contained within a natural word boundary will result in unpredictable operation. For example, an I/O transfer of 4 bytes starting at address $80000010 is considered a valid transfer. An I/O transfer of 4 bytes starting at address $80000011 is considered an invalid transfer since it crosses the natural word boundary at address $80000013/$80000014. -

Page 83: Generating Pci Interrupt Acknowledge Cycles

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Generating PCI Interrupt Acknowledge Cycles Performing a read from the PIACK register will initiate a single PCI Interrupt Acknowledge cycle. Any single byte or combination of bytes may be read from, and the actual byte enable pattern used during the read will be passed on to the PCI bus. -

Page 84: When Mpc Devices Are Little Endian

Functional Description PPC Bus 64-bit PCI PPC Bus 32-bit PCI 1916 9610 Figure 2-3. Big to Little Endian Data Swap When MPC Devices are Little Endian When all MPC devices are operating in little endian mode, the MPC address must be modified to remove the exclusive-ORing applied by MPC60x processors before being passed on to PCI. -

Page 85: Cycles Originating From Pci

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Table 2-4. Address Modification for Little Endian Transfers Data Length Address Modification (bytes) XOR with 111 XOR with 110 XOR with 100 no change Note The only legal data lengths supported in little endian mode are 1, 2, 4, or 8-byte aligned transfers. - Page 86 Functional Description Each of these error conditions will cause an error status bit to be set in the MPC Error Status Register. If a second error is detected while any of the error bits is set, the OVFL bit is asserted, but none of the error bits are changed.

-

Page 87: Pci/Mpc Contention Handling

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip PCI/MPC Contention Handling The Raven has a stall detection mechanism that detects when there is a possible resource contention problem (i.e. deadlock) as a result of overlapping MPC and PCI initiated transactions. The MPC Slave and the PCI Slave functions contain the logic needed to implement this feature. - Page 88 Functional Description between write cycles, and thereby result in a partially completed write cycle. It is recommended that write cycles to write-sensitive non-posted locations be performed on mod-4 address boundaries. The Raven has a programmable option to guarantee all PCI write posted transactions are completed before an MPC initiated read transaction may be allowed to complete.

-

Page 89: Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip 2Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Registers This chapter provides a detailed description of all Raven registers. These registers are broken into two groups: the MPC Registers and the PCI Configuration Registers. - Page 90 Registers Table 2-5. Raven MPC Register Map (Continued) Bit ---> 0 1 2 3 4 5 6 7 8 9 $FEFF0024 MERST $FEFF0028 MERAD $FEFF002C MERAT $FEFF0030 PIACK $FEFF0034 $FEFF0038 $FEFF003C $FEFF0040 MSADD0 $FEFF0044 MSOFF0 MSATT0 $FEFF0048 MSADD1 $FEFF004C MSOFF1 MSATT1 $FEFF0050 MSADD2...

-

Page 91: Vendor Id/Device Id Registers

$4801 VENID Vendor ID. This register identifies the manufacturer of the device. This identifier is allocated by the PCI SIG to ensure uniqueness. $1057 has been assigned to Motorola. This register is duplicated in the PCI Configuration Registers. DEVID Device ID. This register identifies this particular device. -

Page 92: General Control-Status/Feature Registers

Registers General Control-Status/Feature Registers Address $FEFF0008 0 1 2 3 4 5 6 7 8 9 Name GCSR FEAT Operation Reset LEND Endian Select. If set, the MPC bus is operating in little endian mode. The MPC address will be modified as described in the section When MPC Devices are Little Endian. - Page 93 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip MBTx MPC Bus Time-out. This field specifies the MPC bus time-out length. The time-out length is encoded as follows: Time Out Length 256 sec 64 sec 8 sec disabled 64-bit PCI Mode Enable. If set, the Raven is connected to a 64-bit PCI bus.

- Page 94 Registers Current MPC Data Bus Master device on ABG0* device on ABG1* device on ABG2 Raven FEAT Feature Register. Each bit in this register reflects the state of one of the external interrupt input pins on the rising edge of RESET*. This register may be used to report hardware configuration parameters to system software.

-

Page 95: Mpc Arbiter Control Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip MPC Arbiter Control Register Address $FEFF000C 0 1 2 3 4 5 6 7 8 9 Name MARB Operation Reset BREN2 Bus Request 2 Enable. If set, the processor bus request signal ABR2* is enabled. -

Page 96: Prescaler Adjust Register

Registers GLMD Glance Mode. If set, the MPC arbiter will operate in the Glance mode. Please refer to the section on the MPC Arbiter for more information. BAMD Benign Address Retry Mode. If set, the MPC arbiter will operate in the benign address retry mode. Please refer to the section on the MPC Arbiter for more information. -

Page 97: Mpc Error Enable Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip where Clk is the frequency of the CLK input in MHz. The following table shows the scale factors for some common CLK frequencies. Frequency PADJ MPC Error Enable Register Address $FEFF0020 0 1 2 3 4 5 6 7 8 9 Name MEREN... - Page 98 Registers MATOM MPC Address Bus Time-out Machine Check Enable. When this bit is set, the MATO bit in the MERST register will be used to assert the MCHK output to the current address bus master. When this bit is clear, MCHK will not be asserted.

-

Page 99: Mpc Error Status Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip SERRI PCI System Error Interrupt Enable.When this bit is set, the PERR bit in the MERST register will be used to assert an interrupt through the MPIC interrupt controller. When this bit is clear, no interrupt will be asserted. SMAI PCI Master Signalled Master Abort Interrupt Enable.When this bit is set, the SMA bit in the MERST... - Page 100 Registers MATOM bit in the MEREN register is set, the assertion of this bit will assert MCHK to the master designated by the MID field in the MERAT register. When the MATOI bit in the MEREN register is set, the assertion of this bit will assert an interrupt through the MPIC interrupt controller.

-

Page 101: Mpc Error Address Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip register. When the RTAI bit in the MEREN register is set, the assertion of this bit will assert an interrupt through the MPIC interrupt controller. MPC Error Address Register Address $FEFF0028 0 1 2 3 4 5 6 7 8 9 Name MERAD... - Page 102 Registers MIDx MPC Master ID. This field contains the ID of the MPC master which originated the transfer in which the error occurred. The encoding scheme is identical to that used in the GCSR register. TBST Transfer Burst. This bit is set when the transfer in which the error occurred was a burst transfer.

-

Page 103: Pci Interrupt Acknowledge Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip BYTEx PCI Byte Enable. This field contains the PCI byte enables of the PCI transfer in which the error occurred. A set bit designates a selected byte. PCI Interrupt Acknowledge Register Address $FEFF0030 0 1 2 3 4 5 6 7 8 9... -

Page 104: Mpc Slave Address (0,1 And 2) Registers

2Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Registers 0Registers MPC Slave Address (0,1 and 2) Registers Address MSADD0 - $FEFF0040 MSADD1 - $FEFF0048 MSADD2 - $FEFF0050 0 1 2 3 4 5 6 7 8 9 Name MSADDx START Operation Reset... -

Page 105: Mpc Slave Address (3) Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip MPC Slave Address (3) Register Address MSADD3 - $FEFF0058 0 1 2 3 4 5 6 7 8 9 Name MSADD3 START Operation Reset $8000 $8080 MSADD3, MSOFF3 and MSATT3 represent the only register group which can be used to initiate access to the PCI Configuration Address ($80000CF8) and Configuration Data ($80000CFC) registers. -

Page 106: Mpc Slave Offset/Attribute (0,1 And 2) Registers

Registers MPC Slave Offset/Attribute (0,1 and 2) Registers Address MSOFF0/MSATT0 - $FEFF0044 MSOFF1/MSATT1 - $FEFF004C MSOFF2/MSATT2 - $FEFF0054 0 1 2 3 4 5 6 7 8 9 Name MSOFFx MSATTx Operation Reset $0000 MSOFFx MPC Slave Offset. This register contains a 16-bit offset that is added to the upper 16 bits of the MPC address to determine the PCI address used for transfers from the MPC bus to PCI. -

Page 107: Mpc Slave Offset/Attribute (3) Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip PCI I/O Mode. If set, the corresponding MPC slave will generate PCI I/O cycles using spread addressing as defined in the section on Generating PCI Memory and I/O Cycles. When clear, the corresponding MPC slave will generate PCI I/O cycles using contiguous addressing. -

Page 108: General Purpose Registers

Registers PCI I/O Mode. If set, the corresponding MPC slave will generate PCI I/O cycles using spread addressing as defined in the section on Generating PCI Memory and I/O Cycles. When clear, the corresponding MPC slave will generate PCI I/O cycles using contiguous addressing. General Purpose Registers Address GPREG0 (Upper) - $FEFF0070... -

Page 109: Table 2-6. Raven Pci Configuration Register Map

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Table 2-6. Raven PCI Configuration Register Map <--- Bit 0 9 8 7 6 5 4 3 2 1 0 DEVID VENID PSTAT PCOMM CLASS REVID IOBASE MEMBASE $18 - $7F PSADD0 PSOFF0 PSATT0... -

Page 110: Vendor Id/ Device Id Registers

VENID Vendor ID. This register identifies the manufacturer of the device. This identifier is allocated by the PCI SIG to ensure uniqueness. $1057 has been assigned to Motorola. This register is duplicated in the MPC Registers. DEVID Device ID. This register identifies the particular device. - Page 111 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip MEMSP Memory Space Enable. If set, the Raven will respond to PCI memory space accesses when appropriate. If cleared, the Raven will not respond to PCI memory space accesses. MSTR Bus Master Enable. If set, the Raven may act as a master on PCI.

-

Page 112: Revision Id/ Class Code Registers

Registers RCVMA Received Master Abort. This bit is set by the PCI master whenever its transaction (except for Special Cycles) is terminated by a master-abort. It is cleared by writing it to 1; writing a 0 has no effect. SIGSE Signaled System Error. -

Page 113: I/O Base Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip I/O Base Register Offset 0 9 8 7 6 5 4 3 2 1 0 Name IOBASE IOBA Operation Reset $0000 $0000 This register controls the mapping of the MPIC control registers in PCI I/O space. -

Page 114: Pci Slave Address (0,1,2 And 3) Registers

Registers This register controls the mapping of the MPIC control registers in PCI memory space. IO/MEM IO Space Indicator. This bit is hard-wired to a logic zero to indicate PCI memory space. MTYPx Memory Type. These bits are hard-wired to zero to indicate that the MPIC registers can be located anywhere in the 32-bit address space Prefetch. -

Page 115: Pci Slave Attribute/ Offset (0,1,2 And 3) Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip START Start Address. This field determines the start address of a particular memory area on the PCI bus which will be used to access MPC bus resources. The value of this field will be compared with the upper 16 bits of the incoming PCI address. -

Page 116: Config_Address

Registers RAEN Read Ahead Enable. If set, read ahead is enabled for the corresponding PCI slave. WPEN Write Post Enable. If set, write posting is enabled for the corresponding PCI slave. Write Enable. If set, the corresponding PCI slave is enabled for write transactions. -

Page 117: Pci I/O Config_Address Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip PCI I/O CONFIG_ADDRESS Register Offset $CF8 0 9 8 7 6 5 4 3 2 1 0 Name CONFIG_ADDRESS Operation Reset LEND = 0 MPC[39:32] MPC[47:40] MPC[55:48] MPC[63:56] LEND = 1 MPC[31:24] MPC[23:16] MPC[15:8]... -

Page 118: Pci I/O Config_Data Register

Registers Configuration cycle. A value of $0C sets AD bit 12. As the device number increments the AD bit increments until a the value of $1E sets AD bit 30. A value of $00 in device number field will select AD bit 31. The device number field must be all ones for Special cycles. -

Page 119: Raven Interrupt Controller Implementation

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip 2Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Raven Interrupt Controller Implementation Introduction The Raven Interrupt Controller (RavenMPIC) Features MPIC programming model Support for two processors Support for 16 external interrupts Support for 15 programmable Interrupt &... -

Page 120: Csr's Readability

Raven Interrupt Controller Implementation modes of activation; low level or active high positive edge. External interrupt 0 can be either level or edge activated with either polarity. The Interprocessor and timers interrupts are event activated. CSR’s Readability Unless explicitly specified, all registers are readable and return the last value written. -

Page 121: Spurious Vector Generation

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Spurious Vector Generation Under certain circumstances the RavenMPIC will not have a valid vector to return to the processor during an interrupt acknowledge cycle. In these cases the spurious vector from the spurious vector register will be returned. The following cases would cause a spurious vector fetch. -

Page 122: Raven-Detected Errors

Raven Interrupt Controller Implementation Raven-Detected Errors Raven-detected errors are grouped together and sent to the interrupt logic as a singular interrupt source. The interrupt delivery mode for this interrupt is distributed. The Raven Error Vector-Priority Register should be programed for high true level sensitive activation. For system implementations where the RavenMPIC controller is not used, the Raven-Detected Error condition will be made available by a signal which is external to the Raven ASIC. - Page 123 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip when the priority of the interrupt is greater than the priority contained in the task register for that processor, and when the priority of the interrupt is greater than any interrupt which is in-service for that processor. An interrupt is considered to be in service from the time its vector is returned during an interrupt acknowledge cycle until an EOI is received for that interrupt.

-

Page 124: Figure 2-4. Ravenmpic Block Diagram

Raven Interrupt Controller Implementation Block Diagram Description The description of the block diagram focuses on the theory of operation for the interrupt delivery logic. If the preceding section is a satisfactory description of the interrupt delivery modes and the reader is not interested the logic implementation, this section can be skipped. -

Page 125: Program Visible Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Program Visible Registers These are the registers which software can access. They are described in detail in the Register section. Interrupt Pending Register (IPR) The interrupt signals to RavenMPIC are qualified and synchronized to the clock by the IPR. -

Page 126: Interrupt Request Register (Irr)

Raven Interrupt Controller Implementation Interrupt Request Register (IRR) There is a Interrupt Request Register (IRR) for each processor. The IRR always passes the output of the IS except during Interrupt Acknowledge cycles. This guarantees that the vector which is read from the Interrupt Acknowledge Register is not changing due to the arrival of a higher priority interrupt. - Page 127 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Then one of these bits are delivered to each Interrupt Selector. Since this interrupt source can be multicast, each of these IPR bits must be cleared separately when the vector is returned for that interrupt to a particular processor.

-

Page 128: Table 2-8. Ravenmpic Register Map

Raven Interrupt Controller Implementation There is a possibility for a priority tie between the two processors when resolving external interrupts. In that case the interrupt is always delivered to processor 0. This case is not defined in the above rule set. MPIC Registers The following conventions are used in the Raven register charts: Read Only field. - Page 129 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip 0 9 8 7 6 5 4 3 2 1 0 IPI0 VECTOR-PRIORITY REGISTER $010a0 IPI1 VECTOR-PRIORITY REGISTER $010b0 IPI2 VECTOR-PRIORITY REGISTER $010c0 IPI3 VECTOR-PRIORITY REGISTER $010d0 SP REGISTER $010e0 TIMER FREQUENCY REPORTING REGISTER $010f0 TIMER 0 CURRENT COUNT REGISTER $01100...

- Page 130 Raven Interrupt Controller Implementation 0 9 8 7 6 5 4 3 2 1 0 INT. SRC. 2 DESTINATION REGISTER $10050 INT. SRC. 3 VECTOR-PRIORITY REGISTER $10060 INT. SRC. 3 DESTINATION REGISTER $10070 INT. SRC. 4 VECTOR-PRIORITY REGISTER $10080 INT. SRC. 4 DESTINATION REGISTER $10090 INT.

- Page 131 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip 0 9 8 7 6 5 4 3 2 1 0 RAVEN DETECTED ERRORS VECTOR-PRIORITY REGISTER $10200 RAVEN DETECTED ERRORS DESTINATION REGISTER $10210 IPI 0 DISPATCH REGISTER PROC. 0 $20040 IPI 1 DISPATCH REGISTER PROC. 0 $20050 IPI 2 DISPATCH REGISTER PROC.

-

Page 132: Feature Reporting Register

Raven Interrupt Controller Implementation Feature Reporting Register Offset $01000 0 9 8 7 6 5 4 3 2 1 0 Name FEATURE REPORTING NIRQ NCPU Operation Reset $00F NIRQ NUMBER OF IRQs. The number of the highest external IRQ source supported. The IPI, Timer, and Raven Detected Error interrupts are excluded from this count. -

Page 133: Global Configuration Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Global Configuration Register Offset $01020 0 9 8 7 6 5 4 3 2 1 0 Name GLOBAL CONFIGURATION Operation Reset RESET CONTROLLER. Writing a one to this bit forces the controller logic to be reset. This bit is cleared automatically when the reset sequence is complete. -

Page 134: Vendor Identification Register

2Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Raven Interrupt Controller Implementation 0Raven Interrupt Controller Implementation Vendor Identification Register Offset $01080 0 9 8 7 6 5 4 3 2 1 0 Name VENDOR IDENTIFICATION Operation Reset There are two fields in the Vendor Identification Register which are not defined for the RavenMPIC implementation but are defined in the MPIC specification. -

Page 135: Ipi Vector/Priority Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip The Soft Reset input to the 604 is negative edge-sensitive. IPI Vector/Priority Registers Offset IPI 0 - $010A0 IPI 1 - $010B0 IPI 2 - $010C0 IPI 3 - $010D0 0 9 8 7 6 5 4 3 2 1 0 Name IPI VECTOR/PRIORITY PRIOR... -

Page 136: Spurious Vector Register

Raven Interrupt Controller Implementation Spurious Vector Register Offset $010E0 0 9 8 7 6 5 4 3 2 1 0 Name VECTOR Operation Reset VECTOR This vector is returned when the Interrupt Acknowledge register is read during a spurious vector fetch. Timer Frequency Register Offset $010F0... -

Page 137: Timer Current Count Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Timer Current Count Registers Offset Timer 0 - $01100 Timer 1 - $01140 Timer 2 - $01180 Timer 3 - $011C0 0 9 8 7 6 5 4 3 2 1 0 Name TIMER CURRENT COUNT Operation... -

Page 138: Timer Vector/Priority Registers

Raven Interrupt Controller Implementation BASE COUNT. This field contains the 31 bit count for this timer. When a value is written into this register and the CI bit transitions from a 1 to a 0, it is copied into the corresponding Current Count register and the toggle bit in the Current Count register is cleared. -

Page 139: Timer Destination Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Timer Destination Registers Offset Timer 0 - $01130 Timer 1 - $01170 Timer 2 - $011B0 Timer 3 - $011F0 0 9 8 7 6 5 4 3 2 1 0 Name TIMER DESTINATION Operation... - Page 140 Raven Interrupt Controller Implementation MASK MASK. Setting this bit disables any further interrupts from this source. If the mask bit is cleared while the bit associated with this interrupt is set in the IPR, the interrupt request will be generated. ACTIVITY.

-

Page 141: External Source Destination Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip External Source Destination Registers Offset Int Src 0 - $10010 Int Src 2 -> Int Src 15 - $10030 -> $101F0 0 9 8 7 6 5 4 3 2 1 0 Name EXTERNAL SOURCE DESTINATION Operation... -

Page 142: Raven-Detected Errors Destination Register

Raven Interrupt Controller Implementation ACTIVITY. The activity bit indicates that an interrupt has been requested or that it is in-service. The ACT bit is set to a one when its associated bit in the Interrupt Pending Register or In-Service Register is set. SENSE SENSE. -

Page 143: Interprocessor Interrupt Dispatch Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Interprocessor Interrupt Dispatch Registers Offset Processor 0 $20040, $20050, $20060, $20070 Processor 1 $21040, $21050,$21060, $21070 0 9 8 7 6 5 4 3 2 1 0 Name IPI DISPATCH Operation Reset There are four Interprocessor Interrupt Dispatch Registers. - Page 144 Raven Interrupt Controller Implementation There is one Task Priority Register per processor. Priority levels from 0 (lowest) to 15 (highest) are supported. Setting the Task Priority Register to 15 masks all interrupts to this processor. Hardware will set the task register to $F when it is reset or when the Init bit associated with this processor is written to a one.

-

Page 145: Interrupt Acknowledge Registers

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip Interrupt Acknowledge Registers Offset Processor 0 $200A0 Processor 1 $210A0 0 9 8 7 6 5 4 3 2 1 0 Name VECTOR Operation Reset On PowerPC-based systems, Interrupt Acknowledge is implemented as a read request to a memory-mapped Interrupt Acknowledge register. -

Page 146: Programming Notes

Raven Interrupt Controller Implementation service by the associated processor. The write operation will update the In-Service register by retiring the highest priority interrupt. Reading this register returns zeros. Programming Notes External Interrupt Service The following summarizes how an external interrupt is serviced: 1. -

Page 147: Reset State

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip a. The device driver interrupt service routine associated with this interrupt vector is invoked. b. If the interrupt source was not the 8259, the interrupt handler issues an EOI request for this interrupt vector to the MPIC. If the interrupt source was the 8259 and any of the nested interrupt modes of the 8259 are enabled, the interrupt handler issues an EOI request to the 8259. -

Page 148: Operation

Raven Interrupt Controller Implementation Operation Interprocessor Interrupts Four interprocessor interrupt (IPI) channels are provided for use by all processors. During system initialization the IPI vector/priority registers for each channel should be programmed to set the priority and vector returned for each IPI event. During system operation a processor may generate an IPI by writing a destination mask to one of the IPI dispatch registers. -

Page 149: Interrupt Acknowledge Register

Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip highest priority source. Once an interrupt is acknowledged, only sources of higher priority will be allowed to interrupt the processor until the EOI command is received. This register should always be written with a value of zero which is the nonspecific EOI command. - Page 150 Raven Interrupt Controller Implementation architecture should recommend that, if the task priority register is not implemented with the processor, the task priority register should be updated only when the processor enter or exits an idle state. Only when the task priority register is integrated within the processor, (such that it can be accessed as quickly as the MSRee bit, for example), should the architecture require the task priority register to be updated synchronously with instruction execution.

- Page 151 Raven PCI Host Bridge & Multi-Processor Interrupt Controller Chip 2-84...

-

Page 152: Bit Ordering Convention

3Falcon ECC Memory Controller Chip Set Introduction The Falcon DRAM controller ASIC is designed for the MVME2600/2700 family of boards. It is used in sets of two to provide the interface between the PowerPC 60x bus and a 144-bit ECC-DRAM memory system. It also provides an interface to ROM/Flash. -

Page 153: Block Diagrams

Falcon ECC Memory Controller Chip Set – Does not provide TEA_ on Double-Bit Error. (Chip has no TEA_ pin.) ROM/Flash Interface – Two blocks with two 8-bit devices, or two 32-bit devices per block. Block Diagrams Figure 3-1 depicts a Falcon pair as it would be connected in a system. Figure 3-2 shows the Falcon’s internal data paths. -

Page 154: Figure 3-1. Falcon Pair Used With Dram In A System

Block Diagrams Lower DRAM ARRAYS Lower PowerPC Lower DRAM Data (32Bits) Data (64 Bits) Data Lower DRAM Address & Control Check Lower DRAM Check-bits (8 Bits) Upper PowerPC DRAM Address & ARRAYS Control Upper DRAM Data (64 Bits) Data Upper DRAM Address &... -

Page 155: Figure 3-2. Falcon Internal Data Paths (Simplified)

Falcon ECC Memory Controller Chip Set PowerPC DRAM Side Side (64 Bits) Latched D (64 Bits) (64 Bits) (8 Bits) (8 Bits) (8 Bits) Uncorrected Data (64 Bits) 1901 9609 Figure 3-2. Falcon Internal Data Paths (Simplified) -

Page 156: Figure 3-3. Overall Dram Connections

Block Diagrams BD_RAS_/CAS_ AC_RAS_/CAS_ RA/OE_/WE_ LOWER FALCON RD0-63 CKD0-7 DRAM DRAM DRAM DRAM BLOCK A BLOCK B BLOCK C BLOCK D LOWER LOWER LOWER LOWER BD_RAS_/CAS_ AC_RAS_/CAS_ RA/OE_/WE_ UPPER FALCON RD0-63 CKD0-7 DRAM DRAM DRAM DRAM BLOCK A BLOCK B BLOCK C BLOCK D UPPER... -

Page 157: Performance

Falcon ECC Memory Controller Chip Set Functional Description The following sections describe the logical function of the ASIC. The Falcon is designed to be used as a set of two chips. A pair of Falcons works with x1 or wider DRAM memory devices to form a memory system for the PowerPC 60x bus. -

Page 158: Single-Beat Reads/Writes

Functional Description Single-beat Reads/Writes Single-beat cycles to and from the PowerPC 60x bus do not achieve data rates as high as do four-beat cycles. The Falcon pair does take advantage of the PowerPC 60x address pipelining as much as possible for single-beat accesses. -

Page 159: Table 3-1. Powerpc 60X Bus To Dram Access Timing When Configured For

Falcon ECC Memory Controller Chip Set Table 3-1. PowerPC 60x Bus to DRAM Access Timing When Configured for 70ns Page Devices CLOCK PERIODS REQUIRED FOR: ACCESS TYPE Total Clocks Beat Beat Beat Beat 4-Beat Read after Idle (Quad-word aligned) 4-Beat Read after Idle (Quad-word misaligned) 4-Beat Read after 4-Beat Read 14/8... -

Page 160: Table 3-2. Powerpc 60X Bus To Dram Access Timing When Configured For 60Ns

Functional Description Table 3-2. PowerPC 60x Bus to DRAM Access Timing When Configured for 60ns Page Devices. CLOCK PERIODS REQUIRED FOR: ACCESS TYPE Total Clocks Beat Beat Beat Beat 4-Beat Read after Idle (Quad-word aligned) 4-Beat Read after Idle (Quad-word misaligned) 4-Beat Read after 4-Beat Read 11/7... -

Page 161: Table 3-3. Powerpc 60X Bus To Dram Access Timing When Configured For 50Ns Hyper Devices

Falcon ECC Memory Controller Chip Set Table 3-3. PowerPC 60x Bus to DRAM Access Timing When Configured for 50ns Hyper Devices CLOCK PERIODS REQUIRED FOR: ACCESS TYPE Total Clocks Beat Beat Beat Beat 4-Beat Read after Idle (Quad-word aligned) 4-Beat Read after Idle (Quad-word misaligned) 4-Beat Read after 4-Beat Read (Quad-word aligned) -

Page 162: Table 3-4. Powerpc 60X Bus To Rom/Flash Access Timing When

Functional Description ROM/Flash Speeds The Falcon pair provides the interface for two blocks of ROM/Flash. Each block can address up to 64Mbytes of memory depending on the type of the devices implemented for that block (8-bit, 32-bit, or 64-bit devices). The access times for ROM/Flash are shown in Tables 3-4 and 3-5. -

Page 163: Powerpc 60X Bus Interface

Falcon ECC Memory Controller Chip Set PowerPC 60x Bus Interface The Falcon pair has a PowerPC slave interface only. It has no PowerPC master interface. The slave interface is the mechanism for all accesses to DRAM, ROM/Flash, and Falcon registers/SRAM. Responding to Address Transfers When the Falcon pair detects an address transfer that it is to respond to, it asserts AACK_ immediately if there is no uncompleted PowerPC 60x bus... -

Page 164: Cache Coherency Restrictions

Functional Description Cache Coherency Restrictions The PowerPC 60x GBL_ signal must not be asserted in the CSR areas. L2 Cache Support The Falcon pair provides support for a look-aside L2 cache by implementing a hold-off input, L2CLM_. On cycles that select the Falcon pair, the Falcon pair samples L2CLM_ on the second rising edge of CLOCK after the assertion of TS_. -

Page 165: Table 3-6. Error Reporting

Falcon ECC Memory Controller Chip Set Note that the Falcon pair does not assert TEA_ on double-bit errors. In fact, the Falcon pair does not have a TEA_ signal pin and it assumes that the system does not implement TEA_. The Falcon can, however, assert machine check (MCP_) on double-bit error. -

Page 166: Error Logging

Functional Description Error Logging ECC error logging is facilitated by the Falcon because of its internal latches. When an error (single- or double-bit) occurs in the DRAMs to which a Falcon is connected, it records the address and syndrome bits associated with the data in error. -

Page 167: Rom/Flash Interface

Falcon ECC Memory Controller Chip Set ROM/Flash Interface The Falcon pair provides the interface for two blocks of ROM/Flash. Each block provides addressing and control for up to 16Mbytes of memory using two 8-bit devices, or up to 64Mbytes using two 32-bit devices or one 64-bit device. -

Page 168: Table 3-7. Powerpc 60X To Rom/Flash Address Mapping With Two

Functional Description b. only single-byte writes are allowed (all other sizes are ignored), c. all reads are allowed (multiple accesses are performed to the ROM/Flash devices when the read is for greater than one byte). When the device type status bit is set, the block’s ROM/Flash is considered to be two 32-bit read/write devices or one 64-bit read- only device. - Page 169 Falcon ECC Memory Controller Chip Set PowerPC 60x A0-A31 ROM/Flash A22-A0 ROM/Flash Device Selected $XX000002 $000002 Upper $XX000003 $000003 Upper $XX000004 $000000 Lower $XX000005 $000001 Lower $XX000006 $000002 Lower $XX000007 $000003 Lower $XX000008 $000004 Upper $XX000009 $000005 Upper $XX00000A $000006 Upper $XX00000B $000007...

-

Page 170: Table 3-8. Powerpc 60X Address To Rom/Flash Address Mapping With Two 32-Bit Or One 64-Bit Device(S)

Functional Description Table 3-8. PowerPC 60x Address to ROM/Flash Address Mapping with Two 32-bit or One 64-bit Device(s) ROM/Flash Device Selected PowerPC 60x A0-A31 ROM/Flash A22-A0 (Applies only when using two 32-bit Devices) $X0000000 $000000 Upper $X0000001 $000000 Upper $X0000002 $000000 Upper $X0000003... -

Page 171: Refresh/Scrub

Falcon ECC Memory Controller Chip Set ROM/Flash Device Selected PowerPC 60x A0-A31 ROM/Flash A22-A0 (Applies only when using two 32-bit Devices) $X3FFFFF8 $7FFFFF Upper $X3FFFFF9 $7FFFFF Upper $X3FFFFFA $7FFFFF Upper $X3FFFFFB $7FFFFF Upper $X3FFFFFC $7FFFFF Lower $X3FFFFFD $7FFFFF Lower $X3FFFFFE $7FFFFF Lower $X3FFFFFF... -

Page 172: Blocks A And/Or B Present, Blocks C And/Or D Present

Functional Description Blocks A and/or B Present, Blocks C and/or D present The Falcon pair performs refresh by doing a burst of four RAS_ cycles approximately once every 30 s. This increases to once every 15 s when certain DRAM devices are used. (Controlled by the ram_fref bit in the status registers.) RAS_ is asserted to blocks A and B during the first cycle, to blocks C and D during the second cycle, back to blocks A and B during the third cycle and to blocks C and D during the fourth cycle. -

Page 173: Chip Defaults

Falcon ECC Memory Controller Chip Set The tester The refresher/scrubber The Falcon pair’s arbiters assign priority with the refresher/scrubber highest, the tester next, and the PowerPC 60x bus lowest. When no requests are pending, the arbiter defaults to providing a PowerPC 60x bus grant. -

Page 174: Csr Accesses

Functional Description CSR Accesses An important part of the operation of a Falcon pair is that the value written to the internal control registers and SRAM in each of the two chips must be the same at all times. In order to facilitate this, writes to the pair itself are restricted to the upper Falcon only. -

Page 175: Figure 3-4. Data Path For Reads From The Falcon Internal Csrs

3Falcon ECC Memory Controller Chip Set Falcon ECC Memory Controller Chip Set Programming Model CSR Architecture The CSR (control and status register set) consists of the chip’s internal register set, its test SRAM, and its external register set. The base address of the CSR is hard coded to the address $FEF80000 (or $FEF90000 if the SIO pin is low at reset). -

Page 176: Figure 3-5. Data Path For Writes To The Falcon Internal Csrs

Programming Model MPC60x Master Upper FALCON Lower FALCON 1904 9609 Figure 3-5. Data Path for Writes to the Falcon Internal CSRs External register data that is written on the upper data bus goes through the upper Falcon, while data that is written on the lower data bus goes through the lower Falcon. -

Page 177: Figure 3-6. Memory Map For Byte Reads To The Csr

Falcon ECC Memory Controller Chip Set $FEF80000 Upper Falcon Upper Falcon $FEF80001 Upper Falcon $FEF80002 Upper Falcon $FEF80003 Lower Falcon $FEF80004 Lower Falcon $FEF80005 Lower Falcon $FEF80006 Lower Falcon $FEF80007 Upper Falcon $FEF80008 Upper Falcon $FEF80009 Lower Falcon $FEF807FF 1905 9609 Figure 3-6. -

Page 178: Figure 3-7. Memory Map For Byte Writes To The Internal Register Set And

Programming Model $FEF80000 Both Falcons Both Falcons $FEF80001 Both Falcons $FEF80002 Writes not allowed Here Both Falcons $FEF80003 $FEF80004 $FEF80005 $FEF80006 $FEF80007 Both Falcons $FEF80008 Both Falcons $FEF80009 $FEF807FF 1906 9609 Figure 3-7. Memory Map for Byte Writes to the Internal Register Set and Test SRAM 3-27... -

Page 179: Figure 3-8. Memory Map For 4-Byte Reads To The Csr

Falcon ECC Memory Controller Chip Set $FEF80000 Upper Falcon $FEF80004 Lower Falcon Upper Falcon $FEF80008 Lower Falcon $FEF8000C Lower Falcon $FEF807FC 1907 9609 Figure 3-8. Memory Map for 4-Byte Reads to the CSR Writes not allowed Here $FEF80000 Both Falcons $FEF80004 Both Falcons $FEF80008... -

Page 180: Register Summary

Programming Model Register Summary Table 3-9 on the following page shows a summary of the CSR. Note that the table only shows addresses for accesses to the upper Falcon. To get the addresses for accesses to the lower Falcon, add 4 to the address shown. Since the only way to write to the lower Falcon’s internal register set and test SRAM is to duplicate what is written to the upper Falcon, only the addresses shown in the table should be used for writes to them. -

Page 181: Table 3-9. Register Summary

Falcon ECC Memory Controller Chip Set Table 3-9. Register Summary BIT # ----> FEF80000 VENDID DEVID REVID FEF80008 RAM A RAM B RAM C RAM D FEF80010 FEF80018 RAM A BASE RAM B BASE RAM C BASE RAM D BASE FEF80020 CLK FREQUENCY FEF80028... - Page 182 Programming Model Table 3-9. Register Summary (Continued) FEF800A0 FEF800A8 TEST D1 (Upper 8 Bits) FEF800B0 TEST D1 (Middle 32 Bits) FEF800B8 TEST D1 (Lower 32 Bits) FEF800C0 FEF800C8 TEST D2 (Upper 8 Bits) FEF800D0 TEST D2 (Middle 32 Bits) FEF800D8 TEST D2 (Lower 32 Bits) FEF800E0 FEF800E8...

-

Page 183: Detailed Register Bit Descriptions

Falcon ECC Memory Controller Chip Set Table 3-9. Register Summary (Continued) FEF80C00 FEF87FF8 FEF88000 EXTERNAL REGISTER SET FEF8FFF8 BIT # ----> Notes 1. All shaded bit fields are reserved and read as zeros. 2. All status bits are shown in italics. 3. -

Page 184: Vendor/Device Register

READ ONLY RESET VENDID This read-only register contains the value $1507. It is the vendor number assigned to Motorola Inc. Note Note that the current value ($1507) of VENDID is not correct. The correct vendor ID should be $1057. This issue will be treated as just an erratum for now. -

Page 185: Revision Id/ General Control Register

Falcon ECC Memory Controller Chip Set Revision ID/ General Control Register ADDRESS $FEF80008 REVID NAME OPERATIO READ ZERO READ ONLY RESET REVID The REVID bits are hard-wired to indicate the revision level of the Falcon. The value for the first revision is $01, for the second is $02. -

Page 186: Table 3-10. Ram Spd1,Ram Spd0 And Dram Type

Programming Model ram fref Some DRAMs require that they be refreshed at the rate of 7.8 s per row rather than the standard 15.6 s per row. If any of the DRAM devices require the higher rate, then the ram fref bit should be left set, otherwise, it can be cleared. ram spd0,ram spd1 Together ram spd0,ram spd1 control DRAM timing used by the Falcon pair. -

Page 187: Table 3-11. Block_A/B/C/D Configurations

Falcon ECC Memory Controller Chip Set DRAM Attributes Register ADDRESS $FEF80010 NAME OPERATIO RESET ram a/b/c/d en ram a/b/c/d en enables accesses to the corresponding block of DRAM when set, and disables them when cleared. ram a/b/c/d siz0-2 These control bits define the size of their corresponding block of DRAM. -

Page 188: Dram Base Register

Programming Model Table 3-11. Block_A/B/C/D Configurations ram a/b/c/d Block Devices Used Technology Comments siz0-2 SIZE %100 128MB 8Mx8’s 64Mb 16Mx1’s 16Mb %101 256MB 16Mx4’s 64Mb 16Mx36’s 64Mb/16Mb SIMM/DIMM %110 1024MB 64Mx1’s 64Mb %111 Reserved DRAM Base Register ADDRESS $FEF80018 NAME RAM A BASE RAM B BASE RAM C BASE... -

Page 189: Clk Frequency Register

Falcon ECC Memory Controller Chip Set CLK Frequency Register ADDRESS $FEF80020 CLK FREQUENCY NAME OPERATIO READ/WRITE READ ZERO READ ZERO 42 P RESET CLK FREQUENCY These bits should be programmed with the hexadecimal value of the operating CLOCK frequency in MHz (i.e. - Page 190 Programming Model the refresh cycle has completed. This prevents the generation of illegal cycles to the DRAM when refdis is updated. rwcb rwcb, when set, enables the data from the 8 check-bits in this Falcon to be written and read on the PowerPC 60x data bus (DH24-31 for upper Falcon, DL24-31 for lower Falcon).

- Page 191 Falcon ECC Memory Controller Chip Set 1. During reads, data is presented to the PowerPC 60x data bus unaltered from the DRAM array. 2. During single-beat writes, data is written without correcting single- bit errors that may occur on the read portion of the read-modify- write.

-

Page 192: Error Logger Register

Programming Model Note that the INT_ and MCP_ pins are the only non-polled notification that a multiple-bit error has occurred. The Falcon pair does not assert TEA as a result of a multiple bit error. In Caution fact, the Falcon pair does not have a TEA_ signal pin and it assumes that the system does not implement TEA_. - Page 193 Falcon ECC Memory Controller Chip Set embt embt is set when the last error logged was due to a multiple-bit error. It is cleared when a 1 is written to the elog bit. The syndrome code is meaningless if embt is set. esbt esbt is set when the last error logged was due to a single- bit error.

-

Page 194: Error_Address Register

3Falcon ECC Memory Controller Chip Set 0Programming Model Programming Model Error_Address Register ADDRESS $FEF80038 NAME ERROR_ADDRESS OPERATIO READ ONLY RESET ERROR_ADDRESS These bits reflect the value that corresponds to bits 0-27 of the PowerPC 60x address bus at the last logging of an error during a PowerPC access to DRAM. -

Page 195: Table 3-12. Rtest Encodings

Falcon ECC Memory Controller Chip Set swen When set, swen allows the scrubber to perform write cycles. When cleared, swen prevents scrubber writes. rtest0,1,2 The rtest bits enable certain refresh counter test modes. Table 3-12 shows their encodings. Note that these test modes are not intended to be used once the chip is in a system. -

Page 196: Rom A Base/Size Register

Programming Model COL ADDRESS These bits form the column address counter used by the refresher/scrubber for all blocks of DRAM. The counter increments by one every eighth time the ROW ADDRESS rolls over. COL ADDRESS is readable and writable for test purposes. Note that within each block, the most significant bits of COL ADDRESS are only used when their DRAM devices are large enough to require them. -

Page 197: Table 3-13. Rom Block A Size Encoding

Falcon ECC Memory Controller Chip Set Also note that the combination of ROM_A_BASE and rom_a_siz should never be programmed such that ROM Block A responds at the same address as the CSR, DRAM, External Register Set, or any other slave on the PowerPC bus. -

Page 198: Table 3-15. Read/Write To Rom/Flash

Programming Model rom_a_rv rom_a_rv and rom_b_rv determine which if either of Blocks A and B is the source of reset vectors or any other access in the range $FFF00000 - $FFFFFFFF as shown in the table below. Table 3-14. rom_a_rv and rom_b_rv encoding rom_a_rv rom_b_rv Result... -

Page 199: Rom B Base/Size Register

Falcon ECC Memory Controller Chip Set Transfer Cycle Alignment rom_x_64 rom_x_we Falcon Response Size write 1-byte Normal termination, write occurs to ROM/Flash write 1-byte No Response write 4-byte Misaligned No Response write 4-byte Aligned No Response write 4-byte Aligned Normal termination, but no write to ROM/Flash write 4-byte... - Page 200 Programming Model Note that in addition to the programmed address, the first 1Mbyte of Block B also appears at $FFF00000 - $FFFFFFFF if the rom_b_rv bit is set. Also note that the combination of ROM_B_BASE and rom_b_siz should never be programmed such that ROM Block B responds at the same address as the CSR, DRAM, External Register Set, or any other slave on the PowerPC bus.

-

Page 201: Table 3-16. Rom Block B Size Encoding

Falcon ECC Memory Controller Chip Set rom b siz The rom b siz control bits are the size of ROM/Flash for Block B. They are encoded as shown in Table 3-16. Table 3-16. ROM Block B Size Encoding BLOCK rom b siz SIZE %000 1Mbytes... -

Page 202: Dram Tester Control Registers

Programming Model DRAM Tester Control Registers The tester should not be used by software. The trun and tsse bits (bits 0 and 1 of the register at address $FEF80060) should never be set. Caution 32-Bit Counter ADDRESS $FEF80100 NAME CTR32 OPERATIO READ/WRITE RESET... -

Page 203: Test Sram

Falcon ECC Memory Controller Chip Set Test SRAM ADDRESS $FEF80800 - $FEF80BF8 TEST SRAM NAME (64 Locations) OPERATIO READ ZERO READ ZERO READ/WRITE RESET X PL X PL X PL TEST SRAM The code that is executed by the DRAM Tester is contained in TEST SRAM. -

Page 204: Power-Up Reset Status Register 1

Programming Model Power-Up Reset Status Register 1 ADDRESS $FEF80400 NAME PR_STAT1 OPERATIO READ RESET PR_STAT1 PR_STAT1 (power-up reset status) reflects the value that was on the RD0-RD31 signal pins at power-up reset. This register is read-only. Note For descriptions of how this register is used in the MVME2600/2700 series boards, refer to the Falcon- Controlled System Registers in Chapter 1, especially the System Configuration Register and the Memory... -

Page 205: External Register Set

Falcon ECC Memory Controller Chip Set External Register Set ADDRESS $FEF88000 - $FEF8FFF8 NAME EXTERNAL REGISTER SET OPERATIO READ/WRITE RESET X PL EXTERNAL REGISTER SET The EXTERNAL REGISTER SET is user provided and is external to the Falcon pair. The Falcon pair provides a static RAM style interface for the external registers. -

Page 206: Software Considerations

3Falcon ECC Memory Controller Chip Set Software Considerations Software Considerations This section contains information that will be useful in programming a system that uses the Falcon pair. Parity Checking on the PowerPC Bus The Falcon does not generate parity on the PowerPC address or data buses. Because of this, the appropriate registers in the MPC60x should be programmed to disable parity checking for the address bus and for the data bus. -

Page 207: Sizing Dram

Falcon ECC Memory Controller Chip Set As with DRAM, software should not change control register bits that affect ROM/Flash while the affected Block is being accessed. This generally means that the ROM/Flash size, base address, enable, write enable, etc. are changed only while executing initially in the reset vector area ($FFF00000 - $FFFFFFFF). -

Page 208: Table 3-17. Sizing Addresses

Software Considerations 4. Write differing 64-bit data patterns to certain addresses within the block. The data patterns do not matter as long as each 64-bit data pattern is unique. The addresses to be written vary depending on the size that is currently being checked and are specified in Table 3-17. Table 3-18 also shows how PowerPC addresses correspond to DRAM row/column addresses. -

Page 209: Table 3-18. Powerpc 60X Address To Dram Address Mappings

Falcon ECC Memory Controller Chip Set Table 3-18. PowerPC 60x Address to DRAM Address Mappings RA ----> Block Size A19 A18 A10 A11 A12 A13 A14 A15 A16 A17 16MB A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A10 A11 A12 A13 A14 A15 A16 A17 32MB A18 A19 A20 A21 A22 A23 A24 A25 A26 A27... -

Page 210: Table 3-19. Syndrome Codes Ordered By Bit In Error

ECC Codes ECC Codes When the Falcon reports a single-bit error, software can use the syndrome that was logged by the Falcon (upper or lower depending where the error occurred) to determine which bit was in error. Table 3-19 shows the syndrome for each possible single bit error. -

Page 211: Table 3-20. Single-Bit Errors Ordered By Syndrome Code

Falcon ECC Memory Controller Chip Set Table 3-20. Single-Bit Errors Ordered by Syndrome Code Syn- Syn- Syn- Syn- Syn- Syn- Syn- Syn- drome drome drome drome drome drome drome drome ckd5 ckd6 ckd7 $A0 rd45 ckd0 rd42 rd38 rd37 ckd1 rd41 rd35 rd34... -

Page 212: Data Paths

Data Paths Data Paths Because of the Falcon “pair” architecture, data paths can be confusing. Figure 3-10 attempts to show the placement of data that is written by a PowerPC master to DRAM. Table 3-21 shows the same information in tabular format. -

Page 213: Figure 3-10. Powerpc Data To Dram Data Correspondence

Falcon ECC Memory Controller Chip Set rd63 rd32 Lower Falcon’s rd31 DRAM dl31 PowerPC Data dh31 rd63 Upper Falcon’s DRAM rd32 rd31 1909 9609 Figure 3-10. PowerPC Data to DRAM Data Correspondence 3-62... -

Page 214: Table 3-21. Powerpc Data To Dram Data Mapping

Data Paths Table 3-21. PowerPC Data to DRAM Data Mapping PowerPC DRAM Array Upper Falcon DRAM Lower Falcon DRAM A[27] A[28] Data Bits RA[12] Data Bits Data Bits dh[00:07] rd[00:07] dh[08:15] rd[08:15] dh[16:23] rd[16:23] dh[24:31] rd[24:31] dl[00:07] rd[00:07] dl[08:15] rd[08:15] dl[16:23] rd[16:23] dl[24:31]... - Page 215 Falcon ECC Memory Controller Chip Set 3-64...

-

Page 216: General Information

64-bit VMEbus to PCI interface in one device. Designed by Tundra Semiconductor Corporation in consultation with Motorola, the Universe is compliant with the VME64 specification and is tuned to the new generation of high speed processors. The Universe is ideally suited for CPU boards acting as both master and slave in the VMEbus system, and is particularly fitted for PCI local systems. -

Page 217: Architectural Overview

Universe (VMEbus to PCI) Chip – D64 (MBLT)/D32/D16/D08 master and slave – BLT, ADOH, RMW, LOCK Automatic initialization for slave-only applications Flexible register set, programmable from both the PCI bus and VMEbus ports Full VMEbus system controller functionality IEEE 1149.1 JTAG testability support, and Available in 313-pin Plastic BGA and 324-pin contact Ceramic Functional Description Architectural Overview... -

Page 218: Pci Bus Interface

Functional Description PCI Bus Interface Interrupter and Interrupt Handler DMA Controller These sections describe the operation of the Universe in terms of the different modules and channels illustrated in Figure 4-1. DMA Channel DMA bidirectional FIFO PCI Bus VMEbus Interface Interface VMEbus Slave Channel posted writes FIFO... -

Page 219: Vmebus Interface