Subscribe to Our Youtube Channel

Summary of Contents for Texas Instruments TMS570LC4357

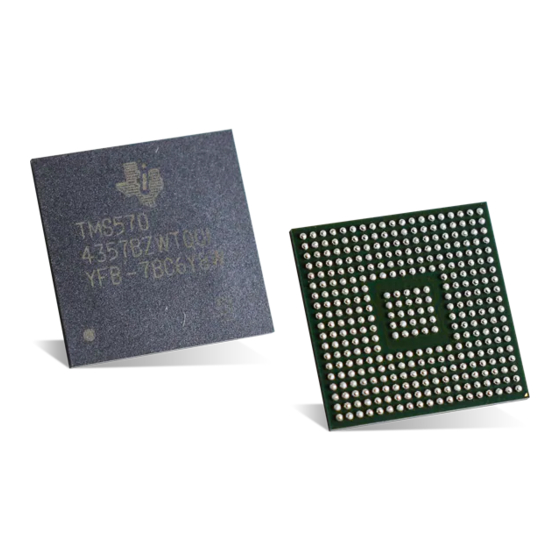

- Page 1 TMS570LC43x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual Literature Number: SPNU563A March 2018...

-

Page 2: Table Of Contents

....................3.2.3 SCM Control Block ......................How to Use SCM ..............3.3.1 How to Check the Parity Compare Logic ................3.3.2 How to Initiate Self-test Sequence Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 3 Logic Power Domain Control Register (LOGICPDPWRCTRL0) .......... 5.4.2 Logic Power Domain Control Register (LOGICPDPWRCTRL1) ..........5.4.3 Power Domain Clock Disable Register (PDCLKDISREG) ........5.4.4 Power Domain Clock Disable Set Register (PDCLKDISSETREG) SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 4 ........6.7.14 PINMMRnn: Special Functionality Multiplexing Control Registers ..............F021 Level 2 Flash Module Controller (L2FMC) ........................Overview ......................7.1.1 Features ....................7.1.2 Definition of Terms Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 5 7.10.27 Crossbar Access Time Threshold Register (ACC_THRESHOLD) ....7.10.28 Flash Error Detection and Correction Sector Disable Register 2 (FEDACSDIS2) ........7.10.29 Lower Word of Reset Configuration Read Register (RCR_VALUE0) SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 6 Fail Status Count Registers (FSRC0 and FSRC1) ............9.5.8 Fail Status Address Registers (FSRA0 and FSRA1) ............9.5.9 Fail Status Data Registers (FSRDL0 and FSRDL1) ................... 9.5.10 ROM Mask Register (ROM) Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 7 ..............11.3.1 How to Use NMPU in Functional Mode ..................11.3.2 How to Use Diagnostics ......................11.4 NMPU Registers ............... 11.4.1 MPU Revision ID Register (MPUREV) SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 8 13.3.8 CCM-R5F Status Register 4 (CCMSR4) ..............13.3.9 CCM-R5F Key Register 4 (CCMKEYR4) ......... 13.3.10 CCM-R5F Power Domain Status Register 0 (CCMPDSTAT0) ......................Oscillator and PLL Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 9 15.4.9 DCC Counter1 Value Register (DCCCNT1) ......15.4.10 DCC Counter1 Clock Source Selection Register (DCCCNT1CLKSRC) ......15.4.11 DCC Counter0 Clock Source Selection Register (DCCCNT0CLKSRC) .................... Error Signaling Module (ESM) SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 10 17.2.5 Digital Watchdog (DWD) ....................17.2.6 Low Power Modes ................17.2.7 Halting Debug Mode Behaviour ....................17.3 RTI Control Registers ..............17.3.1 RTI Global Control Register (RTIGCTRL) Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 11 ..................... 18.2.6 Raw Data Register ................18.2.7 Example DMA Controller Setup ..................18.2.8 Pattern Count Register ............18.2.9 Sector Count Register/Current Sector Register ......................18.2.10 Interrupt SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 12 19.3.2 Interrupt Handling at the CPU ................. 19.3.3 Software Interrupt Handling Options ................... 19.4 Interrupt Handling Inside VIM ................19.4.1 VIM Interrupt Channel Mapping ................19.4.2 VIM Input Channel Management Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 13 ....................20.2.14 Request Polarity .................... 20.2.15 Memory Protection ....................20.2.16 ECC Checking ....................20.2.17 ECC Testing ..................20.2.18 Initializing RAM with ECC .................... 20.2.19 Transaction Errors SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 14 ............... 22.2.5 ADC Magnitude Threshold Interrupts .................... 22.2.6 ADC Special Modes ................ 22.2.7 ADC Results’ RAM Special Features ............. 22.2.8 ADEVT Pin General Purpose I/O Functionality Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 15 22.3.50 ADC ADEVT Pin Pull Control Select Register (ADEVTPSEL) ....22.3.51 ADC Event Group Sample Cap Discharge Control Register (ADEVSAMPDISEN) ......22.3.52 ADC Group1 Sample Cap Discharge Control Register (ADG1SAMPDISEN) SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 16 N2HET Control Registers 1017 ..............23.4.1 Global Configuration Register (HETGCR) 1018 ............... 23.4.2 Prescale Factor Register (HETPFR) 1020 ............23.4.3 N2HET Current Address Register (HETADDR) 1021 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 17 ............... 23.5.19 HWAG Filter Register 2 (HWAFIL2) 1058 ............23.5.20 HWAG Angle Increment Register (HWAANGI) 1059 ......................23.6 Instruction Set 1060 ..................23.6.1 Instruction Summary 1060 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 18 24.5.5 Current Full Address A Register (HTU CFADDRA) 1178 ............24.5.6 Current Full Address B Register (HTU CFADDRB) 1179 ............24.5.7 Current Frame Count Register (HTU CFCOUNT) 1180 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 19 1243 ....................26.2.9 Transmit Process 1246 ..................... 26.2.10 Receive Process 1248 ....................26.2.11 FIFO Function 1249 ................... 26.2.12 Message Handling 1250 ....................26.2.13 Module RAMs 1258 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 20 27.8.7 Reception of Data Frames 1440 ................27.8.8 Reception of Remote Frames 1440 ................27.8.9 Reading Received Messages 1440 ............. 27.8.10 Requesting New Data for a Receive Object 1441 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 21 27.17.23 IF1/IF2 Command Registers (DCAN IF1CMD, DCAN IF2CMD) 1478 ........... 27.17.24 IF1/IF2 Mask Registers (DCAN IF1MSK, DCAN IF2MSK) 1481 ........27.17.25 IF1/IF2 Arbitration Registers (DCAN IF1ARB, DCAN IF2ARB) 1482 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 22 28.3.22 Interrupt Vector 0 (INTVECT0) 1568 ................28.3.23 Interrupt Vector 1 (INTVECT1) 1569 ..............28.3.24 SPI Pin Control Register 9 (SPIPC9) 1571 ..........28.3.25 Parallel/Modulo Mode Control Register (SPIPMCTRL) 1572 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 23 1641 ......................... 29.3 1642 ................29.3.1 LIN Communication Formats 1642 ....................29.3.2 LIN Interrupts 1659 .................... 29.3.3 LIN DMA Interface 1659 .................... 29.3.4 LIN Configurations 1660 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 24 30.2.1 SCI Frame Formats 1720 ....................30.2.2 SCI Timing Mode 1721 ....................30.2.3 SCI Baud Rate 1722 ............... 30.2.4 SCI Multiprocessor Communication Modes 1722 ......................30.3 SCI Interrupts 1725 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 25 I2C Module Data Validity 1770 ..............31.2.4 I2C Module Start and Stop Conditions 1771 ................... 31.2.5 Serial Data Formats 1771 ..................31.2.6 NACK Bit Generation 1773 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 26 1802 ......................EMAC/MDIO Module 1803 ....................... 32.1 Introduction 1804 ..................32.1.1 Purpose of the Peripheral 1804 ......................32.1.2 Features 1804 ..................32.1.3 Functional Block Diagram 1805 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 27 32.4.14 MDIO User PHY Select Register 1 (USERPHYSEL1) 1879 ....................32.5 EMAC Module Registers 1880 ..............32.5.1 Transmit Revision ID Register (TXREVID) 1883 ..............32.5.2 Transmit Control Register (TXCONTROL) 1883 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 28 32.5.50 Network Statistics Registers 1918 ..................Enhanced Capture (eCAP) Module 1927 ....................... 33.1 Introduction 1928 ......................33.1.1 Features 1928 ..................... 33.1.2 Description 1928 ......................33.2 Basic Operation 1929 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 29 34.3.19 eQEP Interrupt Clear Register (QCLR) 1991 ..............34.3.20 eQEP Capture Timer Register (QCTMR) 1992 ................. 34.3.21 eQEP Status Register (QEPSTS) 1993 ............ 34.3.22 eQEP Capture Timer Latch Register (QCTMRLAT) 1994 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 30 36.3.7 DMM Interrupt Offset 2 Register (DMMOFF2) 2134 ........36.3.8 DMM Direct Data Mode Destination Register (DMMDDMDEST) 2135 ..........36.3.9 DMM Direct Data Mode Blocksize Register (DMMDDMBL) 2135 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 31 38.3.1 eFuse Controller Connections to ESM 2188 ..............38.3.2 Checking for eFuse Errors After Power Up 2188 ..................... 38.4 eFuse Controller Registers 2191 ............38.4.1 EFC Boundary Control Register (EFCBOUND) 2191 SPNU563A – March 2018 Contents Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 32 38.4.3 EFC Error Status Register (EFCERRSTAT) 2194 ............... 38.4.4 EFC Self Test Cycles Register (EFCSTCY) 2194 ............38.4.5 EFC Self Test Signature Register (EFCSTSIG) 2195 ........................Revision History 2196 Contents SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 33 ........... 2-44. System Software Interrupt Request 3 Register (SSIR3) (offset = B8h) ........... 2-45. System Software Interrupt Request 4 Register (SSIR4) (offset = BCh) SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 34 2-92. Peripheral Power-Down Clear Register 0 (PSPWRDWNCLR0) (offset = A0h) ........2-93. Peripheral Power-Down Clear Register 1 (PSPWRDWNCLR1) (offset = A4h) ........2-94. Peripheral Power-Down Clear Register 2 (PSPWRDWNCLR2) (offset = A8h) List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 35 ....... 5-6. Power Domain Clock Disable Set Register (PDCLKDISSETREG) (offset = 24h) ......5-7. Power Domain Clock Disable Clear Register (PDCLKDISCLRREG) (offset = 28h) SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 36 7-14. Flash Port A Error and Status Register (FEDAC_PASTATUS) (offset = 14h) ........7-15. Flash Port B Error and Status Register (FEDAC_PBSTATUS) (offset = 18h) List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 37 ....... 8-11. L2RAMW Bank to Domain Mapping Register1 (BANK_DOMAIN_MAP1) (offset = 48h) ....................9-1. PBIST Block Diagram ................9-2. PBIST Memory Self-Test Flow Diagram SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 38 11-5. MPU Lock Register (MPULOCK) [offset = 04h] ..........11-6. MPU Diagnostics Control Register (MPUDIAGCTRL) [offset = 08h] ..........11-7. MPU Diagnostic Address Register (MPUDIAGADDR) [offset = 0Ch] List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 39 15-4. Clock1 Faster Than Clock0 - Results in an Error and Stops Counting ............. 15-5. Clock1 Not Present - Results in an Error and Stops Counting SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 40 ......... 16-36. ESM Interrupt Enable Set/Status Register 7 (ESMIESR7) [offset = 88h] ........16-37. ESM Interrupt Enable Clear/Status Register 7 (ESMIECR7) [offset = 8Ch] List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 41 ....... 17-45. Digital Windowed Watchdog Window Size Control (RTIWWDSIZECTRL) [offset = A8h] ......17-46. RTI Compare Interrupt Clear Enable Register (RTIINTCLRENABLE) [offset = ACh] SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 42 ............... 19-1. Block Diagram of Dual VIM for Safety Support ................. 19-2. Device Level Interrupt Block Diagram ................. 19-3. VIM Interrupt Handling Block Diagram List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 43 20-3. Example of a DMA Transfer Using Block Trigger Source ............20-4. DMA Request Mapping and Control Packet Organization ..............20-5. Control Packet Organization and Memory Map ....................20-6. DMA Transfer Example 1 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 44 20-53. BTC Interrupt Enable Set Register (BTCINTENAS) [offset = 10Ch] ..........20-54. BTC Interrupt Enable Reset Register (BTCINTENAR) [offset = 114h] ............20-55. Global Interrupt Flag Register (GINTFLAG) [offset = 11Ch] List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 45 20-102. DMA ECC Single-Bit Error Address Register (DMAECCSBE) [offset = 230h] ............. 20-103. FIFO A Status Register (FIFOASTAT) [offset = 240h] ............. 20-104. FIFO B Status Register (FIFOBSTAT) [offset = 244h] SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 46 21-33. LH28F800BJE-PTTL90 to EMIF Write Timing Waveforms ........21-34. Asynchronous m Configuration Register (m = 1, 2) (CEnCFG (n = 2, 3)) ................22-1. Channel Assignments of Two ADC Cores List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 47 22-48. ADC Group1 Sampling Time Configuration Register (ADG1SAMP) [offset = 64h] ......22-49. ADC Group2 Sampling Time Configuration Register (ADG2SAMP) [offset = 68h] ............22-50. ADC Event Group Status Register (ADEVSR) [offset = 6Ch] SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 48 22-97. ADC Parity Control Register (ADPARCR) [offset = 180h] ..........22-98. ADC Parity Error Address Register (ADPARADDR) [offset = 184h] ......... 22-99. ADC Power-Up Delay Control Register (ADPWRUPDLYCTRL) [offset = 188h] List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 49 23-36. Hardware Angle Generator Block Diagram ..................23-37. Angle Tick Generation Principle ................23-38. New Angle Tick Generation Architecture ..............23-39. Angle Generation Using Time Based Algorithm SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 50 23-86. Loop Back Pair Select Register (HETLBPSEL) 1041 ..............23-87. Loop Back Pair Direction Register (HETLBPDIR) 1042 ................23-88. N2HET Pin Disable Register (HETPINDIS) 1043 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 51 23-134. CNT Program Field (P31:P0) 1086 ..................23-135. CNT Control Field (C31:C0) 1086 ..................... 23-136. CNT Data Field (D31:D0) 1086 ................... 23-137. DADM64 Program Field (P31:P0) 1090 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 52 23-183. SHFT Program Field (P31:P0) 1124 ..................23-184. SHFT Control Field (C31:C0) 1124 ................... 23-185. SHFT Data Field (D31:D0) 1124 ..................23-186. WCAP Program Field (P31:P0) 1127 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 53 24-42. Initial Full Address A Register (HTU IFADDRA) 1175 ..............24-43. Initial Full Address B Register (HTU IFADDRB) 1175 ..........24-44. Initial N2HET Address and Control Register (HTU IHADDRCT) 1176 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 54 26-19. Swapping of IBCM and IBCR Bits 1253 ................26-20. Double Buffer Structure Output Buffer 1255 .................. 26-21. Swapping of OBCM and OBCR Bits 1255 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 55 26-69. Trigger Transfer to Communication Controller Reset 2 (TTCCR2) [offset_TU = ACh] 1304 ......26-70. Trigger Transfer to Communication Controller Set 3 (TTCCS3) [offset_TU = B0h] 1305 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 56 26-117. Error Interrupt Register (EIR) [offset_CC = 20h] 1341 ..............26-118. Status Interrupt Register (SIR) [offset_CC = 24h] 1343 ........... 26-119. Error Interrupt Line Select Register (EILS) [offset_CC = 28h] 1346 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 57 26-166. Transmission Request Register 4 (TXRQ4) [offset_CC = 32Ch] 1396 ..........26-167. Transmission Request Register 3 (TXRQ3) [offset_CC = 328h] 1396 ..........26-168. Transmission Request Register 2 (TXRQ2) [offset_CC = 324h] 1396 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 58 27-23. Bit Timing Register (DCAN BTR) [offset = 0Ch] 1462 ................ 27-24. Interrupt Register (DCAN INT) [offset = 10h] 1463 ................27-25. Test Register (DCAN TEST) [offset = 14h] 1464 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 59 ............. 27-73. IF3 Data A Register (DCAN IF3DATA) [offset = 150h] 1492 ............. 27-74. IF3 Data B Register (DCAN IF3DATB) [offset = 154h] 1492 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 60 ............... 28-42. SPI Pin Control Register 5 (SPIPC5) [offset = 28h] 1551 ............... 28-43. SPI Pin Control Register 6 (SPIPC6) [offset = 2Ch] 1552 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 61 28-88. Multi-buffer RAM Transmit Data Register (TXRAM) [offset = Base + 000-1FFh] 1607 ....... 28-89. Multi-buffer RAM Receive Buffer Register (RXRAM) [offset = RAM Base + 200-3FFh] 1610 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 62 29-33. SCI Set Interrupt Level Register (SCISETINTLVL) (offset = 14h) 1681 .......... 29-34. SCI Clear Interrupt Level Register (SCICLEARINTLVL) (offset = 18h) 1684 ................ 29-35. SCI Flags Register (SCIFLR) (offset = 1Ch) 1687 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 63 30-23. SCI Pin I/O Control Register 1 (SCIPIO1) [offset = 40h] 1754 ............30-24. SCI Pin I/O Control Register 2 (SCIPIO2) [offset = 44h] 1755 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 64 31-39. I2C Pins Slew Rate Select Register (I2CSRS) [offset = 6Ch] 1801 ........31-40. Difference between Normal Operation and Backward Compatibility Mode 1802 ..................32-1. EMAC and MDIO Block Diagram 1805 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 65 ......32-49. Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) (offset = 84h) 1887 ........32-50. Transmit Interrupt Mask Set Register (TXINTMASKSET) (offset = 88h) 1888 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 66 .................. 33-6. Counter and Synchronization Block 1933 ..................... 33-7. Interrupts in eCAP Module 1934 ..............33-8. PWM Waveform Details of APWM Mode Operation 1935 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 67 34-30. eQEP Watchdog Period Register (QWDPRD) [offset = 24h] 1982 ............34-31. eQEP Watchdog Timer Register (QWDTMR) [offset = 26h] 1982 ..............34-32. eQEP Control Register (QEPCTL) [offset = 28h] 1983 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 68 2031 .................... 35-30. PWM-Chopper Submodule 2033 ..............35-31. PWM-Chopper Submodule Operational Details 2034 ....... 35-32. Simple PWM-Chopper Submodule Waveforms Showing Chopping Action Only 2034 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 69 35-78. Trip Zone Digital Compare Event Select Register (TZDCSEL) [offset = 24h] 2085 ..............35-79. Trip-Zone Select Register (TZSEL) [offset = 26h] 2086 ............35-80. Trip-Zone Enable Interrupt Register (TZEINT) [offset = 28h] 2088 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 70 36-27. DMM Pin Control 5 (DMMPC5) [offset = 80h] 2148 ............... 36-28. DMM Pin Control 6 (DMMPC6) [offset = 84h] 2149 ............... 36-29. DMM Pin Control 7 (DMMPC7) [offset = 88h] 2151 List of Figures SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 71 ............38-5. EFC Self Test Cycles Register (EFCSTCY) [offset = 48h] 2194 ............38-6. EFC Self Test Cycles Register (EFCSTSIG) [offset = 4Ch] 2195 SPNU563A – March 2018 List of Figures Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 72 2-45. PLL Control Register 2 (PLLCTL2) Field Descriptions ............2-46. SYS Pin Control Register 10 (SYSPC10) Field Descriptions ..........2-47. Die Identification Register, Lower Word (DIEIDL) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 73 2-94. Peripheral Protection Clear Register 0 (PPROTCLR0) Field Descriptions ........2-95. Peripheral Protection Clear Register 1 (PPROTCLR1) Field Descriptions ........2-96. Peripheral Protection Clear Register 2 (PPROTCLR2) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 74 Error Generic Parity Register (ERR_GENERIC_PARITY) Field Descriptions ....4-9. Error Unexpected Transaction Register (ERR_UNEXPECTED_TRANS) Field Descriptions ..........4-10. Error Transaction ID Register (ERR_TRANS_ID) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 75 ............... 6-24. Pin Multiplexing Control Registers Field Descriptions ............... 6-25. Pin Multiplexing Control Registers Field Descriptions ............... 6-26. Pin Multiplexing Control Registers Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 76 7-46. FSM Sector Register 2 (FSM_SECTOR2) Field Descriptions ..........7-47. Flash Bank Configuration Register (FCFG_BANK) Field Descriptions ....................7-48. POM Control Registers ..........7-49. POM Global Control Register (POMGLBCTRL) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 77 10-13. STC Current Interval Count Register (STCCICR) Field Descriptions ..........10-14. Self-Test Global Status Register (STCGSTAT) Field Descriptions ............ 10-15. Self-Test Fail Status Register (STCFSTAT) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 78 13-13. CCM-R5F Key Register 2 (CCMKEYR2) Field Descriptions ........13-14. CCM-R5F Polarity Control Register (CCMPOLCNTRL) Field Descriptions ............13-15. CCM-R5F Status Register 4 (CCMSR4) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 79 ......16-26. ESM Influence ERROR Pin Set/Status Register 7 (ESMIEPSR7) Field Descriptions ......16-27. ESM Influence ERROR Pin Clear/Status Register 7 (ESMIEPCR7) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 80 18-1. CRC Modes in Which DMA Request and Counter Logic are Active or Inactive ..............18-2. Modes in Which Interrupt Condition Can Occur ....................18-3. Interrupt Offset Mapping List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 81 19-12. IRQ Index Offset Vector Register (IRQINDEX) Field Descriptions ..........19-13. FIQ Index Offset Vector Register (FIQINDEX) Field Descriptions ..........19-14. FIQ/IRQ Program Control Registers (FIRQPR) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 82 20-37. FTC Interrupt Enable Set Register (FTCINTENAS) Field Descriptions ........... 20-38. FTC Interrupt Enable Reset (FTCINTENAR) Field Descriptions ..........20-39. LFS Interrupt Enable Set Register (LFSINTENAS) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 83 20-87. DMA Memory Protection Region 6 Start Address Register (DMAMPR6S) Field Descriptions ....20-88. DMA Memory Protection Region 6 End Address Register (DMAMPR6E) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 84 21-27. SDRAM Configuration Register (SDCR) Field Descriptions ........... 21-28. SDRAM Refresh Control Register (SDRCR) Field Descriptions ........... 21-29. Asynchronous n Configuration Register (CEnCFG) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 85 22-33. ADC Group2 Sampling Time Configuration Register (ADG2SAMP) Field Descriptions ..........22-34. ADC Event Group Status Register (ADEVSR) Field Descriptions ............22-35. ADC Group1 Status Register (ADG1SR) Field Descriptions SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 86 22-81. ADC Group1 Maximum Count Register (ADG1MAXCOUNT) Field Descriptions ........ 22-82. ADC Group2 Current Count Register (ADG2CURRCOUNT) Field Descriptions ........ 22-83. ADC Group2 Maximum Count Register (ADG2MAXCOUNT) Field Descriptions List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 87 23-47. Suppression Filter Enable Register (HETSFENA) Field Descriptions 1040 ..........23-48. Loop Back Pair Select Register (HETLBPSEL) Field Descriptions 1041 ..........23-49. Loop Back Pair Direction Register (HETLBPDIR) Field Descriptions 1042 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 88 ................... 23-96. Event Encoding Format for WCAP 1128 ................. 23-97. Event Encoding Format for WCAPE 1130 ..................24-1. CPENA / TMBx Priority Rules 1139 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 89 24-49. Current Frame Count Register (HTU CFCOUNT) Field Descriptions 1180 ....... 24-50. Application Examples for Setting the Transfer Modes of CP A and B of a DCP 1181 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 90 26-25. Transfer Base Address (TBA) Field Descriptions 1285 ............26-26. Next Transfer Base Address (NTBA) Field Descriptions 1285 ............. 26-27. Base Address of Mirrored Status (BAMS) Field Descriptions 1286 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 91 26-75. Transfer to System Memory Interrupt Enable Reset 3 (TSMIER3) Field Descriptions 1317 ......26-76. Transfer to System Memory Interrupt Enable Set 4 (TSMIES4) Field Descriptions 1318 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 92 26-123. GTU Configuration Register 10 (GTUC10) Field Descriptions 1373 ........... 26-124. GTU Configuration Register 11 (GTUC11) Field Descriptions 1374 ........ 26-125. Communication Controller Status Vector Register (CCSV) Field Descriptions 1375 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 93 27-7. CAN Control Register (DCAN CTL) Field Descriptions 1456 ............27-8. Error and Status Register (DCAN ES) Field Descriptions 1459 ............27-9. Error Counter Register (DCAN ERRC) Field Descriptions 1461 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 94 28-21. SPI Pin Control Register 7 (SPIPC7) Field Descriptions 1554 ............28-22. SPI Pin Control Register 8 (SPIPC8) Field Descriptions 1555 ............. 28-23. SPI Transmit Data Register 0 (SPIDAT0) Field Descriptions 1556 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 95 29-5. Response Length Info Using IDBYTE Field Bits [5:4] for LIN Standards Earlier than 1.3 1644 ............29-6. Response Length with SCIFORMAT[18:16] Programming 1644 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 96 30-5. SCI Global Control Register 1 (SCIGCR1) Field Descriptions 1735 ............30-6. SCI Set Interrupt Register (SCISETINT) Field Descriptions 1738 ..........30-7. SCI Clear Interrupt Register (SCICLEARINT) Field Descriptions 1740 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 97 31-21. I2C Extended Mode Register (I2CEMDR) Field Descriptions 1794 ..............31-22. I2C Prescale Register (I2CPSC) Field Descriptions 1794 ............31-23. I2C Peripheral ID Register 1 (I2CPID1) Field Descriptions 1795 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 98 32-34. MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR) Field ......................Descriptions 1875 ..........32-35. MDIO User Access Register 0 (USERACCESS0) Field Descriptions 1876 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 99 32-81. Transmit Pause Timer Register (TXPAUSE) Field Descriptions 1913 .......... 32-82. MAC Address Low Bytes Register (MACADDRLO) Field Descriptions 1914 .......... 32-83. MAC Address High Bytes Register (MACADDRHI) Field Descriptions 1915 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 100 35-1. ePWM Module Control and Status Register Set Grouped by Submodule 1999 ................35-2. Submodule Configuration Parameters 2000 ..................35-3. Time-Base Submodule Registers 2002 ....................35-4. Key Time-Base Signals 2003 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 101 35-51. Digital Compare A Control Register (DCACTL) Field Descriptions 2101 ............ 35-52. Digital Compare Trip Select (DCTRIPSEL) Field Descriptions 2102 ........... 35-53. Digital Compare Filter Control Register (DCFCTL) Field Descriptions 2103 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 102 37-10. Pins Used for Data Communication 2166 ............ 37-11. RTP Trace Enable Register (RTPTRENA) Field Descriptions 2167 ............37-12. RTP Global Status Register (RTPGSR) Field Descriptions 2169 List of Tables SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 103 38-5. EFC Error Status Register (EFCERRSTAT) Field Descriptions 2194 ..........38-6. EFC Self Test Cycles Register (EFCSTCY) Field Descriptions 2194 ..........38-7. EFC Self Test Cycles Register (EFCSTSIG) Field Descriptions 2195 SPNU563A – March 2018 List of Tables Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 104: Preface

SPNU597— TMS570LC43x Hercules™ Development Kit (HDK) User's Guide. Describes the board level operations of the TMS570LC43 Hercules Development Kit (HDK). The HDK is based on the Texas Instruments TMS570LC4357 Microcontroller. The TMS570LC43 HDK is a table top card that allows engineers and software developers to evaluate certain characteristics of the TMS570LC4357 microcontroller to determine if the microcontroller meets the designer’s application requirements as... - Page 105 TI Embedded Processors Wiki— Texas Instruments Embedded Processors Wiki. Established to help developers get started with Embedded Processors from Texas Instruments and to foster innovation and growth of general knowledge about the hardware and software surrounding these devices. Trademarks Hercules, E2E are trademarks of Texas Instruments.

-

Page 106: Introduction

Chapter 1 SPNU563A – March 2018 Introduction ........................... Topic Page ............... Designed for Safety Applications .................... Family Description ................. Endianism Considerations Introduction SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 107: Designed For Safety Applications

A DMA driven hardware engine for the background calculation of CRC signatures during data transfers. • A centralized error reporting function including a status output pin to enable external monitoring of the device status. SPNU563A – March 2018 Introduction Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 108: Family Description

ECLK1 and ECLK2 terminals. The ECLK frequency is a user-programmable ratio of the peripheral interface clock (VCLK) frequency. This low frequency output can be monitored externally as an indicator of the device operating frequency. Introduction SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 109 With integrated safety features and a wide choice of communication and control peripherals, the TMS570LC43x is an ideal solution for high performance real time control applications with safety critical requirements. SPNU563A – March 2018 Introduction Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 110 N2HET2 SCI1 LIN1_TX LIN2/ LIN2_RX LIN2_TX SCI2 SCI3_RX SCI 3 SCI3_TX SCI4_RX SCI4 SCI4_TX I2C1_SDA I2C1 I2C1_SCL I2C2_SDA I2C2 I2C2_SCL Copyright © 2016, Texas Instruments Incorporated Introduction SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 111: Endianism Considerations

/**lt; 0xF448: CS to Transmit char T2CDELAY /**lt; 0xF449: Transmit to CS char T2EDELAY /**lt; 0xF44A: Transmit to ENA char C2EDELAY /**lt; 0xF44B: CS to ENA SPNU563A – March 2018 Introduction Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 112: Architecture

........................... Topic Page ..................... Introduction ..................Memory Organization ....................... Exceptions ......................Clocks ............System and Peripheral Control Registers Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 113: Introduction

Introduction www.ti.com Introduction The TMS570LC43x family of microcontrollers is based on the Texas Instruments TMS570 Architecture. This chapter describes specific aspects of the architecture as applicable to the TMS570LC43x family of microcontrollers. 2.1.1 Architecture Block Diagram The TMS570LC43x microcontrollers are based on the TMS570 Platform architecture, which defines the interconnect between the bus masters and the bus slaves. - Page 114 I2C2 DCAN4 w/ ECC eCAP STC1 FlexRay MibSPI1 1..6 CCM- ePWM MibSPI2 DCC2 1..7 MibSPI3 N2HET1 STC2 MibSPI4 N2HET2 MibSPI5 MibADC 1 LIN1/SCI1 MibADC 2 LIN2/SCI2 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 115: Definitions Of Terms

These fuses are programmed during the initial factory test of the device. The eFuse controller is designed so that the state of the eFuses cannot be changed once the device is packaged. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 116 General-purpose Input/Output The GIO module allows up to 16 terminals to be used as general-purpose Input or Output. Each of these are also capable of generating an interrupt to the CPU. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 117 Idle and Off modes in this device behave the same from power consumption perspective. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 118: Bus Master / Slave Access Privileges

There is a checker for each master and slave attached to the CPU Interconnect Subsystem. The checker checks the expected behavior against the generated Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 119: Interconnect Subsystem Runtime Status

4-1. Also see Section 2.5.3 for details on the registers definition. Figure 2-2. PCR MasterID Filtering MasterID Address/Control ID Decode Addr Decode Peripheral Select N PCRx SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 120: Memory Organization

NOTE: After the swap with the flash memory-mapped to 0x08000000, only 512kB of the flash memory from 0x08000000 to 0x0807FFFF will be accessible by the bus masters. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 121 0x68000000 Async RAM 0x64000000 0x60000000 RESERVED 0x33FFFFFF R5F-0 Cache 0x30000000 RESERVED 0x0847FFFF RAM - ECC 0x08400000 RESERVED 0x0807FFFF RAM (512kB) 0x08000000 RESERVED 0x003FFFFF Flash (4MB) 0x00000000 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 122: Memory-Map Table

TI OTP, Bank1 0xF008_2000 0xF008_3FFF Abort TI OTP, EEPROM 0xF008_E000 0xF008_FFFF Abort Bank TI OTP-ECC, Bank0 0xF00C_0000 0xF00C_03FF 512B Abort TI OTP-ECC, Bank1 0xF00C_0400 0xF00C_07FF 512B Abort Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 123 0xFB00_0000 0xFBFF_FFFF 16MB 512kB Accesses above 0xFB000200 generate abort. Memories under User PCR3 (Peripheral Segment 3) MIBSPI5 RAM PCS[5] 0xFF0A_0000 0xFF0B_FFFF 128kB Abort for accesses above SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 124 0x2000 and ends at address offset 0x217F. Wrap around for accesses between offsets 0x0180 and 0x3FFF. Abort generation for accesses beyond offset 0x4000. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 125 CoreSight TPIU CSCS[3] 0xFFA0_3000 0xFFA0_3FFF Reads return zeros, writes have no effect CSCS[4] 0xFFA0_4000 0xFFA0_4FFF Reads return zeros, writes have no effect SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 126 DCAN1 PS[8] 0xFFF7_DC00 0xFFF7_DDFF 512B 512B Reads return zeros, writes have no effect DCAN2 PS[8] 0xFFF7_DE00 0xFFF7_DFFF 512B 512B Reads return zeros, writes have no effect Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 127 TI during have no effect test STC2 (NHET1/2) PPSE[2] 0xFFFF_0800 0xFFFF_08FF 256B 256B Reads return zeros, writes have no effect PPSE[2] 0xFFFF_0A00 0xFFFF_0AFF 256B 256B Abort SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 128 System Module - PPS[7] 0xFFFF_FF00 0xFFFF_FFFF 256B 256B Reads return Frame 1 (see platform zeros, writes architecture have no effect specification) Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 129: Flash On Microcontrollers

The Flash banks are 288-bit wide bank with ECC support. • The flash bank7 can be programmed while executing code from flash bank0. • Code execution is not allowed from flash bank7. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 130 0x0038_0000 0x0039_FFFF 128K Bytes 0x003A_0000 0x003B_FFFF 128K Bytes 0x003C_0000 0x003D_FFFF 128K Bytes 0x003E_0000 0x003F_FFFF Bank 7: 128 kBytes 4K Bytes 0xF020_0000 0xF020_0FFF 4K Bytes 0xF021_F000 0xF021_FFFF Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 131 Table 2-4 shows only those registers that associate the bits to a specific interface for this device. See EPC chapter for the full list of registers. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 132 CPU SCR Uncorrectable ECC for DMA I/F Err Gen UERR Addr Reg Err Stat CPU SCR Uncorrectable ECC for PS_SCR_M I/F Uncorrectable Error Capture Block Unorrectable Error Event Source EPC Module Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 133 • Uncorrectable error address register for the UERRADDR0 31:0 DMA interface DMA interface Uncorrectable ECC for • Uncorrectable error address register for the UERRADDR1 31:0 PS_SCR_M interface PS_SCR_M interface SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 134: On-Chip Sram

HTU2 1 to 6 Two-port MIBSPI4 1 to 4 Two-port MIBSPI5 1 to 4 Two-port N2HET2 1 to 12 Two-port Two-port FRAY_INBUF_OUTBUF 1 to 8 Two-port Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 135 Single-port Single-port Single-port Reserved Single-port Single-port Single-port Single-port Reserved Single-port Single-port Single-port Single-port Single-port Single-port FRAY_TRBUF_MSGRAM 9 to 11 Single-port CPGMAC_CPPI Single-port R5_DCACHE_Dirty Single-port Reserved Single-port SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 136 NOTE: PBIST ROM_CLK can be prescaled from GCLK1 via ROM_DIV bits of the MSTGCR register. The valid ratio is either /1, /2 or /4 or /8. See Section 2.5.1.20 for detail. Maximum PBIST ROM_CLK frequency supported is 82.5MHz. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 137 DEV_MMIDONEn (where n = 31:0) (from memory modules to System module) Black indicates System register activity. Gray indicates inter-module activity, not accessible via System register. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 138 This is independent of whether the application has already initialized these RAMs using the auto-initialization method or not. The MibSPIx modules need to be released from reset by writing 1 to their SPIGCR0 registers before starting auto-initialization on their respective RAMs. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 139: Exceptions

An error occurring on an instruction fetch generates a prefetch abort. Errors occurring on data accesses generate data aborts. Aborts are also categorized as being either precise or imprecise. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 140 The A-bit in the CPSR is set by default. This means that no imprecise abort exception will occur. The application must enable imprecise abort exception generation by clearing the A- bit of the CPSR. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 141: System Software Interrupts

SSI registers. Both CPUs will see the SSI registers at the same address. The system module decodes the unique master ID corresponding to the CPU's access to the banked registers. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 142: Clocks

“Oscillator and PLL” user guide for more information on enabling / disabling the oscillator and PLL. On the TMS570LC43x microcontrollers, the clock sources 0, 4, and 5 are enabled by default. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 143: Clock Domains

VCLKA4_DIVR VCLKACON1.20 VCLK VCLKACON1[19:16] • Default frequency is VCLKA4/2 • Is disabled separately via the VCLKACON1 register's VCLKA4_DIV_CDDIS bit, if the VCLKA4 is not already disabled SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 144 VCLK frequency divided by 3. The application can configure the RTI1DIV field of the RCLKSRC register for dividing the selected clock source frequency by 1, 2, 4 or 8 to meet this requirement. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 145: Low Power Modes

Flash pump sleep -> active transition time Sleep None None CAN message, HF LPO SCI message Flash bank sleep -> standby transition time Flash bank standby -> active transition time SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... -

Page 146: Clock Test Mode

The clock test mode is controlled by the CLKTEST register in the system module register frame (see Section 2.5.1.31). The clock test mode is enabled by writing 0x5 to the CLK_TEST_EN field. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 147 Flash HD Pump Oscillator 1111 Oscillator Valid Status 10000 Reserved 10001 HCLK 10010 VCLK 10011 VCLK2 10100 VCLK3 10101-10110 Reserved 10111 EMAC clock output 11000-11111 Reserved SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 148: Embedded Trace Macrocell (Etm-R5)

The TMS570LC43x microcontrollers are targeted for use in several safety-critical applications. The following sections describe the internal or external monitoring mechanisms that detect and signal clock source failures. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 149 Section 2.4.6.4.1 Section 2.4.6.4.2. This mechanism can be used to use a known-good clock to measure the frequency of another clock. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 150 Table 2-17. DCC2 Counter 1 Clock / Signal Inputs Key [3–0] Clock Source [3–0] Clock / Signal Name Reserved PLL2 post_ODCLK/8 PLL2 post_ODCLK/16 3h-7h Reserved 8h-Fh VCLK All other values any value N2HET2[0] Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 151: System And Peripheral Control Registers

System Software Interrupt Request 1 Register Section 2.5.1.35 SSIR2 System Software Interrupt Request 2 Register Section 2.5.1.36 SSIR3 System Software Interrupt Request 3 Register Section 2.5.1.37 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 152 Global Status Register Section 2.5.1.48 DEVID Device Identification Register Section 2.5.1.49 SSIVEC Software Interrupt Vector Register Section 2.5.1.50 SSIF System Software Interrupt Flag Register Section 2.5.1.51 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 153 The ECLK pin is an output. Note: The ECLK pin is placed into GIO mode by clearing the ECPCLKFUN bit to 0 in the SYSPC1 register. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 154 Note: The ECLK pin is placed into GIO mode by clearing the ECPCLKFUN bit to 0 in the SYSPC1 register. The ECLK pin is placed in output mode by setting the ECPCLKDIR bit to 1 in the SYSPC2 register. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 155 Note: The ECLK pin is placed into GIO mode by clearing the ECPCLKFUN bit to 0 in the SYSPC1 register. The ECLK pin is placed in output mode by setting the ECPCLKDIR bit to 1 in the SYSPC2 register. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 156 Note: The ECLK pin is placed into GIO mode by clearing the ECPCLKFUN bit to 0 in the SYSPC1 register. The ECLK pin is placed in input mode by clearing the ECPCLKDIR bit to 0 in the SYSPC2 register. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 157 Note: The ECLK pin is placed into GIO mode by clearing the ECPCLKFUN bit to 0 in the SYSPC1 register. The ECLK pin is placed in input mode by clearing the ECPCLKDIR bit to 0 in the SYSPC2 register. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 158 Clock Source 5 High frequency LPO (Low Power Oscillator) clock Clock Source 6 PLL2 Clock Source 7 EXTCLKIN2 NOTE: Non-implemented clock sources should not be enabled or used. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 159 CSDIS register (offset 30h), the CSDISSET register (offset 34h), and the CSDISCLR register (offset 38h). NOTE: A list of the available clock sources is shown in the Table 2-29. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 160 CSDIS register (offset 30h), the CSDISSET register (offset 34h) and the CSDISCLR register (offset 38h). NOTE: A list of the available clock sources is shown in the Table 2-29. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 161 VCLK2 domain off. The VCLK2 domain is enabled. The VCLK2 domain is disabled. VCLKPOFF VCLK_periph domain off. The VCLK_periph domain is enabled. The VCLK_periph domain is disabled. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 162 The HCLK and VCLK_sys domains are enabled. The HCLK and VCLK_sys domains are disabled. GCLK1OFF GCLK1 domain off. The GCLK1 domain is enabled. The GCLK1 domain is disabled. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 163 Read: The VCLK2 domain is enabled. Write: The VCLK2 domain is unchanged. Read: The VCLK2 domain is disabled. Write: The VCLK2 domain is set to the enabled state. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 164 Read: The GCLK1 domain is enabled. Write: The GCLK1 domain is unchanged. Read: The GCLK1 domain is disabled. Write: The GCLK1 domain is set to the enabled state. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 165 Read: The VCLK2 domain is enabled. Write: The VCLK2 domain is unchanged. Read: The VCLK2 domain is disabled. Write: The VCLK2 domain is cleared to the enabled state. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 166 Read: The GCLK1 domain is enabled. Write: The GCLK1 domain is unchanged. Read: The GCLK1 domain is disabled. Write: The GCLK1 domain is cleared to the enabled state. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 167 Clock source5 is the source for GCLK1, HCLK, VCLK, VCLK2. Clock source6 is the source for GCLK1, HCLK, VCLK, VCLK2. Clock source7 is the source for GCLK1, HCLK, VCLK, VCLK2. 8h-Fh Reserved SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 168 VCLK is the source for peripheral asynchronous clock1. NOTE: Non-implemented clock sources should not be enabled or used. A list of the available clock sources is shown in Table 2-29. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 169 Clock source7 is the source for RTICLK1. 8h-Fh VCLK is the source for RTICLK1. NOTE: A list of the available clock sources is shown in the Table 2-29. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 170 Note: If the valid bit of the source of a clock domain is not set (that is, the clock source is not fully stable), the respective clock domain is disabled. NOTE: A list of the available clock sources is shown in the Table 2-29. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 171 Note: It is recommended that a value of Ah be used to disable the memory self-test controller. This value will give maximum protection from a bit flip inducing event that would inadvertently enable the controller. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 172 Note: It is recommended that a value of 5h be used to disable memory hardware initialization. This value will give maximum protection from an event that would inadvertently enable the controller. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 173 Note: Software should ensure that both the memory self-test global enable key (MSTGENA) and the memory hardware initialization global key (MINITGENA) are not enabled at the same time. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 174 Read: Memory self-test is not completed. Write: A write of 0 has no effect. Read: Memory self-test is completed. Write: The bit is cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 175 Reserved REFCLKDIV R/WP-0 R/WP-3h PLLMUL R/WP-4100h LEGEND: R/W = Read/Write; R = Read only; WP = Write in privileged mode only; -n = value after reset SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 176 100h VCO CLK INT CLK 5B00h x 92 VCO CLK INT CLK 5C00h x 93 VCO CLK INT CLK FF00h x 256 VCO CLK INT CLK Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 177 If frequency modulation is disabled and SPR_AMOUNT is changed, there is no effect on the PLL output clock. NV = 1/2048 NV = 2/2048 1FFh NV = 512/2048 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 178 ECPCLK slew control. This bit controls between the fast or slow slew mode. Fast mode is enabled; the normal output buffer is used for this pin. Slow mode is enabled; slew rate control is used for this pin. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 179 NOTE: Die Identification Information The die identification information will vary from unit to unit. This information is programmed by TI as part of the initial device test procedure. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 180 Read: OSC freq is > 20MHz and ≤ 80MHz. Write: A write of 1 has no effect. 15-13 Reserved Reads return 0. Writes have no effect. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 181 100.00% Default at Reset. 104.09 108.17 112.32 116.41 120.67 124.42 128.38 132.24 136.15 140.15 143.94 148.02 151.80x 155.50x 159.35% Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 182 65.78 70.75 75.63 80.61 85.39 90.23 95.11 100.00% Default at Reset 104.84 109.51 114.31 119.01 123.75 128.62 133.31 138.03 142.75 147.32 152.02 156.63 161.38 165.90 170.42 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 183 ECPCLKFUN bit to 1 in the SYSPC1 register. Clock going to ECLK pin is enabled. Others Clock going to ECLK pin is disabled. 15-12 Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 184 Flash HD Pump Oscillator Reserved HCLK VCLK VCLK2 VCLK3 15h-16h Reserved EMAC clock output 18h-1Fh Reserved NOTE: Non-implemented clock sources should not be enabled or used. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 185 Register key enable. ALL the bits can be written to only when the key is enabled. On reset, these bits will be set to 5h. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 186 Register key disable. All bits in this register will maintain their default value and cannot be (except Ah) written. Register key enable. ALL the bits can be written to only when the key is enabled. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 187 FBSLIP occurs when the KEY is programmed and a non-zero value is present in the COUNT field. 15-0 Reserved Reads return 0 or 1 and write in privilege mode. The functionality of this bit is unavailable in this device. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 188 SSKEY1 field matches the key (75h); therefore, byte writes cannot be performed on the SSDATA1 field. NOTE: This register is mirrored at offset FCh for compatibility reasons. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 189 SSKEY2 field matches the key (84h); therefore, byte writes cannot be performed on the SSDATA2 field. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 190 SSKEY3 field matches the key (93h); therefore, byte writes cannot be performed on the SSDATA3 field. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 191 SSKEY4 field matches the key (A2h); therefore, byte writes cannot be performed on the SSDATA4 field. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 192 Reads return 0. Writes have no effect. Reserved Reads return 0 or 1 depends on what is written in privileged mode. The functionality of this bit is unavailable in this device. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 193 Program memory (Flash) starts at address 0. eSRAM starts at address 800 0000h. Swapped memory-map: eSRAM starts at address 0. Program memory (Flash) starts at address 800 0000h. Others The device memory-map is unchanged. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 194 Reads return 0. Writes have no effect. CPU RESET CPU RESET. Only the CPU is reset whenever this bit is toggled. There is no system reset. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 195 Peripheral enable bit. The application must set this bit before accessing any peripheral. The global peripheral/peripheral memory frames are in reset. All peripheral/peripheral memory frames are out of reset. Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 196 VBUS clock or OSCIN as shown in the formula: V C L K o rO S C I E C L K E C P D IV Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 197 Software reset bits. Setting RESET1 or clearing RESET0 causes a system software reset. No reset will occur. 0, 2h-3h A global system reset will occur. 13-0 Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 198 No CPUx reset has occurred because of an interconnect self-test check. A reset has occurred to the CPUx because of the interconnect self-test check. Reserved Reads return 0. Writes have no effect. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 199 The external reset pin has not asserted a reset. A reset has been caused by the external reset pin. Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 200 JTAG data register. In either case, the autoload machine was not able or not allowed to complete its operation. Others Read: Reserved. Write: These bits are cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 201 Read: No oscillator failure has been detected. Write: The bit is unchanged. Read: An oscillator failure has been detected. Write: The bit is cleared to 0. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 202 0-1Fh Version. These bits provide the revision of the device. PLATFORM ID The device is part of the TMS570Px family. The TMS570Px ID is always 5h. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 203 A software interrupt has been generated by writing the correct key value to The SSIR3 register. A software interrupt has been generated by writing the correct key value to The SSIR4 register. 5h-FFh Reserved SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 204 Read: No IRQ/FIQ interrupt was generated since the bit was last cleared. Write: The bit is unchanged. Read: An IRQ/FIQ interrupt was generated. Write: The bit is cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 205: Secondary System Control Registers (Sys2)

Section 2.5.2.10 DIEIDH_REG1 Die Identification Register Upper Word Section 2.5.2.11 DIEIDL_REG2 Die Identification Register Lower Word Section 2.5.2.12 DIEIDH_REG3 Die Identification Register Upper Word Section 2.5.2.13 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 206 User and privileged mode (read): Privileged mode (write): 100h VCOCLK2 INTCLK2 5B00h x 92 VCOCLK2 INTCLK2 5C00h x 93 VCOCLK2 INTCLK2 FF00h x 256 VCOCLK2 INTCLK2 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 207 Reads return 0. Writes have no effect. 26-24 CLKDIV Clock divider/prescaler for CPU clock during logic BIST 23-0 Reserved Reads return 0. Writes have no effect. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 208 VBUS clock or OSCIN as shown in the formula: V C L K o rO S C I E C L K E C P D IV Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 209 Reserved Reads return 0. Writes have no effect. VCLK3R VBUS clock3 ratio. The ratio is HCLK divide by 1. The ratio is HCLK divided by 16. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 210 Reserved 109h Reserved NOTE: Non-implemented clock sources should not be enabled or used. A list of the available clock sources is shown in the Table 2-29. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 211 HCLK is equal to GCLK1 divide by 1. HCLK is equal to GCLK1 divide by 2. HCLK is equal to GCLK1 divide by 3. HCLK is equal to GCLK1 divide by 4. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 212 PLL RFSLIP filtering is enabled. Recommended to program Ah in this bit field. Enabling of the PLL RFSLIP occurs when the KEY is programmed and a non- zero value is present in the COUNT field. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 213 Disable ECC error generation for ECC errors detected on DMA Port A master by the CPU Interconnect Subsystem. Enable ECC error generation for ECC errors detected on DMA Port A master by the CPU Interconnect Subsystem. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 214 NOTE: Die Identification Information The die identification information will vary from unit to unit. This information is programmed by TI as part of the initial device test procedure. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 215 Value Description 31-0 DIEIDL2(95-64) 0-FFFF FFFFh This read-only register contains the lower word (95:64) of the die ID information. The contents of this register is reserved. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 216 Value Description 31-0 DIEIDH2(127-96) 0-FFFF FFFFh This read-only register contains the upper word (127:97) of the die ID information. The contents of this register is reserved. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

-

Page 217: Peripheral Central Resource (Pcr) Control Registers

Peripheral Frame 0 Master-ID Protection Register_L Section 2.5.3.30 304h PS0MSTID_H Peripheral Frame 0 Master-ID Protection Register_H Section 2.5.3.31 308h PS1MSTID_L Peripheral Frame 1 Master-ID Protection Register_L Section 2.5.3.32 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated... - Page 218 Peripheral Frame 23 Master-ID Protection Register_H Section 2.5.3.32 3C0h PS24MSTID_L Peripheral Frame 24 Master-ID Protection Register_L Section 2.5.3.32 3C4h PS24MSTID_H Peripheral Frame 24 Master-ID Protection Register_H Section 2.5.3.32 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 219 Section 2.5.3.38 Register_H 460h PPSE4MSTID_L Privilege Peripheral Extended Frame 4 Master-ID Protection Section 2.5.3.38 Register_L 464h PPSE4MSTID_H Privilege Peripheral Extended Frame 4 Master-ID Protection Section 2.5.3.38 Register_H SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 220 Section 2.5.3.38 Register_H 4D0h PPSE18MSTID_L Privilege Peripheral Extended Frame 18 Master-ID Protection Section 2.5.3.38 Register_L 4D4h PPSE18MSTID_H Privilege Peripheral Extended Frame 18 Master-ID Protection Section 2.5.3.38 Register_H Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 221 Peripheral Memory Frame Master-ID Protection Register1 Section 2.5.3.39 548h PCS2MSTID Peripheral Memory Frame Master-ID Protection Register2 Section 2.5.3.39 54Ch PCS3MSTID Peripheral Memory Frame Master-ID Protection Register3 Section 2.5.3.39 SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 222 Privileged Peripheral Memory Frame Master-ID Protection Section 2.5.3.40 Register5 5D8h PPCS6MSTID Privileged Peripheral Memory Frame Master-ID Protection Section 2.5.3.40 Register6 5DCh PPCS7MSTID Privileged Peripheral Memory Frame Master-ID Protection Section 2.5.3.40 Register7 Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 223 Read: The peripheral memory framen can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PMPROTSET1 and PMPROTCLR1 registers is set to 1. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 224 Read: The peripheral memory framen can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PMPROTSET1 and PMPROTCLR1 registers is cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 225 Read: The peripheral select quadrant can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PPROTSET0 and PPROTCLR0 registers is set to 1. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 226 Read: The peripheral select quadrant can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PPROTSET2 and PPROTCLR2 registers is set to 1. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 227 Read: The peripheral select quadrant can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PPROTSET0 and PPROTCLR0 registers is cleared to 0. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 228 Read: The peripheral select quadrant can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PPROTSET2 and PPROTCLR2 registers is cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 229 Read: The peripheral select quadrant can be written to only in privileged mode, but it can be read in both user and privileged modes. Write: The corresponding bit in PPROTSET3 and PPROTCLR3 registers is cleared to 0. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 230 Write: The bit is unchanged. Read: The peripheral memory clock[63-32] is inactive. Write: The corresponding bit in the PCSPWRDWNSET1 and PCSPWRDWNCLR1 registers is set to 1. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 231 Write: The bit is unchanged. Read: The peripheral memory clock[63-32] is inactive. Write: The corresponding bit in the PCSPWRDWNSET1 and PCSPWRDWNCLR1 registers is cleared to 0. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 232 Write: The bit is unchanged. Read: The clock to the peripheral select quadrant is inactive. Write: The corresponding bit in PSPWRDWNSET0 and PSPWRDWNCLR0 registers is set to 1. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 233 Write: The bit is unchanged. Read: The clock to the peripheral select quadrant is inactive. Write: The corresponding bit in PSPWRDWNSET2 and PSPWRDWNCLR2 registers is set to 1. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 234 Write: The bit is unchanged. Read: The clock to the peripheral select quadrant is inactive. Write: The corresponding bit in PSPWRDWNSET0 and PSPWRDWNCLR0 registers is cleared to 0. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 235 Write: The bit is unchanged. Read: The clock to the peripheral select quadrant is inactive. Write: The corresponding bit in PSPWRDWNSET2 and PSPWRDWNCLR2 registers is cleared to 0. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 236 Read: The clock to the debug frame is active. Write: The bit is unchanged. Read: The clock to the debug frame is inactive. Write: Set the bit to 1. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 237 Read: All master-ID registers are unlocked and available for writes. Write: Writes to master-ID registers are unlocked. Others Read: Writes to all master-ID registers are locked. Write: Write to master-ID registers are locked. SPNU563A – March 2018 Architecture Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...

- Page 238 1010 to enable Master-ID Check functionality. Read: The master-ID check is enabled. Write: Enable master-ID check. Others Read: The master-ID check is disabled. Write: Disable master-ID check. Architecture SPNU563A – March 2018 Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated...