Texas Instruments TMS370 Series Application Book

Hide thumbs

Also See for TMS370 Series:

- User manual (99 pages) ,

- Technical reference (142 pages) ,

- Getting started manual (42 pages)

Table of Contents

Advertisement

Quick Links

Download this manual

See also:

User Manual

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Texas Instruments TMS370 Series

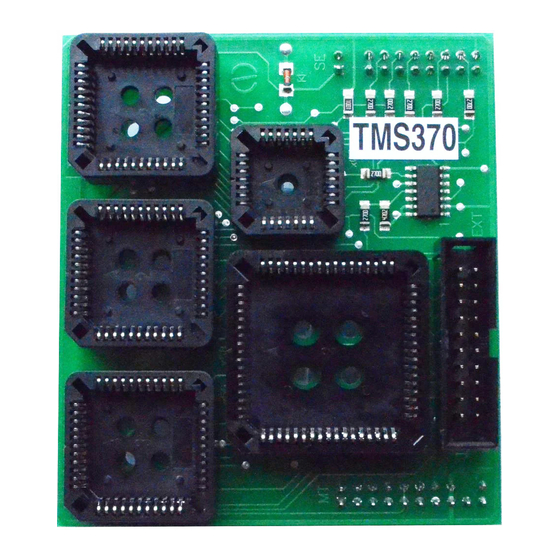

- Page 1 TMS370 Microcontroller Family Application Book 1996 8-Bit Microcontroller Family...

- Page 2 Printed in U.S.A., February 1996 SPNA017...

- Page 3 TMS370 Microcontroller Family Application Book...

- Page 4 TMS370 Microcontroller Family Application Book Microcontroller Products—Semiconductor Group SPNA017 February 1996...

- Page 5 IMPORTANT NOTICE Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

-

Page 6: Table Of Contents

Contents Part I: Introduction Introduction ..............Overview . - Page 7 Table Search With the TMS370 ..........Bubble Sort With the TMS370 .

- Page 8 The SCI – How It Works ............Choosing SCI Protocols and Formats .

- Page 9 Fast Method to Determine Parity ..........Automatic Baud Rate Calculation .

- Page 10 Display Dimming Application Routine ......... . . Speedometer and Tachometer Display Application .

- Page 11 Appendix B: A / D Errors ............Appendix C: External A / D Converters .

- Page 12 I/O Pins Proper Termination of Unused I/O Pins ........Introduction .

- Page 13 ..............Cost Effective Input Protection Circuitry for the Texas Instruments...

- Page 14 Advantages of Internal Diode Protection Circuitry ........Designing Input Protection Circuitry for TMS370 Microcontrollers .

- Page 15 List of Illustrations Binary Division With the TMS370 ..........1.

- Page 16 16. Flowchart for Time of Day Clock Application ........17.

- Page 17 ............Cost Effective Input Protection Circuitry for the Texas Instruments TMS370 Family of Microcontrollers .

- Page 18 Indeterminate Range for TTL and CMOS Input Thresholds (V = 5 V) ..........Switching to Vehicle Battery (Vbat) .

- Page 19 ......... . . Cost Effective Input Protection Circuitry for the Texas Instruments TMS370 Family of Microcontrollers .

-

Page 20: Part I: Introduction

Part I Introduction... - Page 22 Introduction Microcontroller Products—Semiconductor Group Texas Instruments...

-

Page 24: Introduction

Overview The TMS370 family consists of VLSI, 8-bit, CMOS microcontrollers with on-chip EEPROM storage and peripheral support functions. These devices offer superior performance in complex, real-time control applications in demanding environments. They are available with mask-programmable ROM and EPROM. Robust features in the TMS370 family of devices enhance performance and enable new application technologies. -

Page 26: Part Ii: Software Routines

Part II Software Routines Part II contains three sections: Arithmetic ......Memory Operations ....Specific Functionality . -

Page 28: 16 16 (32-Bit) Multiplication

16 16 (32-Bit) Multiplication With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... - Page 30 16 16 (32-Bit) Multiplication This example multiplies the 16-bit value in register pair R2, R3 by the value in register pair R4, R5. The results are stored in R6, R7, R8, R9; registers A and B are altered. Routine ******************************************************** 16-BIT MPY: X VALUE Y VALUE...

-

Page 32: Binary Division With The Tms370

Binary Division With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 34: Divide 16 Bit Number By 8 Bit Number

Divide 16-Bit Number by 8-Bit Number This routine divides a 16-bit number concatenated in R1:R2 by an 8-bit number in R3 to give a 16-bit quotient and an 8-bit remainder as shown in Figure 1. This routine uses the DIV instruction (note that a DIV function provides maximum values of 8-bits, 255 , for both quotient and remainder). -

Page 35: Divide 16 Bit Number By 16 Bit Number

Divide 16-Bit Number by 16-Bit Number This program divides a 16-bit dividend by a 16-bit divisor and produces a 16-bit quotient with a 16-bit remainder. All numbers are unsigned positive integers and can range from 0 to FFFFh. The same principle can be applied to larger or smaller divide routines to allow different-sized quotients, dividends, divisors, and remainders. -

Page 36: Bcd-To-Binary Conversion On The Tms370

BCD-to-Binary Conversion on the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... - Page 38 BCD-to-Binary Conversion This routine converts a four-digit BCD number to binary. The maximum BCD number is 9999 decimal. Operands originate and are stored in general-purpose RAM. The BCD number is composed of the four digits (D3, D2, D1, and D0) contained in the bytes DH and DL. The binary number is calculated by dividing the number into powers of ten (Binary = D3 1000 + D2 100 + D1 10 + D0 1).

-

Page 40: Binary-To-Bcd Conversion On The Tms370

Binary-to-BCD Conversion on the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 42: Register Values

Binary-to-BCD Conversion This program converts a 16-bit binary word (0 to 65.535) to a packed six-nibble BCD value. Table 1. Register Values Register Before After BCD MSbyte BCD LSbyte BINARY MSbyte ZERO BINARY LSbyte ZERO ZERO Routine .TEXT 7000H ;Absolute start address BN2BCD ;Prepare answer registers #16,R5... -

Page 44: Bcd String Addition With The Tms370

BCD String Addition With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 46: Register Values And Functions

BCD String Addition The following routine uses the addition instruction to add two multi-digit numbers together. Each number is a packed BCD string of less than 256 bytes (512 digits), stored at memory locations STR1 and STR2. This routine adds the two strings together and places the result in STR2. The strings must be stored with the most significant byte in the lowest numbered register. -

Page 48: Tms370 Floating Point Package

TMS370 Floating Point Package Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 50: Introduction

Introduction This report describes assembly language floating point math routines for the TMS370 family of microcontrollers. Floating point operations allow binary processors to carry out decimal, signed arithmetic. This package includes most of the common arithmetic and conversion routines used in floating point operations. -

Page 51: Floating Point Format

Floating Point Format Each number in this floating point format is 24 bits long. This includes eight bits for the exponent, fifteen for the mantissa, and the remaining bits for the sign. The format is as follows: E E E E E E E E S M M M M M M M M M M M M M M M The first byte is devoted to the exponent. -

Page 52: Floating Point Routines

Floating Point Routines Floating Point Addition / Subtraction ;Rev.1.0 ;Function name $fp_add,$fp_sub ;Purpose 1) Perform the addition of two floating point numbers. OP1 + OP2 2) Perform the subtraction of two floating point numbers. OP1 - OP2 ;Registers used Register Before After -------------------------------------------------------... - Page 53 2) If an operation results in a sum or difference which is greater than MAX_POS, then it is overflow. The result placed in registers R17, R18, R19 will be MAX_POS. 3) If an operation results in a sum or difference which is less than MAX_NEG, then it is overflow.

- Page 54 negneg #80h,a ;Eventual sign negative cont negpos #82h,a ;Result negative, set subtract flag. cont pospos ;Eventual sign positive cont #80h,msb1 ;Set the implied one. #80h,msb2 #0h,b noshift loop clrc msb1 ;Align the smaller mantissa. lsb1 djnz b,loop noshift jbit1 subflag,sub lsb1,lsb2 ;Add the mantissas.

- Page 55 maxval #0ffh,exp2 ;Create maximum value. movw #07fffh,lsb2 a,msb2 ;Set sign bit as appropriate.

-

Page 56: Floating Point Number Comparison

Floating Point Number Comparison ;Rev.1.0 ;Function name $fp_cmp ;Purpose Perform a comparison of two floating point numbers. The routine compares OP2 to OP1 and sets the status bits. The status result of this routine will be equivalent to an 8-bit integer cmp such as: OP1,OP2. - Page 57 $fp_cmp PUSH msb2 ;Check for different sign first. msb1,msb2 BTJZ #080h,msb2,SAMESIGN ;If MSB is 0, operands have same sign. msb2 ;Operands have different sign. Test ;MSB2 to check sign. Make ;appropriate dummy move to set NONEG ;status. SAMESIGN POP msb2 ;Restore MSB2 exp1,exp2 ;OP1 >...

-

Page 58: Floating Point Division

Floating Point Division ;Rev.1.0 ;Function name $fp_div ;Purpose Perform the division of two floating point numbers OP1 / OP2 ;Registers used Register Before After ------------------------------------------------------- Status | Modified OP1 exponent Modified OP1 mantissa MSB Modified OP1 mantissa LSB Modified OP2 exponent Result exponent OP2 mantissa MSB Result mantissa MSB... - Page 59 ;Stack space 4 bytes ;Notes 1) Some special considerations for floating point divide are: ZERO ZERO ZERO MAX_POS (if OP1 >= 0) MAX_NEG (if OP1 < 2) If a division results in a quotient which is greater than MAX_POS, then it is overflow. The result placed in registers R17, R18, R19 will be MAX_POS.

- Page 60 FINDSIGN PUSH ;Save registers. PUSH COUNTER PUSH FLAGS MAN1MSB,FLAGS ;Find sign of quotient. MAN2MSB,FLAGS ;If sign flags differ, FLAGS 7=1. #080h,FLAGS ;Clear other bits in FLAGS. #080h,MAN1MSB ;Set implied 1 in sign bit position. #080h,MAN2MSB SUBEXP ;Clear B for result of exponent math. EXP2,EXP1 ;Subtract exponents.

- Page 61 DIVEND DJNZ COUNTER,DIVIDE ;Next bit. Is divide done? ;Finish last rotate. DONE ;If MSB is not one, decrement EXP2 #01h,EXP2 ;and go back up and shift one more ;time. UNDERFLOW ;If EXP2 was zero, decrement has ;caused an underflow. SBIT0 OVFL ;Clear flag to show possible overflow ;condition has been corrected.

-

Page 62: Floating Point Multiplication

Floating Point Multiplication ;Rev.1.0 ;Function name $fp_mul ;Purpose Perform the multiplication of two floating point numbers. OP1 * OP2 ;Registers used Register Before After ------------------------------------------------------- Status | Modified OP1 exponent Modified OP1 mantissa MSB Modified OP1 mantissa LSB Modified OP2 exponent Result exponent OP2 mantissa MSB Result mantissa MSB... - Page 63 .global $fp_mul $fp_mul ;Check for OP1=ZERO. BTJO #0FFh,EXP2,CHK_OP2 BTJO #0FFh,MAN1LSB,CHK_OP2 BTJO #0FFh,MAN1MSB,CHK_OP2 MAN2LSB ;OP1 is ZERO, so clear OP2 as answer. MAN2MSB EXP2 ;Exit fp_mul CHK_OP2 ;Check for OP2=ZERO BTJO #0FFh,EXP2,FINDSIGN BTJO #0FFh,MAN2LSB,FINDSIGN BTJO #0FFh,MAN2MSB,FINDSIGN ;OP2 is ZERO, so done. Exit fp_mul.

- Page 64 CHK_UNDER ;Addition of exponents has ;underflowed. BTJZ #0FFh,EXP2,UNDERFLOW ;If exponent is not FF, then the ;exponent has definitely ;underflowed. SBIT1 UNDER_BIT ;Set bit to indicate that an ;underflow is possible if not ;corrected at end of multiplication ;routine. MULTIPLY PUSH ;Save value of B register.

-

Page 65: Floating Point Increment / Decrement

Floating Point Increment / Decrement ;Rev.1.0 ;Function name $fp_inc,$fp_dec ;Purpose 1) Increment a floating point number, i.e. add a 1.0 to it. OP1 + 1.0 2) Decrement a floating point number, i.e. subtract 1.0 from it. OP1 - 1.0 ;Registers used Register Before After... - Page 66 $fp_inc ;Entry point for increment. push ;Save A register. msb1,a ;Move msb1 to A register and set every #07fh,a ;bit except sign bit. #90h,exp1 ;Check to see if 1.0 is insignificant done ;compared with size of OP1. Exit if ;OP1 will not change. #71h,exp1 ;Check to see if OP1 is insignificant size_ok...

- Page 67 adjust exp1 ;Shift the mantissa and adjust the clrc ;exponent until an implied one is set. lsb1 msb1 adjust done2 greater lsb2 ;OP1 is greater than 1. Shift 1 so it msb2 ;has the same exponent as OP1. If the #07h,b ;exponents differ by <...

-

Page 68: Floating Point Number Test

Floating Point Number Test ;Rev.1.0 ;Function name $fp_tst ;Purpose Perform a test of the floating point number, similar to the hardware TST instruction for the A and B registers. ;Registers used Register Before After ------------------------------------------------------- Status | Set on result OP1 exponent OP1 exponent OP1 mantissa MSB... -

Page 69: Floating Point Number Negation

Floating Point Number Negation ;Rev.1.0 ;Function name $fp_neg ;Purpose Perform the sign negation of a floating point number -OP1 ;Registers used Register Before After ------------------------------------------------------- Status | Set on result MSB OP1 exponent Result exponent OP1 mantissa MSB Result mantissa MSB OP1 mantissa LSB Result mantissa LSB ;Size... -

Page 70: Floating Point To Signed 8-Bit Integer Conversion

Floating Point To Signed 8-Bit Integer Conversion ;Rev.1.0 ;Function name $fp_ftoi ;Purpose Convert a 24-bit signed floating representation of a number to an equivalent 8-bit signed integer representation. ;Registers used Register Before After ------------------------------------------------------- Status | Modified Result OP2 exponent OP2 exponent OP2 mantissa MSB OP2 mantissa MSB... - Page 71 bigminus ;Number is too small to be represented as a #80h,a ;signed integer. Set result to max negative ;value.

-

Page 72: Floating Point To Signed Long (16-Bit) Integer Conversion

Floating Point To Signed Long (16-Bit) Integer Conversion ;Rev.1.0 ;Function name $fp_ftol ;Purpose Convert a 24-bit signed floating representation of a number to an equivalent 16-bit signed integer representation. ;Registers used Register Before After ------------------------------------------------------- Status | Modified Signed integer MSB Signed integer LSB OP1 exponent OP1 exponent... - Page 73 expon jbit1 fsign,bigminus #0ffh,b ;Number is too big to be represented as a ;signed integer. #7fh,a ;Set result to max positive value. bigminus #0,b ;Number is too small to be represented as a #80h,a ;signed integer. Set result to max negative ;value.

-

Page 74: Floating Point To Unsigned 8-Bit Integer Conversion

Floating Point To Unsigned 8-Bit Integer Conversion ;Rev.1.0 ;Function name $fp_ftou ;Purpose Convert a 24-bit signed floating representation of a number to an equivalent 8-bit unsigned integer representation. ;Registers used Register Before After ------------------------------------------------------- Status | Modified Result OP1 exponent OP1 exponent OP1 mantissa MSB OP1 mantissa MSB... -

Page 75: Floating Point To Unsigned Long (16-Bit) Integer Conversion

Floating Point To Unsigned Long (16-Bit) Integer Conversion ;Rev.1.0 ;Function name $fp_ftoul ;Purpose Convert a 24-bit signed floating representation of a number to an equivalent 16-bit unsigned integer representation. ;Registers used Register Before After ------------------------------------------------------- Status | Modified Signed integer MSB Signed integer LSB OP1 exponent OP1 exponent... -

Page 76: Signed 8-Bit Integer To Floating Point Conversion

Signed 8-Bit Integer To Floating Point Conversion ;Rev.1.0 ;Function name $fp_itof ;Purpose Convert an 8-bit signed integer representation of a number to an equivalent 24-bit signed floating point representation. ;Registers used Register Before After ------------------------------------------------------- Status | Set on Result Signed integer Modified Result exponent... -

Page 77: Signed Long (16-Bit) Integer To Floating Point Conversion Comparison

Signed Long (16-Bit) Integer To Floating Point Conversion Comparison ;Rev.1.0 ;Function name $fp_ltof ;Purpose Convert a 16-bit signed long integer representation of a number to an equivalent 24-bit signed floating point representation. ;Registers used Register Before After ------------------------------------------------------- Status | Set on result MSB Signed integer MSB | Modified... -

Page 78: Unsigned Long (16-Bit) Integer To Floating Point Conversion

Unsigned Long (16-Bit) Integer To Floating Point Conversion ;Rev.1.0 ;Function name $fp_ultof ;Purpose Convert a 16-bit unsigned long integer representation of a number to an equivalent 24-bit signed floating point representation. ;Registers used Register Before After ------------------------------------------------------- Status | | Set on status of MSB Integer MSB Integer LSB Result exponent... -

Page 79: Unsigned 8-Bit Integer To Floating Point Conversion

Unsigned 8-Bit Integer To Floating Point Conversion ;Rev.1.0 ;Function name $fp_utof ;Purpose Convert an 8-bit unsigned integer representation of a number to an equivalent 24-bit signed floating point representation. ;Registers used Register Before After ------------------------------------------------------- Status | | Set on status of MSB Integer MSB Modified Integer LSB... -

Page 80: Memory Operations

Part II Software Routines Part II contains three sections: Arithmetic ......Memory Operations ....Specific Functionality . -

Page 82: Clear Ram Routine

Clear RAM Microcontroller Products—Semiconductor Group Texas Instruments... - Page 84 Clear RAM This routine clears all of the internal RAM registers. It can be used at the beginning of a program to initialize the first 256 bytes of RAM to a known value. Registers A and B have the following functions in this routine: Register A holds the initialization value.

-

Page 86: Ram Self-Test Routine

RAM Self-Test on the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 88: Ram Self-Test Routine

RAM Self-Test This routine performs a simple alternating 0/1 test on RAM locations R3–R255 by writing an AA,55 pattern to this RAM space and then checking the RAM for this pattern. The inverted pattern is then written to RAM and rechecked. Finally, the entire RAM is cleared. If an error is found, a bit is set in the flag register. The error flag bit should be cleared before the routine is started. -

Page 90: Rom Checksum On The Tms370

ROM Checksum on the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 92: Register And Function Values

ROM Checksum This routine checks the integrity of a 4K-byte ROM by performing a checksum on the entire ROM. All ROM bytes from 7002h to 7FDFh are added together in a 16-bit word. The sum is checked against the value at the beginning of the ROM (7000h, 7001h). - Page 93 Routine .TEXT 7000h ;Absolute start address FLAG .EQU R15 ;Error status CHECKSUM .EQU 12345 ;Value to be checked against .WORD CHECKSUM ;Put correct checksum into ;ROM ;Other initialization ;program here ROMCHK MOVW #7FDFh,R5 ;Starting address (end of ;memory) MOVW #0FDDh,R7 ;Number of bytes to add + 1 MOVW #0,R3 ;Reset summing register...

-

Page 94: Table Search With The Tms370

Table Search With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 96: Register And Expression Functions

Table Search The CMPA (Compare Register A Extended) instruction efficiently performs table searches. In the following example, a 150-byte table is searched for a match with a 6-byte string. The indexed addressing mode is used in this example and has the capability to search a 256-byte string, if needed. -

Page 98: Bubble Sort With The Tms370

Bubble Sort With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 100: Register Functions

Bubble Sort This routine sorts up to 256 bytes using the bubble sort method. Longer tables can be sorted using the indirect addressing mode. Table 1. Register Functions Register Function Temporary storage register Index into the RAM Holds flag to indicate a byte swap has been made Routine .TEXT 7000h ;Absolute start address... -

Page 102: Specific Functionality

Part II Software Routines Part II contains three sections: Arithmetic ......Memory Operations . -

Page 104: Routine To Read A 16-Key Keyboard

Routine to Read a 16-Key Keyboard Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 106: Register Properties

Keyboard Scan This routine reads a 16-key keyboard through port D, returns the hex digit of the key, and debounces the key to avoid noise. A valid-key flag is set when a new key is found. Figure 1. Keyboard Scan Connections to Port D TMS370 Keys Table 1. - Page 107 Routine .TEXT 07000h FLAG .EQU ; ”Swap has been made” flag DDIR .EQU P02F ; Port D data direction register DDATA .EQU P02E ; Port D data register THESE ASSIGNMENTS NEED TO BE DONE IN THE MAIN INITIALIZATION START #00,DDATA ;...

-

Page 108: Dtmf Generation With The Tms370

DTMF Generation With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... - Page 110 DTMF Generator The TMS370 can be used to generate DTMF dialing. The following routine can be used to generate all 16 DTMF digits. Routine ;*************************************************************************** .TITLE ”DTMF GENERATOR” ;*************************************************************************** *** DTMF GENERATOR *** GENERATES ALL 16 DTMF DIGITS CRYSTAL: 7.158MHZ (2X COLOR BURST) OUTPUT: 4 BIT DATA TO THE LOW NIBBLE OF B–PORT UPPER NIBBLE OF B–PORT IS LEFT UNMODIFIED B0 LSB...

- Page 111 CNT2 .EQU R029 ;FREQUENCY 2 COUNT ADJ2 .EQU R02A ;FREQUENCY 2 ADJUST ;R32DIGIT DURATION: 1 = 100 µS TIMER .EQU R02B BPORT .EQU P026 ;I/O PORT .EQU P027 ;DATA DIRECTION REGISTER ;*************************************************************************** ; CALCULATIONS: ; FREQ. = [(CNT,ADJ)/(# SAMPLES)] / 100.02794US ;...

- Page 112 ; SINE WAVE UPDATE LOOP – 179 MACHINE CYCLES = 100 µS ; ADJ ADDED TO PREVIOUS ADJUSTMENT TO SINE TABLE ; CNT ADDED W CARRY TO PREVIOUS LSB OF 16 BIT SINE TABLE ; MSB OF 16 BIT ADDR FIXED ;...

- Page 113 .WORD L1,H3 .WORD L2,H1 .WORD L2,H2 .WORD L2,H3 .WORD L3,H1 .WORD L3,H2 .WORD L3,H3 .WORD L1,H4 .WORD L2,H4 .WORD L3,H4 .WORD L4,H4 .WORD L4,H1 .WORD L4,H3 ;*************************************************************************** ; 1 COMPLETE PERIOD OF A SINE WAVE IN 64 TIME SAMPLES ; BITS ARRANGED: B0 LSB ;...

-

Page 114: System Integrity Check For The Tms370

System Integrity Check for the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... - Page 116 System Integrity This routine provides a simple software check of system integrity. It can be placed before the return (RTS) in a timer service routine to periodically examine the value of the return stack pointer (one byte) and return program counter value (two bytes) to see if they are within the normal operating range. Routine ;...

- Page 118 Part III Module Specific Application Design Aids Part III contains six sections: RESET Operations ....SPI and SCI Modules ....Timer and Watchdog Modules .

-

Page 120: Reset: Explanation Of Operation And Suggested Designs

Reset: Explanation of Operation and Suggested Designs Michael S. Stewart Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 122: Cold Start

Explanation of Operation and Suggested Designs The function of the RESET pin is to ensure an orderly software startup and hardware initialization. The TMS370 family of microcontrollers has three possible reset sources: 1. Low level input on the RESET pin 2. - Page 123 care must be taken in designing the reset circuitry. A typical reset circuit is illustrated in figure 1. Additional reset circuit information is available in the TMS370 Family User’s Guide. Figure 1. Typical Reset Circuit To other devices’ resets TMS370 10 kΩ...

- Page 124 Part III Module Specific Application Design Aids Part III contains six sections: RESET Operations ....SPI and SCI Modules ....Timer and Watchdog Modules .

-

Page 126: Spi And Sci Modules

Using the TMS370 SPI and SCI Modules Kevin L. Self Microcontroller Products—Semiconductor Group Texas Instruments Contributions by Paul Krause, Mark Palmer, and Al Lovrich... -

Page 128: Introduction

Introduction The TMS370 family of 8-bit microcontrollers has been designed with two serial communications modules: the serial peripheral interface (SPI) and the serial communications interface (SCI). These two modules greatly enhance the ability of the microcontroller to interface to other serial devices and common interfaces such as the industry standard RS-232. -

Page 129: Module Description: Serial Peripheral Interface (Spi)

Module Description: Serial Peripheral Interface (SPI) The SPI – How It Works The SPI module is a high-speed synchronous serial I / O port that shifts a serial bit stream of variable length and data rate between the device and other peripheral devices. The SPI is especially suited for multiprocessor and external peripheral communications where the designer needs high-speed synchronous data transfer. -

Page 130: Spi Operating Modes The Master Mode

SPI Operating Modes The Master Mode The SPI operates in one of two modes. The master mode is used when the SPI controls the data transfer. The master SPI initiates and controls the data transfer by issuing the SPICLK signal. Writing data to the SPIDAT buffer starts the transfer by starting SPICLK and shifting the data out of the SPIDAT shift register onto the SPISIMO pin. -

Page 131: Configuring The Spi Spi Data Format - Transmitting And Receiving

Figure 2. Master / Slave Connection SPI MASTER (MASTER/SLAVE = 1) SPI SLAVE (MASTER/SLAVE = 0) SIMO SIMO SLAVE IN/ MASTER SERIAL INPUT BUFFER SERIAL INPUT BUFFER (SPIBUF) (SPIBUF) É É É É É É É É SLAVE OUT SOMI SOMI SHIFT REGISTER SHIFT REGISTER... -

Page 132: The Spiclk And Data Transfer Rate

The SPICLK and Data Transfer Rate The rate at which data is transferred out of SPIDAT is programmed by the SPI bit rate bits (SPICCR.3–5). The rate can be set from SYSCLK / 2 to SYSCLK / 256 as shown in Table 2. The SPICLK rate is only used in the master mode;... -

Page 133: Controlling The Spi Through Interrupts And Flag Checking

A table showing the baud rates for common crystal frequencies versus SPI bit rate values is shown below in Table 3. The values were found using the formula SPI BAUD RATE = SYSCLK / (2 x 2 where b = bit rate specified in the SPI control register (SPICCR.5-3) (range 0–7). Table 3. -

Page 134: The Talk Bit And Multiprocessor Communications

2. If the program cannot do anything until the new data value is received or transmitted, the SPI INT flag can be continuously polled until it goes high. At that time, the character can be read or a new one transmitted. It is important to use one of the above methods to wait for the data before reading or writing again. -

Page 135: Data Integrity And The Spi

Data Integrity and the SPI The SPI was designed as a fast, simple interface to serial logic. As a result, it has no direct way to check for transmission errors. There are a number of software methods that can be used to check the integrity of the transmission. -

Page 136: Spi Module Software Examples

SPI Module Software Examples The following are examples of the various modes of operation and common software routines used in operating the SPI. The register equate for the following examples shown below. Common Equates SPICCR .equ P030 ;SPI Configuration Control Register SPICTL .equ P031... -

Page 137: Master Spi Configuration

Master SPI Configuration This routine shows how to configure the SPI to operate in the master mode. Data is sent to a peripheral device. The value needed for the SPI bit rate register is computed from the formula: SPI BAUD RATE = SYSCLK / (2 x 2 where b is the bit rate from SPICCR.3–5 in the range from 0–7. -

Page 138: Slave Spi Configuration

Slave SPI Configuration This routine shows how to use the SPI interrupt to interrupt a program and load two 8-bit characters from the SPI. The program will call the SPI interrupt upon receipt of an 8-bit character, save it, and wait for one more character. -

Page 139: Dynamic Bit Justification

Dynamic Bit Justification On occasion it may be necessary to transmit characters of length less than eight bits. As stated previously, the data needs to be left-justified for transmitting from SPIDAT and right-justified when read from SPIBUF. If the SPI is accessing several peripherals with different character lengths, it may be more efficient to have one subroutine justify all the transmitted data. -

Page 140: Address Recognition By Spi Routine

Address Recognition by SPI In multiprocessor systems using the SPI for communication, it is necessary to keep conversations limited to two microprocessors at a time. The TALK bit is used to disable the transmit ability of a TMS370 in slave mode until it sees its address, MYADDRESS, at which time it will transmit a byte of data. -

Page 141: Spi Module Specific Applications

SPI Module Specific Applications Vacuum Fluorescent Display Driver Use SPI to Transmit Data to Serial Shift Register One common and very practical use of an SPI is sending serial data to a display. The use of simple software routines can simplify your design and eliminate expensive external hardware such as decoders. This example interfaces a TMS370C010 microcontroller to a vacuum fluorescent display. -

Page 142: Vacuum Florescent Interface

Figure 3. Vacuum Florescent Interface 4 DIGIT DISPLAY TMS0170 COMMON ANODE SEGMENT 1–A BIT 33 SEGMENT 1–B BIT 32 SEGMENT 1–C BIT 31 SEGMENT 1–D BIT 30 SEGMENT 1–E BIT 29 SEGMENT 1–F BIT 28 SPISIMO DATA IN SEGMENT 1–G BIT 27 SPICLK CLOCK... - Page 143 This display update routine is controlled by T1 interrupts. The compare 1 and compare 2 registers are set to control the refresh rate and intensity, respectively. Because the display is pulsed more frequently than new values are calculated, an interval counter is used to specify when it is time to update the display value. In this example, the following parameters are used: Refreshes / s = 100 (eliminates flicker in display)

- Page 144 Routine The source code for this application is as follows: .title “Display Driver” This routine uses the SPI and T1 modules to output values to a serial display. The display is updated every 0.5 seconds. Display intensity is changed by toggling TlIC/CR pin. SPICCR .equ P030...

- Page 145 DIGIT1 .equ ; ” DIGIT2 .equ ; ” DIGIT3 .equ ; ” TEMPMSB .equ TEMPLSB .equ DUMMY .equ Assign values for display intensity, and refresh period. TIMER .equ 3125 ;100 interrupts/sec @ 5 MHz BRIGHT .equ TIMER*9 / 10 ;Max intensity = 90 DIFF .equ BRIGHT ^(TIMER*4/ 10)

- Page 146 ;T1. Enable Timer1 & SPI #005h,T1CTL3 ;Enable T1EDGE INT, enable T1C1 INT. #066h,SPICCR ;Release SPI. #0F0h,B ;Move stack pointer value to B. LDSP ;Set stack pointer. EINT ;Global interrupt enable MAIN ;Main loop Place major portion of code here. This part of the program should calculate the value to be displayed, scale it from 0 to 9999, and store the result in DISPMSB and DISPLSB.

- Page 147 #060h,T1PC2 ;Reenable T1PWM. T1CCLSB,TEMPLSB ;Get current display intensity. T1CCMSB,TEMPMSB #LO(DIFF),TEMPLSB ;Toggle display intensity. #HI(DIFF),TEMPMSB TEMPMSB,T1CCMSB ;Update display intensity TEMPLSB,T1CCLSB #005h,T1CTL1 ;Restart timer. #07Fh,T1CTL3 ;Clear T1IC / CR interrupt flag. DONE ;End of display toggle: wait for ;update. TIMERINT DJNZ ICOUNT,NOTNOW ;Is it time for new value be ;displayed? ;If it is not, do not calc new value.

- Page 148 characters, which gives a maximum value of 9999. #000h,DCOUNT ;Set counter for data address. NEXTCHAR DCOUNT,B ;Store DCOUNT in temp register. *DIGIT0[B],A ;Move BCD value of current char into XCHB ;Move BCD value into B. *TABLE[B],A ;Look up 7-seg value and store in A. A,SPIDAT ;Move character byte into SPIDAT ;register.

- Page 149 Set up interrupt vector addresses .sect “Vectors”,07FF4h .word DISPLAY ;T1 interrupt .word START ;All other vectors go to ’START’. .word START .word START .word START .word START...

-

Page 150: Bootstrap Loader Reprogram Data Or Program Memory Through Spi Port

Bootstrap Loader Reprogram Data or Program Memory through SPI Port The SPI is very useful as a bootstrap loader for loading program or data information directly into RAM, EPROM, or EEPROM. The TMS370 family SPI and instruction set provide a fast, efficient way of moving serial data directly into memory. -

Page 151: Dsp Controller Interface Tms370 Spi To Tms320C25 Dsp

DSP Controller Interface TMS370 SPI to TMS320C25 DSP This example shows how the SPI can be used to communicate with other microprocessors. The exact method of communication varies from system to system, but the key parts can be shown to demonstrate how to interface the TMS320C25 and TMS370 serial ports. -

Page 152: Continuous Mode No Frame Synchronization Pulse

TMS320C25 wants to transmit: C25 loads DXR. ;Places data to be transmitted in buffer. C25 toggles XF low. ;Generates TMS370 INT3. TMS370 executes INT3 routine. TMS370 wants to transmit: TMS370 sets SPEAK370 bit. ;TMS370 initiates the transmission. TMS370 toggles A0 low. ;Generates TMS370 INT2. - Page 153 Different protocols have different benefits, and the protocol used depends on the requirements of the system. If the system requires continual transmission of data from the C25, then the no frame synchronization mode (no FSX / FSR pulse) allows greater throughput and less system overhead on the TMS370 processor.

- Page 154 COM370 .equ ;Status register for TMS320–TMS370 comm SPEAK370 .dbit 0,COM370 ;=1 if TMS370 is transmitting FIRSTX .dbit 7,COM370 ;=1 C25 in continuous mode, need to ;generate first sync pulse DATAIN .equ ;Received data DATAOUT .equ ;Data to be transmitted .text 07000H START DINT ;Disable all interrupts.

- Page 155 part to execute the INT1 service routine, which will prepare it to initiate a transfer. Since both transmissions by the TMS320 and TMS370 involve calling the TMS370 INT1 routine, the SPEAK370 bit is set by the TMS370 when it initiates a transfer. The data to be transmitted is stored in DATA OUT and received data, if it is valid, will be stored in DATA IN.

- Page 156 SBIT0 SPEAK370 ;Clear TMS370 transmission flag. ;End of INT3 routine. INTR2 ;Interrupt 2 routine #01H,INT2 ;Clear and enable interrupt 2 flag. INTR1 ;Interrupt 1 routine #01H,INT1 ;Clear and enable interrupt 1 flag. Set up interrupt vector addresses. .sect “Vectors”,07FF4H .word START ;Vector goes to ’START’.

- Page 157 START .equ DINT ;Disable interrupts. LDPK ;Point to page 0. FORT ;Set serial port to 8-bit mode. LALK 0ffc4h ;Enable interrupt 2. SACL STXM ;FSX is output. RFSM ;Continuos mode ;Zero the accumulator. SACL ;Initialize receiver register. SACL ;Initialize transmit register. EINT Main body of program goes here.

- Page 158 SACL DATA ;Store received data. RXISR: .equ ;Serial receive interrupt EINT ;Enable interrupts. XMTISR:.equ ;Initiate data transfer to 370 routine. ;Toggle XF flag low, causes 370 ;interrupt ;and then high, to clear only, want 370 ;INT3 ;routine to execute once.

-

Page 159: Sci Module Description

SCI Module Description The SCI – How It Works The SCI module is a high-speed serial I / O port that permits asynchronous or isosynchronous communication between the TMS370 and other peripheral devices such as keyboards, display terminal drivers, and RS-232 interfaces. The SCI transmit and receive registers are double-buffered to prevent data collisions. -

Page 160: Sci Data Frame Formats

Choosing SCI Protocols and Formats Data formatting is a characteristic of the SCI that sets it off from standard serial communications interfaces such as shift registers. The basic unit of data is called a character and is one to eight bits in length. Each character of data is formatted with a start bit, one or two stop bits, and optional parity and address bits. -

Page 161: Transmitter Character Bit Length

Table 4. Transmitter Character Bit Length Character Char2 Char1 Char0 Length 3. Parity: Parity is a method of checking the integrity of a transmitted / received character. It sends an extra bit with the character to make sure that the sum of 1s in the character is an odd or even number. -

Page 162: Asynchronous Communication Format

Operating Modes of the SCI The SCI has two modes of operation. The first, asynchronous, is the most commonly used mode and requires no synchronizing clock between the TMS370 and a peripheral device. When transmitting in the asynchronous mode, each bit is held for 16 shift-clock cycles. This repetition ensures that the data will be present long enough for the unsynchronized receiver to get valid data. -

Page 163: Asynchronous Baud Rate Register Values For Common Sci Baud Rates

Setting the SCICLK Pins and Baud Rate The SCICLK is usually configured internally for asynchronous communications, but can be external if your application requires it. For isosynchronous communications, the clock can be configured internally or externally, depending on whether the TMS370 will be issuing the clock signal. If the SCICLK pin is not configured as the serial clock (SCICLK FUNCTION = 0), then the pin may be used for general purpose I / O by setting SCICLK DATA DIR (SCIPC1.0) to the appropriate value and reading or writing to SCICLK DATA IN or DATA OUT. -

Page 164: Sci Receiver Operation

NOTE: When using an externally generated SCICLK in isosynchronous mode, the maximum speed at which the SCICLK can run is limited to SYSCLK / 10. This is necessary so that the internal clocks of the SCI have time to synchronize with the external clock. For this reason, use the TMS370 to drive the master serial clock in a system where maximum throughput is a major concern. -

Page 165: Receiver Operation Flowchart

Figure 11. Receiver Operation Flowchart BEGIN SCI RECEIVER ROUTINE RXSHF – RX BUF RXRDY = 1 RXWAKE = 0 START OF FRAME? (FALLING EDGE ON SCIRXD, RXSHF – DATA LOCATION FIRST BIT = 0) RXRDY = 0 READ CHARACTER INTO RXSHF ADDRESS BIT MODE ADDRESS... -

Page 166: Sci Transmitter Operation

SCI Transmitter Operation A flowchart of the operation of the SCI transmitter is shown in Figure 12. The SCI transmitter is activated by loading the transmitter buffer, TXBUF, which clears the TXRDY flag. When TXSHF, the transmitter shift register, is empty the contents of TXBUF are latched into TXSHF and the TXRDY flag is set to indicate the transmitter is ready for a new character. -

Page 167: Transmitter Operation Flowchart

Figure 12. Transmitter Operation Flowchart TRANSMITTER ROUTINE IDLE MODE TXWAKE = 1 ADDRESS – TXBUF TXWAKE = 1 TXBUF – TXSHF DUMMY – TXBUF TXWAKE – WUT TXREADY = 1 TXEMPTY = 0 TXWAKE = 0 TXWAKE – WUT TXBUF – TXSHF DELAY >... -

Page 168: Sci Interrupts And Flags

Data transmission is initiated by moving data into TXBUF. The status of the TXWAKE flag, set prior to writing to TXBUF, determines whether or not the current character is an address or data. The contents of TXWAKE and TXBUF are transferred to WUT (wake up temporary) and TXSHF, respectively, to be shifted out as soon as the current transmission is complete. -

Page 169: Multiprocessor Communications

Multiprocessor Communications Using the SLEEP Bit Quite often several serial ports will be tied to a common line, and a method is needed to restrict the conversation between two devices to avoid a communications conflict. The SLEEP flag can be used to disable an SCI until the start of a new block, at which time an address check can be made to see if that particular receiver is being addressed. -

Page 170: Using The Txwake Bit

Using the TXWAKE Bit The TXWAKE bit is used by the transmitter to format the data going out as an address frame or a data frame. If a data character is being transmitted, the TXWAKE flag is left at 0. If an address needs to be sent, TXWAKE is set to 1 before the address byte is loaded into TXBUF. -

Page 171: Timing The Flow Of Data

Timing the Flow of Data Transmitting A few items need to be taken into consideration when using the SCI transmitter. It is important not to write data to the TXBUF register before it has shifted its data to the TXSHF register. This becomes more likely as the SCI baud rate decreases and it takes longer to shift out the data. -

Page 172: What To Do With Transmission Errors

All of the above flags are cleared by reading RXBUF, executing an SCI SW RESET, or executing a system reset. Of course, if data integrity is not an issue, you can ignore checking for errors. Disabling parity checking decreases the number of bits sent per frame so, in effect, a faster transmission rate is achieved. In most cases, however, you will want to make sure your data has been transmitted correctly and leave parity checking enabled. -

Page 173: Sci Module Software Examples

SCI Module Software Examples The following are examples of the various modes of operation and common software routines used in the implementation of the SCI. The register equates are shown below. Common Equates SCICCR .equ P050 ;SCI communication control register SCICTL .equ P051... -

Page 174: Sleep Bit – Multiprocessing Control

SLEEP Bit – Multiprocessing Control By using the SLEEP bit (SCICTL2), several microprocessors can be tied to common SCIRXD and SCITXD lines. This example shows a slave microcontroller set to listen for its own address and load its RAM with a block of data of a fixed size when it is addressed. The data is received through the use of an interrupt routine. -

Page 175: System Controller Configuration

System Controller Configuration In this example, the device is setup as a system controller that requests data from specific devices using the idle line protocol. The address of the device to be interrogated is stored in ADDROUT. The address is sent out and the controller waits for the data to be sent to it. If an error occurs, the controller asks for the data to be transmitted again. -

Page 176: Nine-Bit Data Protocol

Nine-Bit Data Protocol Data transfer can be made more efficient by transferring more bits per character. By using the address bit mode, an extra bit of data can be added to each character, creating in effect a 9-bit character protocol. Extra bits, BITNINE for the transmitter and HIGHBIT for the receiver, are used to hold the ninth bits and can be assigned to any unused register. -

Page 177: Halt Mode Wakeup Using The Sci Receiver

HALT Mode Wakeup Using the SCI Receiver In many applications, power consumption is a major concern. The TMS370 has two low power modes, HALT and STANDBY, which stop execution of various modules in the device. This greatly reduces the power used by the part. For a complete description of the powerdown/idle modes, see the TMS370 Family User’s Guide. -

Page 178: Sci Module Specific Applications

SCI Module Specific Applications RS-232-C Interface Interface TMS370C050 to RS-232-C Connection The most common of the myriad of serial interfaces is the RS-232-C. Over time it has become an industry standard for digital communications, used for everything from PCs to telecommunication. This example will show the software and hardware necessary to connect a TMS370C050 to an RS-232-C interface. -

Page 179: Tms370C050 - Rs 232 C Interface

SCI Module Specific Applications Figure 13. TMS370C050 – RS-232-C Interface V CC V – C1– V SS T1 OUT C2– T2 OUT R1 IN T1 IN R2 IN T2 IN SCIRXD SCICLK R1OUT R2 OUT SCITXD V CC V SS TMS370C050 MAX232 V CC... -

Page 180: Routine

The framework of a program for controlling communications between the TMS370C050 and a DTE (data terminal equipment) configured device is shown below. Routine .title “RS-232-C Interface” This example shows the skeleton of a program for implementing an RS-232-C interface in hardware and software. Set up EQUATE table for peripheral file registers used in the program. - Page 181 ;Idle line protocol, 8-bit characters #HI(B9600),BAUDMSB ;Set for 9600 baud (@ 4.9152 MHz) #LO(B9600),BAUDLSB #002h,SCIPC1 ;Set SCICLK as function pin. #022h,SCIPC2 ;Set SCIRXD,SCITXD as input. #060h,SCIPRI ;SCIRX interrupt low priority #033h,SCICTL ;Release SCI, set internal clock, ;Sleep=0,RXENA,TXENA #200,B ;Start stack pointer at R200. LDSP EINT ;Enable interrupts...

- Page 182 RXBUF,A ;Save received character. SCI transmitter subroutine. The subroutine waits for the other device to bring the DTR line high before transmitting. The character is then sent and the TXCTL register is polled to make sure the character has been transmitted before continuing.

-

Page 183: Terminal Interface Example

Dumb Terminal Driver Use TMS370C050 SCI to Interface to Dumb Terminal The power of the TMS370C050 microcontroller allows it to control a large number of tasks at the same time. The on-chip peripherals can operate independently of each other, releasing the CPU to do other tasks. This example shows a TMS370C050 microcontroller configured as a dumb terminal driver. -

Page 184: Routine

Routine .title “SCI Terminal Driver” Set up equate table for peripheral registers used in program. SCCR0 .equ P010 ;System configuration register ;assignments. SCCR1 .equ P011 SCCR2 .equ P012 SCICCR .equ P050 ;SCI configuration control register SCICTL .equ P051 ;SCI operation control register BAUDMSB .equ P052... - Page 185 RXLIMIT .equ ;XOFF or XON is sent RXLIMIT2 .equ .equ 011h ;Control-Q character XOFF .equ 013h ;Control-S character .text 07000h START DINT Initialize SCI. #077h,SCICCR ;1 stop bit, even parity, asynchronous, ;Idle line protocol, 8-bit characters #000h,SCICTL ;SCI SW RESET. #000h,BAUDMSB ;Set for 9600 (@ 5 MHz) #00Fh,BAUDLSB...

- Page 186 Place main block of code here. When a character is received the SCI receiver interrupt routine is called, and the character is stored in the data buffer. When the program is ready to process a character that has been received, the subroutine RXCHAR is called. When a character is ready to be transmitted, the routine TXCHAR is called, and the character is transmitted.

- Page 187 GRABCHAR PUSH RXPTR,B ;Increment pointer. BTJZ #020h,B,NOROLL1 ;Does RXPTR need to be rolled over? #0,B ;Yes, reset RXPTR to start of RXBUFFER. NOROLL1 B,RXPTR ;Save new value of RXPTR. *RXBUFFER[B],A ;Get new value from RXBUFFER. SCI Transmitter Subroutine. This routine is called whenever the program is ready to transmit a character to the terminal.

- Page 188 BTJZ #020h,TXPTRI,NOROLL3 ;If TXPTRI past end of buffer, clear ;it. TXPTRI ;Set TXPTRI to beginning of buffer. NOROLL3 TXDIFF ;If so, nothing to transmit. TXPTRI,B *TXBUFFER[B],A TXWAIT1 BTJZ #080h,TXCTL,TXWAIT1 ;Wait until previous characters have ;finished transmitting. A,TXBUF ;Transmit character. ;Increment TXPTR. BTJO #0FFh,TXDIFF,TXEXIT ;If no more characters to send, #0FEh,TXCTL...

- Page 189 NOROLL4 B,RXPTRI ;Save new value of RXPTRI. A,*RXBUFFER[B] RXDIFF ;# of stored characters + 1. ;Restore B register contents. JBIT1 LOCSTAT,RXDONE ;XOFF already sent? Don’t send another. #RXLIMIT,RXDIFF ;Receiver buffer getting full? RXDONE ;No, exit interrupt routine. RXWAIT BTJZ #080h,TXCTL,RXWAIT ;Wait until present transmission ;complete.

- Page 190 There are a few things that should be noted about any terminal controller code. The most important is to watch the timing of the transmission of X-Off and X-On characters from the receiver routines. It is important that as soon as the receiver buffer passes its limit (in this case 27 characters) that an X-Off be transmitted to make sure that the buffer does not overflow.

-

Page 191: Remote Data Acquisition Example

Low Power Remote Data Acquisition Use TMS370CO50 in STANDBY Mode with SCIRX Wake-Up Procedure The low-power modes and flexible serial interface of the TMS370 family make it ideal for applications involving remote sensing. In this application example, a TMS370C050 is acting as a climate recorder in a remote location. - Page 192 The program uses T1 to periodically read the A / D values and store them in ATABLE. T1 can also bring the device out of STANDBY mode through the T1 interrupt. In this way, the device will draw less than one-quarter its normal operating current most of the time.

- Page 193 TXCTL .equ P054 ;Transmitter int. control/status ;register RXCTL .equ P055 ;Receiver int. control/status register RXBUF .equ P057 ;Receiver data buffer register TXBUF .equ P059 ;Transmit data buffer register SCIPC1 .equ P05D ;SCI port control register 1 SCIPC2 .equ P05E ;SCI port control register 2 SCIPRI .equ P05F...

- Page 194 START DINT ;Disable interrupts while initializing. System Initialization #041h,SCCR2 ;STANDBY mode, no priv mode, no osc ;fault reset SCI Initialization #000h,SCICTL ;SCI SW RESET #077h,SCICCR ;1 stop bit, even parity, asynchronous, ;idle line protocol, 8-bit characters #000h,BAUDMSB ;Set for 9600 baud @ 5 MHz. #00Fh,BAUDLSB #001h,RXCTL ;Enable SCIRX INT.

- Page 195 MAIN ;Main loop Tl Interrupt Routine When the interrupt routine is called, the part will come out of STANDBY mode. The routine will collect information from the A/D and store it in register A. The data is then loaded into ATABLE so it can be easily transmitted out.

- Page 196 A,TXBUF DJNZ B,LOOP ;If not done, send next character. WAIT BTJZ #040h,TXCTL,WAIT ;Wait for last character to be sent. RXDONE ;Exit interrupt routine and go back into ;STANDBY mode. Set up interrupt vectors. .sect “VECTORS”,07FF2h .word RXINT ;SCIRX interrupt routine. .word TIMERINT ;T1 interrupt routine.

-

Page 197: Spi Control Registers

Appendix A: SPI Control Registers The SPI is controlled and accessed through registers in the peripheral file. These registers are listed in Table 6 and described in the TMS370 Family User’s Guide. The bits shown in shaded boxes in Table 6 are privilege mode bits;... -

Page 198: Sci Control Registers

Appendix B: SCI Control Registers The SCI is controlled and accessed through registers in the peripheral file. These registers are listed in Table 7 and described in the TMS370 Family User’s Guide. The bits shown in shaded boxes in Table 7 are privilege mode bits;... - Page 199 SCI2 Designa- ADDR Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 tion SCICCR 1050h P050 STOP EVEN/ODD PARITY ADDRESS/ — BITS PARITY ENABLE IDLE WUP CHAR2 CHAR1 CHAR0 SCICTL 1051h P051 SCI SW —...

-

Page 200: Tms0170 Block Diagram

Appendix C: TMS0170 Specifications The TMS0170 Vacuum Fluorescent (VF) Display Driver is a one-chip interface between low voltage digital logic (5.0 V) and low voltage ( < 18 V ) VF displays. Key Features 33 individually controllable VF drivers: 8 high current drivers and 25 low current drivers Blanking input allows duty cycling of outputs for brightness control. -

Page 201: Shift Register

Shift Register The 34-bit shift register consists of 34 D-type flip-flops. The bits are numbered from 33 down to 00. Each data bit is clocked in on the rising edge of the clock pin, and enters the shift register in flip-flop #33. Upon each successive clock rising edge, the bit is shifted sequentially through the shift register, from flip-flop #33 to flip-flop #00. -

Page 202: Tms0170 Dip Pin Out

V SS BLANK DATA IN V DD CLOCK LOAD ENABLE LC OUTPUT-(BIT 32) DATA OUT LC OUTPUT-(BIT 21) LC OUTPUT-(BIT 20) LC OUTPUT-(BIT 22) LC OUTPUT-(BIT 25) LC OUTPUT-(BIT 23) LC OUTPUT-(BIT 24) LC OUTPUT-(BIT 30) LC OUTPUT-(BIT 19) LC OUTPUT-(BIT 13) LC OUTPUT-(BIT 12) LC OUTPUT-(BIT 14) LC OUTPUT-(BIT 17) -

Page 203: Recommended Operating Conditions

Electrical Specifications Table 8. Recommended Operating Conditions Parameter Units V SS Supply Voltage V IH High Level Input Voltage V DD + 3.5 V SS + 0.3 V IL Low Level Input Voltage V DD - 0.3 V DD + 0.8 Operating Free-Air Temperature Table 9. -

Page 204: Glossary

Glossary address bit mode: An SCI mode of communication incorporating an extra bit into each frame to distinguish address frames from data frames. Setting the address bit to a logic 1 signifies a frame beginning a new block. asynchronous mode: A communication format in which no synchronizing clocks are used. The data being transmitted is repeated several times and a majority vote is taken of selected bits to determine the transmitted value. - Page 205 NRZ (non return to zero) format: A communication format in which the inactive state is a logic one. RS-232-C: An industry standard serial communications interface. The most commonly used serial interface for personal computers. parity: An error checking protocol based on the assumption that the number of 1s in a character of data is odd or even.

-

Page 206: References

Instruments Information Publishing Center, 1984. Schwartz, Mischa. Information, Transmission, Modulation, and Noise. McGraw-Hill Book Company, 1980. T. I. Microcontroller Applications Group. TMS370 Family User’s Guide, Texas Instruments Technical Publishing. 1996. T. I. Digital Signal Processing Applications Group. TMS320C25 User’s Guide, Texas Instruments... -

Page 208: Fast Method To Determine Parity

Fast Method to Determine Parity With the TMS370 Microcontroller Products — Semiconductor Group Texas Instruments... -

Page 210: Register Values And Functions

Fast Method to Determine Parity This routine presents a quick way to determine the parity of a byte. Exclusive ORing all the bits of the byte together derives a single bit that is the even parity of the word. With exclusive ORing, an even number of 1s combines to form a 0, leaving either an odd 1 or 0 bit. -

Page 212: Automatic Baud Rate Calculation

Automatic Baud Rate Calculation With the TMS370 Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 214: Spi Port Interfacing

SCI Port Interfacing The SCI port provides communication with a variety of peripheral devices in either asynchronous or isosynchronous mode. The format parameters of the SCI are programmable: Table 1. Format Parameters Parameter Options Mode Asynchronous, isosynchronous Bit rate (baud) 64K possible bit rates Character length 1 to 8 bits... -

Page 215: Sci Control Registers

Table 2. SCI1 Control Registers Designa- ADDR Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 tion SCICCR 1050h P050 STOP EVEN/ODD PARITY ASYNC/ ADDRESS/ BITS PARITY ENABLE ISOSYNC IDLE WUP CHAR2 CHAR1 CHAR0 SCICTL 1051h... - Page 216 BAUDLSB .EQU P053 ;Baud counter LSB TXCTL .EQU P054 ;Transmitter control RXCTL .EQU P055 ;Receiver control RXBUF .EQU P057 ;Receiver buffer TXBUF .EQU P059 ;Transmitter buffer SCIPC1 .EQU P05D ;Port control 1 (SCLK) SCIPC2 .EQU P05E ;Port control 2 (TXD,RXD) SCIPRI .EQU P05F...

-

Page 217: Possible Improvements

Figure 2. Autobaud Waveform Idle Start Data Data Bit 1 Bit 2 Waitstart Waitbit Setup Possible Improvements To increase flexibility and accuracy, you can improve the routine by using some of the following suggestions: For greater accuracy, time more than one bit and then divide by the number of bits. To do this, you must choose carefully the character to start the automatic baud routine. - Page 218 Part III Module Specific Application Design Aids Part III contains six sections: RESET Operations ....SPI and SCI Modules ....Timer and Watchdog Modules .

-

Page 220: Using The Tms370 Timer Modules

Using the TMS370 Timer Modules Microcontroller Products—Semiconductor Group Texas Instruments... -

Page 222: Introduction

Introduction The TMS370 family of 8-bit microcontrollers presently provides up to three timer modules designed to meet user demands for timer applications. This application report provides examples of software routines and hardware interface circuits designed to illustrate how the features of the timer modules may be used to solve a variety of system timer requirements. -

Page 223: Module Description

Module Description Timer 1 (T1) The T1 module is available on most TMS370 devices, and contains three major blocks as shown in Figure 1: an 8-bit prescaler/clock source block, a 16-bit general-purpose timer (T1), and a 16-bit watchdog timer (WD). Additional functions of the T1 module not illustrated in Figure 1 include the interrupts and l/O pins. -

Page 224: T1 Prescaler Clock Source

Prescaler / Clock Source The prescaler/clock source block provides eight available clock sources for the general-purpose timer (T1) and the WD. (See Figure 2.) These clock sources are: System clock Pulse accumulation Event input System clock with /4 prescale tap System clock with /16 prescale tap System clock with /64 prescale tap System clock with /256 prescale tap... -

Page 225: T1 Counter

T1 Counter The T1 block (Figure 3) contains a 16-bit counter, a 16-bit compare register, and a 16-bit capture /compare register. It provides input capture, output compare, and external event functions. T1 can be operated in either the dual compare mode or the capture /compare mode, depending on the needs of your individual application. -

Page 226: Watchdog (Wd)

Standard Watchdog (WD) The WD (Figure 4) is a separate 16-bit counter in the T1 module. The WD can be used to cause a system reset or can be software configured as a simple counter / timer, an event counter, or a pulse accumulator if the WD reset feature is not needed. -

Page 227: Keyboard Scan Using T1Ic/Cr As An External Interrupt

Compare equals 2: In the dual compare mode, the capture / compare register functions as an additional compare register, and when the value of the capture / compare register matches the value of the T1 counter, the T1C2 INT FLAG bit (T1CTL3.6) is set. This action also toggles the T1PWM pin if the T1C2 OUT ENA bit (T1CTL4.5) is enabled. -

Page 228: T1 I/O Pins

T1 I/O Pins The T1 module includes three I/O pins which can be dedicated for timer functions or as general-purpose I/O pins. The configuration for these pins is controlled through the timer port control registers T1PC1 and T1PC2. Their names and T1 functions are as follows: T1EVT: This pin may be used as an external clock input to the prescaler / clock source block. -

Page 229: T1 Operational Modes

T1 Operational Modes The T1 module may be used in either of two modes of operation: dual compare mode or capture/compare mode. See Section 7.2 of the TMS370 Family User’s Guide for additional information. Dual compare mode: To operate in the dual compare mode, the T1 MODE bit (T1CTL4.7) must be cleared. -

Page 230: Capture/Compare Mode For T1

Capture/compare mode: To operate in the capture/compare mode, the T1 mode bit (T1CTL4.7) must be set. This mode provides one compare register, and the capture/compare register is configured as a capture register. The compare register can be used to generate periodic interrupts or toggle the T1PWM pin and the capture register can be used for pulse measurement. -

Page 231: T2 Interrupts

T2n (T2A and T2B) The Timer 2 (T2n) module is a 16-bit general-purpose timer available on several TMS370 devices and is illustrated in Figure 8. TMS370 devices may contain more than 1 T2n Timer Module. T2A and T2B (T2n) refer to these timer modules. T2n allows program selection of four input clock sources: system clock, external event, pulse accumulate, or no clock. -

Page 232: T2 I/O Pins

Input capture 1 / external edge detection 1: When an active transition occurs on the T2nIC1 / CR pin, the T2nEDGE1 INT FLAG bit (T2nCTL2.7) is set. If the T2nEDGE1 DET bit (T2nCTL3.0) is enabled, then this action also loads the contents of the T2n counter into the capture/ compare register. -

Page 233: T2 Operational Modes

T2n Operational Modes The T2n module may be used in either of two modes of operation: the dual compare mode or the dual capture mode. See Section 8.2 of the TMS370 Family User’s Guide for additional information. Dual compare mode: To operate in the dual compare mode, the T2nMODE bit (T2nCTL3.7) must be cleared. -

Page 234: Dual Capture Mode For T2

Figure 10. Dual Capture Mode for T2n T2nIC.15–0 T2nCC.15 – 0 16-bit 16-bit capture/compare capture T2n PRIORITY register 1 register 2 Clock source T2nPRI.6 T2nCNTR.15–0 Level 1 Int 16-bit Level 2 Int counter T2nC1 INT FLAG Compare = T2nCTL2.5 Reset T2nCTL2.0 T2nC.15–0 T2nC1 INT ENA... -

Page 235: Timer Formulas

Timer Formulas The following formulas are used to calculate the timer overflow, WD overflow, and compare register values for the T1 and T2n modules. The formulas illustrated in this section deal with time periods. Therefore, the variable SYSCLK is used in the formulas. Timer 1: T1 and WD Counter Overflow The maximum counter duration using the internal clock is determined by the internal system clock time (SYSCLK) and the prescale tap (PS). -

Page 236: T1: Compare Register Formula

T1: Compare Register Formula The compare register value required for a specific timing application can be calculated using the following formula: SYSCLK x t Compare value where: t = desired timer compare period (seconds) SYSCLK = external clock frequency PS = 1, 4, 16, 64, or 256 depending on the prescale tap selected Table 3 provides some sample compare register values to achieve various desired timings using a 5-MHz SYSCLK. -

Page 237: Timer 2: T2 Counter Overflow

Timer 2: T2n Counter Overflow The maximum counter duration using the internal clock is determined by the internal system clock time (SYSCLK). This relationship is shown below: Maximum counter duration (seconds) = 2 SYSCLK Counter resolution = SYSCLK where: SYSCLK = internal operational frequency Table 4 gives the real-time counter overflow rates for various SYSCLK values. -

Page 238: Timer 2: Compare Register Formula

Timer 2: Compare Register Formula The compare register value required for a specific timing application can be calculated using the following formula: Compare value (SYSCLK x t) where: t = desired timer compare period (seconds) SYSCLK = internal operational frequency Table 5 provides some sample compare register values to achieve various desired timings. -

Page 239: Timer Application Software Routine Examples

Timer Application Software Routine Examples The following examples show various uses of the timer modules. Each example includes source code and timing diagram. The examples shown attempt to illustrate typical timer application requirements. The Common Register Equate table for all the software examples (T2A) is shown below. (See the Conclusion section of this report to determine how to download copies of the software examples). -

Page 240: Real-Time System Control: Periodic Interrupt Of T1

Real-Time System Control: Periodic Interrupt of T1 Interrupt the main program every 10 ms (100 times a second). Timer Interrupt Period 10 ms This application routine provides a T1 compare equal interrupt 100 times a second. This routine compares the present value of the 16-bit T1 counter to the value stored in the 16-bit T1C1 register. When these two registers are equal, an interrupt will occur and the T1 counter will be reset. - Page 241 10-ms Timer Interrupt Routine T1INIT MOV #0C3h,T1CM ;Value to give 10 ms with 5-MHz SYSCLK ; (C34F) MOV #04Fh,T1CL ;Must load MSB first then LSB. MOV #00000000b,T1PC1 ;T1EVT, T1PWM, AND T1IC/CR pins are set to MOV #00000000b,T1PC2 ; general-purpose input pins. MOV #00000000b,T1PRI ;Select interrupt priority level 1.

-

Page 242: Output Pulse Width Generation: 1-Khz Square Wave

Output Pulse Width Generation: 1-kHz Square Wave Output a 1-kHz square wave (50% duty cycle). T1PWM This application routine generates a 1-kHz square wave output signal by using the 16-bit T1 compare regis- ter to toggle the T1PWM output pin. Since the timer needs to toggle the output pin twice to produce one square wave pulse, the timer needs to toggle at a 2-kHz rate, or every 0.5 ms. - Page 243 50% Square Wave Signal Routine SQUARE MOV #009h,T1CM ;Value to give .5 ms with 5-MHz SYSCLK (9C3h) MOV #0C3h,T1CL ;Must load MSB first, then LSB. MOV #00000000b,T1PC1 ;T1EVT pin is set as a general-purpose input ; pin MOV #00100000b,T1PC2 ;Enable T1PWM pin (initial output value ;...

-

Page 244: Pulse Width Modulation #1

Pulse Width Modulation (PWM) #1 Output a 1-kHz signal with a fixed 20% duty cycle. T1PWM In this example of pulse width modulation, the pulse frequency remains 1 kHz while the duty cycle is 20%. The duty cycle is defined as the time the pulse remains high divided by the period of the pulse, so in this case, the pulse remains high for 0.2 ms per cycle. - Page 245 Routine MOV #013h,T1CM ;Value to give 1 ms with ; 5-MHz SYSCLK (1387h) MOV #087h,T1CL ;Must load MSB first then LSB. MOV #003h,T1CCM ;Value to give .2 ms with ; 5-MHz SYSCLK (3E7h) MOV #0E7h,T1CCL ;Must load MSB first then LSB. MOV #000000000b,T1PC1 ;T1EVT pin is set as a general- ;...

-

Page 246: Pulse Width Modulation #2

PWM #2 Output a 1-kHz signal with a varying duty cycle. T1PWM In this example of PWM, a fixed-frequency signal (1 kHz) is output with a varying duty cycle. The main difference between this routine and the the previous routine (PWM #1) is that the duty cycle, t , may vary. - Page 247 Routine T1INIT #013h,T1CM ;Value to give 1 ms with 5-MHz ; SYSCLK (1387h) #087h,T1CL ;Must load MSB first then LSB. HIDC,T1CCM ;Load value for the duty cycle. LODC,T1CCL ;Must load MSB first then LSB. #00000000b,T1PC1 ;T1EVT pin is set as a general- ;...

-

Page 248: Pulse Position Modulation (Ppm)

Pulse Position Modulation (PPM) Output a fixed 0.2-ms pulse at a variable frequency (1-kHz rate initially). T1PWM In this example of PPM, the high pulse width, t , remains constant while the periods, t , of the pulses vary. The program code for this example is similar to the PWM #2 example. In the PWM #2 example, the pro- gram changes the pulse width by varying the value in the capture/compare register. - Page 249 Routine T1INIT #013h,T1CM ;Value to give 1 ms with 5-MHz ; SYSCLK (1387h) #087h,T1CL ;Must load MSB first then LSB. #004h,T1CCM ;Load value for the .2-ms duty cycle #0E1h,T1CCL ;Must load MSB first then LSB. #00000000b,T1PC1 ;T1EVT pin is set as a general- ;...

-

Page 250: Pulse Width Measurement Using Pulse Accumulation Clock Source

Pulse Width Measurement Using Pulse Accumulation Clock Source Measures the positive pulse of a signal with input connected to both T1IC / CR and T1EVT pins. T1IC/CR T1EVT Time x Time y This method measures the time that a single pulse remains high. The signal line connects to both the input capture (T1IC/CR) and the event counter (T1EVT) inputs. - Page 251 Pulse Accumulation Measurement PWM Routine .REG STOREOF ;Registers used in this routine .REG STOREM .REG STOREL .REG BITS STOREOF ;Initialize the registers that will be used STOREM in this routine. STOREL BITS TIMEPULSMOV #00000010b,T1PC1 ;T1EVT and T1IC/CR pins enabled; T1PWM pin #00000010b,T1PC2 ;...

-

Page 252: Counting External Pulses Relative To An External Signal

Counting External Pulses Relative to an External Signal Determines the number of external clock pulses per measure signal with the measure signal attached to the T1IC / CR pin and the clock signal attached to the T1EVT pin. T1IC/CR Measure Signal Clock Signal T1EVT In this example, two signals are input to the processor, a measure signal and a clock signal. - Page 253 External Pulse Counting Routine .REG STOREOF ;Registers used in this routine .REG STOREM .REG STOREL .REG BITS STOREOF ;Clear registers used to store the sum of STOREM ; the T1EVT pulses. STOREL T1INIT #02h,T1PC1 ;T1EVT and T1IC/CR pins enabled, T1PWM pin #02h,T1PC2 ;...

-

Page 254: Output Pulse Drive Referenced To Input Signal: Triac Controller Or One Shot

Output Pulse Drive Referenced to Input Signal: TRIAC Controller or One Shot Output a 1-ms pulse on every positive edge of an input signal. The input signal goes to IC/CR pin. T1IC/CR T1PWM 1 ms 16-Bit Resolution Maximum In this example, a rising edge on the T1IC/CR input pin causes a 1-ms pulse to be output on the T1PWM pin. -

Page 255: Pulse Width Measurement: Time Between Edges

Pulse Width Measurement: Time Between Edges Measures the time between the rising edge on one signal and the falling edge of another signal using T2A in dual capture mode. T2AIC1/CR Time Time T2AIC2/PWM How much time is between the rising edge of one signal and the falling edge of another signal? This exam- ple uses the T2A module with its dual capture registers to accurately give the answer to this problem. - Page 256 Edge Measurement Routine EDGES #02h,T2APC1 ;Set up T2AEVT pin as general-purpose input ; pin #22h,T2APC2 ;Enable T2AIC1/CR and T2AIC2/PWM pins. #8Bh,T2ACTL3 ;Select dual capture mode, enable rising ; edge of T2AIC1/CR and falling edge of ; T2AIC2/PWM to load the capture registers. #11h,T2ACTL1 ;Reset counter, enable T2A overflow ;...

-

Page 257: Output Pulse Generation (Delayed) Referenced To Input Signal

Output Pulse Generation (Delayed) Referenced to Input Signal Output a 1-ms pulse 5 ms after the input signal goes high. Input 5 ms T1IC/CR delay Output T1PWM 1 ms This program outputs a 1-ms pulse 5 ms after the input line goes high. This example uses T1 in the dual compare mode with the output toggle function of the T1IC/PWM pin. - Page 258 Delayed Output Pulse Generation Routine ;Put 6 ms into C1 and 5 ms into C2. ;Input pulse must remain high at least 9 ;Input = T1IC/CR output = T1PWM. DELAY #18h,T1CCM ;Value to give 5 ms with 5-MHz SYSCLK ; (1869h) #69h,T1CCL ;Must load MSB first then LSB.

-

Page 259: Watchdog Operation And Initialization

Watchdog (WD) Operation and Initialization A WD timer operates as a sentry to guard against improper program flow. Any time the WD is enabled to cause a system reset and then overflows without being reset by a proper value being written to the WDRST register, a system reset will occur. - Page 260 There are conditions where the program will fail to work properly due to low V levels and the WD will not catch the failure. Your system should incorporate circuitry to cause a RESET when V is out of spec. (See Figure 11.) If a reset occurs, the RESET subroutine needs to determine if the reset was caused by the WD or not by checking the WD OVRFL INT FLAG (T1CTL2.5).

-

Page 261: Typical Power Up/Down Circuit

Figure 11. Typical Power-Up/Down Circuit To other devices’ resets TMS370 10 kΩ Reset in 2.7 kΩ Manual 0.47 µF Reset out reset... -

Page 262: Wd Reset Enable Initialization #1

WD Reset Enable Initialization #1 This example can be used for those programs that always pass periodically through two or more points (see Figure 12) in the main program routine, but not interrupt service routines. In this example, the main pro- gram resets the WD at those points by writing immediate values directly to the WD reset register. -

Page 263: One Point Main Routine Plus Interrupt Operation

WD Reset Enable Initialization #2 This example can be used for those programs that have many paths through the main routine, but also con- tain a periodic interrupt service routine (ISR), as shown in Figure 13. Since a program could get lost in a continuous loop in either the main or interrupt routine, the WD routine should not be entirely contained in either one. - Page 264 Routine WDCOUNT .EQU WDSTORE .EQU ; The following routine detects whether the reset was caused by the ; WD or not. RESET BTJZ #20h,P04A,GPINIT ;Is the WD flag set? If NOT go to GPINIT. WDINIT #0DFh,P04A ;Clear the WD flag. ;Do any initialization here you desire specific to the WD.

-

Page 265: Wd Initialization When System Reset Is Not Desired

WD Initialization When System Reset is Not Desired If a program does not use the WD reset circuit, any erroneously enabled WD can generate a reset. If the program also clears the WD overflow interrupt flag, then the WD reset can continue to occur until a power- down. -

Page 266: Specific Applications

Specific Applications This section describes sample routines for specific applications using the timer modules. Stepper Motor Control This application routine uses the T1 compare register to generate an interrupt which drives a stepper motor through the following series of activities: 1. -

Page 267: Stepper Motor Drive Application Schematic

Figure 14. Stepper Motor Drive Application Schematic +5 V V CC V CC V SS (10 –20 V) V CC RESET (10 –20 V) V CC B’ (10 –20 V) XTAL2 XTAL1 V CC A’ A’ (10 –20 V) V CC B’... -

Page 268: Stepper Motor Control Application Flowchart

The flowchart for the stepper motor application is shown in Figure 15. Figure 15. Stepper Motor Control Application Flowchart Begin Stepper Motor Begin T1 Application. Interrupt Routine. Initialize: 1. Stack Pointer Optional: Did T1EDGE Flag 2. Port A Cause Interrupt Do Interrupt Code Here. - Page 269 Stepper Motor Routine .title “Stepper Motor Control” Allocate register space for the four registers used in the routine. MSCOMP .equ ;Working registers for new values for LSCOMP .equ ; the T1 compare register. FLAG .equ ;Register tellS if acceleration or ;...

- Page 270 Initialize the T1 module. INTPGM MOV #080h,T1CM ;Value to give minimum speed (rpm) using a MOV #00h,T1CL ; 20-MHz crystal. Must load the MS byte ; first then the LS byte. MOV #00000000b,T1PC1 ;T1EVT, T1PWM, AND T1IC/CR pins are set to MOV #00000000b,T1PC2 ;...

- Page 271 T1 interrupt service routine: Routine will first check to see which of three possible flags caused the interrupt, and jump to the correct routine. If the T1C1 flag (compare register 1) is set, the STPMTR routine is entered. This routine loads the motor pole drivers with a value that causes the motor to accelerate or decelerate in either the forward or reverse direction, depending on the values of the ACCEL/DECEL and DIRECTION bits in the FLAG...

- Page 272 .word START All other interrupt vectors point to .word START the reset vector. .word START .word START .word START .end...

- Page 273 Time-of-Day Clock Application Routine This application routine uses the T1 compare register to generate an interrupt service routine every 1 / 10 second (100 ms), which will be used to update a time-of-day clock. The value required by the compare register to generate a 100-ms interrupt period with a 5-MHz SYSCLK is 07A11h .

-

Page 274: Flowchart For Time Of Day Clock Application

Figure 16. Flowchart for Time-of-Day Clock Application Main Loop T1 Interrupt Routine Begin Enter T1 Interrupt Routine. Clear and Reenable Initialize Stack the T1C1 Flag. Pointer to Begin at Increment the TENTH R10. Register. Set Up the 5 Registers Used in the Does Time = 1 s Routine. - Page 275 Time-of-Day Routine .title “Time-of-Day Clock” This routine will use T1 in the dual compare mode to implement a real-time 12-hour clock (with AM/PM flag) down to tenths of seconds. Allocate register space for the five registers used in the application routine. AMPM .equ ;AM/PM flag register...

- Page 276 Initialize the clock registers to 12:00 a.m. ;Initialize SEC register to 00. ;Initialize MIN register to 00. #12h,HOUR ;Initialize HOUR register to 12. #00,AMPM ;Initialize AMPM. 0 = AM, 1 = PM #0Ah,TENTH ;Initialize TENTH register with 10. #00,T1PRI ;Set T1 priority for level 1. #7Ah,T1CM ;Move 07A11h into the T1C1 register #11h,T1CL...

-

Page 277: Optional Calendar Functions For The Time Of Day (Tod) Clock

Optional Calendar Functions for the Time-of-Day (TOD) Clock This code could be substituted for the T1 interrupt service routine of the previous example to give a TOD clock which keeps track of days, months, and years including leap years. To implement these functions, you need to replace the register equates, the T1 interrupt service routine, and the value of the stack pointer. - Page 278 RESTOREB POP ;Restore B with time unit ; count. DONE ;Increment the present time ; unit. A,*TIME[B] ;Restore B and A then exit. ;Return from interrupt. DOMONTH PUSH ;M O N T H S MONTH,B ;Get the value of the MONTH ;...

-

Page 279: Frequency Counter Application

Frequency Counter Application This routine uses the T1 module in a frequency counter application. The frequency is calculated by keeping track of the number of pulses for one second. The pulse count is input on the T1IC/CR pin, and the T1 compare register is set up to give a one-second interrupt. - Page 280 Frequency Counter Routine .title “Frequency Counter”;accurate to approx 60 kHz Allocate space for the seven registers used in the routine. COUNTH .equ ;The COUNTX registers are used to keep COUNTM .equ ; track of the external pulses on the COUNTL .equ ;...

- Page 281 Begin your main program here. A simple jump/loop routine is used in this application. MAIN MAIN ;Loop on self while waiting for interrupt. T1 interrupt service routine: Routine first checks to see which of the two enabled T1 interrupt sources caused the interrupt. If the T1C1 flag (compare register 1) is set, the service routine jumps to SAVE and loads the contents of the COUNTX registers into the STOREX registers,...

-

Page 282: Display Dimming Application Routine

Display Dimming Application Routine Output a PWM signal with a varying duty cycle to control the brightness of a display. (VF, LED, etc.) The schematic for this application is as follows: Figure 17. Display Dimming Application Display T1PWM TMS370 Microcontroller I/O Pin ENABLE SPICLK... - Page 283 The main program loads any new values for the PWM duty cycle into the MS/LSDATA working registers. These values are checked against the latest values in the HI / LODUTY registers. If they are different, the HI / LODUTY registers are updated, and the MAIN loop compares to see if the new value is 0% or 100%. If so, the PWM pin is set either LO or HIGH.

-

Page 284: Display Dimming Flowchart

Figure 19. Display Dimming Flowchart Display Dimming T1 Interrupt Applications Service Routine Begin T1 INT, Begin Service Routine. Clear T1C Flag, Stop T1. Initialize: Load Upgrade Duty Cycle 1. Stack Pointer Information. 2. Registers 3. T1 Module Reset T1. Reset T1PWM Pin. Restart T1. - Page 285 Display Dimming Routine .title “Display Dimming Function” .text 7000h Allocate register space for the five registers used in the application routine. HIDUTY .equ ;Register used to store MSB of any new ; duty cycle value. LODUTY .equ ;Register used to store LSB of any new duty cycle value.