Analog Devices Blackfin ADSP-BF537 Manuals

Manuals and User Guides for Analog Devices Blackfin ADSP-BF537. We have 3 Analog Devices Blackfin ADSP-BF537 manuals available for free PDF download: Hardware Reference Manual, Service Manual, Specification

Analog Devices Blackfin ADSP-BF537 Hardware Reference Manual (1218 pages)

Brand: Analog Devices

|

Category: Computer Hardware

|

Size: 4 MB

Table of Contents

-

Preface

43-

-

Myanalog.com49

-

Conventions55

-

-

Introduction

59-

Peripherals59

-

DMA Support65

-

Ports68

-

Ethernet MAC72

-

Timers76

-

UART Ports77

-

Boot Modes83

-

-

-

Overview91

-

-

-

Memory

103-

L1 Data SRAM104

-

L1 Data Cache110

-

Boot ROM110

-

External Memory110

-

-

Overview113

-

Features113

-

-

Interfaces114

-

-

SIC_ISR Register133

-

SIC_IWR Register134

-

-

-

-

Peripheral DMA145

-

Memory DMA147

-

-

-

DMA Startup158

-

DMA Refresh163

-

DMA Receive168

-

-

DMA Performance182

-

-

-

DMA Registers205

-

-

HMDMA Registers236

-

-

EBIU Overview257

-

Block Diagram260

-

Shared Pins262

-

Registers262

-

-

System Clock263

-

Error Detection263

-

Operation264

-

-

AMC Registers277

-

-

Row Precharge289

-

-

Burst Type290

-

Trcd293

-

Trfc294

-

SDC Commands303

-

-

Overview341

-

-

-

-

Overview381

-

Pins385

-

Power Management387

-

Operation390

-

-

Power Management411

-

-

Configure PHY430

-

Receiving Data431

-

-

-

-

-

Overview513

-

-

CAN Mailbox Area516

-

CAN Operation521

-

-

CAN Interrupts535

-

Global Interrupt536

-

-

Event Counter538

-

-

Error Frames541

-

Error Levels543

-

-

-

Global Registers554

-

CAN_GIM Register559

-

CAN_GIF Register560

-

-

Can_Aax Register588

-

Can_Tax Register589

-

-

Error Registers597

-

CAN_EWR Register598

-

-

SPI Control624

-

Clock Signals625

-

SPI Baud Rate626

-

Interrupt Output629

-

-

SPI Registers646

-

-

Stopping654

-

-

-

Overview661

-

Bus Arbitration667

-

Fast Mode670

-

-

Slave Mode Setup712

-

-

-

Companding749

-

PAB Errors759

-

SPORT Registers765

-

Advertisement

Analog Devices Blackfin ADSP-BF537 Service Manual (628 pages)

VisualDSP++ 5.0 Device Drivers and System for Blackfin Processors

Brand: Analog Devices

|

Category: Computer Hardware

|

Size: 3 MB

Table of Contents

-

-

Preface

31 -

Introduction

39-

-

General41

-

-

Dependencies46

-

Termination48

-

-

Termination62

-

-

-

Introduction70

-

Examples83

-

-

Adi_Int_Init86

-

-

-

Getting Started105

-

Introduction106

-

-

Adi_Pwr_Control122

-

Adi_Pwr_Getfreq125

-

Adi_Pwr_Init129

-

Adi_Pwr_Reset135

-

Adi_Pwr_Setfreq137

-

-

Adi_Pwr_Command146

-

Adi_Pwr_Csel151

-

Adi_Pwr_Df152

-

Adi_Pwr_Mode153

-

Adi_Pwr_Result154

-

Adi_Pwr_Ssel156

-

Adi_Pwr_Vddext157

-

Adi_Pwr_Vlev157

-

Adi_Pwr_Vr_Canwe158

-

Adi_Pwr_Vr_Usbwe158

-

Adi_Pwr_Vr_Freq159

-

Adi_Pwr_Vr_Gain159

-

Adi_Pwr_Vr_Phywe160

-

Adi_Pwr_Vr_Wake160

-

-

PM Module Macros160

-

-

-

Introduction166

-

-

Adi_Ebiu_Control176

-

Adi_Ebiu_Init180

-

-

Adi_Ebiu_Command195

-

-

-

-

Introduction213

-

-

Adi_Dcb_Close225

-

Adi_Dcb_Control226

-

Adi_Dcb_Init229

-

Adi_Dcb_Open231

-

Adi_Dcb_Post233

-

Adi_Dcb_Remove235

-

-

Adi_Dcb_Command238

-

Adi_Dcb_Result239

-

-

Dma Manager

241-

Introduction242

-

-

-

-

Interrupts267

-

Adi_Dma_Buffer274

-

Adi_Dma_Close276

-

Adi_Dma_Control277

-

Adi_Dma_Init280

-

Adi_Dma_Open288

-

Adi_Dma_Queue290

-

-

-

Data Types294

-

Data Structures295

-

Adi_Dma_Tc_Set297

-

Adi_Dma_Event298

-

Adi_Dma_Tc_Get298

-

Adi_Dma_Mode299

-

Adi_Dma_Pmap300

-

Adi_Dma_Result300

-

Adi_Dma_Di_En301

-

Adi_Dma_Di_Sel301

-

Adi_Dma_Dma2D301

-

Adi_Dma_En302

-

Adi_Dma_Wdsize302

-

Adi_Dma_Wnr302

-

DMA Commands302

-

-

-

Introduction306

-

Operation307

-

Initialization307

-

Flag Ids308

-

Termination308

-

Adi_Flag_Close309

-

Adi_Flag_Open309

-

Adi_Flag_Set309

-

Adi_Flag_Clear310

-

Adi_Flag_Sense310

-

Adi_Flag_Toggle310

-

Callbacks310

-

Coding Example313

-

Initialization314

-

Opening a Flag315

-

Termination318

-

Adi_Flag_Clear320

-

Adi_Flag_Close321

-

Adi_Flag_Init322

-

Adi_Flag_Open324

-

Adi_Flag_Set327

-

Adi_Flag_Toggle328

-

Adi_Flag_Sense329

-

-

-

Adi_Flag_Id336

-

Adi_Flag_Result337

-

Adi_Flag_Event338

-

Adi_Flag_Trigger339

-

-

Timer Service341

-

Introduction342

-

Operation343

-

Initialization343

-

Termination343

-

Adi_Tmr_Close344

-

Adi_Tmr_Open344

-

Timer Ids344

-

Adi_Tmr_Reset345

-

Callbacks347

-

-

Coding Example349

-

Opening a Timer350

-

Adi_Tmr_Init356

-

Adi_Tmr_Open357

-

Adi_Tmr_Close359

-

Adi_Tmr_Reset360

-

Timer Ids370

-

Adi_Tmr_Result372

-

Adi_Tmr_Core_Cmd373

-

Adi_Tmr_Event373

-

Adi_Tmr_Wdog_Cmd374

-

Adi_Tmr_Gp_Cmd375

-

Introduction380

-

Adi_Ports_Init384

-

Adi_Ports_Result394

-

Data405

-

Callbacks414

-

Circular416

-

Handles429

-

Callback Events430

-

Command Ids430

-

Return Codes430

-

-

Data Structures432

-

Static Data432

-

Pddcallback439

-

Static Functions439

-

Dmacallback440

-

Setdataflow442

-

-

-

Adi_Dev_Close456

-

Adi_Dev_Control457

-

Adi_Dev_Init458

-

Adi_Dev_Open459

-

Adi_Dev_Read461

-

Adi_Dev_Write463

-

Adi_Dev_Mode465

-

Callback Events466

-

Result Codes467

-

COMMAND Ids470

-

Adi_Dev_Dma_Info477

-

Adi_Dev_Buffer480

-

Adi_Pdd_Close482

-

Adi_Pdd_Control483

-

Adi_Pdd_Open484

-

Adi_Pdd_Read486

-

Adi_Pdd_Write487

-

Examples488

-

Introduction489

-

Initialization490

-

Operation490

-

Termination491

-

Callbacks496

-

Coding Example499

-

Adi_Rtc_Init()506

-

Tm Structure516

-

Event Ids517

-

Result Codes518

-

DMA Service530

-

Device Manager531

-

File Cache537

-

Adi_Fss_Init540

-

Adi_Fss_Control544

-

Adi_Fss_Fileopen550

-

Adi_Fss_Fileread554

-

Adi_Fss_Fileseek555

-

Adi_Fss_Filetell557

-

Adi_Fss_Iseof558

-

Adi_Fss_Diropen561

-

Adi_Fss_Dirclose562

-

Adi_Fss_Dirread563

-

Adi_Fss_Dirseek564

-

Adi_Fss_Dirtell565

-

Adi_Fss_Wchar571

-

Result Codes575

-

Fopen578

-

Fclose579

-

Fwrite580

-

Fread581

-

Fprintf582

-

Fscanf583

-

Fgetc584

-

Fgets585

-

Fputc586

-

Fputs587

-

Fseek588

-

Ftell589

-

Feof590

-

Opendir592

-

Closedir593

-

Readdir594

-

Readdir_R595

-

Rewinddir596

-

Seekdir597

-

Telldir598

-

Mkdir599

-

Rmdir600

-

Rename601

-

Remove602

-

Extensibility603

-

Description604

-

Harddiskaccess604

-

Configuration605

-

Harddiskformat605

-

Configuration606

-

Description606

-

-

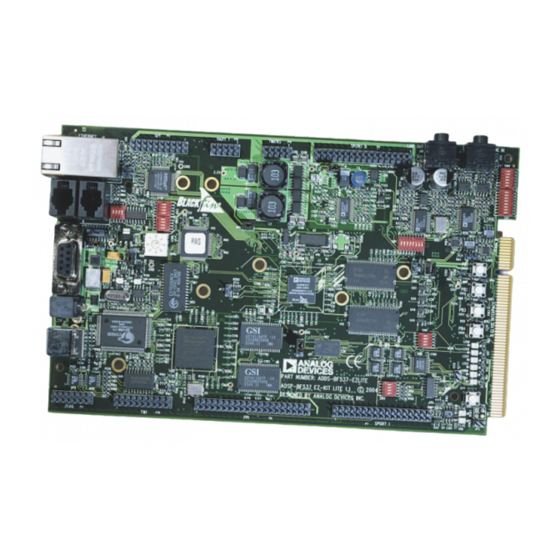

Analog Devices Blackfin ADSP-BF537 Specification (2 pages)

EZ-KIT Lite for Analog Devices Blackfin Processor

Brand: Analog Devices

|

Category: Computer Hardware

|

Size: 0 MB

Advertisement

Advertisement

Related Products

- Analog Devices Blackfin

- Analog Devices Blackfin ADSP-BF548

- Analog Devices Blackfin FPGA EZ-Extender

- Analog Devices Blackfin USB-LAN EZ-Extender

- Analog Devices Blackfin Audio EZ-Extender

- Analog Devices Blackfin/SHARC USB EZ-Extender ADZS-BFSHUSB-EZEXT

- Analog Devices Blackfin A-V EZ-Extender

- Analog Devices Blackfin Landscape LCD EZ-Extender ADZS-BFLLCD-EZEXT

- Analog Devices AD5100

- Analog Devices AD7172-4