Table of Contents

Advertisement

Quick Links

Download this manual

See also:

Service Manual

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Analog Devices Blackfin ADSP-BF537

- Page 1 ADSP-BF537 Blackfin Processor ® Hardware Reference Revision 2.0, December 2005 Part Number 82-000555-01 Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106...

- Page 2 Analog Devices, Inc. Printed in the USA. Disclaimer Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use;...

-

Page 3: Table Of Contents

CONTENTS PREFACE Purpose of This Manual ............... xliii Intended Audience ............... xliii Manual Contents ................xliv What’s New in This Manual ............xlvii Technical or Customer Support ............ xlvii Supported Processors ..............xlviii Product Information ..............xlix MyAnalog.com ................ xlix Processor Product Information .......... - Page 4 Contents Conventions ..................lv Register Diagram Conventions ..........lvi INTRODUCTION Peripherals ..................1-1 Memory Architecture ..............1-4 Internal Memory ..............1-6 External Memory ..............1-6 I/O Memory Space ..............1-7 DMA Support ................1-7 External Bus Interface Unit ............1-9 PC133 SDRAM Controller .............

- Page 5 Contents Clock Signals ................1-22 Dynamic Power Management ............1-23 Full On Mode (Maximum Performance) ........ 1-23 Active Mode (Moderate Power Savings) ........1-23 Sleep Mode (High Power Savings) .......... 1-23 Deep Sleep Mode (Maximum Power Savings) ......1-24 Hibernate State ..............1-24 Voltage Regulation ..............

- Page 6 Contents External Access Bus (EAB) ............ 2-10 Arbitration of the External Bus ..........2-11 DEB/EAB Performance ............2-11 MEMORY Memory Architecture ..............3-1 L1 Instruction SRAM ..............3-5 L1 Data SRAM ................3-7 L1 Data Cache ................3-8 Boot ROM ................... 3-8 External Memory ................

- Page 7 Contents System Interrupt Controller Registers .......... 4-16 SIC_IARx Registers ............... 4-18 SIC_IMASK Register ............4-20 SIC_ISR Register ..............4-21 SIC_IWR Register ..............4-22 Programming Examples ............... 4-23 Clearing Interrupt Requests ........... 4-23 DIRECT MEMORY ACCESS Overview and Features ..............5-1 DMA Controller Overview ............

- Page 8 Contents Variable Descriptor Size ............ 5-18 Mixing Flow Modes ............5-19 Functional Description ............... 5-20 DMA Operation Flow ............5-20 DMA Startup ..............5-20 DMA Refresh ..............5-25 Work Unit Transitions ............5-27 DMA Transmit and MDMA Source ......5-28 DMA Receive ...............

- Page 9 Contents Programming Model ..............5-55 Synchronization of Software and DMA ........5-56 Single-buffer DMA Transfers ..........5-58 Continuous Transfers Using Autobuffering ......5-58 Descriptor Structures ............5-60 Descriptor Queue Management ......... 5-61 Descriptor Queue Using Interrupts on Every Descriptor 5-62 Descriptor Queue Using Minimal Interrupts ....

- Page 10 Contents DMAx_Y_COUNT/ MDMA_yy_Y_COUNT Registers ......... 5-90 DMAx_CURR_Y_COUNT/ MDMA_yy_CURR_Y_COUNT Registers ..... 5-91 DMAx_Y_MODIFY/MDMA_yy_Y_MODIFY Registers ................ 5-93 DMAx_NEXT_DESC_PTR/ MDMA_yy_NEXT_DESC_PTR Registers ..... 5-94 DMAx_CURR_DESC_PTR/ MDMA_yy_CURR_DESC_PTR Registers ....5-96 HMDMA Registers ............... 5-98 HMDMAx_CONTROL Registers ........5-99 HMDMAx_BCINIT Registers ........5-101 HMDMAx_BCOUNT Registers ........5-101 HMDMAx_ECOUNT Registers ........

- Page 11 Contents EXTERNAL BUS INTERFACE UNIT EBIU Overview ................6-1 Block Diagram ................ 6-4 Internal Memory Interfaces ............6-5 Registers .................. 6-6 Shared Pins ................6-6 System Clock ................6-7 Error Detection ............... 6-7 Bus Request and Grant ............6-8 Operation ................6-8 AMC Overview and Features ............

- Page 12 Contents AMC Programming Model ............6-18 AMC Registers ................6-21 EBIU_AMGCTL Register ............. 6-21 EBIU_AMBCTL0 and EBIU_AMBCTL1 Registers ....6-21 AMC Programming Examples ............. 6-24 SDC Overview and Features ............6-25 Features ................6-25 SDRAM Configurations Supported ........6-26 SDRAM External Bank Size ..........6-27 SDC Address Mapping ............

- Page 13 Contents Burst Length ..............6-33 Burst Type ................ 6-34 CAS Latency ..............6-34 Data I/O Mask Function ........... 6-34 SDRAM Commands ............6-34 Mode Register Set (MRS) command ........6-34 Extended Mode Register Set (EMRS) command ....6-34 Bank Activate command ............ 6-35 Read/Write command ............

- Page 14 Contents tXSR ................6-38 tREF ................6-39 tREFI ................6-39 SDC Functional Description ............6-39 SDC Operation ..............6-39 SDC Address Muxing ............6-42 Multibank Operation ............6-43 Core and DMA Arbitration ..........6-44 Changing System Clock During Runtime ......6-44 Changing Power Management During Runtime ....

- Page 15 Contents Self-Refresh Mode ............. 6-53 Self-Refresh Entry Command ........6-53 Self-Refresh Exit Command ........6-54 No Operation Command ..........6-54 SDC SA10 Pin ..............6-55 SDC Programming Model ............6-55 SDC Configuration ............... 6-56 Example SDRAM System Block Diagrams ......6-58 SDC Register Definitions ............

- Page 16 Contents Entire Field ..............7-10 Active Video Only ............7-11 Vertical Blanking Interval (VBI) only ......7-11 ITU-R 656 Output Mode ..........7-12 Frame Synchronization in ITU-R 656 Modes ....7-12 General-Purpose PPI Modes ..........7-13 Data Input (RX) Modes ............ 7-15 No Frame Syncs ............

- Page 17 Contents Programming Examples ............... 7-36 Data Transfer Scenarios ............7-39 ETHERNET MAC Overview ..................8-1 Features ................... 8-1 Interface Overview ................ 8-2 External Interface ..............8-4 Clocking ................8-4 Pins ..................8-5 Internal Interface ..............8-6 Power Management ............. 8-7 Description of Operation ..............

- Page 18 Contents RX IP Frame Checksum Calculation ......8-21 RX DMA Direction Errors ..........8-22 Transmit DMA Operation ..........8-24 Flexible Descriptor Structure ......... 8-27 TX DMA Data Alignment ..........8-27 Late Collisions .............. 8-28 TX Frame Status Classification ........8-29 TX DMA Direction Errors ..........

- Page 19 Contents Configure MAC Registers ............8-48 MAC Address ..............8-48 MII Station Management ..........8-48 Configure PHY ..............8-50 Receive and Transmit Data ............ 8-50 Receiving Data ..............8-51 Transmitting Data ............. 8-51 Ethernet MAC Register Definitions ..........8-51 Control-Status Register Group ..........8-63 EMAC_OPMODE Register ..........

- Page 20 Contents System Interface Register Group ..........8-93 EMAC_SYSCTL Register ..........8-93 EMAC_SYSTAT Register ..........8-95 Ethernet MAC Frame Status Registers ........8-97 EMAC_RX_STAT Register ..........8-97 EMAC_RX_STKY Register ..........8-103 EMAC_RX_IRQE Register ..........8-107 EMAC_TX_STAT Register ..........8-108 EMAC_TX_STKY Register ..........8-112 EMAC_TX_IRQE Register ..........

- Page 21 Contents CAN Mailbox Control ............. 9-6 CAN Protocol Basics ............... 9-7 CAN Operation ................9-9 Bit Timing ................9-9 Transmit Operation ............... 9-12 Retransmission ..............9-13 Single Shot Transmission ........... 9-15 Auto-Transmission ............9-15 Receive Operation ..............9-15 Data Acceptance Filter ............9-18 Remote Frame Handling ...........

- Page 22 Contents Debug and Test Modes ............9-33 Low Power Features ............... 9-37 CAN Built-In Suspend Mode ..........9-37 CAN Built-In Sleep Mode ..........9-38 CAN Wakeup From Hibernate State ......... 9-38 Register Definitions ..............9-39 Global Registers ..............9-42 CAN_CONTROL Register ..........9-43 CAN_STATUS Register ...........

- Page 23 Contents Mailbox Control Registers ............. 9-68 CAN_MCx Registers ............9-69 CAN_MDx Registers ............9-70 CAN_RMPx Register ............9-71 CAN_RMLx Register ............9-72 CAN_OPSSx Register ............9-73 CAN_TRSx Registers ............9-74 CAN_TRRx Registers ............9-75 CAN_AAx Register ............9-76 CAN_TAx Register ............9-77 CAN_MBTD Register ............

- Page 24 Contents Programming Examples .............. 9-87 CAN Setup Code ..............9-87 Initializing and Enabling CAN Mailboxes ......9-89 Initiating CAN Transfers and Processing Interrupts ....9-90 SPI COMPATIBLE PORT CONTROLLERS Overview ..................10-1 Features ..................10-1 Interface Overview ..............10-3 External Interface ..............10-4 Serial Peripheral Interface Clock Signal (SCK) ....

- Page 25 Contents SPI General Operation ............10-17 SPI Control ................. 10-18 Clock Signals ..............10-19 SPI Baud Rate ..............10-20 Error Signals and Flags ............10-20 Mode Fault Error (MODF) ..........10-21 Transmission Error (TXE) ..........10-22 Reception Error (RBSY) ..........10-22 Transmit Collision Error (TXCOL) .........

- Page 26 Contents Post Transfer and Next Transfer ........10-47 Stopping ................ 10-48 DMA Transfer ..............10-48 DMA Initialization Sequence .......... 10-49 SPI Initialization Sequence ..........10-50 Starting a Transfer ............10-51 Stopping a Transfer ............10-51 TWO WIRE INTERFACE CONTROLLER Overview ..................11-1 Interface Overview ..............

- Page 27 Contents Clock Signal ................ 11-11 Error Signals and Flags ............11-12 TWI Master Status ............11-12 TWI Slave Status ............11-15 TWI FIFO Status ............11-16 TWI Interrupt Status ............11-17 Functional Description ............. 11-20 General Setup ..............11-20 Slave Mode ................11-20 Master Mode Clock Setup ...........

- Page 28 Contents TWI_FIFO_CTL Register ..........11-38 TWI_FIFO_STAT Register ..........11-40 TWI_INT_MASK Register ..........11-40 TWI_INT_STAT Register ..........11-43 TWI_XMT_DATA8 Register ..........11-43 TWI_XMT_DATA16 Register ..........11-44 TWI_RCV_DATA8 Register ..........11-45 TWI_RCV_DATA16 Register ..........11-46 Programming Examples ............11-47 Master Mode Setup ............. 11-47 Slave Mode Setup ..............

- Page 29 Contents Frame Syncs in Multichannel Mode ......... 12-19 The Multichannel Frame ..........12-20 Multichannel Frame Delay ..........12-21 Window Size ..............12-21 Window Offset ............... 12-22 Other Multichannel Fields in SPORTx_MCMC2 .... 12-22 Channel Selection Register ..........12-23 Multichannel DMA Data Packing ........12-24 Support for H.100 Standard Protocol ........

- Page 30 Contents Data Independent Transmit Frame Sync ......12-37 Moving Data Between SPORTs and Memory ....... 12-38 SPORT RX, TX, and Error Interrupts ......... 12-38 PAB Errors ................12-39 Timing Examples ..............12-39 SPORT Registers ..............12-45 Register Writes and Effective Latency ........12-47 SPORTx_TCR1 and SPORTx_TCR2 Registers ....

- Page 31 Contents UART PORT CONTROLLERS Overview ..................13-1 Features ..................13-1 Interface Overview ..............13-2 External Interface ..............13-2 Internal Interface ..............13-3 Description of Operation ............13-4 UART Transfer Protocol ............13-4 UART Transmit Operation ............ 13-5 UART Receive Operation ............13-6 IrDA Transmit Operation ............

- Page 32 Contents UARTx_RBR Registers ............13-26 UARTx_IER Registers ............13-27 UARTx_IIR Registers ............13-29 UARTx_DLL and UARTx_DLH Registers ......13-30 UARTx_SCR Registers ............13-31 UARTx_GCTL Registers ............ 13-31 Programming Examples ............13-32 GENERAL-PURPOSE PORTS Overview ..................14-1 Features ..................14-2 Interface Overview ..............14-3 External Interface ..............

- Page 33 Contents Programming Examples ............. 14-34 GENERAL-PURPOSE TIMERS Overview and Features ..............15-1 Features ................. 15-1 Interface Overview ..............15-2 External Interface ..............15-4 Internal Interface ..............15-6 Description of Operation ............15-6 Interrupt Processing .............. 15-8 Illegal States ................ 15-10 Modes of Operation ..............

- Page 34 Contents Timer Registers ................ 15-37 TIMER_ENABLE Register ..........15-38 TIMER_DISABLE Register ..........15-39 TIMER_STATUS Register ..........15-40 TIMERx_CONFIG Registers ..........15-43 TIMERx_COUNTER Registers .......... 15-45 TIMERx_PERIOD and TIMERx_WIDTH Registers ..15-46 Summary ................15-50 Programming Examples ............15-52 CORE TIMER Overview and Features ..............

- Page 35 Contents WATCHDOG TIMER Overview and Features ..............17-1 Interface Overview ..............17-2 External Interface ..............17-3 Internal Interface ..............17-3 Description of Operation ............17-3 Register Definitions ..............17-5 WDOG_CNT Register ............17-5 WDOG_STAT Register ............17-6 WDOG_CTL Register ............17-7 Programming Examples ...............

- Page 36 Contents Setting Time of Day ............18-12 Using the Stopwatch ............18-13 Interrupts ................18-14 State Transitions Summary ..........18-16 Register Definitions ..............18-19 RTC_STAT Register ............18-20 RTC_ICTL Register ............18-20 RTC_ISTAT Register ............18-21 RTC_SWCNT Register ............18-21 RTC_ALARM Register ............

- Page 37 Contents Servicing Reset Interrupts ............19-9 Booting Process ................. 19-11 Header Information ............. 19-13 Host Wait Feedback Strobe (HWAIT) ......19-19 Final Initialization ............19-21 Initialization Code ............... 19-22 Multi-Application (Multi-DXE) Management ...... 19-26 User-callable Boot ROM Functions ......... 19-27 Booting a Different Application ........

- Page 38 Contents DYNAMIC POWER MANAGEMENT Phase Locked Loop and Clock Control ........20-1 PLL Overview ............... 20-2 PLL Clock Multiplier Ratios ..........20-3 Core Clock/System Clock Ratio Control ......20-5 Dynamic Power Management Controller ........20-7 Operating Modes ..............20-8 Dynamic Power Management Controller States ...... 20-8 Full On Mode ..............

- Page 39 Contents PLL_STAT Register ............. 20-26 PLL_LOCKCNT Register ........... 20-27 VR_CTL Register ..............20-27 Programming Examples ............. 20-28 Active Mode to Full On Mode ..........20-29 Full On Mode to Active Mode ..........20-30 In the Full On Mode, Change CLKIN to VCO Multiplier From 31x to 2x ..........

- Page 40 Contents 5 Volt Tolerance ..............21-11 Resetting the Processor ............21-12 Recommendations for Unused Pins ........21-12 Programmable Outputs ............21-12 Test Point Access ..............21-12 Oscilloscope Probes ............. 21-13 Recommended Reading ............21-13 SYSTEM MMR ASSIGNMENTS Dynamic Power Management Registers ......... A-2 System Reset and Interrupt Control Registers ........

- Page 41 Contents Handshake MDMA Control Registers ........A-34 Core Timer Registers ..............A-36 Processor-Specific Memory Registers .......... A-36 TEST FEATURES JTAG Standard ................B-1 Boundary-Scan Architecture ............B-2 Instruction Register ..............B-4 Public Instructions ..............B-5 EXTEST – Binary Code 00000 .......... B-5 SAMPLE/PRELOAD –...

- Page 42 Contents xlii ADSP-BF537 Blackfin Processor Hardware Reference...

-

Page 43: Purpose Of This Manual

Intended Audience The primary audience for this manual is a programmer who is familiar with Analog Devices processors. This manual assumes that the audience has a working knowledge of the appropriate processor architecture and instruction set. Programmers who are unfamiliar with Analog Devices... -

Page 44: Manual Contents

Manual Contents Manual Contents This manual consists of: • Chapter 1, “Introduction” Provides a high level overview of the processor, including peripher- als, power management, and development tools. • Chapter 2, “Chip Bus Hierarchy” Describes on-chip buses, including how data moves through the system. - Page 45 Preface • Chapter 8, “Ethernet MAC” Describes the Ethernet Media Access Controller (MAC) peripheral that is available on ADSP-BF536 and ADSP-BF537 processors. The Ethernet MAC provides a 10/100Mbit/s Ethernet interface, compliant to IEEE Std. 802.3-2002, between an MII (Media Inde- pendent Interface) and the Blackfin peripheral subsystem.

- Page 46 Manual Contents • Chapter 15, “General-Purpose Timers” Describes the eight general-purpose timers. • Chapter 16, “Core Timer” Describes the core timer. • Chapter 17, “Watchdog Timer” Describes the watchdog timer. • Chapter 18, “Real-Time Clock” Describes a set of digital watch features of the processor, including time of day, alarm, and stopwatch countdown.

-

Page 47: What's New In This Manual

Prelimi- nary version of this manual have been made. Technical or Customer Support You can reach Analog Devices, Inc. Customer Support in the following ways: • Visit the Embedded Processing and DSP products Web site at http://www.analog.com/processors/technicalSupport... -

Page 48: Supported Processors

One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 Supported Processors The following is the list of Analog Devices, Inc. processors supported in VisualDSP++®. Blackfin (ADSP-BFxxx) Processors The name Blackfin refers to a family of 16-bit, embedded processors. VisualDSP++ currently supports the following Blackfin families: ADSP-BF53x and ADSP-BF56x. -

Page 49: Product Information

MyAnalog.com is a free feature of the Analog Devices Web site that allows MyAnalog.com customization of a Web page to display only the latest information on products you are interested in. -

Page 50: Related Documents

Product Information You may also obtain additional information about Analog Devices and its products in any of the following ways. • E-mail questions or requests for information to processor.support@analog.com (World wide support) processor.europe@analog.com (Europe support) processor.china@analog.com (China support) • Fax questions or requests for information to... -

Page 51: Online Technical Documentation

Preface • VisualDSP++ Assembler and Preprocessor Manual for Blackfin Processors • VisualDSP++ Linker and Utilities Manual for Blackfin Processors • VisualDSP++ Kernel (VDK) User's Guide Visit the Technical Library Web site to access all processor and tools manuals and data sheets: http://www.analog.com/processors/technical_library Online Technical Documentation Online documentation comprises the VisualDSP++ Help system, software... -

Page 52: Accessing Documentation From Visualdsp

Product Information If documentation is not installed on your system as part of the software installation, you can add it from the VisualDSP++ CD-ROM at any time by running the Tools installation. Access the online documentation from the VisualDSP++ environment, Windows® Explorer, or the Analog Devices Web site. -

Page 53: Accessing Documentation From The Web

To purchase VisualDSP++ manuals, call 1-603-883-2430. The manuals may be purchased only as a kit. If you do not have an account with Analog Devices, you are referred to Analog Devices distributors. For information on our distributors, log onto http://www.analog.com/salesdir... -

Page 54: Hardware Tools Manuals

1-800-ANALOGD (1-800-262-5643); they also can be downloaded from the Web site. To have a data sheet faxed to you, call the Analog Devices Faxback System at 1-800-446-6212. Follow the prompts and a list of data sheet code numbers will be faxed to you. If the data sheet you want is not listed, check for it on the Web site. -

Page 55: Conventions

Preface Conventions Text conventions used in this manual are identified and described as follows. Example Description SWRST Software Reset Register names appear in UPPERCASE and a special typeface. The register descriptive names of registers are in mixed case and regular typeface. TMR0E, RESET Pin names appear in UPPERCASE and a special typeface. -

Page 56: Register Diagram Conventions

Conventions Register Diagram Conventions Register diagrams use the following conventions: • The descriptive name of the register appears at the top, followed by the short form of the name in parentheses (see Table P-1). • If the register is read-only (RO), write-1-to-set (W1S), or write-1-to-clear (W1C), this information appears under the name. - Page 57 Preface • Bits marked x have an unknown reset value. Consequently, the reset value of registers that contain such bits is undefined or depen- dent on pin values at reset. • Shaded bits are reserved. To ensure upward compatibility with future implementations, write back the value that is read for reserved bits in a register, unless otherwise specified.

- Page 58 Conventions Timer Configuration Registers (TIMERx_CONFIG) 15 14 13 12 11 10 Timer0: 0xFFC0 0600 Reset = 0x0000 Timer1: 0xFFC0 0610 TMODE[1:0] (Timer Mode) Timer2: 00 - Reset state - unused 0xFFC0 0620 01 - PWM_OUT mode 10 - WDTH_CAP mode 11 - EXT_CLK mode ERR_TYP[1:0] (Error PULSE_HI...

-

Page 59: Introduction

1 INTRODUCTION The ADSP-BF534, ADSP-BF536, and ADSP-BF537 processors are new members of the Blackfin processor family that offer significant high per- formance and low power while retaining their ease-of-use benefits. The ADSP-BF536 and ADSP-BF537 processors are completely pin compati- ble, differing only in their performance and on-chip memory, mitigating many risks associated with new product development but allowing the possibility to scale up or down based on specific application demands. - Page 60 Peripherals • Two memory-to-memory DMAs with handshake DMA • Event handler with 32 interrupt inputs • Serial Peripheral Interface (SPI)-compatible • Two UARTs with IrDA® support • Two-Wire Interface (TWI) controller • Eight 32-bit timer/counters with PWM support • Real-Time Clock (RTC) and watchdog timer •...

- Page 61 Introduction EVENT JTAG TEST AND WATCHDOG TIMER CONTROLLER/ EMULATION CORE TIMER GPIO PORT VOLTAGE REGULATOR PORT INSTRUCTION DATA SPORT0 MEMORY MEMORY SPORT1 GPIO CORE / SYSTEM BUS INTERFACE PORT UART 0-1 GPIO CONTROLLER PORT TIMERS 0-7 EXTERNAL PORT BOOT ROM FLASH, SDRAM CONTROL Figure 1-1.

-

Page 62: Memory Architecture

Memory Architecture EVENT JTAG TEST AND WATCHDOG TIMER CONTROLLER/ EMULATION CORE TIMER GPIO PORT ETHERNET MAC VOLTAGE REGULATOR PORT INSTRUCTION DATA SPORT0 MEMORY MEMORY SPORT1 GPIO CORE / SYSTEM BUS INTERFACE PORT UART 0-1 GPIO CONTROLLER PORT TIMERS 0-7 EXTERNAL PORT BOOT ROM FLASH, SDRAM CONTROL... - Page 63 Introduction Table 1-1. Memory Configurations Type of Memory ADSP-BF534 ADSP-BF536 ADSP-BF537 Instruction SRAM/cache, lockable 16K byte 16K byte 16K byte by way or line Instruction SRAM 48K byte 48K byte 48K byte Data SRAM/cache 32K byte 16K byte 32K byte Data SRAM 32K byte 16K byte...

-

Page 64: Internal Memory

Memory Architecture Internal Memory The processor has three blocks of on-chip memory that provide high bandwidth access to the core: • L1 instruction memory, consisting of SRAM and a 4-way set-asso- ciative cache. This memory is accessed at full processor speed. •... -

Page 65: I/O Memory Space

Introduction I/O Memory Space Blackfin processors do not define a separate I/O space. All resources are mapped through the flat 32-bit address space. Control registers for on-chip I/O devices are mapped into memory-mapped registers (MMRs) at addresses near the top of the 4G byte address space. These are separated into two smaller blocks: one contains the control MMRs for all core func- tions and the other contains the registers needed for setup and control of the on-chip peripherals outside of the core. - Page 66 DMA Support than the row step size, allowing implementation of interleaved data- streams. This feature is especially useful in video applications where data can be de-interleaved on the fly. Examples of DMA types supported include: • A single, linear buffer that stops upon completion •...

-

Page 67: External Bus Interface Unit

Introduction External Bus Interface Unit The External Bus Interface Unit (EBIU) on the processor interfaces with a wide variety of industry-standard memory devices. The controller consists of an SDRAM controller and an asynchronous memory controller. PC133 SDRAM Controller The SDRAM controller provides an interface to a single bank of indus- try-standard SDRAM devices or DIMMs. -

Page 68: Ports

Ports Ports Because of the rich set of peripherals, the ADSP-BF534, ADSP-BF536, and ADSP-BF537 processor groups the many peripheral signals to four ports—port F, port G, port H, and port J. Most of the associated pins are shared by multiple signals. The ports function as multiplexer controls. Eight of the pins (port F7–0) offer high source/high sink current capabilities. -

Page 69: Two-Wire Interface

Introduction order to toggle pin values, and one register is written in order to specify a pin value. Reading the GPIO status register allows soft- ware to interrogate the sense of the pins. • GPIO interrupt mask registers – The two GPIO interrupt mask registers allow each individual GPIO pin to function as an inter- rupt to the processor. -

Page 70: Controller Area Network

Controller Area Network The TWI externally moves 8-bit data while maintaining compliance with the I C bus protocol. The Philips I C Bus Specification version 2.1 covers many variants of I C. The TWI controller includes these features: • Simultaneous master and slave operation on multiple device systems •... - Page 71 Introduction The interface to the CAN bus is a simple two-wire line. See Figure 9-1 on page 9-2 for a symbolic representation of the CAN transceiver intercon- nection. The Blackfin processor’s output and input pins are CANTX CANRX connected to an external CAN transceiver’s pins, respectively.

-

Page 72: Ethernet Mac

Ethernet MAC Ethernet MAC The Ethernet Media Access Controller (MAC) peripheral for the ADSP-BF536 and ADSP-BF537 processors provides a 10/100 Mbit/sec- ond Ethernet interface, compliant with IEEE Std. 802.3-2002, between a Media Independent Interface (MII) and the Blackfin peripheral sub- system. - Page 73 Introduction Three distinct ITU-R 656 modes are supported: • Active video only - The PPI does not read in any data between the End of Active Video (EAV) and Start of Active Video (SAV) pre- amble symbols, or any data present during the vertical blanking intervals.

-

Page 74: Sport Controllers

SPORT Controllers These modes support ADC/DAC connections, as well as video communi- cation with hardware signalling. Many of the modes support more than one level of frame synchronization. If desired, a programmable delay can be inserted between assertion of a frame sync and reception/transmission of data. - Page 75 Introduction • Framing Each transmit and receive port can run with or without frame sync signals for each data word. Frame sync signals can be generated internally or externally, active high or low, and with either of two pulse widths and early or late frame sync. •...

-

Page 76: Serial Peripheral Interface (Spi) Port

Serial Peripheral Interface (SPI) Port Serial Peripheral Interface (SPI) Port The processor has an SPI-compatible port that enables the processor to communicate with multiple SPI-compatible devices. The SPI interface uses three pins for transferring data: two data pins and a clock pin. -

Page 77: Uart Ports

Introduction The timer units can be used in conjunction with the UARTs to measure the width of the pulses in the datastream to provide an autobaud detect function for a serial channel. The timers can generate interrupts to the processor core to provide peri- odic events for synchronization, either to the processor clock or to a count of external signals. -

Page 78: Real-Time Clock

Real-Time Clock dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower priority than most DMA chan- nels because of their relatively low service rates. The UARTs’ baud rate, serial data format, error code generation and sta- tus, and interrupts can be programmed to support: •... -

Page 79: Watchdog Timer

Introduction The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60 second counter, a 60 minute counter, a 24 hours counter, and a 32768 day counter. -

Page 80: Clock Signals

Clock Signals If configured to generate a hardware reset, the watchdog timer resets both the CPU and the peripherals. After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in the watchdog control register. -

Page 81: Dynamic Power Management

Introduction Dynamic Power Management The processor provides four operating modes, each with a different perfor- mance/power profile. In addition, dynamic power management provides the control functions to dynamically alter the processor core supply volt- age to further reduce power dissipation. Control of clocking to each of the peripherals also reduces power consumption. -

Page 82: Deep Sleep Mode (Maximum Power Savings)

Voltage Regulation interrupt causes the processor to sense the value of the bypass bit ( BYPASS in the PLL control register ( ). If bypass is disabled, the processor PLL_CTL transitions to the full on mode. If bypass is enabled, the processor transi- tions to the active mode. -

Page 83: Boot Modes

Introduction control register ( ) in increments of 50 mV. To reduce standby VR_CTL power consumption, the internal voltage regulator can be programmed to remove power to the processor core while keeping I/O power supplied. While in this state, V can still be applied, eliminating the need for DDEXT external buffers. - Page 84 Boot Modes R/W access times; 4-cycle setup). The boot ROM evaluates the first byte of the boot stream at address 0x2000 0000. If it is 0x40, 8-bit boot is performed. A 0x60 byte is required for 16-bit boot. • Boot from serial SPI memory (EEPROM or flash). Eight-, 16-, or 24-bit addressable devices are supported as well as AT45DB041, AT45DB081, and AT45DB161 data flash devices from Atmel.

-

Page 85: Instruction Set Description

Introduction • Boot from serial TWI memory (EEPROM/flash) – The Blackfin processor operates in master mode and selects the TWI slave with the unique id 0xA0. It submits successive read commands to the memory device starting at two byte internal address 0x0000 and begins clocking data into the processor. - Page 86 Instruction Set Description small final memory size. The instruction set also provides fully featured multifunction instructions that allow the programmer to use many of the processor core resources in a single instruction. Coupled with many fea- tures more often seen on microcontrollers, this instruction set is very efficient when compiling C and C++ source code.

-

Page 87: Development Tools

Analog Devices emulators and the VisualDSP++ development environment. The same emulator hard- ware that supports other Analog Devices products also fully emulates the ADSP-BF53x processor family. The VisualDSP++ project management environment lets programmers develop and debug an application. This environment includes an... - Page 88 VDK-based objects, and visualizing the system state during application debug. Analog Devices emulators use the IEEE 1149.1 JTAG test access port of the processor to monitor and control the target board processor during emulation. The emulator provides full speed emulation, allowing inspec- tion and modification of memory, registers, and processor stacks.

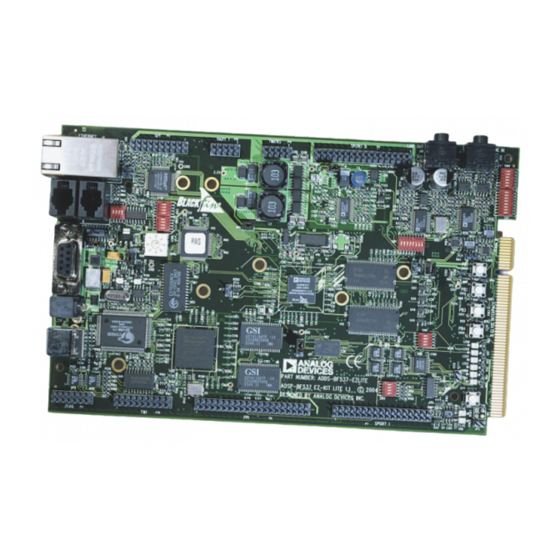

- Page 89 JTAG interface—the emulator does not affect target system loading or timing. In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools support- ing the Blackfin processor family. Hardware tools include the ADSP-BF537 EZ-KIT Lite standalone evaluation/development cards.

- Page 90 Development Tools 1-32 ADSP-BF537 Blackfin Processor Hardware Reference...

-

Page 91: Chip Bus Hierarchy

2 CHIP BUS HIERARCHY This chapter discusses on-chip buses, how data moves through the system, and other factors that determine the system organization. Following an overview and a list of key features is a block diagram of the chip bus hier- archy and a description of its operation. - Page 92 Overview The following sections describe the on-chip interfaces between the system and the peripherals via the: • Peripheral Access Bus (PAB) • DMA Access Bus (DAB) • DMA Core Bus (DCB) • DMA External Bus (DEB) • External Access Bus (EAB) The External Bus Interface Unit (EBIU) is the primary chip pin bus and is discussed in Chapter 6, “External Bus Interface...

-

Page 93: Interface Overview

Chip Bus Hierarchy Interface Overview Figure 2-1 shows the core processor and system boundaries as well as the interfaces between them. CORE L1 MEMORY INSTRUCTION PROCESSOR LOAD DATA CORE CLOCK LOAD DATA (CCLK) DOMAIN STORE DATA SYSTEM CLOCK (SCLK) DOMAIN CORE BUS (DCB) EXTERNAL... -

Page 94: Internal Clocks

Interface Overview Internal Clocks The core processor clock ( ) rate is highly programmable with respect CCLK . The rate is divided down from the Phase Locked Loop CLKIN CCLK (PLL) output rate. This divider ratio is set using the parameter of the CSEL PLL divide register. - Page 95 Chip Bus Hierarchy Figure 2-2 shows the core processor and its interfaces to the peripherals and external memory resources. SYSTEM CLOCK DSP ID JTAG AND POWER (8 BITS) MANAGEMENT DEBUG AND JTAG INTERFACE CORE EVENT CONTROLLER POWER AND RESET CLOCK VECTOR CONTROLLER PROCESSOR...

-

Page 96: Peripheral Access Bus (Pab)

Interface Overview When the instruction request is filled, the 64-bit read can contain a single 64-bit instruction or any combination of 16-, 32-, or 64-bit (partial) instructions. When cache is enabled, four 64-bit read requests are issued to support 32-byte line fill burst operations. These requests are pipelined so that each transfer after the first is filled in a single, consecutive cycle. -

Page 97: Pab Performance

Chip Bus Hierarchy • Watchdog timer • Real-time clock (RTC) • Timer 0–7 • SPORT0–1 • SPI • Ports • UART0–1 • PPI • TWI • CAN • Ethernet MAC • Asynchronous memory controller (AMC) • SDRAM controller (SDC) • DMA controller PAB Performance For the PAB, the primary performance criteria is latency, not throughput. -

Page 98: Dma Access Bus (Dab), Dma Core Bus (Dcb), Dma External Bus (Deb)

Interface Overview DMA Access Bus (DAB), DMA Core Bus (DCB), DMA External Bus (DEB) The DAB, DCB, and DEB buses provide a means for DMA-capable peripherals to gain access to on-chip and off-chip memory with little or no degradation in core bandwidth to memory. DAB Arbitration Sixteen DMA channels and bus masters support the DMA-capable periph- erals in the processor system. -

Page 99: Dab Bus Agents (Masters)

Chip Bus Hierarchy Table 2-1. DAB, DCB, and DEB Arbitration Priority DAB, DCB, DEB Master Default Arbitration Priority PPI receive/transmit 0 - highest Ethernet receive Ethernet transmit SPORT0 receive SPORT0 transmit SPORT1 receive SPORT1 transmit SPI receive/transmit UART0 receive UART0 transmit UART1 receive UART1 transmit MDMA stream 0 destination... -

Page 100: Dab, Dcb, And Deb Performance

Interface Overview DAB, DCB, and DEB Performance The processor DAB supports data transfers of 16 bits or 32 bits. The data bus has a 16-bit width with a maximum frequency as specified in the pro- cessor data sheet. The DAB has a dedicated port into L1 memory. No stalls occur as long as the core access and the DMA access are not to the same memory bank (4K byte size for L1). -

Page 101: Arbitration Of The External Bus

Chip Bus Hierarchy Arbitration of the External Bus Arbitration for use of external port bus interface resources is required because of possible contention between the potential masters of this bus. A fixed-priority arbitration scheme is used. That is, core accesses via the EAB will be of higher priority than those from the DMA external bus (DEB). - Page 102 Interface Overview the form where P0 points to an address in SDRAM). In R0 = W[P0++]; this example, a 32-bit SDRAM read takes 10 cycles while two 16-bit SCLK reads take 9 cycles each. SCLK Table 2-2. Performance of DMA Access to External Memory Source Destination Approximate SCLKs For n Words...

-

Page 103: Memory

3 MEMORY This chapter discusses memory population specific to the ADSP-BF534, ADSP-BF536, and ADSP-BF537 processors. Functional memory archi- tecture is described in the ADSP-BF53x/BF56x Blackfin Processor Programming Reference. Memory Architecture Figure 3-1 on page 3-3 provides an overview of the ADSP-BF534 proces- sor system memory map. -

Page 104: L1 Data Sram

Memory Architecture Table 3-1. Memory Configurations Type of Memory ADSP-BF534 ADSP-BF536 ADSP-BF537 Instruction SRAM/Cache, lockable 16K byte 16K byte 16K byte by Way or line Instruction SRAM 48K byte 48K byte 48K byte Data SRAM/Cache 32K byte 16K byte 32K byte Data SRAM 32K byte 16K byte... - Page 105 Memory ADSP-BF534 MEMORY MAP 0xFFFF FFFF CORE MMR REGISTERS (2M BYTE) 0xFFE0 0000 SYSTEM MMR REGISTERS (2M BYTE) 0xFFC0 0000 RESERVED 0xFFB0 1000 SCRATCHPAD SRAM (4K BYTE) 0xFFB0 0000 RESERVED 0xFFA1 4000 INSTRUCTION SRAM/CACHE (16K BYTE) 0xFFA1 0000 RESERVED INTERNAL 0xFFA0 C000 MEMORY INSTRUCTION BANK B SRAM (16K BYTE)

- Page 106 Memory Architecture ADSP-BF536 MEMORY MAP 0xFFFF FFFF CORE MMR REGISTERS (2M BYTE) 0xFFE0 0000 SYSTEM MMR REGISTERS (2M BYTE) 0xFFC0 0000 RESERVED 0xFFB0 1000 SCRATCHPAD SRAM (4K BYTE) 0xFFB0 0000 RESERVED 0xFFA1 4000 INSTRUCTION SRAM/CACHE (16K BYTE) 0xFFA1 0000 RESERVED INTERNAL 0xFFA0 C000 MEMORY...

- Page 107 Memory ADSP-BF537 MEMORY MAP 0xFFFF FFFF CORE MMR REGISTERS (2M BYTE) 0xFFE0 0000 SYSTEM MMR REGISTERS (2M BYTE) 0xFFC0 0000 RESERVED 0xFFB0 1000 SCRATCHPAD SRAM (4K BYTE) 0xFFB0 0000 RESERVED 0xFFA1 4000 INSTRUCTION SRAM/CACHE (16K BYTE) 0xFFA1 0000 RESERVED INTERNAL 0xFFA0 C000 MEMORY INSTRUCTION BANK B SRAM (16K BYTE)

- Page 108 L1 Instruction SRAM Table 3-2 lists the memory start locations of the L1 instruction memory subbanks. Table 3-2. L1 Instruction Memory Subbanks Memory Subbank Memory Start Location ADSP-BF534, ADSP-BF536, ADSP-BF537 0xFFA0 0000 0xFFA0 1000 0xFFA0 2000 0xFFA0 3000 0xFFA0 4000 0xFFA0 5000 0xFFA0 6000 0xFFA0 7000...

- Page 109 Memory L1 Data SRAM Table 3-3 shows how the subbank organization is mapped into memory. Table 3-3. L1 Data Memory SRAM Subbank Start Addresses Memory Bank and Subbank ADSP-BF534 and ADSP-BF536 ADSP-BF537 Data Bank A, Subbank 0 0xFF80 0000 Data Bank A, Subbank 1 0xFF80 1000 Data Bank A, Subbank 2 0xFF80 2000...

-

Page 110: L1 Data Cache

L1 Data Cache L1 Data Cache When data cache is enabled (controlled by bits in the DMC[1:0] register), either 16K byte of data bank A or 16K byte of DMEM_CONTROL both data bank A and data bank B can be set to serve as cache. For the ADSP-BF534 and ADSP-BF537, the upper 16K byte is used. -

Page 111: Dmem_Control Register

Memory DMEM_CONTROL Register The data memory control register ( ), shown in Figure 3-4, DMEM_CONTROL contains control bits for the L1 data memory. Data Memory Control Register (DMEM_CONTROL) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 0xFFE0 0004 Reset = 0x0000 1001 15 14 13 12 11 10... -

Page 112: Dtest_Command Register

Processor-Specific MMRs DTEST_COMMAND Register When the data test command register ( ) is written to, the DTEST_COMMAND L1 cache data or tag arrays are accessed, and the data is transferred through the data test data registers ( ). This register is DTEST DATA[1:0] shown in Figure... -

Page 113: System Interrupts

4 SYSTEM INTERRUPTS This chapter discusses the System Interrupt Controller (SIC), which is specific to the ADSP-BF534, ADSP-BF536, ADSP-BF537 derivatives. While this chapter does refer to features of the Core Event Controller (CEC), it does not cover all aspects of it. Please refer to the ADSP-BF53x/BF56x Blackfin Processor Programming Reference for more information on the CEC. -

Page 114: Interfaces

Interfaces Interfaces Figure 4-1 provides an overview of how the individual peripheral inter- rupt request lines connect to the SIC. It also shows how the four interrupt assignment registers ( ) control the assignment to the nine avail- SIC_IARx able peripheral request inputs of the CEC. The memory-mapped , and registers are part of... - Page 115 System Interrupts IPEND IMASK DMA ERROR ILAT DMAR0 BLOCK DONE DMAR1 BLOCK DONE DMAR0 OVERFLOW DMAR1 OVERFLOW PLL WAKEUP CAN ERROR MAC ERROR SPORT0 ERROR DMA0 (PPI) SPORT1 ERROR DMA3 (SPORT0 RX) PPI ERROR DMA4 (SPORT0 TX) SPI ERROR DMA5 (SPORT1 RX) UART0 ERROR UART1 ERROR DMA6 (SPORT1 RX)

- Page 116 Description of Operation An interrupt is an event that changes the normal processor instruction flow and is asynchronous to program flow. In contrast, an exception is a software initiated event whose effects are synchronous to program flow. The event system is nested and prioritized. Consequently, several service routines may be active at any time, and a low priority event may be pre-empted by one of higher priority.

- Page 117 System Interrupts Table 4-1. System and Core Event Mapping (Cont’d) Event Source Core Event Name System interrupts PLL wakeup interrupt IVG7 DMA error (generic) DMAR0 block done DMAR1 block done DMAR0 overflow DMAR1 overflow CAN error interrupt MAC error interrupt PPI error interrupt SPORT0 error interrupt SPORT1 error interrupt...

- Page 118 Description of Operation Table 4-1. System and Core Event Mapping (Cont’d) Event Source Core Event Name System interrupts, continued DMA9 interrupt (UART0 TX) IVG10 TWI interrupt DMA7 interrupt (SPI) DMA8 interrupt (UART0 RX) DMA10 interrupt (UART1 RX) DMA11 interrupt (UART1 TX) Port H interrupt A IVG11 CAN RX interrupt...

-

Page 119: System Peripheral Interrupts

System Interrupts System Peripheral Interrupts To service the rich set of peripherals, the SIC has 32 interrupt request inputs and 9 interrupt request outputs which go to the CEC. The primary function of the SIC is to mask, group, and prioritize interrupt requests and to forward them to the 9 general-purpose interrupt inputs of the CEC –... - Page 120 Description of Operation of whether the particular interrupt is enabled at the peripheral itself. At reset, the contents of are all 0s to mask off all peripheral inter- SIC_IMASK rupts. Turning off a system interrupt mask and enabling the particular interrupt is performed by writing a 1 to a bit location in SIC_IMASK The SIC includes a read-only system interrupt status register (...

- Page 121 System Interrupts register is not affected by the state of the system interrupt SIC_ISR mask register ( ) and can be read at any time. Writes to the SIC_IMASK register have no effect on its contents. SIC_ISR Peripheral DMA channels are mapped in a fixed manner to the peripheral interrupt IDs.

- Page 122 Description of Operation read from or written to at any time. To prevent spurious or lost interrupt activity, this register should be written to only when all peripheral inter- rupts are disabled. The wakeup function is independent of the interrupt mask func- tion.

- Page 123 System Interrupts Table 4-2 shows the peripheral interrupt events, the default mapping of each event, the peripheral interrupt ID used in the system interrupt assignment registers ( ), and the core interrupt ID. See SIC_IARx “SIC_IARx Registers” on page 4-18. Table 4-2.

- Page 124 Description of Operation Table 4-2. System Interrupt Controller (SIC) (Cont’d) Peripheral Interrupt Default DMA Source Peripheral Default Default Event Mapping Interrupt ID Mapping Core Interrupt ID DMA channel 6 SPORT 1 TX IVG9 IVG10 IVG10 DMA channel 7 IVG10 DMA channel 8 UART0 RX IVG10 DMA channel 9...

- Page 125 System Interrupts Table 4-2. System Interrupt Controller (SIC) (Cont’d) Peripheral Interrupt Default DMA Source Peripheral Default Default Event Mapping Interrupt ID Mapping Core Interrupt ID Port H interrupt B IVG11 Timer 0 IVG12 Timer 1 IVG12 Timer 2 IVG12 Timer 3 IVG12 Timer 4 IVG12...

-

Page 126: Programming Model

Programming Model Programming Model The programming model for the system interrupts is described in the fol- lowing sections. System Interrupt Initialization If the default assignments shown in Table 4-2 on page 4-11 are accept- able, then interrupt initialization involves only: •... - Page 127 System Interrupts 4. The registers, which map the peripheral interrupts to a SIC_IARx smaller set of general-purpose core interrupts ( IVG7 – IVG15 determine the core priority of interrupt A. adds interrupt A to its log of interrupts latched by the core ILAT but not yet actively being serviced.

-

Page 128: System Interrupt Controller Registers

System Interrupt Controller Registers RESET "INTERRUPT IVTMR A" IVHW PERIPHERAL CORE INTERRUPT CORE SYSTEM ASSIGN EVENT CORE REQUESTS INTERRUPT INTERRUPT SYSTEM VECTOR STATUS MASK MASK PRIORITY TABLE (ILAT) (IMASK) (SIC_IMASK) (SIC_IAR0..3) (EVT[15:0]) SYSTEM SYSTEM CORE WAKEUP STATUS PENDING (SIC_IWR) (SIC_ISR) (IPEND) TO DYNAMIC POWER MANAGEMENT... - Page 129 System Interrupts Table 4-3 defines the value to write in to configure a peripheral SIC_IARx for a particular IVG priority. Table 4-3. IVG Select Definitions General-purpose Interrupt Value in SIC_IAR IVG7 IVG8 IVG9 IVG10 IVG11 IVG12 IVG13 IVG14 IVG15 ADSP-BF537 Blackfin Processor Hardware Reference 4-17...

-

Page 130: Sic_Iarx Registers

System Interrupt Controller Registers SIC_IARx Registers System Interrupt Assignment Register 0 (SIC_IAR0) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 0xFFC0 0110 Reset = 0x2221 1000 DMA Channel 0 (PPI) DMA Channel 5 Interrupt (SPORT1 RX) Interrupt DMA Channel 3 (SPORT0... - Page 131 System Interrupts System Interrupt Assignment Register 2 (SIC_IAR2) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 Reset = 0x5555 5444 0xFFC0 0118 Timer 4 Interrupt Timer 1 Interrupt Timer 3 Interrupt Timer 2 Interrupt 15 14 13 12 11 10 Timer 0 Interrupt CAN TX Interrupt...

-

Page 132: Sic_Imask Register

System Interrupt Controller Registers SIC_IMASK Register System Interrupt Mask Register (SIC_IMASK) For all bits, 0 - Interrupt masked, 1 - Interrupt enabled 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 0xFFC0 010C Reset = 0x0000 0000 Software Watchdog CAN TX Interrupt... -

Page 133: Sic_Isr Register

System Interrupts SIC_ISR Register System Interrupt Status Register (SIC_ISR) For all bits, 0 - Deasserted, 1 - Asserted 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 0xFFC0 0120 Reset = 0x0000 0000 Software Watchdog CAN TX Interrupt Timer, Port F Inter-... -

Page 134: Sic_Iwr Register

System Interrupt Controller Registers SIC_IWR Register System Interrupt Wakeup-enable Register (SIC_IWR) For all bits, 0 - Wakeup function not enabled, 1 - Wakeup function enabled 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 0xFFC0 0124 Reset = 0xFFFF FFFF Software Watchdog... -

Page 135: Programming Examples

System Interrupts Programming Examples The following sections provide examples for programming system interrupts. Clearing Interrupt Requests When the processor services a core event it automatically clears the requesting bit in the register and no further action is required by the ILAT interrupt service routine. - Page 136 Programming Examples Listing 4-1. Servicing GPIO Interrupt Request #include <defBF537.h> .section program; _portg_a_isr: /* push used registers */ [--sp] = (r7:7, p5:5); /* clear interrupt request on GPIO pin PG2 */ /* no matter whether used A or B channel */ p5.l = lo(PORTGIO_CLEAR);...

- Page 137 System Interrupts of the service routine, or the instruction is followed by another set SSYNC of instructions before the service routine returns. Commonly, a pop-mul- tiple instruction is used for this purpose as shown in Listing 4-1. The level-sensitive nature of peripheral interrupts enables more than one of them to share the same IVG channel and therefore the same interrupt priority.

- Page 138 Programming Examples 4-26 ADSP-BF537 Blackfin Processor Hardware Reference...

-

Page 139: Direct Memory Access

5 DIRECT MEMORY ACCESS This chapter describes the Direct Memory Access (DMA) controller. Fol- lowing an overview and list of key features is a description of operation and functional modes of operation. The chapter concludes with a pro- gramming model, consolidated register definitions, and programming examples. - Page 140 Overview and Features The DMA controller can perform several types of data transfers: • Peripheral DMA transfers data between memory and on-chip peripherals. The processor has 12 peripheral DMA channels that support 7 peripherals. • Ethernet MAC (dedicated DMA channel for transmit and receive.

- Page 141 Direct Memory Access set of parameters stored within memory to initiate a DMA sequence. This sort of transfer allows the chaining together of multiple DMA sequences. In descriptor-based DMA operations, a DMA channel can be pro- grammed to automatically set up and start another DMA transfer after the current sequence completes.

- Page 142 Overview and Features • SPORT0 receive • SPORT0 transmit • SPORT1 receive • SPORT1 transmit • SPI receive/transmit • UART0 receive • UART0 transmit • UART1 receive • UART1 transmit • MDMA0 destination • MDMA0 source • MDMA1 destination • MDMA1 source ADSP-BF537 Blackfin Processor Hardware Reference...

-

Page 143: Dma Controller Overview

Direct Memory Access DMA Controller Overview Figure 5-1 provides a block diagram of the DMA controller. DMAR0 DMAR1 CCLK SCLK DMA TRAFFIC CONTROL IRQ 1 MDMA 0 SOURCE CONTROL FIFO IRQ 29 MDMA 0 DESTINATION CONTROL HMDMA 0 MDMA 1 SOURCE CONTROL FIFO IRQ 30 HMDMA 1... -

Page 144: External Interfaces

DMA Controller Overview External Interfaces The DMA does not connect external memories and devices directly. Rather, data is passed through the EBIU port. Any kind of device that is supported by the EBIU can also be accessed by peripheral DMA or mem- ory DMA operation. -

Page 145: Peripheral Dma

Direct Memory Access The 16-bit DMA Access Bus (DAB) connects the DMA controller to the on-chip peripherals, PPI, SPI, Ethernet MAC, the SPORTs, and the UARTs. It operates at frequency. SCLK The 16-bit DMA External Bus (DEB) connects the DMA controller to the EBIU port. - Page 146 DMA Controller Overview Table 5-1. Default Mapping of Peripheral to DMA (Cont’d) DMA Channel PMAP Default Value Peripheral Mapped by Default DMA 2 Ethernet MAC transmit DMA 3 SPORT0 receive DMA 4 SPORT0 transmit DMA 5 SPORT1 receive DMA 6 SPORT1 transmit DMA 7 DMA 8...

-

Page 147: Memory Dma

Direct Memory Access channel, that channel is disabled—DMA requests are ignored, and no DMA grants are issued. The DMA requests are also not for- warded from the peripheral to the interrupt controller. The twelve peripheral DMA channels work completely independently from each other. - Page 148 DMA Controller Overview A memory-to-memory transfer always requires the source and the destina- tion channel to be enabled. The four channels are hardwired for DMA priorities 12 through 15. Each source/destination channel forms a “stream,” and these two streams are hardwired for DMA priorities 8 through 11.

-

Page 149: Handshaked Memory Dma Mode

Direct Memory Access To start an MDMA transfer operation, the MMRs for the source and des- tination channels are written, each in a manner similar to peripheral DMA. Note the register for the source channel must be writ- DMAx_CONFIG ten before the register for the destination channel. -

Page 150: Modes Of Operation

Modes of Operation Modes of Operation The following sections describe the DMA operation. Register-based DMA Operation Register-based DMA is the traditional kind of DMA operation. Software writes source or destination address and length of the data to be trans- ferred into memory-mapped registers and then starts DMA operation. For basic operation the software performs these steps: •... -

Page 151: Stop Mode

Direct Memory Access • Write the operation mode to the register. These bits DMAx_CONFIG in particular need to be changed as needed: • The bit enables the DMA channel. DMAEN • The bit controls the DMA direction. DMAs that read from memory keep this bit cleared, for example, transmit- ting peripheral DMAs and the source channel of memory DMAs. -

Page 152: Autobuffer Mode

Modes of Operation should clear the enable bit to disable a paused channel. Stop mode DMAEN is entered if the bit field in the DMA channel’s register FLOW DMAx_CONFIG is 0. The field must always be 0 in this mode. NDSIZE For receive (memory write) operation, the bit functions almost... -

Page 153: Examples Of Two-Dimensional Dma

Direct Memory Access value is the byte-address increment that is applied DMAx_X_MODIFY after each transfer that decrements the register. The DMAx_CURR_X_COUNT value is not applied when the inner loop count is ended by DMAx_X_MODIFY decrementing from 1 to 0, except that it is applied on DMAx_CURR_X_COUNT the final transfer when is 1 and... -

Page 154: Descriptor-Based Dma Operation

Modes of Operation This produces the following address offsets from the start address: 0,1,2,...15, N,N + 1, ... N + 15, 2N, 2N + 1,... 2N + 15, ... 7N, 7N + 1,... 7N + 15, Example 2: Receive a video datastream of bytes, (R,G,B pixels) ×... -

Page 155: Descriptor List Mode

Direct Memory Access A descriptor describes what kind of operation should be performed next by the DMA channel. This includes the DMA configuration word as well as data source/destination address, transfer count, and address modify val- ues. A DMA sequence controlled by one descriptor is called a work unit. Optionally, an interrupt can be requested at the end of any work unit by setting the bit in the configuration word of the respective... -

Page 156: Descriptor Array Mode

Modes of Operation descriptor must reside in the same 64 KB address space as the first one, because the upper 16 bits of the register are not DMAx_NEXT_DESC_PTR updated. Descriptor list modes are started by writing first to the DMAx_NEXT_DESC_ register and then to the register. -

Page 157: Mixing Flow Modes

Direct Memory Access All the other registers not loaded from the descriptor retain their prior val- ues, although the , and DMAx_CURR_ADDR DMAx_CURR_X_COUNT DMAx_CURR_Y_ registers are reloaded between the descriptor fetch and the start of COUNT DMA operation. Table 5-2 shows the offsets for descriptor elements in the three modes described above. -

Page 158: Functional Description

Functional Description the first descriptor if a descriptor array is used in an endless manner. If the descriptor chain is not endless and the DMA is required to stop after a cer- tain descriptor has been processed, the last descriptor is typically processed in stop mode, that is, its fields are 0, but its bit is... - Page 159 Direct Memory Access descriptor elements in memory. After the descriptor fetch, if any, is com- pleted, DMA operation begins, initiated by writing with DMAx_CONFIG DMAEN = 1 USER WRITES SOME OR ALL DMA PARAMETER REGISTERS, AND THEN WRITES DMA_CONFIG BAD DMA_CONFIG? DMA ERROR DMAEN = 0 TEST DMAEN...

- Page 160 Functional Description NDSIZE = 0 OR NDSIZE > MAX_SIZE* TEST NDSIZE ABORT OCCURS NDSIZE > 0 AND NDSIZE <= MAX_SIZE* READ NDSIZE ELEMENTS OF DESCRIPTOR INTO PARAMETER REGISTERS VIA CURRENT DESCRIPTOR POINTER FLOW = 0 OR 1 CLEAR DFETCH IN IRQ_STATUS DMA TRANSFER BEGINS AND...

- Page 161 Direct Memory Access When is written directly by software, the DMA controller DMAx_CONFIG recognizes this as the special startup condition that occurs when starting DMA for the first time on this channel or after the engine has been stopped ( FLOW = 0 When the descriptor fetch is complete and , the...

- Page 162 Functional Description is not part of the descriptor, the previous settings DMACFG DMAx_CONFIG (as written by MMR access at startup) control the work unit operation. If is part of the descriptor, then the value programmed DMACFG DMAx_CONFIG by the MMR access controls only the loading of the first descriptor from memory.

-

Page 163: Dma Refresh

Direct Memory Access Then DMA data transfer operation begins, as shown in Figure 5-3 on page 5-22. DMA Refresh On completion of a work unit, the DMA controller: • Completes the transfer of all data between memory and the DMA unit. - Page 164 Functional Description Next, fetches a descriptor from memory into DMA registers via the new contents of , while incrementing DMAx_CURR_DESC_PTR DMAx_ . The first descriptor element loaded is a new 16-bit CURR_DESC_PTR value for the lower 16 bits of , followed by the DMAx_NEXT_DESC_PTR rest of the descriptor elements.

-

Page 165: Work Unit Transitions

Direct Memory Access • If (descriptor array, descriptor list small, or FLOW 4, 6, or 7 descriptor list large, respectively) the DMA controller clears the bit in the register. DFETCH DMAx_IRQ_STATUS • If = any value but 0 (Stop), the DMA controller begins the FLOW next work unit, contending with other channels for priority on the memory buses. -

Page 166: Dma Transmit And Mdma Source

Functional Description the cost of higher latency in the transition. In synchronized transitions, the DMA FIFO pipeline is drained to the destination or flushed (RX data discarded) between work units. Work unit transitions for MDMA streams are controlled by the bit of the MDMA source channel’s register. - Page 167 Direct Memory Access however, and not yet at the peripheral, so the DMA interrupt should not be used as the sole means of synchronizing the shutdown or reconfigura- tion of the peripheral following a transmission. (continuous transition) on a transmit (memory read) SYNC = 0 descriptor, the next descriptor is required to have the same data word size, read/write direction, and source memory (internal vs.

-

Page 168: Dma Receive

Functional Description DMA Receive In DMA receive (memory write) channels, the bit controls the han- SYNC dling of the DMA FIFO between descriptor chains (not individual descriptors), when the DMA channel is paused. The DMA channel pauses after descriptors with mode, and may be restarted (for exam- FLOW = STOP ple, after an interrupt) by writing the channel’s... -

Page 169: Stopping Dma Transfers

Direct Memory Access If a descriptor chain begins with a bit of 1, there is no restriction on SYNC DMA word size of the new chain in comparison to the previous chain. The DMA word size must not change between one descriptor and the next in any DMA receive (memory write) channel within a sin- gle descriptor chain, regardless of the bit setting. -

Page 170: Dma Errors (Aborts)

Functional Description a row in its usage of the relevant memory space to allow up to three pending DMA accesses to issue, plus allowing enough memory access time for the accesses themselves to complete. DMA Errors (Aborts) The DMA controller flags conditions that cause the DMA process to end abnormally (that is, abort). - Page 171 Direct Memory Access • A disallowed register write occurred while the channel was run- ning. Only the registers can be DMAx_CONFIG DMAx_IRQ_STATUS written when DMA_RUN = 1 • An address alignment error occurred during any memory access. For example, register (16 bit) but the DMAx_CONFIG WDSIZE = 1...

-

Page 172: Dma Control Commands

Functional Description • Descriptor chain indicates data buffers that are not in the same internal/external memory space. • In 2D DMA, X_COUNT = 1 Table 5-3. Legal NDSIZE Values FLOW NDSIZE Note 0 < NDSIZE <= 7 Descriptor array, no descriptor pointer fetched 0 <... - Page 173 Direct Memory Access restrictions regarding work units and descriptor chains (described later in this section) so that the peripheral operates properly whenever it issues DMA control commands. The ADSP-BF536/ADSP-BF537 processors have just one DMA-manage- ment-capable peripheral, the Ethernet MAC. Refer to Chapter 8, “Ethernet MAC”, for a description of how receive and transmit channels...

- Page 174 Functional Description Additional information for the control commands includes: • Restart The restart control command causes the current work unit to inter- rupt processing and start over, using the addresses and counts from , and . No interrupt DMAx_START_ADDR DMAx_X_COUNT DMAx_Y_COUNT is signalled.

- Page 175 Direct Memory Access stream into work units on its own, perhaps as a result of parsing the data currently passing though its supported communication chan- nel, without direct real-time control by the processor. If a channel programmed for transmit (memory read) receives a finish control command, the channel momentarily pauses while any pending memory reads initiated prior to the finish command are completed.

-

Page 176: Restrictions

Functional Description • Request Data Urgent The request data urgent control command behaves identically to the DMA request control command, except that while it is asserted the DMA channel performs its memory accesses with urgent prior- ity. This includes both data and descriptor-fetch memory accesses. A DMA-management-capable peripheral might use this control command if an internal FIFO is approaching a critical condition, for example. -

Page 177: Receive Restart Or Finish

Direct Memory Access Receive Restart or Finish No restart or finish control command may be issued by a peripheral to a channel configured for memory write unless either (a) the peripheral has already performed at least five DMA transfers in the current work unit, or (b) the previous work unit was terminated by a finish control command and the peripheral has performed at least one DMA transfer in the current work unit. -

Page 178: Handshaked Memory Dma Operation

Functional Description Handshaked Memory DMA Operation Both inputs have their own set of control and status registers. DMARx Handshake operation for MDMA0 is enabled by the bit in the HMDMAEN register. Similarly, the bit in the HMDMA0_CONTROL HMDMAEN HMDMA1_CONTROL register enables handshake mode for MDMA1. It is important to understand that the handshake hardware works com- pletely independent from the descriptor and autobuffer capabilities of the MDMA, allowing most flexible combinations of logical data organization... -

Page 179: Pipelining Dma Requests

Direct Memory Access Since the block count registers are 16 bits wide, blocks can group up to 65535 transfers. Once a block transfer has been started, the registers return HMDMAx_BCOUNT the remaining number of transfers to complete the current block. When the complete block has been processed, the register returns HMDMAx_BCOUNT... - Page 180 Functional Description Figure 5-4 illustrates how an asynchronous FIFO could be connected. In such a scenario the bit was cleared to let the request pin listen to DMARx falling edges. The Blackfin processor does not evaluate the full flag such FIFOs usually provide, because asynchronous polling of that signal would reduce the system throughput drastically.

-

Page 181: Hmdma Interrupts

Direct Memory Access half the FIFO depth. Then, the MDMA does not start consuming data as long as the FIFO is not half filled. BLACKFIN 1024K x 16 FIFO O0 .. O15 I0 .. I15 D0 .. D15 AMSx DMARx Figure 5-5. -

Page 182: Dma Performance

Functional Description The block done interrupt signals that a complete MDMA block as defined by the register has been transferred, that is, when the HMDMAx_BCINIT register decrements to zero. While the bit enables this HMDMAx_BCOUNT BDIE interrupt, the bit can gate it until the edge count also becomes zero, MBDI meaning that all requested MDMA transfers have been completed. -

Page 183: Dma Throughput

Direct Memory Access • How often do competing DMA channels require the bus systems to alter direction? • How often do competing DMA or core accesses cause the SDRAM to open different pages? • Is there a way to distribute DMA requests nicely over time? A key feature of the DMA architecture is the separation of the activity on the peripheral DMA bus (the DMA Access Bus (DAB)) from the activity on the buses between the DMA and memory (the DMA Core Bus (DCB) - Page 184 Functional Description When all DMA channels’ traffic is taken in the aggregate: • Transfers between the peripherals and the DMA unit have a maxi- mum rate of one 16-bit transfer per system clock. • Transfers between the DMA unit and internal memory (L1) have a maximum rate of one 16-bit transfer per system clock.

- Page 185 Direct Memory Access • Descriptor fetches consume one DMA memory cycle per 16-bit word read from memory, but do not delay transfers on the DAB bus. • Initialization of a DMA channel stalls DMA activity for one cycle. This occurs when changes from 0 to 1 or when the DMAEN SYNC...

-

Page 186: Memory Dma Timing Details

Functional Description Memory DMA Timing Details When the destination register is written, MDMA operation DMAx_CONFIG starts, after a latency of 3 cycles. SCLK First, if either MDMA channel has been selected to use descriptors, the descriptors are fetched from memory. The destination channel descriptors are fetched first. - Page 187 Direct Memory Access Table 5-5. Priority and Default Mapping of Peripheral to DMA Priority DMA Channel PMAP Default Peripheral Mapped by Default Value Highest DMA 0 PPI receive or transmit DMA 1 Ethernet MAC receive DMA 2 Ethernet MAC transmit DMA 3 SPORT0 receive DMA 4...

-

Page 188: Temporary Dma Urgency

Functional Description Temporary DMA Urgency Typically, DMA transfers for a given peripheral occur at regular intervals. Generally, the shorter the interval, the higher the priority that should be assigned to the peripheral. If the average bandwidth of all the peripherals is not too large a fraction of the total, then all peripherals’... -

Page 189: Memory Dma Priority And Scheduling

Direct Memory Access DMA requests from an MDMA channel become urgent when handshaked operation is enabled and the DMARx edge count exceeds the value stored in the register. If handshaked operation is disabled, soft- HMDMAx_ECURGENT ware can control urgency of requests directly by altering the bit field in the register. - Page 190 Functional Description If two MDMA streams are used (S0-D0 and S1-D1), the user may choose to allocate bandwidth either by fixed stream priority or by a round robin scheme. This is selected by programming the MDMA_ROUND_ROBIN_PERIOD field in the register (see “Static Channel Prioritization”...

-

Page 191: Traffic Control

Direct Memory Access transfer corresponding to a count of 1, the MDMA stream selection is passed automatically to the other stream with zero overhead, and the counter is reloaded with the period value from MDMA_ROUND_ROBIN_COUNT . In this cycle, if the other MDMA stream is MDMA_ROUND_ROBIN_PERIOD ready to perform a transfer, the stream selection is locked on the new MDMA stream. - Page 192 Functional Description is requesting DMA but its FIFO is not ready (for example, an empty transmit FIFO or full receive FIFO). For more information, see “Tempo- rary DMA Urgency” on page 5-50. Traffic control is an important consideration in optimizing use of DMA resources.

-

Page 193: Programming Model

Direct Memory Access This type of traffic control represents a trade-off of latency to improve uti- lization (efficiency). Higher traffic timeouts might increase the length of time each request waits for its grant, but it often dramatically improves the maximum attainable bandwidth in congested systems, often to above 90%. -

Page 194: Synchronization Of Software And Dma

Programming Model Synchronization of Software and DMA A critical element of software DMA management is synchronization of DMA buffer completion with the software. This can best be done using interrupts, polling of , or a combination of both. Polling DMAx_IRQ_STATUS for address or count can only provide synchronization within loose toler- ances comparable to pipeline lengths. - Page 195 Direct Memory Access Polling of the current address, pointer, and count registers can permit loose synchronization of DMA with software, however, if allowances are made for the lengths of the DMA/memory pipeline. The length of the DMA FIFO for a peripheral DMA channel is four locations (either four 8- or 16-bit data elements, or two 32-bit data elements) and for an MDMA FIFO is eight locations (four 32-bit data elements).

-

Page 196: Single-Buffer Dma Transfers

Programming Model read DMA, the final memory read data will have been safely received in the DMA’s FIFO; for memory write DMA, the DMA unit will have received an acknowledge from L1 memory or the EBIU that the data has been written. - Page 197 Direct Memory Access transfer, which might overwrite or re-read the first buffer location before it is processed by software. This scheme may be workable if the system design guarantees that the data repeat period is longer than the interrupt latency under all circumstances. •...

-

Page 198: Descriptor Structures

Programming Model for four sub-buffers DMAx_Y_COUNT = 4 , same as for contiguous DMAx_Y_MODIFY = 4 DMAx_X_MODIFY sub-buffers The synchronization core might read to determine DMAx_Y_COUNT which sub-buffer is currently being transferred, and then allow one full sub-buffer to account for pipelining. For example, if a read of shows a value of 3, then the software should assume DMAx_Y_COUNT that sub-buffer 3 is being transferred, but some portion of... -

Page 199: Descriptor Queue Management

Direct Memory Access It is important to remember the meaning of the various fields in the descriptor elements when building a list or array of DMA DMAx_CONFIG descriptors. In particular: • The lower byte of specifies the DMA transfer to be DMAx_CONFIG performed by the current descriptor (for example, interrupt-enable, 2D mode) -

Page 200: Descriptor Queue Using Interrupts On Every Descriptor

Programming Model structure. In this case, the members of each descriptor NDPH NDPL could even be written once at startup, and skipped over as each descrip- tor’s new contents are written. The recommended method for synchronization of a descriptor queue is through the use of an interrupt. -

Page 201: Descriptor Queue Using Minimal Interrupts

Direct Memory Access If the counts are unequal, the software instead modifies the next-to-last descriptor’s value so that its upper half ( DMAx_CONFIG FLOW NDSIZE now describes the newly queued descriptor. This operation does not dis- rupt the DMA channel, provided the rest of the descriptor data structure is initialized in advance. - Page 202 Programming Model When each new DMA request is processed, the software’s non-interrupt code fills in a new descriptor’s contents and adds it to the waiting portion of the queue. The descriptor’s word should have a value DMAx_CONFIG FLOW of zero. If more than one request is received before the DMA queue com- pletion interrupt occurs, the non-interrupt code should queue later descriptors, forming a waiting portion of the queue that is disconnected from the active portion of the queue being processed by the DMA unit.

-

Page 203: Software Triggered Descriptor Fetches

Direct Memory Access active queue. The interrupt handler should then pass a message back to the non-interrupt software indicating the location of the last descriptor accepted into the active queue. If, on the other hand, the interrupt han- dler reads its mailbox and finds a value of zero, indicating DMAx_CONFIG there is no more work to perform, then it should pass an appropriate mes-... - Page 204 Programming Model The next descriptor pointer remains valid, if the DMA halts and is restarted. As soon as the bit clears, software can restart the DMA DMA_RUN and force the DMA controller to fetch the next descriptor. To accomplish this, the software writes a value with the bit set and with proper val- DMAEN ues in the...

-

Page 205: Dma Registers

Direct Memory Access If all fields in a descriptor chain have the fields set DMACFG FLOW NDSIZE to zero, the individual DMA sequences do not start until triggered by soft- ware. This is useful when the DMAs need to be synchronized with other events in the system, and it is typically performed by interrupt service rou- tines. -

Page 206: Dma Channel Registers

DMA Registers DMA Channel Registers The processor features twelve peripheral DMA channels and two channel pairs for memory DMA. All channels have an identical set of registers summarized in Table 5-6. Table 5-6 lists the generic names of the DMA registers. For each register, the table also shows the MMR offset, a brief description of the register, the register category. - Page 207 Direct Memory Access Table 5-6. Generic Names of the DMA Memory-mapped Registers (Cont’d) Generic MMR Name MMR Description Register Name of Offset Category Corresponding Descriptor Element in Memory 0x20 CURR_DESC_PTR Current Descriptor Pointer Current 0x24 CURR_ADDR Current DMA Address Current 0x28 IRQ_STATUS Interrupt Status register:...

- Page 208 DMA Registers “yy” stands for either “D0”, “S0”, “D1”, or “S1” to indicate destination and source channel registers of MDMA0 and MDMA1. For example, the configuration register of peripheral DMA channel 6 is called DMA6_CONFIG The one for MDMA1 source channel is called MDMA_S1_CONFIG The generic MMR names shown in Table 5-6...

-

Page 209: Dmax_Peripheral_Map

Direct Memory Access DMAx_PERIPHERAL_MAP/MDMA_yy_PERIPHERAL_MAP Registers Each DMA channel’s peripheral map register ( DMAx_PERIPHERAL_ , shown in Figure 5-6) contains bits that: MAP/MDMA_yy_PERIPHERAL_MAP • Map the channel to a specific peripheral. • Identify whether the channel is a peripheral DMA channel or a memory DMA channel. - Page 210 DMA Registers Table 5-7. Peripheral Map Register Memory-mapped Addresses Register Name Memory-mapped Address DMA0_PERIPHERAL_MAP 0xFFC0 0C2C DMA1_PERIPHERAL_MAP 0xFFC0 0C6C DMA2_PERIPHERAL_MAP 0xFFC0 0CAC DMA3_PERIPHERAL_MAP 0xFFC0 0CEC DMA4_PERIPHERAL_MAP 0xFFC0 0D2C DMA5_PERIPHERAL_MAP 0xFFC0 0D6C DMA6_PERIPHERAL_MAP 0xFFC0 0DAC DMA7_PERIPHERAL_MAP 0xFFC0 0DEC DMA8_PERIPHERAL_MAP 0xFFC0 0E2C DMA9_PERIPHERAL_MAP 0xFFC0 0E6C DMA10_PERIPHERAL_MAP...

- Page 211 Direct Memory Access Table 5-8 lists the binary peripheral map settings for each DMA-capable peripheral. Table 5-8. Peripheral Mapping Default Peripheral Default PERIPHERAL_ Comments Channel Mapping MAP Setting (Binary) DMA0 PPI receive/transmit b#0000 0000 0000 0000 (highest priority) DMA1 Ethernet receive b#0001 0000 0000 0000 Invalid PMAP default setting on...

-

Page 212: Dmax_Config/Mdma_Yy_Config Registers

DMA Registers DMAx_CONFIG/MDMA_yy_CONFIG Registers The DMA configuration register ( , shown DMAx_CONFIG/MDMA_yy_CONFIG) Figure 5-7, is used to set up DMA parameters and operating modes. Note that writing the register while DMA is already running DMAx_CONFIG will cause a DMA error unless writing with the bit set to 0. - Page 213 Direct Memory Access Table 5-9. Configuration Register Memory-mapped Addresses Register Name Memory-mapped Address DMA0_CONFIG 0xFFC0 0C08 DMA1_CONFIG 0xFFC0 0C48 DMA2_CONFIG 0xFFC0 0C88 DMA3_CONFIG 0xFFC0 0CC8 DMA4_CONFIG 0xFFC0 0D08 DMA5_CONFIG 0xFFC0 0D48 DMA6_CONFIG 0xFFC0 0D88 DMA7_CONFIG 0xFFC0 0DC8 DMA8_CONFIG 0xFFC0 0E08 DMA9_CONFIG 0xFFC0 0E48 DMA10_CONFIG...

- Page 214 DMA Registers interrupts are still filtered out by the DMA unit. The channel may be restarted simply by another write to the register DMAx_CONFIG specifying the next work unit, in which the bit is set to 1. DMAEN 0x1 - autobuffer mode. In this mode, no descriptors in memory are used.

- Page 215 Direct Memory Access • (data interrupt enable). This bit specifies whether to allow DI_EN completion of a work unit to generate a data interrupt. • (data interrupt timing select). This bit specifies the timing DI_SEL of a data interrupt—after completing the whole buffer or after completing each row of the inner loop.

-

Page 216: Mdma_Yy_Irq_Status Registers

DMA Registers • (DMA direction). This bit specifies DMA direction—memory read (0) or memory write (1). • (DMA channel enable). This bit specifies whether to enable DMAEN a given DMA channel. When a peripheral DMA channel is enabled, interrupts from the peripheral denote DMA requests. - Page 217 Direct Memory Access For a memory write DMA channel, the state of the bit has DMA_RUN no meaning after the last event has been signaled. It does DMA_DONE not indicate the status of the DMA FIFO. For MDMA transfers where it is not desired to use an interrupt to notify when the DMA operation has ended, software should poll bit, and not the bit, to determine when the...

- Page 218 DMA Registers Table 5-10. Interrupt Status Register Memory-mapped Addresses Register Name Memory-mapped Address DMA0_IRQ_STATUS 0xFFC0 0C28 DMA1_IRQ_STATUS 0xFFC0 0C68 DMA2_IRQ_STATUS 0xFFC0 0CA8 DMA3_IRQ_STATUS 0xFFC0 0CE8 DMA4_IRQ_STATUS 0xFFC0 0D28 DMA5_IRQ_STATUS 0xFFC0 0D68 DMA6_IRQ_STATUS 0xFFC0 0DA8 DMA7_IRQ_STATUS 0xFFC0 0DE8 DMA8_IRQ_STATUS 0xFFC0 0E28 DMA9_IRQ_STATUS 0xFFC0 0E68 DMA10_IRQ_STATUS...

- Page 219 Direct Memory Access Separate interrupt request (IRQ) levels are allocated for data and periph- eral error interrupts, and DMA error interrupts. Table 5-11. Data Driven Interrupts Interrupt Name Description No Interrupt Interrupts can be disabled for a given work unit. Peripheral Interrupt These are peripheral (non-DMA) interrupts.

-

Page 220: Mdma_Yy_Start_Addr Registers