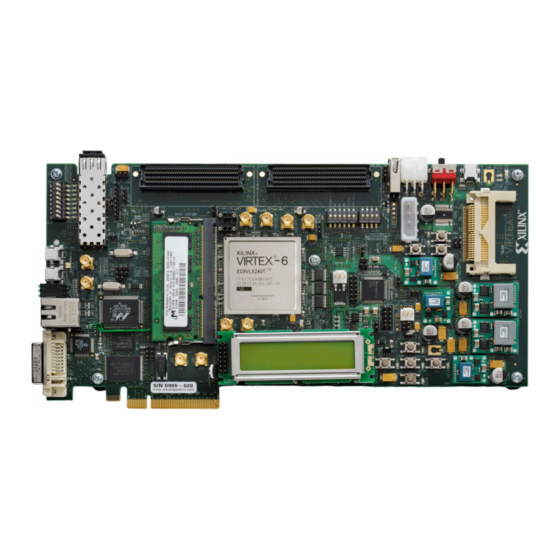

Xilinx Virtex-6 FPGA User Manual

Gth transceivers

Hide thumbs

Also See for Virtex-6 FPGA:

- Manual (381 pages) ,

- User manual (317 pages) ,

- Getting started manual (77 pages)

Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Xilinx Virtex-6 FPGA

- Page 1 Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 2 Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates.

-

Page 3: Revision History

Enabling 8B/10B Mode, page 85. In Table 3-12, and added reference to the Virtex-6 FPGA GTH Transceiver Wizard to attribute PRBS_CFG_LANE, bits [15:4] and PCS_RESET_1_LANE, bits [15:2]; changed the Reserved bits for [13:11] and [10:8] in the PCS_MODE_LANE attribute. In... - Page 4 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 5: Table Of Contents

Functional Description ........... . 67 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com... - Page 6 Interfacing to the RX AFE ..........105 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 7 ..........144 Reference Clock Power Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com...

- Page 8 ........146 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 9: Guide Contents

This document describes how to use the GTH transceivers in Virtex®-6 FPGAs. In this document: • Virtex-6 FPGA GTH transceiver is abbreviated as GTH transceiver. • GTHE1_QUAD is the name of the instantiation primitive that instantiates one Virtex-6 FPGA GTH transceiver. -

Page 10: Additional Resources

• Virtex-6 FPGA PCB Designer Guide This guide provides information on PCB design for Virtex-6 FPGA GTX transceivers, with a focus on strategies for making design decisions at the PCB and interface level. Additional Resources To find additional documentation, see the Xilinx website at: http://www.xilinx.com/support/documentation/index.htm. -

Page 11: Chapter 1: Transceiver And Tool Overview

Configurable fabric interface width • DRP and management interface to access the configuration registers The Xilinx® CORE Generator™ tool includes a Wizard to automatically configure GTH transceivers to support configurations for different protocols or perform custom configuration (see Virtex-6 FPGA GTH Transceiver Wizard, page 30). - Page 12 This figure does not illustrate exact size, location, or scale of the functional blocks to each other. It does show the correct number of available resources. To improve clarity, this figure does not show the CLB, DSP, and block RAM columns. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 13 Control, and Interface Clock for GTH1 GTH1 Fabric Data, PCS to Fabric Control, and Interface Clock for GTH0 GTH0 GTH QUAD UG371_c1_02_120809 Figure 1-2: GTH Quad Block Diagram Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 14: Port And Attribute Summary

Names that end with LANE3 are for the GTH3 transceiver on the Quad • Attribute names that do not end with LANE0, LANE1, LANE2 or LANE3 are shared. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 15 GTH Quad ports. Table 1-3: GTH Quad Port Summary Port Clock Domain DADDR[15:0] DCLK DCLK DCLK DFETRAINCTRL0 DFETRAINCTRL1 DCLK DFETRAINCTRL2 DFETRAINCTRL3 DI[15:0] DCLK DISABLEDRP DCLK DRPDO[15:0] DCLK Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 16 DCLK PLLREFCLKSEL[2:0] DCLK POWERDOWN0 TXUSERCLKIN0 POWERDOWN1 TXUSERCLKIN1 POWERDOWN2 TXUSERCLKIN2 POWERDOWN3 TXUSERCLKIN3 REFCLK RXBUFRESET0 RXUSERCLKIN0 RXBUFRESET1 RXUSERCLKIN1 RXBUFRESET2 RXUSERCLKIN2 RXBUFRESET3 RXUSERCLKIN3 RXCODEERR0[7:0] RXUSERCLKIN0 RXCODEERR1[7:0] RXUSERCLKIN1 RXCODEERR2[7:0] RXUSERCLKIN2 RXCODEERR3[7:0] RXUSERCLKIN3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 17 RXUSERCLKIN0 RXENCOMMADET1 RXUSERCLKIN1 RXENCOMMADET2 RXUSERCLKIN2 RXENCOMMADET3 RXUSERCLKIN3 RXN0 RXN1 RXN2 RXN3 In (Pad) RX Serial Clock RXP0 RXP1 RXP2 RXP3 RXPOLARITY0 RXUSERCLKIN0 RXPOLARITY1 RXUSERCLKIN1 RXPOLARITY2 RXUSERCLKIN2 RXPOLARITY3 RXUSERCLKIN3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 18 RXUSERCLKIN0 RXUSERCLKIN1 RXUSERCLKIN2 RXUSERCLKIN3 RXUSERCLKOUT0 RXUSERCLKOUT1 RXUSERCLKOUT2 RXUSERCLKOUT3 RXVALID0[7:0] RXUSERCLKIN0 RXVALID1[7:0] RXUSERCLKIN1 RXVALID2[7:0] RXUSERCLKIN2 RXVALID3[7:0] RXUSERCLKIN3 SAMPLERATE0[2:0] TXUSERCLKIN0 SAMPLERATE1[2:0] TXUSERCLKIN1 SAMPLERATE2[2:0] TXUSERCLKIN2 SAMPLERATE3[2:0] TXUSERCLKIN3 TSTPATH Async TSTREFCLKFAB TSTREFCLKOUT www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 19 TXDATA2[63:0] TXUSERCLKIN2 TXDATA3[63:0] TXUSERCLKIN3 TXDATAMSB0[7:0] TXUSERCLKIN0 TXDATAMSB1[7:0] TXUSERCLKIN1 TXDATAMSB2[7:0] TXUSERCLKIN2 TXDATAMSB3[7:0] TXUSERCLKIN3 TXDEEMPH0 TXUSERCLKIN0 TXDEEMPH1 TXUSERCLKIN1 TXDEEMPH2 TXUSERCLKIN2 TXDEEMPH3 TXUSERCLKIN3 TXMARGIN0[2:0] TXUSERCLKIN0 TXMARGIN1[2:0] TXUSERCLKIN1 TXMARGIN2[2:0] TXUSERCLKIN2 TXMARGIN3[2:0] TXUSERCLKIN3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 20 TXUSERCLKOUT2 TXUSERCLKOUT3 The ports in Table 1-4 are part of the GTH IBUFDS primitive. Table 1-4: GTH Reference Clock (IBUFDS_GTHE1) Port Summary Port Clock Domain Async Async Async www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 21 16-bit Hex E10GBASEKR_LD_COEFF_UPD_LANE2 E10GBASEKR_LD_COEFF_UPD_LANE3 E10GBASEKR_LP_COEFF_UPD_LANE0 E10GBASEKR_LP_COEFF_UPD_LANE1 16-bit Hex E10GBASEKR_LP_COEFF_UPD_LANE2 E10GBASEKR_LP_COEFF_UPD_LANE3 E10GBASEKR_PMA_CTRL_LANE0 E10GBASEKR_PMA_CTRL_LANE1 16-bit Hex E10GBASEKR_PMA_CTRL_LANE2 E10GBASEKR_PMA_CTRL_LANE3 E10GBASEKX_CTRL_LANE0 E10GBASEKX_CTRL_LANE1 16-bit Hex E10GBASEKX_CTRL_LANE2 E10GBASEKX_CTRL_LANE3 E10GBASER_PCS_CFG_LANE0 E10GBASER_PCS_CFG_LANE1 16-bit Hex E10GBASER_PCS_CFG_LANE2 E10GBASER_PCS_CFG_LANE3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 22 16-bit Hex E10GBASER_PCS_SEEDA3_LANE2 E10GBASER_PCS_SEEDA3_LANE3 E10GBASER_PCS_SEEDB0_LANE0 E10GBASER_PCS_SEEDB0_LANE1 16-bit Hex E10GBASER_PCS_SEEDB0_LANE2 E10GBASER_PCS_SEEDB0_LANE3 E10GBASER_PCS_SEEDB1_LANE0 E10GBASER_PCS_SEEDB1_LANE1 16-bit Hex E10GBASER_PCS_SEEDB1_LANE2 E10GBASER_PCS_SEEDB1_LANE3 E10GBASER_PCS_SEEDB2_LANE0 E10GBASER_PCS_SEEDB2_LANE1 16-bit Hex E10GBASER_PCS_SEEDB2_LANE2 E10GBASER_PCS_SEEDB2_LANE3 E10GBASER_PCS_SEEDB3_LANE0 E10GBASER_PCS_SEEDB3_LANE1 16-bit Hex E10GBASER_PCS_SEEDB3_LANE2 E10GBASER_PCS_SEEDB3_LANE3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 23 16-bit Hex LANE_PWR_CTRL_LANE2 LANE_PWR_CTRL_LANE3 LNK_TRN_CFG_LANE0 LNK_TRN_CFG_LANE1 16-bit Hex LNK_TRN_CFG_LANE2 LNK_TRN_CFG_LANE3 LNK_TRN_COEFF_REQ_LANE0 LNK_TRN_COEFF_REQ_LANE1 16-bit Hex LNK_TRN_COEFF_REQ_LANE2 LNK_TRN_COEFF_REQ_LANE3 MISC_CFG 16-bit Hex MODE_CFG1 16-bit Hex MODE_CFG2 16-bit Hex MODE_CFG3 16-bit Hex Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 24 16-bit Hex PCS_CTRL2_LANE2 PCS_CTRL2_LANE3 PCS_MISC_CFG_0_LANE0 PCS_MISC_CFG_0_LANE1 16-bit Hex PCS_MISC_CFG_0_LANE2 PCS_MISC_CFG_0_LANE3 PCS_MISC_CFG_1_LANE0 PCS_MISC_CFG_1_LANE1 16-bit Hex PCS_MISC_CFG_1_LANE2 PCS_MISC_CFG_1_LANE3 PCS_MODE_LANE0 PCS_MODE_LANE1 16-bit Hex PCS_MODE_LANE2 PCS_MODE_LANE3 PCS_RESET_LANE0 PCS_RESET_LANE1 16-bit Hex PCS_RESET_LANE2 PCS_RESET_LANE3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 25 16-bit Hex PMA_CTRL2_LANE2 PMA_CTRL2_LANE3 PMA_LPBK_CTRL_LANE0 PMA_LPBK_CTRL_LANE1 16-bit Hex PMA_LPBK_CTRL_LANE2 PMA_LPBK_CTRL_LANE3 PRBS_BER_CFG0_LANE0 PRBS_BER_CFG0_LANE1 16-bit Hex PRBS_BER_CFG0_LANE2 PRBS_BER_CFG0_LANE3 PRBS_BER_CFG1_LANE0 PRBS_BER_CFG1_LANE1 16-bit Hex PRBS_BER_CFG1_LANE2 PRBS_BER_CFG1_LANE3 PRBS_CFG_LANE0 PRBS_CFG_LANE1 16-bit Hex PRBS_CFG_LANE2 PRBS_CFG_LANE3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 26 16-bit Hex RX_AGC_CTRL_LANE2 RX_AGC_CTRL_LANE3 RX_CDR_CTRL0_LANE0 RX_CDR_CTRL0_LANE1 16-bit Hex RX_CDR_CTRL0_LANE2 RX_CDR_CTRL0_LANE3 RX_CDR_CTRL1_LANE0 RX_CDR_CTRL1_LANE1 16-bit Hex RX_CDR_CTRL1_LANE2 RX_CDR_CTRL1_LANE3 RX_CDR_CTRL2_LANE0 RX_CDR_CTRL2_LANE1 16-bit Hex RX_CDR_CTRL2_LANE2 RX_CDR_CTRL2_LANE3 RX_CFG0_LANE0 RX_CFG0_LANE1 16-bit Hex RX_CFG0_LANE2 RX_CFG0_LANE3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 27 RX_FABRIC_WIDTH3 RX_LOOP_CTRL_LANE0 RX_LOOP_CTRL_LANE1 16-bit Hex RX_LOOP_CTRL_LANE2 RX_LOOP_CTRL_LANE3 RX_MVAL0_LANE0 RX_MVAL0_LANE1 16-bit Hex RX_MVAL0_LANE2 RX_MVAL0_LANE3 RX_MVAL1_LANE0 RX_MVAL1_LANE1 16-bit Hex RX_MVAL1_LANE2 RX_MVAL1_LANE3 RX_P0_CTRL 16-bit Hex RX_P0S_CTRL 16-bit Hex RX_P1_CTRL 16-bit Hex Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 28 16-bit Hex TERM_CTRL_LANE2 TERM_CTRL_LANE3 TX_CFG0_LANE0 TX_CFG0_LANE1 16-bit Hex TX_CFG0_LANE2 TX_CFG0_LANE3 TX_CFG1_LANE0 TX_CFG1_LANE1 16-bit Hex TX_CFG1_LANE2 TX_CFG1_LANE3 TX_CFG2_LANE0 TX_CFG2_LANE1 16-bit Hex TX_CFG2_LANE2 TX_CFG2_LANE3 TX_CLK_SEL0_LANE0 TX_CLK_SEL0_LANE1 16-bit Hex TX_CLK_SEL0_LANE2 TX_CLK_SEL0_LANE3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 29 TX_DISABLE_LANE1 16-bit Hex TX_DISABLE_LANE2 TX_DISABLE_LANE3 TX_FABRIC_WIDTH0 TX_FABRIC_WIDTH1 Integer TX_FABRIC_WIDTH2 TX_FABRIC_WIDTH3 TX_P0P0S_CTRL 16-bit Hex TX_P1P2_CTRL 16-bit Hex TX_PREEMPH_LANE0 TX_PREEMPH_LANE1 16-bit Hex TX_PREEMPH_LANE2 TX_PREEMPH_LANE3 TX_PWR_RATE_OVRD_LANE0 TX_PWR_RATE_OVRD_LANE1 16-bit Hex TX_PWR_RATE_OVRD_LANE2 TX_PWR_RATE_OVRD_LANE3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 30: Virtex-6 Fpga Gth Transceiver Wizard

Chapter 1: Transceiver and Tool Overview Virtex-6 FPGA GTH Transceiver Wizard The Virtex-6 FPGA GTH Transceiver Wizard is the preferred tool to generate a wrapper to instantiate a GTH transceiver primitive called GTHE1_QUAD. The Wizard can be found in the CORE Generator tool. The user is recommended to download the most up-to-date IP update before using the Wizard. -

Page 31: Simulation

The default for this attribute is 1.0. Implementation Functional Description This section provides the information needed to map Virtex-6 FPGA GTH transceivers instantiated in a design to device resources, including: • The location of the GTH transceiver on the available device and package combinations. - Page 32 GTH Quads located on both the left column (X0) and right column (X1) of the die. There are two ways to create a UCF for designs that use the GTH transceiver. The preferred method is to use the Virtex-6 FPGA GTH Transceiver Wizard (see Virtex-6 FPGA GTH Transceiver Wizard, page 30).

-

Page 33: Ff1155 Package Diagrams

MGTTXP2_118 MGTTXN2_118 HX255T: GTHE1_QUAD_X1Y2 MGTREFCLKP_118 HX380T: GTHE1_QUAD_X1Y2 MGTREFCLKN_118 MGTRXP1_118 MGTRXN1_118 MGTTXP1_118 MGTTXN1_118 MGTRXP0_118 MGTRXN0_118 MGTTXP0_118 MGTTXN0_118 UG371_C1_04_080609 Figure 1-4: Placement Diagram for the FF1155 Package (1 of 3) Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 34 MGTTXP2_117 MGTTXN2_117 HX255T: GTHE1_QUAD_X1Y1 MGTREFCLKP_117 HX380T: GTHE1_QUAD_X1Y1 MGTREFCLKN_117 MGTRXP1_117 MGTRXN1_117 MGTTXP1_117 MGTTXN1_117 MGTRXP0_117 MGTRXN0_117 MGTTXP0_117 MGTTXN0_117 UG371_C1_05_080609 Figure 1-5: Placement Diagram for the FF1155 Package (2 of 3) www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 35 MGTTXP2_116 MGTTXN2_116 HX255T: GTHE1_QUAD_X1Y0 MGTREFCLKP_116 HX380T: GTHE1_QUAD_X1Y0 MGTREFCLKN_116 MGTRXP1_116 MGTRXN1_116 MGTTXP1_116 MGTTXN1_116 MGTRXP0_116 MGTRXN0_116 MGTTXP0_116 MGTTXN0_116 UG371_C1_06_080609 Figure 1-6: Placement Diagram for the FF1155 Package (3 of 3) Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 36: Ff1923 And Ff1924 Package Diagrams

MGTRXN0_118 MGTTXP0_118 MGTTXN0_118 UG371_C1_07_080609 Figure 1-7: Placement Diagram for the FF1923 and FF1924 Packages (1 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 37 MGTRXN0_117 MGTTXP0_117 MGTTXN0_117 UG371_C1_08_080609 Figure 1-8: Placement Diagram for the FF1923 and FF1924 Packages (2 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 38 MGTRXN0_116 MGTTXP0_116 MGTTXN0_116 UG371_C1_09_080609 Figure 1-9: Placement Diagram for the FF1923 and FF1924 Packages (3 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 39 MGTRXN0_108 MGTTXP0_108 MGTTXN0_108 UG371_C1_10_080609 Figure 1-10: Placement Diagram for the FF1923 and FF1924 Packages (4 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 40 MGTRXN0_107 MGTTXP0_107 MGTTXN0_107 UG371_C1_11_080609 Figure 1-11: Placement Diagram for the FF1923 and FF1924 Packages (5 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 41 MGTRXN0_106 MGTTXP0_106 MGTTXN0_106 UG371_C1_12_080609 Figure 1-12: Placement Diagram for the FF1923 and FF1924 Packages (6 of 6) Note: The XC6VHX255T device is available only in the FF1923 package. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 42 Chapter 1: Transceiver and Tool Overview www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 43: Chapter 2: Shared Transceiver Features

IBUFDS_GTHE1 primitives are mapped to the respective GTHE1_QUAD primitive. X-Ref Target - Figure 2-1 MGTHAVCCPLL_[L,R] MGTHAVCCRX_[L,R] pll_refclk_term_b Nominal 50Ω MGTREFCLKP Nominal 50Ω MGTHAVCCPLL_[L,R] MGTREFCLKN UG371_c2_14_120809 Figure 2-1: Reference Clock Input Structure Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 44: Ports And Attributes

The reference clock is always used in an AC-coupled mode. The recommended value for the AC-coupling capacitors is 100 nF. The LVPECL clock must be used to drive the reference clock pins. Refer to DS152, Virtex-6 FPGA Data Sheet: DC and Switching Characteristics for electrical and switching specifications. -

Page 45: Reference Clock Distribution And Selection

(must be connected through a BUFG) and can be used to clock FPGA logic. This port can also connect directly to an MMCM or BUFR. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 46: Clocking From An External Source

GTH Quad to clock one neighbor above and one neighbor below. A GTH Quad shares its clock with its neighbors using the dedicated clock routing resources. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 47 The reference clock cannot be shared with a neighboring GTX transceiver. The maximum number of GTH transceivers that can be sourced by a single clock pin pair is 12. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 48: Pll

PLL architecture. A low phase noise PLL input clock is recommended for optimal jitter performance. The feedback divider determines the VCO multiplication and the PLL output frequency. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 49 Figure 2-4: PLL Block Diagram The feedback divider value (M), part of the PLL_CFG0 attribute, is set by the Virtex-6 FPGA GTH Transceiver Wizard. The TX output lane divider (D ) is set by the TXRATE port, and the RX output lane divider (D ) is set by the RXRATE ports.

- Page 50 PCS clock for the each lane. The FABRIC_WIDTH attributes need to have correct values to get the correct TXUSERCLKOUT and RXUSERCLKOUT values, depending on the ratio between the FPGA logic data bus width and internal data bus width. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 51 RX PCS Clock for Lane 3 RXUSERCLK3 CDR3 Divider 3 Clock Divider PMA Block Lane 3 SIPO_Data_Width3 UG371_c2_16_020210 Figure 2-5: TX and RX Parallel Clock Dividers in the PCS Block Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 52: Ports And Attributes

GTHINITDONE is driven High and TXUSERCLKIN<n> is stable. This port is not asserted until all internal clocks for the RX datapath, including the PLL output clock, are stable. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 53 TXRATE2[1:0] TXUSERCLKIN2 10: 1/4 data rate TXRATE3[1:0] TXUSERCLKIN3 All other encodings are reserved. This port must always be set to 2'b00 during initialization and when GTHRESET is asserted. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 54 “40” (DRP value 3'b101): PCS to Fabric 1:2 40 bit “64” (DRP value 3'b010): PCS to Fabric 1:4 64 bit “80” (DRP value 3'b110): PCS to Fabric 1:4 80 bit “6466” (DRP value 3'b111): 64B/66B mode www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 55: Pll Settings For The Common Protocol

DCLK must always be provided to the GTHE1_QUAD primitive even if the DRP or management interface is not used. Note: DCLK must be sourced from a free-running clock. It cannot be sourced from TSTREFCLKOUT or TSTREFCLKFAB of the GTH Quad. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 56: Ports And Attributes

Figure 4-5, page 136). Both the internal RX clock and RXBUFRESET1 RXUSERCLKIN1 RXUSERCLKIN<n> must be stable before a reset can be RXBUFRESET2 RXUSERCLKIN2 applied to the buffer. RXBUFRESET3 RXUSERCLKIN3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 57 TXRATE<n>, SAMPLERATE<n>, and TXCTRLACK1 TXUSERCLKIN1 TXPOWERDOWN<n>. TXCTRLACK2 TXUSERCLKIN2 The state of this port is valid only after the GTHINITDONE TXCTRLACK3 TXUSERCLKIN3 is driven High and TXUSERCLKIN<n> is stable. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 58 It is a buffered version of the TXUSERCLKIN1 TXUSERCLKOUT<n>. TXUSERCLKIN2 This clock must be stable for RXCTRLACK<n> and TXUSERCLKIN3 RXRATE<n> ports to be active. Notes: 1. <n> denotes lane 0, 1, 2, or 3. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 59 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 60: Gth Quad Initialization In Response To Completion Of Configuration

[1]: Reset RX loopback FIFO [0]: Reset 64B/66B and PRBS TX FIFO PCS_RESET_1_LANE0 16-bit Hex [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_RESET_1_LANE1 [1:0]: These bits control the datapath resets. They vary by mode:... - Page 61 Pulse TXBUFRESET for one TXUSERCLKIN clock cycle. 10. Change TXPOWERDOWN<n>[1:0] to 2'b00 to power up the transmitter logic. 11. Wait for TXCTRLACK<n> to go High. The transmitter is ready for normal operation. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 62: Gth Quad Reset In Response To Gthreset

Set PCS_RESET_1_LANE<n> to the datapath mode used in the application. Set TXPOWERDOWN<n>[1:0] and RXPOWERDOWN<n>[1:0] to 2'b10. Assert GTHRESET for 1 DCLK clock cycle. The TXCTRLACK<n> and RXCTRLACK<n> ports from all four lanes are asserted. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 63 Set PCS_RESET_LANE<n> to the datapath mode used in the application. Set PCS_RESET_1_LANE<n> to the datapath mode used in the application. Set TXPOWERDOWN<n>[1:0] and RXPOWERDOWN<n>[1:0] to 2'b10. Set TXRATE<n>[1:0] and RXRATE<n>[1:0] to 2'b00, and set SAMPLERATE<n>[2:0] to 3'b000. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 64 Quad. The user must wait for all four TXCTRLACK<n> and RXCTRLACK<n> signals to be deasserted before asserting GTHINIT. The TXCTRLACK<n> and RXCTRLACK<n> signals can be High for more than 1 DCLK clock cycle. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 65: Resetting The Transmit Datapath

G 3 7 1 _ c 2 _ 0 8 _ 0 8 0 8 0 9 Figure 2-11: GTH Reset for the Receive Datapath Note relevant to Figure 2-11: The RXCTRLACK<n> signal can be High for more than 1 DCLK clock cycle. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 66: Power Down

This port must always be set to 2'b10 during initialization and when GTHRESET is asserted. If the Quad is configured as a x4 link, only the port from Lane 0 is valid. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 67: Using Power Down

PMA. Figure 2-12 shows the Far-end loopback datapath. X-Ref Target - Figure 2-12 Serializer TXN/TXP Buffer Deserializer RXN/RXP Buffer UG371_c2_09_020510 Figure 2-12: Far-end Loopback Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 68: Near-End Pcs Loopback

X-Ref Target - Figure 2-14 Pre-emphasis Serializer TXDATA TXN/TXP Buffer PRBS Serial Generator Loopback Deserializer RXDATA Buffer RXN/RXP PRBS Checker Linear EQ UG371_c2_11_120109 Figure 2-14: Near-end PMA Loopback www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 69: Ports And Attributes

Description PMA_LPBK_CTRL_LANE0 16-bit Hex This attribute configures the PMA loopback mode. PMA_LPBK_CTRL_LANE1 [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PMA_LPBK_CTRL_LANE2 [1:0]: Configure the source of the on-chip loopback connection to the RX: PMA_LPBK_CTRL_LANE3 2’b00: User loopback disabled 2’b01: TX output... -

Page 70: Dynamic Reconfiguration Port

(DRDY) are the control signals that implement read and write operations, indicate operation completion, or indicate the availability of data. Refer to UG360, Virtex-6 FPGA Configuration User Guide for detailed descriptions and timing diagrams of the DRP operations. -

Page 71: Management Interface

This input is the management interface write request valid signal. MGMTPCSWRDATA[15:0] DCLK This input bus is the management interface register write data bus. There are no management interface attributes. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 72: Using The Management Interface

A read operation can be requested right after the acknowledgment indicator signal as shown in Event 1 of Figure 2-15. No read or write operation can be requested prior to the acknowledgment indicator signal. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 73 The management interface supports multiple write accesses by asserting the MGMTPCSREGWR signal as shown in Event 1 of Figure 2-16. Multiple MGMTPCSLANESEL[3:0] signals can be asserted simultaneously for a write access. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 74 Chapter 2: Shared Transceiver Features www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 75: Fpga Tx Interface

• 64 bits 64B/66B mode • 64 bits Raw mode • 16 bits • 20 bits • 32 bits • 40 bits • 64 bits • 80 bits Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 76 16 bits 1010 16 bits 32 bits 1010 16 bits 64 bits 1010 20 bits 20 bits 1011 20 bits 40 bits 1011 20 bits 80 bits 1011 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 77 The data mode must be the same for both the transmitter and receiver within a GTH lane. • The data mode must be the same on all four GTH lanes within a Quad. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 78: Ports And Attributes

This port is the transmit parallel clock output based on the transmitter data bus width, TXRATE<n>, and TXUSERCLKOUT1 SAMPLERATE<n>. This clock is used to drive TXUSERCLKOUT2 TXUSERCLKIN<n> through a buffer. TXUSERCLKOUT3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 79 “16” or “20” (DRP value 3'b000): 4’b0001 “32” (DRP value 3'b011): 4’b0000 “40” (DRP value 3'b101): 4’b0000 “64” (DRP value 3'b010): 4’b0000 “80” (DRP value 3'b110): 4’b0000 “6466” (DRP value 3'b111): 4’b0001 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 80 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 81: Transmit Clocking

• The transmitter cannot use the same clock as the receiver; that is, TXUSERCLKIN and RXUSERCLKIN cannot be sourced from the same clock. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 82: Configuring The Transmitter For Multi-Lane Applications

Raw mode: These inputs are used as part of TXDATA<n>[71:64]. TXDATA0[63:0] TXUSERCLKIN0 This input bus is the transmit data bus of the transmit interface from the FPGA. TXDATA1[63:0] TXUSERCLKIN1 TXDATA2[63:0] TXUSERCLKIN2 TXDATA3[63:0] TXUSERCLKIN3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 83 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 84 ” 64 ” (DRP value 3'b010): PCS to Fabric 1:4 64 bits ” 80 ” (DRP value 3'b110): PCS to Fabric 1:4 80 bits ” 6466 ” (DRP value 3'b111): 64B/66B mode www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 85: Enabling 8B/10B Mode

The 8B/10B table includes special characters (K characters) that are often used for control functions. To transmit TXDATA as a K character instead of regular data, the TXCTRL port must be driven High. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 86: Tx 64B/66B Block

Raw mode: These inputs are used as part of TXDATA<n>[71:64]. TXDATA0[63:0] TXUSERCLKIN0 This input bus is the transmit data bus of the transmit interface from the FPGA. TXDATA1[63:0] TXUSERCLKIN1 TXDATA2[63:0] TXUSERCLKIN2 TXDATA3[63:0] TXUSERCLKIN3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 87 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 88 ” 80 ” (DRP value 3'b110): PCS to Fabric 1:4 80 bits ” 6466 ” (DRP value 3'b111): 64B/66B mode “ 6466. ” The default for these attributes is www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 89: Enabling 64B/66B Mode

This input bus is the transmit data bus of the transmit interface from the FPGA. TXDATA1[63:0] TXUSERCLKIN1 TXDATA2[63:0] TXUSERCLKIN2 TXDATA3[63:0] TXUSERCLKIN3 TXDATAMSB0[7:0] TXUSERCLKIN0 This bus extends the transmit data bus as TXDATA<n>[79:72]. TXDATAMSB1[7:0] TXUSERCLKIN1 TXDATAMSB2[7:0] TXUSERCLKIN2 TXDATAMSB3[7:0] TXUSERCLKIN3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 90 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 91 [2]: Reset TX FIFO [1]: Reset RX loopback FIFO [0]: Reserved PCS_RESET_1_LANE0 16-bit Hex [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_RESET_1_LANE1 [1:0]: This attribute controls the datapath resets. It varies by mode: PCS_RESET_1_LANE2...

-

Page 92: Enabling Raw Mode

If the transmit fabric data width is configured to 20 bits, 40 bits, or 80 bits Set PCS_MODE_LANE<n>[3:0] to 4'b1011. b. Set PCS_RESET_LANE<n> to 0xFF3B. Set PCS_RESET_1_LANE<n>[1:0] to 2'b00. d. Set TX_FABRIC_WIDTH<n> to “20”, “40”, or “80.” www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 93: Tx Pattern Generator

TX pattern generator attributes. Table 3-12: TX Pattern Generator Attributes Attribute Type Description PRBS_CFG_LANE0 16-bit Hex [15:4]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PRBS_CFG_LANE1 [3:2]: PRBS generate width PRBS_CFG_LANE2 2'b11: 20b PRBS_CFG_LANE3... - Page 94 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 95 [2]: Reset TX FIFO [1]: Reset RX loopback FIFO [0]: Reserved PCS_RESET_1_LANE0 16-bit Hex [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_RESET_1_LANE1 [1:0]: This attribute controls the datapath resets. It varies by mode: PCS_RESET_1_LANE2...

-

Page 96: Tx Polarity Control

• PCS_MISC_CFG_0_LANE2: 0x5201 • PCS_MISC_CFG_0_LANE3: 0x5301 • Management Interface Address: 0x8001 with MMD Address 0x03 • Use the Lane Address setting to specify which GTH lane to access www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 97: Tx Configurable Driver

Differential zero: TXP is held Low; TXN is held High. • During configuration Differential zero: TXP is held Low; TXN is held High. • Reset Differential zero: TXP is held Low; TXN is held High. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 98: Ports And Attributes

TXN2 primitive. These ports represent pads. TXN3 The location of these ports must be constrained and brought to the top TXP0 level of the design. TXP1 TXP2 TXP3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 99 0x0025 0101 0x002D 0110 0x0035 0111 0x003D 1000 0x0045 1001 0x004D 1010 0x0055 1000 1011 0x005D 1050 1100 0x0065 1100 1101 0x006D 1150 1110 0x0075 1200 1111 0x007D Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 100: Setting The Tx Driver

Table 3-15 for voltage swing control settings) Post-Cursor Emphasis The override bit has to be set as specified: • TX_CFG1_LANE<n>[8] = tx_premptap_ovrrd_en = 1'b1 • TX_PREEMPH_LANE<n>[7:4] = tx_postcursor www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 101: Pre-Cursor Emphasis

4'd11 1000 – – – – 4'b1011 4'd0 4'd5 4'd11 1100 – – – – 4'b1101 4'd0 4'd7 4'd13 1200 – – – – 4'b1111 4'd0 4'd7 4'd15 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 102 Chapter 3: Transmitter www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 103 RX Pattern Checker, page 112 • RX Raw Mode, page 117 • RX 64B/66B Block, page 122 • RX 8B/10B Block, page 126 • FPGA RX Interface, page 130 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 104: Chapter 4: Receiver

(configuration the maximum voltage value ongoing and of the RXP/RXN signals not complete) specified in DS152, Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 105: Ports And Attributes

The RX AFE is only to be used with external AC coupling capacitors. The recommended value for the AC coupling capacitor is 100 nF. For the maximum and minimum swing requirements, refer to DS152, Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. RX Equalization... -

Page 106: Ports And Attributes

Table 4-4: RX Equalization Ports Port Clock Domain Description DFETRAINCTRL0 DCLK When the DFE is enabled, asserting this pin overrides DFETRAINCTRL1 completion of the DFE training. DFETRAINCTRL2 DFETRAINCTRL3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 107 • Raw: If data encoding is similar to 64B/66B, use 13'h04C4. If data encoding is similar to 8B/10B, use 13'h03D0. RX_AEQ_VAL0_LANE0 16-bit Hex Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. RX_AEQ_VAL0_LANE1 RX_AEQ_VAL0_LANE2 RX_AEQ_VAL0_LANE3 RX_AEQ_VAL1_LANE0 16-bit Hex Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard.

-

Page 108: Setting The Rx Equalization

The DFE is auto-adapting but requires some training control parameters to be set. For modes that use the internal 8B/10B and PRBS blocks, DFE_TRAIN_CTRL_LANE<n>[15:13] = 100. For modes that use the internal 64B/66B blocks, DFE_TRAIN_CTRL_LANE<n>[15:13] = 001. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 109: Ctle

Figure 4-4 shows the CDR sampler positions. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 110: Ports And Attributes

Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. RX_CDR_CTRL2_LANE1 RX_CDR_CTRL2_LANE2 RX_CDR_CTRL2_LANE3 RX_LOOP_CTRL_LANE0 16-bit Hex Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. RX_LOOP_CTRL_LANE1 RX_LOOP_CTRL_LANE2 RX_LOOP_CTRL_LANE3 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 111: Rx Polarity Control

Type Description PCS_MISC_CFG_0_LANE0 16-bit Hex This attribute sets the polarity and PRBS configuration. PCS_MISC_CFG_0_LANE1 [15:12]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_MISC_CFG_0_LANE2 [11]: Invert TX polarity PCS_MISC_CFG_0_LANE3 [10]: RX polarity override enable [9]: RX polarity override value... -

Page 112: Rx Pattern Checker

The error and sample counters saturate when they reach the maximum value. In pattern check mode, data does not appear on RXDATA ports. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 113: Ports And Attributes

[8]: Reset the PRBS error counter when read [7]: Revert bit order of parallel data to serializer/deserializer TX [6]: Revert bit order of parallel data from serializer/deserializer RX [5:0]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com... - Page 114 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 16-bit 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 115 [15:4]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PRBS_CFG_LANE2 [3:2]: PRBS generate width PRBS_CFG_LANE3 2'b11: 20b 2'b10: 16b Others: Reserved [1:0]: PRBS checker width 2'b11: 20b 2'b10: 16b Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 116: Using Rx Pattern Checker

PRBS_TIMER_0_LANE2: 0x5204 • PRBS_TIMER_0_LANE3: 0x5304 • PRBS_TIMER_1_LANE0: 0x5005 • PRBS_TIMER_1_LANE1: 0x5105 • PRBS_TIMER_1_LANE2: 0x5205 • PRBS_TIMER_1_LANE3: 0x5305 • PRBS_TIMER_2_LANE0: 0x5006 • PRBS_TIMER_2_LANE1: 0x5106 • PRBS_TIMER_2_LANE2: 0x5206 • PRBS_TIMER_2_LANE3: 0x5306 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 117: Rx Raw Mode

RXCODEERR<n>[0] corresponds to RXDATA<n>[7:0] 64B/66B: RXCODEERR<n>[0] indicates a 64B/66B code error. RXCODEERR<n>[7:1] are not used for this mode. Raw mode: These outputs are used as part of RXDATA<n>[79:72]. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 118 RXSLIP3 position for the given receiver lane width. It wraps back to 0 after adjusting to the maximum alignment position. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 119 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 120 “ 64 ” (DRP value 3'b010): PCS to Fabric 1:4 64 bits “ 80 ” (DRP value 3'b110): PCS to Fabric 1:4 80 bits “ 6466 ” (DRP value 3'b111): 64B/66B mode www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 121: Enabling Raw Mode

RAW_SHIFT_MON_LANE1: 0x510E • RAW_SHIFT_MON_LANE2: 0x520E • RAW_SHIFT_MON_LANE3: 0x530E • Management Interface Address: 0x800E with MMD Address 0x03 Use the Lane Address setting to specify which GTH lane to access. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 122: Rx 64B/66B Block

RXCODEERR<n>[0] corresponds to RXDATA<n>[7:0] 64B/66B: RXCODEERR<n>[0] indicates a 64B/66B code error. RXCODEERR<n>[7:1] are not used for this mode. Raw mode: These outputs are used as part of RXDATA<n>[79:72]. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 123 Raw mode: These outputs are used as part of RXDATA<n>[71:64]. RXDATA0[63:0] RXUSERCLKIN0 This output bus is the receive data bus of the receive interface to the FPGA. RXDATA1[63:0] RXUSERCLKIN1 RXDATA2[63:0] RXUSERCLKIN2 RXDATA3[63:0] RXUSERCLKIN3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 124 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 125 [2]: Reset TX FIFO [1]: Reset RX loopback FIFO [0]: Reserved PCS_RESET_1_LANE0 16-bit Hex [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_RESET_1_LANE1 [1:0]: These bits control the datapath resets. They vary by mode: PCS_RESET_1_LANE2...

-

Page 126: Enabling 64B/66B Mode

RXCODEERR<n>[0] corresponds to RXDATA<n>[7:0] 64B/66B: RXCODEERR<n>[0] indicates a 64B/66B code error. RXCODEERR<n>[7:1] are not used for this mode. Raw mode: These outputs are used as part of RXDATA<n>[79:72]. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 127 RXVALID<n>[6] corresponds to RXDATA<n>[55:48] RXVALID3[7:0] RXUSERCLKIN3 RXVALID<n>[5] corresponds to RXDATA<n>[47:40] RXVALID<n>[4] corresponds to RXDATA<n>[39:32] RXVALID<n>[3] corresponds to RXDATA<n>[31:24] RXVALID<n>[2] corresponds to RXDATA<n>[23:16] RXVALID<n>[1] corresponds to RXDATA<n>[15:8] RXVALID<n>[0] corresponds to RXDATA<n>[7:0] Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 128 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 129 [2]: Reset TX FIFO [1]: Reset RX loopback FIFO [0]: Reserved PCS_RESET_1_LANE0 16-bit Hex [15:2]: Reserved. Use the recommended values from the Virtex-6 FPGA GTH Transceiver Wizard. PCS_RESET_1_LANE1 [1:0]: These bits control the datapath resets. They vary by mode: PCS_RESET_1_LANE2...

-

Page 130: Enabling 8B/10B Mode

RXDATA port, and whether or not 8B/10B mode is used. A block inside the PCS handles the mapping of the internal data width to the fabric data width selected in the design. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 131 The data mode must be the same for both the transmitter and receiver within a GTH lane. • The data mode must be the same on all four GTH lanes within a Quad. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 132: Ports And Attributes

RXCTRL<n>[2] corresponds to RXDATA<n>[23:16] RXCTRL<n>[1] corresponds to RXDATA<n>[15:8] RXCTRL<n>[0] corresponds to RXDATA<n>[7:0] 64B/66B: These outputs are 64B/66B control bits. Raw mode: These outputs are used as part of RXDATA<n>[71:64]. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... - Page 133 This output is the recovered clock based on the receiver data bus width and RXRATE<n>. This clock is used to drive RXUSERCLKOUT1 RXUSERCLKIN<n> through a buffer. RXUSERCLKOUT2 RXUSERCLKOUT3 Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

- Page 134 “16” or “20” (DRP value 3'b000): 4’b0001 “32” (DRP value 3'b011): 4’b0000 “40” (DRP value 3'b101): 4’b0000 “64” (DRP value 3'b010): 4’b0000 “80” (DRP value 3'b110): 4’b0000 “6466” (DRP value 3'b111): 4’b0001 www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

- Page 135 1011: 20-bit raw data 1100: PRBS Others: Reserved [3:0]: PCS TX mode 0000: Zero 0001: 64B/66B 0111: 8B/10B 1010: 16-bit raw data 1011: 20-bit raw data 1100: PRBS Others: Reserved Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 136: Receive Clocking

BUFG/BUFR. • The transmitter cannot use the same clock as the receiver; that is, TXUSERCLKIN and RXUSERCLKIN cannot be sourced from the same clock. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010... -

Page 137: Configuring The Receiver For Multi-Lane Applications

POWERDOWN ports. The POWERDOWN ports of all GTH lanes within a Quad in a x4 link should be driven by the same source. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 138 Chapter 4: Receiver www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

-

Page 139: Chapter 5: Board Design Guidelines

Refer to Termination Resistor Calibration Circuit. MGTHAVCC In (Pad) MGTHAVCC is an analog supply for internal circuits for the receiver and the transmitter. The nominal voltage is 1.1 V Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... - Page 140 Figure 5-1: Virtex-6 GTH Transceiver Power Supply Connections Notes relevant to Figure 5-1: The voltages shown are nominal values. Refer to DS152, Virtex-6 FPGA Data Sheet: DC and Switching Characteristics for values and tolerances. Capacitor symbols are representative. www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide...

-

Page 141: Termination Resistor Calibration Circuit

GTH transceiver analog power supplies (MGTHAVCC, MGTHAVCCRX, MGTHAVCCPLL, and MGTHAVTT) must be present and within the proper tolerance as specified in the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. For reliable operation of the RBIAS circuit, the connection between the RBIAS pin of the FPGA and the pin of the precision resistor must be less than 5 pF and the resistance must be less than 10Ω. -

Page 142: Gth Transceiver Reference Clock Checklist

• The differential voltage swing of the reference clock must have the range specified in the Virtex-6 FPGA Data Sheet: DC and Switching Characteristics. The nominal range is 500 mV–1600 mV and the nominal typical value is 800 mV. •... -

Page 143: Reference Clock Interface

To minimize noise and power consumption, external AC coupling capacitors between the sourcing oscillator and the GTH Quad dedicated clock reference clock input pins are required. Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010... -

Page 144: Unused Reference Clocks

This section discusses the GTH transceiver power supplies, the two main types of power supply regulators (linear and switching), and performance degradation due to crosstalk. Overview The Virtex-6 FPGA GTH Quad requires four analog power supplies: • MGTHAVCC, at a nominal voltage level of 1.1 V •... - Page 145 The disadvantages of the switching regulator are the complexity of the circuit and noise generated by the regulator switching function. Switching regulator circuits are usually more complex than linear regulator circuits. This shortcoming has recently been addressed Virtex-6 FPGA GTH Transceivers User Guide www.xilinx.com UG371 (v2.0) February 16, 2010...

-

Page 146: Crosstalk

SelectIO™ interface activity , it is important to have guidelines for SelectIO interface usage that minimize the impact on GTH transceiver performance. The pinout for the Virtex-6 FPGA package maintains a physical separation between the GTH transceiver pins and the SelectIO interface pins. Because of this separation in the package pinout, no SelectIO interface pins need to be excluded when using the GTH transceivers. - Page 147 SelectIO Interface Usage Guidelines Even though the Virtex-6 FPGA package pinout eliminates the crosstalk between the SelectIO interface and the GTH transceiver pins due to pin adjacency, it is still possible to induce crosstalk on the PCB. Therefore, when routing signals on the PCB: •...

- Page 148 Chapter 5: Board Design Guidelines www.xilinx.com Virtex-6 FPGA GTH Transceivers User Guide UG371 (v2.0) February 16, 2010...

Need help?

Do you have a question about the Virtex-6 FPGA and is the answer not in the manual?

Questions and answers