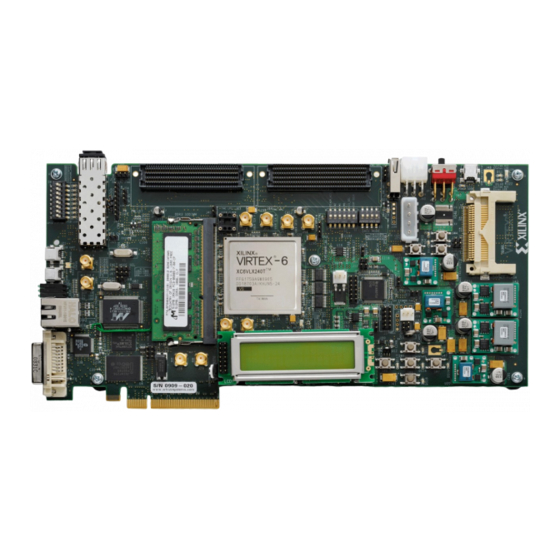

Xilinx Virtex-6 FPGA User Manual

Configurable logic block

Hide thumbs

Also See for Virtex-6 FPGA:

- Manual (381 pages) ,

- User manual (317 pages) ,

- Getting started manual (77 pages)

Summary of Contents for Xilinx Virtex-6 FPGA

- Page 1 Virtex-6 FPGA Configurable Logic Block User Guide UG364 (v1.2) February 3, 2012 www.BDTIC.com/XILINX...

-

Page 2: Revision History

(including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. -

Page 3: Table Of Contents

Carry Chain Primitive ........... . . 49 www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com... - Page 4 Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

-

Page 5: Preface: About This Guide

Virtex-6 Family Overview The features and product selection of the Virtex-6 family are outlined in this overview. • Virtex-6 FPGA Data Sheet: DC and Switching Characteristics This data sheet contains the DC and Switching Characteristic specifications for the Virtex-6 family. -

Page 6: Additional Support Resources

PCB and interface level. Additional Support Resources To search the database of silicon and software questions and answers or to create a technical support case in WebCase, see the Xilinx website at: http://www.xilinx.com/support. www.BDTIC.com/XILINX www.xilinx.com... -

Page 7: Virtex-6 Fpga Clb

Figure 1: Arrangement of Slices within the CLB The Xilinx tools designate slices with the following definitions. An “X” followed by a number identifies the position of each slice in a pair as well as the column position of the slice. -

Page 8: Slice Description

Each CLB can contain zero or one SLICEM. Every other CLB column contains a SLICEMs. In addition, the two CLB columns to the left of the DSP48E columns both contain a SLICEL and a SLICEM. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012... - Page 9 A6:A1 W6:W1 FF/LAT INIT1 INIT0 SRHI SRLO MC31 SRHI SRLO INIT1 INIT0 AMUX A6:1 A6:A1 W6:W1 FF/LAT INIT1 INIT0 SRHI SRLO MC31 ug364_03_040209 Figure 3: Diagram of SLICEM www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 10 INIT1 INIT0 BMUX B6:1 A6:A1 FF/LAT INIT1 INIT0 SRHI SRLO SRHI SRLO INIT1 INIT0 AMUX A6:1 A6:A1 FF/LAT INIT1 INIT0 SRHI SRLO ug364_04_040209 Figure 4: Diagram of SLICEL www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 11 Distributed RAM Shift Registers Carry Chains 256 bits 128 bits Notes: 1. SLICEM only, SLICEL does not have distributed RAM or shift registers. Table 2: Virtex-6 FPGA Logic Resources Available in All CLBs Total Number of Maximum Shift Number of Device...

- Page 12 SRVAL Function SRLOW (default) No Logic Change SRLOW (default) SRHIGH No Logic Change SRHIGH Figure 5 shows both the register only and the register/latch configuration in a slice. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 13 • No set or reset • Synchronous set • Synchronous reset • Asynchronous set (preset) • Asynchronous reset (clear) www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 14 32 x 1S 32 x 1D 32 x 2Q 32 x 6SDP 64 x 1S 64 x 1D 64 x 1Q 64 x 3SDP 128 x 1S 128 x 1D www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 15 RAM configurations occupying one SLICEM. When using x2 configuration (RAM32X2Q), A6 and WA6 are driven High by the software to keep O5 and O6 independent. www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 16 (WE) DPRAM32 DOC[0] C[5:1] ADDRC[4:0] A[6:1] WA[6:1] DOC[1] DPRAM32 DOB[0] B[5:1] ADDRB[4:0] A[6:1] WA[6:1] DOB[1] DPRAM32 DOA[0] A[5:1] ADDRA[4:0] A[6:1] WA[6:1] DOA[1] ug364_06_080609 Figure 6: Distributed RAM (RAM32X2Q) www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 17 A[6:1] RADDR[6] = 1 WA[6:1] O[1] DPRAM32 DATA[3] O[4] DATA[4] B[5:1] A[6:1] WA[6:1] O[3] DPRAM32 DATA[5] O[6] DATA[6] A[5:1] A[6:1] WA[6:1] O[5] ug364_07_080609 Figure 7: Distributed RAM (RAM32X6SDP) www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 18 SLICEM, as long as they share the same clock, write enable, and shared read and write port address inputs. This configuration equates to 64 x 2-bit dual-port distributed RAM. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 19 ADDRC A[6:1] Registered Output WA[6:1] (Optional) DPRAM64 (B[6:1]) Registered ADDRB A[6:1] Output WA[6:1] (Optional) DPRAM64 (A[6:1]) Registered ADDRA A[6:1] Output WA[6:1] (Optional) ug364_10_080609 Figure 10: Distributed RAM (RAM64X1Q) www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 20 A[6:1] WA[6:1] ug364_11_080609 Figure 11: Distributed RAM (RAM64X3SDP) Implementation of distributed RAM configurations with depth greater than 64 requires the usage of wide-function multiplexers (F7AMUX, F7BMUX, and F8MUX). www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 21 SLICEM, as long as they share the same clock, write enable, and shared read and write port address inputs. This configuration equates to 128 x 2-bit single-port distributed RAM. www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 22 WA[7:1] (CLK) WCLK (WE) Registered DPRAM64 F7BMUX Output (Optional) A[6:1] WA[7:1] DPRAM64 DPRA[6:0] A[6:1] WA[7:1] Registered DPRAM64 F7AMUX Output (Optional) A[6:1] WA[7:1] ug364_13_080609 Figure 13: Distributed RAM (RAM128X1D) www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 23 The synchronous write operation is a single clock-edge operation with an active-High write-enable (WE) feature. When WE is High, the input (D) is loaded into the memory location at address A. Asynchronous Read Operation www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 24 (less than 32 bits). For example, when building a 13-bit shift register, simply set the address to the 13 bit. Figure 15 is a logic block diagram of a 32-bit shift register. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 25 SHIFTOUT(Q31) Address (A[4:0]) ug364_16_040209 Figure 16: Representation of a Shift Register Figure 17 shows two 16-bit shift registers. The example shown can be implemented in a single LUT. www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 26 SHIFTIN (D) A[5:0] A[6:2] A5 (AX) MC31 (CLK) (WE/CE) Output (Q) (AQ) Registered SRL32 F7AMUX Output (Optional) (MC31) A[6:2] MC31 SHIFTOUT (Q63) ug364_18_040209 Figure 18: 64-bit Shift Register Configuration www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 27 BX (A6) (CLK) (WE/CE) (BMUX) Output (Q) (BQ) Registered F8MUX Output (Optional) SRL32 A[6:2] MC31 AX (A5) SRL32 Not Used F7AMUX A[6:2] UG364_19_012509 Figure 19: 96-bit Shift Register Configuration www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 28 The Q output is determined by the 5-bit address. Each time a new address is applied to the 5-input address pins, the new bit position value is available on the Q output after the time www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 29 Each LUT can be configured into a 4:1 MUX. The 4:1 MUX can be implemented with a flip- flop in the same slice. Up to four 4:1 MUXes can be implemented in a slice, as shown in Figure www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 30 LUTs to form a combinatorial function up to 13 inputs (or an 8:1 MUX). Up to two 8:1 MUXes can be implemented in a slice, as shown in Figure www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 31 Each slice has an F8MUX. F8MUX combines the outputs of F7AMUX and F7BMUX to form a combinatorial function up to 27 inputs (or a 16:1 MUX). Only one 16:1 MUX can be implemented in a slice, as shown in Figure www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 32 However, there are no direct connections between slices to form these wide multiplexers. Fast Lookahead Carry Logic In addition to function generators, dedicated carry logic is provided to perform fast arithmetic addition and subtraction in a slice. A Virtex-6 FPGA CLB has two separate carry chains, as shown in Figure 1.

- Page 33 The CIN input is used to cascade slices to form a longer carry chain. The O outputs contain the sum of the addition/subtraction. The CO outputs compute the carry out for www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

-

Page 34: Clb / Slice Timing Models

Most of the timing parameters found in the section on switching characteristics are described in this chapter. All timing parameters reported in the Virtex-6 FPGA Data Sheet are associated with slices and CLBs. The following sections correspond to specific switching characteristics sections in the Virtex-6 FPGA Data Sheet: •... - Page 35 CLB / Slice Timing Models X-Ref Target - Figure 25 Inputs DMUX FF/LAT F7BMUX Inputs CMUX FF/LAT F8MUX Inputs BMUX FF/LAT F7AMUX Inputs AMUX FF/LAT ug364_25_040209 Figure 25: Simplified Virtex-6 FPGA Slice www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 36 Time before/after the CLK that the SR (Set/Reset) SRCK CKSR element of the slice must be stable at the SR inputs of the slice sequential elements (configured as a flip- flop). www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

- Page 37 = Setup Time (before clock edge), and T = Hold Time (after clock edge). XXCK CKXX Timing Characteristics Figure 26 illustrates the general timing characteristics of a Virtex-6 FPGA slice. X-Ref Target - Figure 26 DICK AX/BX/CX/DX (DATA) SRCK SR (RESET)

-

Page 38: Slice Distributed Ram Timing Model And Parameters (Available In Slicem Only)

Slice Distributed RAM Timing Model and Parameters (Available in SLICEM only) Figure 27 illustrates the details of distributed RAM implemented in a Virtex-6 FPGA slice. Some elements of the slice are omitted for clarity. Only the elements relevant to the timing paths described in this section are shown. - Page 39 2. T = Setup Time (before clock edge), and T = Hold Time (after clock edge). XXCK CKXX 3. Parameter includes AX/BX/CX/DX configured as a data input (DI2). www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

- Page 40 CLB / Slice Timing Models Distributed RAM Timing Characteristics The timing characteristics of a 16-bit distributed RAM implemented in a Virtex-6 FPGA slice (LUT configured as RAM) are shown in Figure X-Ref Target - Figure 28 A/B/C/D (ADDR) AI/BI/CI/DI (DI)

-

Page 41: Slice Srl Timing Model And Parameters (Available In Slicem Only)

Slice SRL Timing Model and Parameters (Available in SLICEM only) Figure 29 illustrates shift register implementation in a Virtex-6 FPGA slice. Some elements of the slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown. - Page 42 3. Parameter includes AX/BX/CX/DX configured as a data input (DI2) or two bits with a common shift. Slice SRL Timing Characteristics Figure 30 illustrates the timing characteristics of a 16-bit shift register implemented in a Virtex-6 FPGA slice (a LUT configured as an SRL). X-Ref Target - Figure 30 Write Enable (WE)

- Page 43 DMUX output of the slice via the MC31 output of LUT A (SRL). This is also applicable to the AMUX, BMUX, CMUX, DMUX, and COUT outputs at time T after clock event 1. WOSCO www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012...

-

Page 44: Slice Carry-Chain Timing Model And Parameters

Slice Carry-Chain Timing Model and Parameters Figure 24, page 33 illustrates a carry chain in a Virtex-6 FPGA slice. Some elements of the slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown. -

Page 45: Clb Primitives

The input and output data are 1-bit wide (with the exception of the 32-bit RAM). Figure 32 shows generic single-port, dual-port, and quad-port distributed RAM primitives. The A, ADDR, and DPRA signals are address buses. www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012... - Page 46 Following an active write clock edge, the data out (O, SPO, or DOD[#:0]) reflects the newly written data. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

-

Page 47: Shift Registers (Srls) Primitive

The address input selects the bit (range 0 to 31) to be read. The nth bit is available on the output pin (Q). Address inputs have no effect on the cascadable output pin (Q31). It is always the last bit of the shift register (bit 31). www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012... -

Page 48: Other Shift Register Applications

(address tied to 0b00110) and a flip-flop can be used as the last register. (In an SRLC32E primitive, the shift register length is the address input + 1). www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012... -

Page 49: Multiplexer Primitives

This primitive works in conjunction with LUTs in order to build adders and multipliers. This primitive is generally inferred by synthesis tools from standard RTL code. The synthesis tool can identify the arithmetic and/or logic functionality that best maps to this www.BDTIC.com/XILINX Virtex-6 FPGA CLB User Guide www.xilinx.com UG364 (v1.2) February 3, 2012... - Page 50 The carry in input is used to cascade slices to form longer carry chain. To create a longer carry chain, the CO[3] output of another CARRY4 is simply connected to this pin. www.BDTIC.com/XILINX www.xilinx.com Virtex-6 FPGA CLB User Guide UG364 (v1.2) February 3, 2012...

Need help?

Do you have a question about the Virtex-6 FPGA and is the answer not in the manual?

Questions and answers