User Manuals: ST STM32L4 Series Evaluation Board

Manuals and User Guides for ST STM32L4 Series Evaluation Board. We have 8 ST STM32L4 Series Evaluation Board manuals available for free PDF download: Programming Manual, Manual, User Manual, Application Note

ST STM32L4 Series Programming Manual (262 pages)

Brand: ST

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

Advertisement

ST STM32L4 Series Programming Manual (262 pages)

Brand: ST

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

ST STM32L4 Series User Manual (110 pages)

Brand: ST

|

Category: Microcontrollers

|

Size: 1 MB

Table of Contents

Advertisement

ST STM32L4 Series Manual (213 pages)

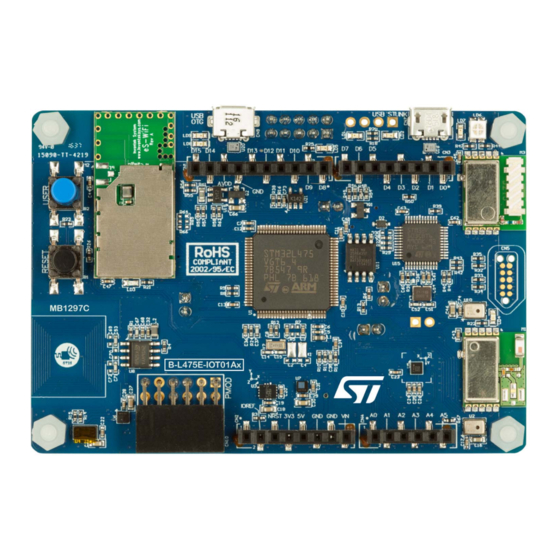

Simplifying Microsoft Azure Connectivity with Discovery Kit IoT Node

Brand: ST

|

Category: Microcontrollers

|

Size: 14 MB

Table of Contents

ST STM32L4 Series Application Note (52 pages)

Getting started with touch sensing control on STM32 microcontrollers

Brand: ST

|

Category: Microcontrollers

|

Size: 4 MB

Table of Contents

ST STM32L4 Series User Manual (57 pages)

Discovery kit for IoT node, multi-channel communication

Brand: ST

|

Category: Motherboard

|

Size: 1 MB

Table of Contents

ST STM32L4 Series Application Note (56 pages)

Brand: ST

|

Category: Microcontrollers

|

Size: 3 MB

Table of Contents

ST STM32L4 Series Application Note (58 pages)

Brand: ST

|

Category: Microcontrollers

|

Size: 0 MB

Table of Contents

Advertisement