VIA Technologies VT82C694X Pro Manuals

Manuals and User Guides for VIA Technologies VT82C694X Pro. We have 4 VIA Technologies VT82C694X Pro manuals available for free PDF download: Design Manual, User Manual

VIA Technologies VT82C694X Pro Design Manual (140 pages)

Brand: VIA Technologies

|

Category: Network Hardware

|

Size: 2 MB

Table of Contents

Advertisement

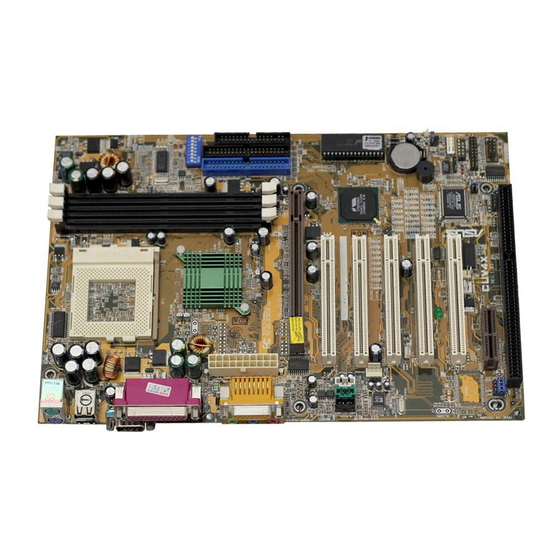

VIA Technologies VT82C694X Pro User Manual (78 pages)

ATX Form Factor Main Board

Brand: VIA Technologies

|

Category: Motherboard

|

Size: 1 MB

Table of Contents

VIA Technologies VT82C694X Pro User Manual (50 pages)

Brand: VIA Technologies

|

Category: Motherboard

|

Size: 1 MB

Table of Contents

Advertisement

VIA Technologies VT82C694X Pro User Manual (43 pages)

Brand: VIA Technologies

|

Category: Motherboard

|

Size: 1 MB