Xilinx 7 Series User Manual

Hide thumbs

Also See for 7 Series:

- User manual (306 pages) ,

- User manual (112 pages) ,

- User manual (74 pages)

Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Xilinx 7 Series

- Page 1 7 Series DSP48E1 Slice User Guide UG479 (v1.10) March 27, 2018...

-

Page 2: Revision History

(including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. - Page 3 Added 7A15T device to Table 2-1. Updated last paragraph in MULTSIGNOUT and CARRYCASCOUT. 09/27/2016 Added Spartan-7 family to Preface. Added 7 series FPGA data sheets to Additional Documentation Resources. DSP48E1 Tile and Interconnect, changed smallest number of slices from 60 to 10 and added Spartan-7 devices.

- Page 4 7 Series DSP48E1 User Guide www.xilinx.com UG479 (v1.10) March 27, 2018...

-

Page 5: Table Of Contents

............14 Architectural Highlights of the 7 Series FPGA DSP48E1 Slice . - Page 6 MACC Operation ............58 www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback...

-

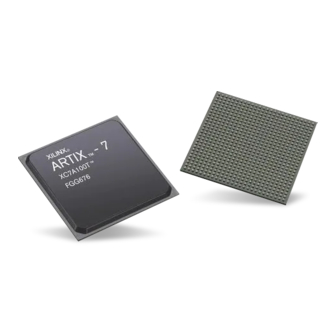

Page 7: Preface: About This Guide

This guide serves as a technical reference describing the 7 series FPGAs DSP48E1 slice. This 7 series FPGAs DSP48E1 slice user guide is part of an overall set of documentation on the 7 series FPGAs, which is available on the Xilinx website at www.xilinx.com/documentation. -

Page 8: Additional Support Resources

Preface: About This Guide Additional Support Resources To search the database of silicon and software questions and answers or to create a technical support case in WebCase, see the Xilinx website at: www.xilinx.com/support www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback... -

Page 9: Chapter 1: Overview

DSP applications use many binary multipliers and accumulators that are best implemented in dedicated DSP slices. All 7 series FPGAs have many dedicated, full-custom, low-power DSP slices, combining high speed with small size while retaining system design flexibility. The DSP slices enhance the... -

Page 10: Features Relative To Prior Generations

The 7 series FPGA DSP48E1 slice is functionally equivalent and fully compatible with the Virtex®-6 FPGA DSP48E1 slice, and a superset of the Virtex-5 FPGA DSP48E slice [Ref The 7 series FPGA DSP48E1 slice offers more capability than the DSP48A1 slice of the Spartan®-6 FPGA family with these differences: •... -

Page 11: Design Recommendations

Design Recommendations Design Recommendations Many DSP designs are well suited for the 7 series architecture. To obtain best use of the architecture, the underlying features and capabilities need to be understood so that design entry code can take advantage of these resources. DSP48E1 resources are used automatically for most DSP functions and many arithmetic functions. - Page 12 Chapter 1: Overview www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 13: Chapter 2: Dsp48E1 Description And Specifics

Chapter 2 DSP48E1 Description and Specifics This chapter provides technical details of the DSP element available in 7 series FPGAs, the DSP48E1 slice. The DSP48E1 slice provides improved flexibility and utilization, improved efficiency of applications, reduced overall power consumption, and increased maximum frequency. -

Page 14: Dsp48E1 Slice Features

Figure 2-1: 7 Series FPGA DSP48E1 Slice DSP48E1 Slice Features This section describes the 7 series FPGA DSP48E1 slice features. The DSP slice consists of a multiplier followed by an accumulator. At least three pipeline registers are required for both multiply and multiply-accumulate operations to run at full speed. - Page 15 96 bits. The DSP slice supports convergent and symmetric rounding, terminal count detection and auto-resetting for counters, and overflow/underflow detection for sequential accumulators. ALU functions are identical in 7 series FPGA DSP48E1 slice as in the Virtex-6 FPGA DSP48E1 slice. See ALUMODE Inputs, page 35 for more information.

-

Page 16: Architectural Highlights Of The 7 Series Fpga Dsp48E1 Slice

The 7 series FPGA DSP48E1 slice is functionally equivalent to the Virtex-6 FPGA DSP48E1. The 7 series FPGA DSP48E1 slice contains a pre-adder after the A register with a 25-bit input vector called D. The D register can be used either as the pre-adder register or an alternate input to the multiplier. - Page 17 Architectural Highlights of the 7 Series FPGA DSP48E1 Slice The features in the 7 series FPGA DSP48E1 slice are: • 25-bit pre-adder with D register to enhance the capabilities of the A path • INMODE control supports balanced pipelining when dynamically switching between multiply (A*B) and add operations (A:B) •...

- Page 18 (counter auto reset). The pattern detector can detect if the output of the DSP48E1 slice matches a pattern, as qualified by a mask. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 19: Dsp48E1 Tile And Interconnect

(CLBs) and also matches the height of one block RAM. The block RAM in 7 series devices can be split into two 18K block RAMs. Each DSP48E1 slice aligns horizontally with an 18K block RAM. The 7 series devices have up to 20 DSP48E1 columns. - Page 20 Chapter 2: DSP48E1 Description and Specifics Table 2-1: Number of DSP48E1 Slices in 7 Series Devices (Cont’d) Total DSP48E1 Slices per Number of DSP48E1 Columns Number of DSP48E1 Slices Device Device per Device per Column 7K160T 7K325T 7K355T 1,440 7K410T...

-

Page 21: Dsp48E1 Slice Primitive

OVERFLOW CEALUMODE UNDERFLOW CECTRL CECARRYIN CEINMODE RSTA RSTB RSTC RSTD RSTM RSTP RSTCTRL RSTALLCARRYIN RSTALUMODE RSTINMODE ACIN[29:0] BCIN[17:0] PCIN[47:0] CARRYCASCIN MULTSIGNIN UG369_c1_04_051209 Figure 2-4: DSP48E1 Slice Primitive 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018... - Page 22 Clock enable for the second B (input) register. B2 is only used if BREG = 1 or 2 and INMODE[4]=0. Clock enable for the C (input) register. CECARRYIN Clock enable for the CARRYIN (input from FPGA logic) register. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 23 Reset for the C (input) register. RSTCTRL Reset for OPMODE and CARRYINSEL (control inputs) registers. RSTD Reset for the D (input) register and for the pre-adder (output) AD pipeline register. 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 24: Simplified Dsp48E1 Slice Operation

The output of the adder/subtracter or logic unit feeds the pattern detector logic. The pattern detector allows the DSP48E1 slice to support Convergent Rounding, Counter Autoreset when a count value has been reached, and Overflow/Underflow/Saturation in www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... - Page 25 X-Ref Target - Figure 2-5 OPMODE Controls Behavior All 1s All 0s PCIN OPMODE, CARRYINSEL, and ALUMODE Control Behavior Shifters UG369_c1_05_051209 Figure 2-5: Simplified DSP Slice Operation 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 26: Dsp48E1 Slice Attributes

(CASCADE). B_INPUT DIRECT, CASCADE Selects the input to the B port between parallel input (DIRECT) (DIRECT) or the cascaded input from the previous slice (CASCADE). www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... - Page 27 2) select special masks based off of the optionally registered C port. These rounding modes can be used to implement convergent rounding in the DSP48E1 slice using the pattern detector. 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

- Page 28 These two partial products are input into the X and Y multiplexers and finally into the adder/subtracter to create the product output. The M register is selected by MREG, enabled by CEM, and reset synchronously by RSTM. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 29: Input Ports

DSP48E1 slice has four direct input data ports labeled A, B, C, and D. The A data port is 30 bits wide, the B data port is 18 bits wide, the C data port is 48 bits wide, and the pre- adder D data port is 25 bits wide. 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback... - Page 30 X MUX INMODE[1] ACIN CEA1 RSTA CEA2 RSTA INMODE[0] A MULT – INMODE[2] INMODE[3] CEAD RSTD CED RSTD UG369_c1_07_040914 Figure 2-7: Dual A, D, and Pre-adder Logic www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 31 Zero TRUE Zero TRUE D + A2 TRUE D + A1 TRUE TRUE TRUE TRUE TRUE Zero TRUE Zero TRUE D – A2 TRUE D – A1 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

- Page 32 2-9. The CREG attribute selects the number of pipestages for the C input datapath. X-Ref Target - Figure 2-9 C Input to Y and Z Multiplexers and Pattern Detector RSTC UG369_c1_09_051209 Figure 2-9: C Port Logic www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 33 (for example, altering the internal datapath configuration of the DSP48E1 slice relative to a given calculation sequence). The OPMODE bits can be optionally registered using the OPMODEREG attribute (as noted in Table 2-3). 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

- Page 34 Must select with PREG = 1 Use for MACC extend only. Must select with PREG = 1 17-bit Shift (PCIN) 17-bit Shift (P) Must select with PREG = 1 Illegal selection www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 35 –Z – X – Y – CIN - 1 Notes: 1. In two’s complement: –Z = not (Z) + 1 Table 2-13, page 42 for two-input ALUMODE operations and Figure A-3, page 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

- Page 36 Chapter 2: DSP48E1 Description and Specifics Carry Input Logic In 7 series devices, the carry input logic result is a function of a 3-bit CARRYINSEL signal. The inputs to the carry input logic appear in Figure 2-11. Carry inputs used to form results for adders and subtracters are always in the critical path.

-

Page 37: Output Ports

For rounding P (round towards zero). Must select with PREG = 1 Output Ports This section describes the output ports of the 7 series FPGA DSP48E1 slice in detail. The output ports of the DSP48E1 slice are shown in Figure 2-12. - Page 38 CARRYCASCOUT port. Larger add, subtract, ACC, and MACC functions can be implemented in the DSP48E1 slice using the CARRYCASCOUT output port. The 1-bit CARRYCASCOUT signal corresponds to CARRYOUT[3], but is not identical. The www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 39 P[N] bit where N is between 1 and 46. The P register must be enabled while using overflow and underflow ports. This is further described in the Embedded Functions section. 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 40: Embedded Functions

*These signals are dedicated routing paths internal to the DSP48E1 column. They are not accessible via fabric routing resources. UG369_c1_14_052109 Figure 2-14: Embedded Functions in a DSP48E1 Slice Pre-adder The 7 series FPGA DSP slice has a 25-bit pre-adder, which is inserted in the A register path (shown in Figure 2-14 with an expanded view in Figure 2-7, page 30). - Page 41 ALUMODE Inputs, page Two-Input Logic Unit In 7 series devices, the capability to perform an addition, subtraction, and simple logic functions in the DSP48E1 slice exists through use of a second-stage, three-input adder. Table 2-13 lists the logic functions that can be implemented in the second stage of the three input adder/subtracter/logic unit.

-

Page 42: Single Instruction, Multiple Data (Simd) Mode

24-bit adder/subtracter/accumulators with carry out signal per segment. The SIMD mode segmentation is a static configuration as opposed to dynamic OPMODE type control (see Figure 2-16). www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... -

Page 43: Pattern Detect Logic

DSP48E1 slice. The use of the pattern detector leads to a moderate speed reduction due to the extra logic on the pattern detect path (see Figure 2-17). 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018... - Page 44 A mask field can also be used to mask out certain bit locations in the pattern detector. The pattern field and the mask field can each come from a distinct 48-bit memory cell field or from the (registered) C input. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

- Page 45 0 .. 0001 0 .. 0010 0 .. 0011 0 .. 0100 PD Caused by Overflow High to Low Overflow UG369_c1_19_051209 Figure 2-19: Overflow Condition in the Pattern Detector 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

- Page 46 Underflow is caused by subtraction when the value goes below –4. Subtracting 1 from 1..1100 yields 1..1010 (–5), which causes the PBD output to go to 0. When the PBD output goes from 1 to 0, an underflow is flagged. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 47: Chapter 3: Dsp48E1 Design Considerations

For multiplier-based designs, the DSP48E1 slice requires a three-stage pipeline. For non-multiplier-based designs, a two-stage pipeline should be used. Also see the 7 series FPGA data sheets [Ref 6]. If latency is important in the design and only one or two registers can be used within the DSP48E1 slice, always use the M register. -

Page 48: Adder Tree Versus Adder Cascade

× performance bottleneck that consume more power. X(n) Z -2 h1(n) × h0(n) × X(n) UG479_c2_01_072210 Figure 3-1: Traditional FIR Filter Adder Tree www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... - Page 49 The 7 series FPGA CLB allows the use of both the 6LUT and the carry chain in the same slice to build an efficient ternary adder. The 6LUT in the CLB functions as a dual 5LUT. The 5LUT is used as a 3:2 compressor to add three input values to produce two output values.

-

Page 50: Adder Cascade

DSP48E1 slice. This involves computing the additive result incrementally, utilizing a cascaded approach as illustrated in Figure 3-5. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... - Page 51 It is important to balance the delay of the input sample and the coefficients in the cascaded adder to achieve the correct results. The coefficients are staggered in time (wave coefficients). 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018...

-

Page 52: Connecting Dsp48E1 Slices Across Columns

Due to the high performance of the DSP48E1 slice within the 7 series device, a single digital filter can be used to filter all eight input channels by clocking the single filter with an 8x clock. This implementation uses 1/8th of the total FPGA resource as compared to implementing each channel separately. -

Page 53: Dsp48E1 Design Resources

DSP48E1 slice. • In 7 series devices, the register at the output of the SRL16 in the slice has a reset pin and a clock-enable pin. To reset the SRL16, a zero is input into the SRL16 for 16 clock cycles while holding the reset of the output register High. -

Page 54: Memory-Mapped I/O Register Application

An address decoder should be implemented in fabric logic to control individual PREG CEs to load the appropriate DSP output register from the write data bus. www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018... -

Page 55: Appendix A: Carryout, Carrycascout, And Multsignout

Sub/Add = 1/0 (Carry input must be 1 for a subtract operation, so it is not available for other uses.) UG369_A_01_111208 Figure A-1: FPGA Logic Interconnect Based Adder/Subtracter 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018... - Page 56 DSP48E1 Slice Add/Subtract UG369_A_03_111208 Figure A-3: DSP48E1 Slice Three-Input Adder Virtex-6 and 7 series FPGA ALUMODE supports additional subtract operations: ALUMODE = 0001 implements (-Z + (X + Y + CIN) – 1). • For most uses, CIN is set to 1 to cancel out the -1.

-

Page 57: Multsignout And Carrycascout

FPGA logic; thus, the DSP48E1 slice requires an inverted CARRYOUT from the FPGA logic. MULTSIGNOUT is invalid in adder-only operation. 7 Series DSP48E1 User Guide www.xilinx.com Send Feedback UG479 (v1.10) March 27, 2018... -

Page 58: Macc Operation

Zmux (e.g., C, P, PCIN) Partial products from the multiply operation are added together in the second stage ternary adder. UG369_A_05_111208 Figure A-5: MACC Software and Hardware Models www.xilinx.com 7 Series DSP48E1 User Guide Send Feedback UG479 (v1.10) March 27, 2018...

Need help?

Do you have a question about the 7 Series and is the answer not in the manual?

Questions and answers