Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Epson S1C31W74

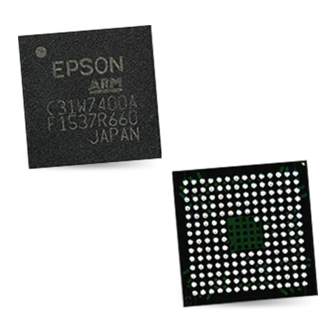

- Page 1 CMOS 32-BIT SINGLE CHIP MICROCONTROLLER S1C31W74 Technical Manual Rev. 1.1...

- Page 2 2. This evaluation board/kit or development tool is intended for use by an electronic engineer and is not a consumer product. The user should use it properly and in a safe manner. Seiko Epson does not assume any responsibility or liability of any kind of damage and/or fire caused by its use.

- Page 3 PREFACE Preface This is a technical manual for designers and programmers who develop a product using the S1C31W74. This document describes the functions of the IC, embedded peripheral circuit operations, and their control methods. Notational conventions and symbols in this manual Register address Peripheral circuit chapters do not provide control register addresses.

-

Page 4: Table Of Contents

3.2 CPU ..........................3-1 3.3 Debugger ........................3-1 3.3.1 List of Debugger Input/Output Pins ..............3-1 3.3.2 External Connection ..................3-1 3.4 Reference Documents ....................3-2 4 Memory and Bus ......................4-1 4.1 Overview ......................... 4-1 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 5 DMAC Request Mask Clear Register ..................6-12 DMAC Enable Set Register ...................... 6-12 DMAC Enable Clear Register ....................6-12 DMAC Primary-Alternate Set Register ..................6-12 DMAC Primary-Alternate Clear Register .................. 6-13 DMAC Priority Set Register ...................... 6-13 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 6 8.1 Overview ......................... 8-1 8.2 Peripheral Circuit I/O Function Assignment ..............8-1 8.3 Control Registers ......................8-2 Pxy–xz Universal Port Multiplexer Setting Register ..............8-2 9 Watchdog Timer (WDT2) ....................9-1 9.1 Overview ......................... 9-1 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 7 11.4.2 SVD2 Operations ................... 11-4 11.5 SVD2 Interrupt and Reset .................... 11-5 11.5.1 SVD2 Interrupt ....................11-5 11.5.2 SVD2 Reset ....................11-5 11.6 Control Registers ......................11-6 SVD2 Ch.n Clock Control Register ..................11-6 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 8 13.6 Receive Errors ......................13-8 13.6.1 Framing Error ....................13-8 13.6.2 Parity Error ..................... 13-9 13.6.3 Overrun Error ....................13-9 13.7 Interrupts ........................13-9 13.8 DMA Transfer Requests ....................13-9 13.9 Control Registers ......................13-10 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 9 15.3 Clock Settings ......................15-6 15.3.1 QSPI Operating Clock ................... 15-6 15.3.2 Clock Supply During Debugging ..............15-7 15.3.3 QSPI Clock (QSPICLKn) Phase and Polarity ..........15-7 15.4 Data Format ......................... 15-8 15.5 Operations ........................15-9 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 10 I2C Ch.n Mode Register ......................16-19 I2C Ch.n Baud-Rate Register ....................16-19 I2C Ch.n Own Address Register ..................... 16-20 I2C Ch.n Control Register ....................... 16-20 I2C Ch.n Transmit Data Register ..................... 16-21 Seiko Epson Corporation viii S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 11 18.4.4 Output in Melody Mode ................. 18-7 18.5 Interrupts ........................18-9 18.6 DMA Transfer Requests ....................18-10 18.7 Control Registers ......................18-10 SNDA Clock Control Register ....................18-10 SNDA Select Register ......................18-11 SNDA Control Register ......................18-12 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 12 20.4.5 LCD Contrast Adjustment ................20-7 20.5 Operations ........................20-7 20.5.1 Initialization ....................20-7 20.5.2 Display On/Off ....................20-8 20.5.3 Inverted Display ..................... 20-8 20.5.4 Drive Duty Switching ..................20-8 20.5.5 Drive Waveforms ................... 20-10 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 13 22.3 Clock Settings ......................22-3 22.4 USB Power Supply ...................... 22-4 22.5 Operations ........................22-4 22.5.1 Initialization ....................22-4 22.5.2 Settings when V is Disconnected ............. 22-6 22.5.3 Transaction Control ..................22-7 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 14 23.3 Current Consumption ....................23-2 23.4 System Reset Controller (SRC) Characteristics ............23-4 23.5 Clock Generator (CLG) Characteristics................ 23-5 23.6 Flash Memory Characteristics ..................23-6 23.7 Input/Output Port (PPORT) Characteristics ..............23-7 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 15 B.1 Operating Status Configuration Examples for Power Saving ........AP-B-1 B.2 Other Power Saving Methods ..................AP-B-2 Appendix C Mounting Precautions ................AP-C-1 Appendix D Measures Against Noise ................ AP-D-1 Revision History Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL xiii (Rev. 1.1)

-

Page 16: Overview

1 OVERVIEW 1 Overview The S1C31W74 is a 32-bit MCU with an Arm Cortex -M0+ processor included that features low-power opera- ® ® tion. It incorporates a lot of serial interface circuits and is suitable for various kinds of battery-driven controller ap- plications. - Page 17 IOSC = OFF, OSC1 = ON, OSC3 = OFF, RTC = ON HALT mode 1.7 µA OSC1 = 32 kHz 7.7 µA OSC1 = 32 kHz, LCD = ON (no panel load) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 18: Block Diagram

TOUT10–11 RFIN0 16-bit PWM timer CAP00–01 R/F converter REF0 (T16B) CAP10–11 (RFC) SENA0 2 Ch. 1 Ch. EXCL00–01 SENB0 EXCL10–11 RFCLKO0 UART USIN0–1 (UART2) USOUT0–1 2 Ch. Figure 1.2.1 S1C31W74 Block Diagram Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 19: Pins

UPMUX UPMUX UPMUX UPMUX QSDIO03 MON) N.C. USB_DM USB_DP V N.C. SPICLK0 SENB0 REF0 RFIN0 EXCL10 EXCL11 OSC3 OSC4 UPMUX UPMUX UPMUX UPMUX UPMUX #QSPISS0 Figure 1.3.1.1 S1C31W74 Pin Configuration Diagram (VFBGA8H-181) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 20: Pad Configuration Diagram

USB_DP USB_DP USB_DM USB_DM 5.480 mm Figure 1.3.2.1 S1C31W74 Pad Configuration Diagram Pad opening: Pad No. 1–36, 83–127 X = 68 µm, Y = 80 µm Pad No. 49–78, 128–167 X = 80 µm, Y = 68 µm Pad No. 37, 38, 81, 82 X = 76 µm, Y = 90 µm... - Page 21 1 OVERVIEW Table 1.3.2.1 S1C31W74 Pad Coordinates X µm Y µm X µm Y µm X µm Y µm X µm Y µm -2,424.0 -2,334.5 2,649.5 -1,898.0 2,272.2 2,329.5 -2,654.5 2,056.0 -2,344.0 -2,334.5 2,649.5 -1,768.0 2,172.2 2,329.5 -2,654.5 1,976.0 -2,264.0 -2,334.5 2,649.5 -1,638.0...

-

Page 22: Pin Descriptions

User-selected I/O (universal port multiplexer) Hi-Z – I/O port BZOUT Sound generator output UPMUX User-selected I/O (universal port multiplexer) Hi-Z – I/O port #BZOUT Sound generator inverted output UPMUX User-selected I/O (universal port multiplexer) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 23 UPMUX User-selected I/O (universal port multiplexer) COM20 LCD common output SEG83 LCD segment output Hi-Z I/O port ✓ UPMUX User-selected I/O (universal port multiplexer) COM21 LCD common output SEG82 LCD segment output Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 24 Hi-Z I/O port ✓ SEG60 LCD segment output Hi-Z I/O port ✓ SEG59 LCD segment output Hi-Z I/O port ✓ SEG58 LCD segment output Hi-Z I/O port ✓ SEG57 LCD segment output Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 25 TOUTn0/CAPn0 n = 0, 1 T16B Ch.n PWM output/capture input 0 (T16B) TOUTn1/CAPn1 T16B Ch.n PWM output/capture input 1 Note: Do not assign a function to two or more pins simultaneously. Seiko Epson Corporation 1-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 26: Power Supply, Reset, And Clocks

For the V operating voltage range and recommended external parts, refer to “Recommended Operating Condi- tions, Power supply voltage V ” in the “Electrical Characteristics” chapter and the “Basic External Connection Diagram” chapter, respectively. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 27: D1 Regulator Operation Mode

6. Write a value other than 0x0096 to the SYSPROT.PROT[15:0] bits. (Set system protection) Note: After the voltage mode has been switched, correct the RTC, as the RTC operating clock is also stopped for the period set using the CLGOSC1.OSC1WT[1:0] bits. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 28: System Reset Controller (Src)

#RESET pin, so the pin can be left open. For the #RESET pin characteris- tics, refer to “#RESET pin characteristics” in the “Electrical Characteristics” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 29: Reset Sources

Table 2.2.4.1 lists the reset groups. For the reset group to initialize the registers and con- trol bits, refer to the “CPU and Debugger” chapter or “Control Registers” in each peripheral circuit chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 30: Clock Generator (Clg)

- The oscillator and clock input circuit on/off state can be maintained or changed at SLEEP mode cancelation. • Provides the FOUT function to output an internal clock for driving external ICs or for monitoring the internal state. Figure 2.3.1.1 shows the CLG configuration. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 31: Input/Output Pins

* Indicates the status when the pin is configured for CLG. If the port is shared with the CLG input/output function and other functions, the CLG function must be assigned to the port. For more information, refer to the “I/O Ports” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 32: Clock Sources

“OSC1 oscillator circuit characteristics” in the “Electrical Characteristics” chapter, respectively. Note: Depending on the circuit board or the crystal resonator type used, an external gate capacitor C and a drain capacitor C may be required. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 33: Operations

Figure 2.3.4.1 shows the relationship be- tween the oscillation start time and the oscillation stabilization waiting time. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 34 (2) CLGOSC1.OSC1BUP bit = 1 (startup boosting operation enabled) Oscillator circuit enable (CLGOSC.OSC1EN) Oscillation inverter INV1B[1:0] setting gain INV1N[1:0] setting gain Oscillation waveform Startup boosting Normal operation operation Figure 2.3.4.2 Operation Example when the Oscillation Startup Control Circuit is Used Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 35 0x0096 to the SYSPROT.PROT[15:0] bits before the register setting can be altered. For the transition between the operating modes including the system clock switching, refer to “Operating Mode.” Seiko Epson Corporation 2-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 36 2. Configure the following CLGFOUT register bits: - CLGFOUT.FOUTSRC[1:0] bits (Select clock source) - CLGFOUT.FOUTDIV[2:0] bits (Set clock division ratio) - Set the CLGFOUT.FOUTEN bit to 1. (Enable clock external output) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-11 (Rev. 1.1)

- Page 37 7. The OSC1 oscillation stops if the CLGINTF.OSC1STPIF bit = 1 after an interrupt occurs. If the CLGOSC1.OSDRB bit = 1, the hardware restarts the OSC1 oscillator circuit. Note: Enabling the oscillation stop detection function increase the oscillation stop detector current (I OSD1 Seiko Epson Corporation 2-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 38: Operating Mode

0 keeps operating, so the peripheral circuits with the clock being supplied can also operate. By setting this mode when no software processing and peripheral circuit operations are required, power consumption can be less than HALT mode. The RAM retains data even in SLEEP mode. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-13 (Rev. 1.1) - Page 39 The conditions listed below generate the HALT/SLEEP cancelation signal to cancel HALT or SLEEP mode and put the CPU into RUN mode. • Interrupt request from a peripheral circuit • NMI from the watchdog timer • Reset request Seiko Epson Corporation 2-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 40: Interrupts

Bits 3–2 Reserved Bits 1–0 REGMODE[1:0] These bits control the V regulator operating mode. Table 2.6.1 Internal Regulator Operating Mode PWGACTL.REGMODE[1:0] bits Operating mode Economy mode Normal mode Reserved Automatic mode Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-15 (Rev. 1.1) -

Page 41: Clg System Clock Control Register

These bits set the division ratio of the clock source to determine the SYSCLK frequency. Bits 3–2 Reserved Bits 1–0 CLKSRC[1:0] These bits select the SYSCLK clock source. When a currently stopped clock source is selected, it will automatically start oscillating or clock input. Seiko Epson Corporation 2-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 42: Clg Oscillation Control Register

Stop oscillating or clock input Each bit corresponds to the clock source as follows: CLGOSC.EXOSCEN bit: EXOSC clock input CLGOSC.OSC3EN bit: OSC3 oscillator circuit CLGOSC.OSC1EN bit: OSC1 oscillator circuit CLGOSC.IOSCEN bit: IOSC oscillator circuit Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-17 (Rev. 1.1) -

Page 43: Clg Iosc Control Register

Remarks CLGOSC1 – – – OSDRB R/WP OSDEN R/WP OSC1BUP R/WP – – 10–8 CGI1[2:0] R/WP 7–6 INV1B[1:0] R/WP 5–4 INV1N[1:0] R/WP 3–2 – – 1–0 OSC1WT[1:0] R/WP Bit 15 Reserved Seiko Epson Corporation 2-18 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 44 These bits set the oscillation inverter gain applied at normal operation of the OSC1 oscillator circuit. Table 2.6.7 Setting Oscillation Inverter Gain at OSC1 Normal Operation CLGOSC1.INV1N[1:0] bits Inverter gain Max. ↑ ↓ Min. Bits 3–2 Reserved Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-19 (Rev. 1.1)

-

Page 45: Clg Osc3 Control Register

IOSCTERIF Cleared by writing 1. – – – (reserved) OSC1STPIF Cleared by writing 1. IOSCTEDIF – – – OSC3STAIF Cleared by writing 1. OSC1STAIF IOSCSTAIF Bits 15–9, 7, 6, 3 Reserved Seiko Epson Corporation 2-20 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 46: Clg Interrupt Enable Register

CLGINTE.IOSCTEDIE bit: IOSC oscillation auto-trimming completion interrupt CLGINTE.OSC3STAIE bit: OSC3 oscillation stabilization waiting completion interrupt CLGINTE.OSC1STAIE bit: OSC1 oscillation stabilization waiting completion interrupt CLGINTE.IOSCSTAIE bit: IOSC oscillation stabilization waiting completion interrupt Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 2-21 (Rev. 1.1) -

Page 47: Clg Fout Control Register

0 (R/W): Disable external output Note: Since the FOUT signal generated is out of sync with writings to the CLGFOUT.FOUTEN bit, a glitch may occur when the FOUT output is enabled or disabled. Seiko Epson Corporation 2-22 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 48: Cpu And Debugger

For the recommended pull-up resistor value, refer to “Recommended Operating Conditions, Debug pin pull-up re- sistors R ” in the “Electrical Characteristics” chapter. R and R are not required when using the debug DBG1–2 DBG1 DBG2 pins as general-purpose I/O port pins. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 49: Reference Documents

Architecture Reference Manual ® 2. Cortex -M0+Technical Reference Manual ® 3. Cortex -M0+ Devices Generic User Guide ® These documents can be downloaded from the document site of Arm Ltd. https://developer.arm.com/documentation Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 50: Memory And Bus

Memory mapped access area for external Flash memory (1M bytes) (Device size: 32 bits) 0x0008 0000 0x0007 ffff Flash area (512K bytes) (Device size: 32 bits) 0x0000 0000 Figure 4.1.1 Memory Map Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 51: Bus Access Cycle

The number of bus access cycles for reading can be configured using the FLASHCWAIT.RDWAIT[1:0] bits. Select a setting for higher frequency than the system clock. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 52: Flash Programming

SVD2 Ch.0 Clock Control Register (SVD2) Ch.0 0x4000 0102 SVD2_0CTL SVD2 Ch.0 Control Register 0x4000 0104 SVD2_0INTF SVD2 Ch.0 Status and Interrupt Flag Register 0x4000 0106 SVD2_0INTE SVD2 Ch.0 Interrupt Enable Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 53 0x4000 026a PPORTP6CHATEN P6 Port Chattering Filter Enable Register 0x4000 026c PPORTP6MODSEL P6 Port Mode Select Register 0x4000 026e PPORTP6FNCSEL P6 Port Function Select Register 0x4000 0270 PPORTP7DAT P7 Port Data Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 54 0x4000 03b0 SPIA_0MOD SPIA Ch.0 Mode Register (SPIA) Ch.0 0x4000 03b2 SPIA_0CTL SPIA Ch.0 Control Register 0x4000 03b4 SPIA_0TXD SPIA Ch.0 Transmit Data Register 0x4000 03b6 SPIA_0RXD SPIA Ch.0 Receive Data Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 55 UART2 Ch.1 Mode Register 0x4000 0604 UART2_1BR UART2 Ch.1 Baud-Rate Register 0x4000 0606 UART2_1CTL UART2 Ch.1 Control Register 0x4000 0608 UART2_1TXD UART2 Ch.1 Transmit Data Register 0x4000 060a UART2_1RXD UART2 Ch.1 Receive Data Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 56 LCD32B Clock Control Register 0x4000 0802 LCD32BCTL LCD32B Control Register 0x4000 0804 LCD32BTIM1 LCD32B Timing Control Register 1 0x4000 0806 LCD32BTIM2 LCD32B Timing Control Register 2 0x4000 0808 LCD32BPWR LCD32B Power Control Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 57 USB EPa Interrupt Enable Register 0x2040 0065 USBEPbINTE USB EPb Interrupt Enable Register 0x2040 0066 USBEPcINTE USB EPc Interrupt Enable Register 0x2040 0100 USBFIFODAT USB FIFO Data Register 0x2040 0104 USBDBGRAMDAT USB Debug RAM Data Register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 58: System-Protect Function

4.8 Memory Mapped Access Area For External Flash Memory This area is used to read data from the external Flash memory via the quad synchronous serial interface. For more information, refer to the “Quad Synchronous Serial Interface” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 59: Control Registers

Notes: • Be sure to set the FLASHCWAIT.RDWAIT[1:0] bits before the system clock is configured. • When the FLASHCWAIT.RDWAIT[1:0] bit setting is altered from 0x2 to 0x1, add two NOP instructions immediately after that. Program example: FLASHC->WAIT_b.RDWAIT = 1; asm(“NOP”); asm(“NOP”); CLG->OSC_b.IOSCEN = 0; Seiko Epson Corporation 4-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 60: Interrupt

• IOSC oscillation stabilization waiting completion • OSC1 oscillation stabilization waiting completion • OSC3 oscillation stabilization waiting completion • OSC1 oscillation stop • IOSC oscillation auto-trimming completion • IOSC oscillation auto-trimming error Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 61 • Transmit buffer empty VTOR + 0x80 IR remote controller • Compare AP interrupt • Compare DB VTOR + 0x84 LCD driver interrupt Frame VTOR + 0x88 16-bit timer Ch.3 interrupt Underflow Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 62: Vector Table Offset Address (Vtor)

Note: To prevent occurrence of unnecessary interrupts, the corresponding interrupt flag should be cleared before setting the interrupt enable bit to 1 (interrupt enabled) and before terminating the interrupt handler routine. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 63: Nmi

The watchdog timer embedded in this IC can generate a non-maskable interrupt (NMI). This interrupt takes prece- dence over other interrupts and is unconditionally accepted by the CPU. For detailed information on generating NMI, refer to the “Watchdog Timer” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 64: Dma Controller (Dmac)

• Priority level for each channel is selectable from two levels. • DMA transfers are allowed even if the CPU is placed into HALT mode. Figure 6.1.1 shows the configuration of the DMAC. Table 6.1.1 DMAC Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 4 channels (Ch.0 to Ch.3) -

Page 65: Operations

256 bytes DMACCPTR.CPTR[31:0] (CPTR[7:0] = 0x00) DMACCPTR.CPTR[31:0] + 0x080 9 to 16 512 bytes DMACCPTR.CPTR[31:0] (CPTR[8:0] = 0x000) DMACCPTR.CPTR[31:0] + 0x100 17 to 32 1,024 bytes DMACCPTR.CPTR[31:0] (CPTR[9:0] = 0x000) DMACCPTR.CPTR[31:0] + 0x200 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 66: Transfer Source End Pointer

6.4.2 Transfer Destination End Pointer Set the address to which the last transfer data is written. The address for writing transfer data should be set as it is if the transfer destination address is not incremented. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 67 When the DMAC is performing a successive transfer, it suspends the data transfer at the cycle set with R_pow- er. If DMA requests have been issued at that point, the DMAC re-arbitrates them according to their priorities and then performs a DMA transfer for the channel with the highest priority. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 68: Dma Transfer Mode

DMA transfer 1 DMA transfer 2 DMA transfer 3 DMA transfer 4 DMA transfer 7 DMA transfer 8 operation DMACENDIF.ENDIFn DMA transfer request Figure 6.5.2.1 Auto-Request Transfer Operation Example (N = 8, 2 = 2) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 69: Ping-Pong Transfer

5. Set cycle_ctrl to 0x0 after a DMA transfer completion interrupt has occurred by the next to last task. 6. The DMA transfer is completed when a DMA transfer completion interrupt occurs by the last task. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 70: Memory Scatter-Gather Transfer

Copy the data structure for Task D to the alternate data structure. (cycle_ctrl = 0x1, 2 = 4, N = 4) Task D DMA transfer completion interrupt Figure 6.5.4.2 Memory Scatter-Gather Transfer Operation Example Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 71: Peripheral Scatter-Gather Transfer

Copy the data structure for Task D to the alternate data structure. (cycle_ctrl = 0x1, 2 = 4, N = 4) Task D DMA transfer completion interrupt Figure 6.5.5.1 Peripheral Scatter-Gather Transfer Operation Example Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 72: Dma Transfer Cycle

The DMAC provides interrupt enable bits corresponding to each interrupt flag. An interrupt request is sent to the CPU only when the interrupt flag, of which interrupt has been enabled by the interrupt enable bit, is set. For more information on interrupt control, refer to the “Interrupt” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 73: Control Registers

– 15–8 – 0x00 – – 7–1 – 0x00 – MSTEN – – Bits 31–1 Reserved Bit 0 MSTEN This bit enables the DMA controller. 1 (W): Enable 0 (W): Disable Seiko Epson Corporation 6-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 74: Dmac Control Data Base Pointer Register

DMA transfer requests from peripheral circuits have been disabled. 0 (R): DMA transfer requests from peripheral circuits have been enabled. Each bit corresponds to a DMAC channel. The high-order bits for the unimplemented channels are ineffective. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 6-11 (Rev. 1.1) -

Page 75: Dmac Request Mask Clear Register

The alternate data structure has been enabled. 0 (R): The primary data structure has been enabled. Each bit corresponds to a DMAC channel. The high-order bits for the unimplemented channels are ineffective. Seiko Epson Corporation 6-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 76: Dmac Primary-Alternate Clear Register

ERRIF This bit indicates the DMAC error interrupt cause occurrence status. 1 (R): Cause of interrupt occurred 0 (R): No cause of interrupt occurred 1 (W): Clear flag 0 (W): Ineffective Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 6-13 (Rev. 1.1) -

Page 77: Dmac Transfer Completion Interrupt Flag Register

DMAC Error Interrupt Enable Set Register Register name Bit name Initial Reset Remarks DMACERRIESET 31–24 – 0x00 – – 23–16 – 0x00 – 15–8 – 0x00 – 7–1 – 0x00 – ERRIESET Bits 31–1 Reserved Seiko Epson Corporation 6-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 78: Dmac Error Interrupt Enable Clear Register

0x00 – ERRIECLR – – Bits 31–1 Reserved Bit 0 ERRIECLR This bit disables DMA error interrupts. 1 (W): Disable interrupt (The DMACERRIESET register is cleared to 0.) 0 (W): Ineffective Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 6-15 (Rev. 1.1) -

Page 79: O Ports (Pport)

Note: ‘x’, which is used in the port names Pxy, register names, and bit names, refers to a port group (x = 0, 1, 2, ··· , d) and ‘y’ refers to a port number (y = 0, 1, 2, ··· , 7). Figure 7.1.1 shows the configuration of PPORT. Table 7.1.1 Port Configuration of S1C31W74 Item S1C31W74... -

Page 80: I/O Cell Structure And Functions

Falling time (port level = high → low) [second] High level Schmitt input threshold voltage [V] Low level Schmitt input threshold voltage [V] : Pull-up/pull-down resistance [W] Pin capacitance [F] Parasitic capacitance on the board [F] BOARD Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 81: Cmos Output And High Impedance State

• Port pins: High impedance state • Port function: Configured to GPIO This status continues until the ports are configured via software. The debugging function ports are configured for debug signal input/output. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 82 * Steps 1 and 5 are required for the ports with an interrupt function. Step 2 is required for the ports with a chat- tering filter function. Table 7.4.1.1 lists the port status according to the combination of data input/output control and pull-up/down control. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 83: Port Input/Output Control

1. Configure the ports to be used for key-entry reset as general-purpose input ports (refer to “Initial settings when using a port as a general-purpose input port (only for the ports with GPIO function)”). 2. Configure the input pin combination for key-entry reset using the PPORTCLK.KRSTCFG[1:0] bits. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 84: Interrupts

These bits are used to set data to be output from the GPIO port pins. 1 (R/W): Output high level from the port pin 0 (R/W): Output low level from the port pin Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 85: Px Port Enable Register

PPORTPxIOEN.PxIENy bit is set and the port is not pulled up/down. These bits do not affect the pull-up/down control when the port is used as a peripheral I/O function. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 86: Px Port Interrupt Flag Register

PPORTPxMODSEL 15–8 – 0x00 – – 7–0 PxSEL[7:0] 0x00 *1: The bit configuration differs depending on the port group. *2: The initial value may be changed by the port. Bits 15–8 Reserved Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 87: Px Port Function Select Register

Table 7.6.2 Key-Entry Reset Function Settings PPORTCLK.KRSTCFG[1:0] bits key-entry reset Reset when P0[3:0] inputs = all low Reset when P0[2:0] inputs = all low Reset when P0[1:0] inputs = all low Disable Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 88: P Port Interrupt Flag Group Register

A port generated an interrupt 0 (R): No port generated an interrupt The PPORTINTFGRP.PxINT bit is cleared when the interrupt flag for the port that has generated an interrupt is cleared. Seiko Epson Corporation 7-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 89: Control Register And Port Function Configuration Of This Ic

RFC Ch.0 SENA0 UPMUX – – – – RFC Ch.0 REF0 UPMUX – – – – RFC Ch.0 RFIN0 UPMUX – – – – *1: Refer to the “Universal Port Multiplexer” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-11 (Rev. 1.1) -

Page 90: P1 Port Group

– – REMC2 REMO UPMUX – – – – REMC2 CLPLS UPMUX – – – – RTCA RTC1S UPMUX – – – – *1: Refer to the “Universal Port Multiplexer” chapter. Seiko Epson Corporation 7-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 91: P2 Port Group

QSDIO03 – – – – T16B Ch.1 EXCL11 QSPI Ch.0 #QSPISS0 – – – – EXOSC – – – – – – – – – – SVD2 Ch.0 EXSVD0 – – Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-13 (Rev. 1.1) -

Page 92: P3 Port Group

– UPMUX – – LCD32B COM21/ SEG82 – – UPMUX – – LCD32B COM22/ SEG81 – – UPMUX – – LCD32B COM23/ SEG80 *1: Refer to the “Universal Port Multiplexer” chapter. Seiko Epson Corporation 7-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 93: P4 Port Group

– LCD32B COM28/ SEG75 – – – – – – LCD32B COM29/ SEG74 – – – – – – LCD32B COM30/ SEG73 – – – – – – LCD32B COM31/ SEG72 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-15 (Rev. 1.1) -

Page 94: P5 Port Group

– – – – – LCD32B SEG67 – – – – – – LCD32B SEG66 – – – – – – LCD32B SEG65 – – – – – – LCD32B SEG64 Seiko Epson Corporation 7-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 95: P6 Port Group

– – – – – LCD32B SEG59 – – – – – – LCD32B SEG58 – – – – – – LCD32B SEG57 – – – – – – LCD32B SEG56 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-17 (Rev. 1.1) -

Page 96: P7 Port Group

– – – – – LCD32B SEG5 – – – – – – LCD32B SEG4 – – – – – – LCD32B SEG3 – – – – – – LCD32B SEG2 Seiko Epson Corporation 7-18 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 97: P8 Port Group

P8yMUX = 0x3 name GPIO (Function 0) (Function 1) (Function 2) (Function 3) Peripheral Peripheral Peripheral Peripheral – – – – – – LCD32B SEG1 – – – – – – LCD32B SEG0 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-19 (Rev. 1.1) -

Page 98: P9 Port Group

P9yMUX = 0x1 P9yMUX = 0x2 P9yMUX = 0x3 name GPIO (Function 0) (Function 1) (Function 2) (Function 3) Peripheral Peripheral Peripheral Peripheral – – – – SVD2 Ch.1 EXSVD1 – – (VBUS_MON) Seiko Epson Corporation 7-20 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 99: Pd Port Group

Peripheral Peripheral Peripheral Peripheral SWCLK – – – – – – – – – – – – – – – – OSC3 – – – – – – OSC4 – – Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 7-21 (Rev. 1.1) -

Page 100: Common Registers Between Port Groups

7–4 CLKDIV[3:0] R/WP 3–2 KRSTCFG[1:0] R/WP 1–0 CLKSRC[1:0] R/WP PPORTINTFGRP 15–10 – 0x00 – – (P Port Interrupt Flag P9INT Group Register) P8INT P7INT P6INT P5INT P4INT P3INT P2INT P1INT P0INT Seiko Epson Corporation 7-22 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 101: Universal Port Multiplexer (Upmux)

4. Initialize the peripheral circuit. 5. Set the PPORTPxFNCSEL.PxyMUX[1:0] bits of the I/O port to 0x1. (Select peripheral I/O function 1) 6. Set the PPORTPxMODSEL.PxSELy bit of the I/O port to 1. (Enable peripheral I/O function) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 102: Control Registers

Note: Do not assign a peripheral input function to two or more I/O ports. Although the I/O ports output the same waveforms when an output function is assigned to two or more I/O port, a skew oc- curs due to the internal delay. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 103: Watchdog Timer (Wdt2)

CLK_WDT2 supply is suspended, the register retains the status before DEBUG mode was entered. If the WDT2CLK.DBRUN bit = 1, the CLK_WDT2 supply is not suspended and WDT2 will keep operating in DEBUG mode. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 104: Operations

1. Write 0x0096 to the SYSPROT.PROT[15:0] bits. (Remove system protection) 2. Write 0xa to the WDT2CTL.WDTRUN[3:0] bits. (Stop WDT2) 3. Write a value other than 0x0096 to the SYSPROT.PROT[15:0] bits. (Set system protection) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 105: Operations In Halt And Sleep Modes

IOSC OSC1 OSC3 EXOSC 1/65,536 1/128 1/65,536 1/32,768 1/32,768 1/16,384 1/16,384 1/8,192 1/8,192 (Note) The oscillation circuits/external input that are not supported in this IC cannot be selected as the clock source. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 106: Wdt2 Control Register

Always 0x0 is read if a value other than 0xa is written. Since an NMI or reset may be generated immediately after running depending on the counter value, WDT2 should also be reset concurrently when running WDT2. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 107: Wdt2 Counter Compare Match Register

These bits set the NMI/reset generation cycle. The value set in this register is compared with the 10-bit counter value while WDT2 is running, and an NMI or reset is generated when they are matched. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 108: Real-Time Clock (Rtca)

If the port is shared with the RTCA output function and other functions, the RTCA function must be assigned to the port. For more information, refer to the “I/O Ports” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-1 (Rev. 1.1) -

Page 109: Clock Settings

· · · · · · · · · · · · 0x3e 59.1 0x7e -1.9 0x3f 60.1 0x7f -1.0 Minimum resolution: 1 ppm, Correction rate range: -61.0 to 60.1 ppm Seiko Epson Corporation 10-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 110: Operations

3. Write 1 to the RTCAINTF.ALARMIF bit to clear the alarm interrupt flag. 4. Write 1 to the RTCAINTE.ALARMIE bit to enable alarm interrupts. When the real-time clock counter reaches the alarm time set in Step 2, an alarm interrupt occurs. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-3 (Rev. 1.1) -

Page 111: Real-Time Clock Counter Operations

The stopwatch consists of 1/100-second and 1/10-second counters and these counters perform counting up in incre- ments of approximate 1/100 and 1/10 seconds with the count-up patterns shown in Figure 10.4.4.1. Seiko Epson Corporation 10-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 112: Interrupts

1 Hz counter value. • An alarm interrupt occurs after a lapse of 1/256 second from matching between the AM/PM (in 12H mode), hour, minute, and second counter value and the alarm setting value. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-5 (Rev. 1.1) -

Page 113: Control Registers

This bit executes the 30-second correction time adjustment function. 1 (W): Execute 30-second correction 0 (W): Ineffective 1 (R): 30-second correction is executing. 0 (R): 30-second correction has finished. (Normal operation) Seiko Epson Corporation 10-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 114: Rtca Control Register (High Byte)

1 as well. However, no correcting operation is performed. RTCA Second Alarm Register Register name Bit name Initial Reset Remarks RTCAALM1 – – – 14–12 RTCSHA[2:0] 11–8 RTCSLA[3:0] 7–0 – 0x00 – Bit 15 Reserved Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-7 (Rev. 1.1) -

Page 115: Rtca Hour/Minute Alarm Register

BCD code. RTCA Stopwatch Control Register Register name Bit name Initial Reset Remarks RTCASWCTL 15–12 BCD10[3:0] – 11–8 BCD100[3:0] 7–5 – – SWRST Read as 0. 3–1 – – – SWRUN Seiko Epson Corporation 10-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 116: Rtca Second/1Hz Register

10-second digit and the 1-second digit of the second counter, respectively. The setting/read values are a BCD code within the range from 0 to 59. Note: Be sure to avoid writing to the RTCASEC.RTCSH[2:0]/RTCSL[3:0] bits while the RTCACTLL. RTCBSY bit = 1. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-9 (Rev. 1.1) -

Page 117: Rtca Hour/Minute Register

1 to 12 in 12H mode or 0 to 23 in 24H mode. Note: Be sure to avoid writing to the RTCAHUR.RTCHH[1:0]/RTCHL[3:0] bits while the RTCACTLL. RTCBSY bit = 1. Bit 7 Reserved Seiko Epson Corporation 10-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 118: Rtca Month/Day Register

The day of the week counter is a base-7 counter and the setting/read values are 0x0 to 0x6. Table 10.6.2 lists the correspondence between the count value and day of the week. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-11 (Rev. 1.1) -

Page 119: Rtca Interrupt Flag Register

The following shows the correspondence between the bit and interrupt: RTCAINTF.RTCTRMIF bit: Theoretical regulation completion interrupt RTCAINTF.SW1IF bit: Stopwatch 1 Hz interrupt RTCAINTF.SW10IF bit: Stopwatch 10 Hz interrupt RTCAINTF.SW100IF bit: Stopwatch 100 Hz interrupt Bits 11–9 Reserved Seiko Epson Corporation 10-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 120: Rtca Interrupt Enable Register

The following shows the correspondence between the bit and interrupt: RTCAINTE.RTCTRMIE bit: Theoretical regulation completion interrupt RTCAINTE.SW1IE bit: Stopwatch 1 Hz interrupt RTCAINTE.SW10IE bit: Stopwatch 10 Hz interrupt RTCAINTE.SW100IE bit: Stopwatch 100 Hz interrupt Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 10-13 (Rev. 1.1) - Page 121 RTCAINTE.T1DAYIE bit: 1-day interrupt RTCAINTE.T1HURIE bit: 1-hour interrupt RTCAINTE.T1MINIE bit: 1-minute interrupt RTCAINTE.T1SECIE bit: 1-second interrupt RTCAINTE.T1_2SECIE bit: 1/2-second interrupt RTCAINTE.T1_4SECIE bit: 1/4-second interrupt RTCAINTE.T1_8SECIE bit: 1/8-second interrupt RTCAINTE.T1_32SECIE bit: 1/32-second interrupt Seiko Epson Corporation 10-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 122: Supply Voltage Detector (Svd2)

- Continuous operation is also possible. Figure 11.1.1 shows the configuration of SVD2. Table 11.1.1 SVD2 Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 2 channels (Ch.0 and Ch.1) -

Page 123: Input Pin And External Connection

SLEEP mode and SVD2 Ch.n stops with the register settings maintained at those before entering SLEEP mode. After the CPU returns to normal mode, CLK_SVD2_n is supplied and the SVD2 Ch.n operation re- sumes. Seiko Epson Corporation 11-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 124: Clock Supply During Debugging

SVD2_nCTL.MODEN bit = 1, wait for at least SVD circuit response time before reading the SVD2_nINTF. SVDDT bit (refer to “Supply Voltage Detector Characteristics, SVD circuit response time t ” in the “Electrical Characteristics” chapter). Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 11-3 (Rev. 1.1) -

Page 125: Svd2 Operations

Voltage detection operating status SVD2_nINTF.SVDDT Power supply voltage rise detection interrupt : Level set using the SVD2_nCTL.SVDC[4:0] bits : Voltage detection masking time : Voltage detection operation Figure 11.4.2.1 SVD2 Operations Seiko Epson Corporation 11-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 126: Svd2 Interrupt And Reset

SVDMD[1:0] Cleared to 0 to set continuous operation mode. MODEN The set value (1) is retained. SVD2_nINTF SVDIF The status (1) before being reset is retained. SVD2_nINTE SVDIE Cleared to 0. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 11-5 (Rev. 1.1) -

Page 127: Control Registers

– 2–1 SVDMD[1:0] MODEN Bit 15 VDSEL This bit selects the power supply voltage to be detected by SVD2 Ch.n. 1 (R/WP): Voltage applied to the EXSVDn pin 0 (R/WP): V Seiko Epson Corporation 11-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 128 1 (R/W): Enable (Start detection operations) 0 (R/W): Disable (Stop detection operations) After this bit has been altered, wait until the value written is read out from this bit without subsequent operations being performed. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 11-7 (Rev. 1.1)

-

Page 129: Svd2 Ch.n Status And Interrupt Flag Register

• To prevent generating unnecessary interrupts, the corresponding interrupt flag should be cleared before enabling interrupts. Seiko Epson Corporation 11-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 130: 16-Bit Timers (T16)

• A clock source and clock division ratio for generating the count clock are selectable. • Repeat mode or one-shot mode is selectable. • Can generate counter underflow interrupts. Figure 12.1.1 shows the configuration of a T16 channel. Table 12.1.1 T16 Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 4 channels (Ch.0–Ch.3) -

Page 131: Clock Settings

(Set reload data (counter preset data)) 5. Set the following bits when using the interrupt: - Write 1 to the T16_nINTF.UFIF bit. (Clear interrupt flag) - Set the T16_nINTE.UFIE bit to 1. (Enable underflow interrupt) Seiko Epson Corporation 12-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 132: Counter Underflow

At the same time the counter stops, the T16_ nCTL.PRUN bit is cleared automatically. Select this mode to stop the counter after an interrupt has occurred once, such as for checking a specific lapse of time. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 12-3 (Rev. 1.1) -

Page 133: Counter Value Read

Bits 7–4 CLKDIV[3:0] These bits select the division ratio of the T16 Ch.n operating clock (counter clock). Bits 3–2 Reserved Bits 1–0 CLKSRC[1:0] These bits select the clock source of T16 Ch.n. Seiko Epson Corporation 12-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 134: T16 Ch.n Control Register

PRESET MODEN Bits 15–9 Reserved Bit 8 PRUN This bit starts/stops the timer. 1 (W): Start timer 0 (W): Stop timer 1 (R): Timer is running 0 (R): Timer is idle Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 12-5 (Rev. 1.1) -

Page 135: T16 Ch.n Reload Data Register

This bit indicates the T16 Ch.n underflow interrupt cause occurrence status. 1 (R): Cause of interrupt occurred 0 (R): No cause of interrupt occurred 1 (W): Clear flag 0 (W): Ineffective Seiko Epson Corporation 12-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 136: T16 Ch.n Interrupt Enable Register

This bit enables T16 Ch.n underflow interrupts. 1 (R/W): Enable interrupts 0 (R/W): Disable interrupts Note: To prevent generating unnecessary interrupts, the corresponding interrupt flag should be cleared before enabling interrupts. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 12-7 (Rev. 1.1) -

Page 137: Uart (Uart2)

• Input pin can be pulled up with an internal resistor. • The output pin is configurable as an open-drain output. Figure 13.1.1 shows the UART2 configuration. Table 13.1.1 UART2 Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 2 channels (Ch.0 and Ch.1) -

Page 138: Input/Output Pins And External Connections

(Clock source selection) - UART2_nCLK.CLKDIV[1:0] bits (Clock division ratio selection = Clock frequency setting) The UART2 operating clock should be selected so that the baud rate generator will be configured easily. Seiko Epson Corporation 13-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 139: Clock Supply In Sleep Mode

(UART2_nMOD.STPB bit = 1). Parity function The parity function is configured using the UART2_nMOD.PREN and UART2_nMOD.PRMD bits. Table 13.4.1 Parity Function Setting UART2_nMOD.PREN bit UART2_nMOD.PRMD bit Parity function Odd parity Even parity Non parity Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-3 (Rev. 1.1) -

Page 140: Operations

7. Configure the DMA controller and set the following UART2 control bits when using DMA transfer: - Write 1 to the DMA transfer request enable bits in the UART2_nTBEDMAEN and UART2_nRB1FDMAEN registers. (Enable DMA transfer requests) Seiko Epson Corporation 13-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 141: Data Transmission

Read the UART2_nINTF.TBEIF bit UART2_nINTF.TBEIF = 1 ? Write transmit data to the UART2_nTXD register Transmit data remained? Wait for an interrupt request (UART2_nINTF.TBEIF = 1) Figure 13.5.2.2 Data Transmission Flowchart Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-5 (Rev. 1.1) -

Page 142: Data Reception

UART2_nINTF.RB1FIF bit to 1 (receive buffer one byte full). If the sec- ond data is received without reading the first data, the UART2_nINTF.RB2FIF bit is set to 1 (receive buffer two bytes full). Seiko Epson Corporation 13-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 143: Irda Interface

Set the UART2_nMOD.IRMD bit to 1 to use the IrDA interface. Data transfer control is identical to that for normal interface even if the IrDA interface function is enabled. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-7 (Rev. 1.1) -

Page 144: Receive Errors

The interrupt flag will be set when the first data byte already loaded is read out after the data that encountered an error is transferred to the second byte entry of the receive data buffer. Seiko Epson Corporation 13-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 145: Parity Error

Transmit buffer empty Transmit buffer empty flag When transmit data written Writing transmit data (UART2_nINTF.TBEIF) to the transmit data buffer is transferred to the shift register Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-9 (Rev. 1.1) -

Page 146: Control Registers

(Note) The oscillation circuits/external input that are not supported in this IC cannot be selected as the clock source. Note: The UART2_nCLK register settings can be altered only when the UART2_nCTL.MODEN bit = 0. Seiko Epson Corporation 13-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 147: Uart2 Ch.n Mode Register

This bit sets the data length. 1 (R/W): 8 bits 0 (R/W): 7 bits Bit 2 PREN This bit enables the parity function. 1 (R/W): Enable parity function 0 (R/W): Disable parity function Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-11 (Rev. 1.1) -

Page 148: Uart2 Ch.n Baud-Rate Register

Note: If the UART2_nCTL.MODEN bit is altered from 1 to 0 while sending/receiving data, the data being sent/received cannot be guaranteed. When setting the UART2_nCTL.MODEN bit to 1 again after that, be sure to write 1 to the UART2_nCTL.SFTRST bit as well. Seiko Epson Corporation 13-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 149: Uart2 Ch.n Transmit Data Register

This bit indicates the receiving status. (See Figure 13.5.3.1.) 1 (R): During receiving 0 (R): Idle Bit 8 TBSY This bit indicates the sending status. (See Figure 13.5.2.1.) 1 (R): During sending 0 (R): Idle Bit 7 Reserved Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-13 (Rev. 1.1) -

Page 150: Uart2 Ch.n Interrupt Enable Register

UART2_nINTE.PEIE bit: Parity error interrupt UART2_nINTE.OEIE bit: Overrun error interrupt UART2_nINTE.RB2FIE bit: Receive buffer two bytes full interrupt UART2_nINTE.RB1FIE bit: Receive buffer one byte full interrupt UART2_nINTE.TBEIE bit: Transmit buffer empty interrupt Seiko Epson Corporation 13-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 151: Uart2 Ch.n Transmit Buffer Empty Dma Request Enable Register

(Ch.0–Ch.15) when a receive buffer one byte full state has occurred. 1 (R/W): Enable DMA transfer request 0 (R/W): Disable DMA transfer request Each bit corresponds to a DMA controller channel. The high-order bits for the unimplemented chan- nels are ineffective. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 13-15 (Rev. 1.1) -

Page 152: Synchronous Serial Interface (Spia)

• Slave mode is capable of being operated in SLEEP mode allowing wake-up by an SPIA interrupt. • Input pins can be pulled up/down with an internal resistor. Figure 14.1.1 shows the SPIA configuration. Table 14.1.1 SPIA Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 1 channel (Ch.0) -

Page 153: Input/Output Pins And External Connections

SDIn #SPISS0 SPICLKn #SPISS1 #SPISS #SPISS2 External SPI master device External SPI slave devices SPICLK SPICLK #SPISS SPICLK Figure 14.2.2.2 Connections between SPIA in Slave Mode and External SPI Master Device Seiko Epson Corporation 14-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 154: Pin Functions In Master Mode And Slave Mode

16-bit timer channel and converts it to the SPICLKn. The 16-bit timer must be run with an appro- priate reload data set. The SPICLKn frequency (baud rate) and the 16-bit timer reload data are calculated by the equations shown below. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-3 (Rev. 1.1) -

Page 155: Clock Supply During Debugging

SDIn SDOn (Master mode) SDOn (Slave mode) SDOn (Slave mode) Writing data to the SPIA_nTXD register Figure 14.3.3.1 SPI Clock Phase and Polarity (SPIA_nMOD.LSBFST bit = 0, SPIA_nMOD.CHLN[3:0] bits = 0x7) Seiko Epson Corporation 14-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 156: Data Format

6. Configure the DMA controller and set the following SPIA control bits when using DMA transfer: - Write 1 to the DMA transfer request enable bits in the SPIA_nTBEDMAEN and SPIA_nRBFDMAEN registers. (Enable DMA transfer requests) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-5 (Rev. 1.1) -

Page 157: Data Transmission In Master Mode

Data (W) → SPIA_nTXD Data (W) → SPIA_nTXD Software operations Data (W) → SPIA_nTXD 1 (W) → SPIA_nINTF.TENDIF Figure 14.5.2.1 Example of Data Sending Operations in Master Mode (SPIA_nMOD.CHLN[3:0] bits = 0x7) Seiko Epson Corporation 14-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 158 Transfer destination SPIA_nTXD register address Control data dst_inc 0x3 (no increment) dst_size 0x1 (haflword) src_inc 0x1 (+2) src_size 0x1 (halfword) R_power 0x0 (arbitrated for every transfer) n_minus_1 Number of transfer data cycle_ctrl 0x1 (basic transfer) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-7 (Rev. 1.1)

-

Page 159: Data Reception In Master Mode

Software operations SPIA_nRXD → Data (R) Data (W) → SPIA_nTXD SPIA_nRXD → Data (R) 1 (W) → SPIA_nINTF.TENDIF Figure 14.5.3.1 Example of Data Receiving Operations in Master Mode (SPIA_nMOD.CHLN[3:0] bits = 0x7) Seiko Epson Corporation 14-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 160 Control data dst_inc 0x3 (no increment) dst_size 0x1 (haflword) src_inc 0x3 (no increment) src_size 0x1 (halfword) R_power 0x0 (arbitrated for every transfer) n_minus_1 Number of transfer data cycle_ctrl 0x1 (basic transfer) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-9 (Rev. 1.1)

-

Page 161: Terminating Data Transfer In Master Mode

Writing transmit data is not a trigger to start data transfer. Therefore, it is not necessary to write dummy data to the transmit data buffer when performing data reception only. Seiko Epson Corporation 14-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 162: Terminating Data Transfer In Slave Mode

1. Wait for an end-of-transmission interrupt (SPIA_nINTF.TENDIF bit = 1). Or determine end of transfer via the received data. 2. Set the SPIA_nCTL.MODEN bit to 0 to disable the SPIA Ch.n operations. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-11 (Rev. 1.1) -

Page 163: Interrupts

SPIA_nINTF.BSY SPIA_nMOD register CPOL bit CPHA bit SPICLKn SDOn SPICLKn SDOn SPIA_nINTF.TENDIF Writing data to the SPIA_nTXD register Figure 14.6.1 SPIA_nINTF.BSY and SPIA_nINTF.TENDIF Bit Set Timings (when SPIA_nMOD.CHLN[3:0] bits = 0x7) Seiko Epson Corporation 14-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 164: Dma Transfer Requests

16 bits 15 bits 14 bits 13 bits 12 bits 11 bits 10 bits 9 bits 8 bits 7 bits 6 bits 5 bits 4 bits 3 bits 2 bits Setting prohibited Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-13 (Rev. 1.1) -

Page 165: Spia Ch.n Control Register

Note: If the SPIA_nCTL.MODEN bit is altered from 1 to 0 while sending/receiving data, the data being sent/received cannot be guaranteed. When setting the SPIA_nCTL.MODEN bit to 1 again after that, be sure to write 1 to the SPIA_nCTL.SFTRST bit as well. Seiko Epson Corporation 14-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 166: Spia Ch.n Transmit Data Register

These bits indicate the SPIA interrupt cause occurrence status. 1 (R): Cause of interrupt occurred 0 (R): No cause of interrupt occurred 1 (W): Clear flag (OEIF, TENDIF) 0 (W): Ineffective Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 14-15 (Rev. 1.1) -

Page 167: Spia Ch.n Interrupt Enable Register

Ch.15) when a receive buffer full state has occurred. 1 (R/W): Enable DMA transfer request 0 (R/W): Disable DMA transfer request Each bit corresponds to a DMA controller channel. The high-order bits for the unimplemented chan- nels are ineffective. Seiko Epson Corporation 14-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 168: Quad Synchronous Serial Interface (Qspi)

• Can issue a DMA transfer request when a receive buffer full, a transmit buffer empty, or a memory mapped ac- cess (32-bit read) occurs. Figure 15.1.1 shows the QSPI configuration. Table 15.1.1 QSPI Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 1 channel (Ch.0) -

Page 169: Input/Output Pins And External Connections

In this case, GPIO pins other than #QSPISSn can also be used as the slave select output ports to connect the QSPI to more than one external QSPI device. Figures 15.2.2.1 to 15.2.2.7 show connection diagrams between the QSPI in each mode and external QSPI devices. Seiko Epson Corporation 15-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 170 External dual-I/O SPI slave devices QSDIOn0 SDIO0 QSPICLKn SPICK #SPISS SDIO1 SDIO0 SPICK Figure 15.2.2.3 Connections between QSPI in Register Access Master Mode and External Dual-I/O SPI Slave Devices Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-3 (Rev. 1.1)

- Page 171 #SPISS2 External single-I/O SPI master device SPICK SPICK External single-I/O SPI slave devices #SPISS SPICK Figure 15.2.2.5 Connections between QSPI in Slave Mode and External Single-I/O SPI (Legacy SPI) Master Device Seiko Epson Corporation 15-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 172 QSDIO2 QSDIO2 QSDIO1 QSDIO1 QSDIO0 QSDIO0 QSPICLK QSPICLK External QSPI slave devices #QSPISS QSDIO3 QSDIO2 QSDIO1 QSDIO0 QSPICLK Figure 15.2.2.7 Connections between QSPI in Slave Mode and External QSPI Master Device Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-5 (Rev. 1.1)

-

Page 173: Pin Functions In Master Mode And Slave Mode

To supply CLK_QSPIn to the QSPI, the 16-bit timer clock source must be enabled in the clock generator. It does not matter how the T16_mCTL.MODEN and T16_mCTL.PRUN bits of the corresponding 16-bit timer channel are set (1 or 0). Seiko Epson Corporation 15-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 174: Clock Supply During Debugging

(Master mode, output) QSDIOn (Slave mode, output) QSDIOn (Slave mode, output) QSDIOn Writing data to the QSPI_nTXD register Figure 15.3.3.1 QSPI Clock Phase and Polarity (QSPI_nMOD.LSBFST bit = 0, QSPI_nMOD.CHLN[3:0] bits = 0x7) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-7 (Rev. 1.1) -

Page 175: Data Format

Figure 15.4.2 Data Format Selection for Dual Transfer Mode Using the QSPI_nMOD.LSBFST Bit (QSPI_nMOD.TMOD[1:0] bits = 0x1, QSPI_nMOD.CHDL[3:0] bits = 0x7, QSPI_nMOD.CHLN[3:0] bits = 0x7, QSPI_nMOD.CPOL bit = 0, QSPI_nMOD.CPHA bit = 0) Seiko Epson Corporation 15-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 176: Operations

(QSPI_nCTL.DIR bit = 1). The number of data transfer clocks is configured with the QSPI_nMOD. CHLN[3:0] bits. Since four data lines are used for data transfer, the data bit length (number of clocks) is obtained by dividing the number of transfer data bits by four. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-9 (Rev. 1.1) -

Page 177: Memory Mapped Access Mode

The QSPI treats the data cycle as 2 cycles including 2 driving cycles. (QSPI_nMOD.CHDL[3:0] bits = 0x1, QSPI_nMOD.CHLN[3:0] bits = 0x1) Figure 15.5.2.1 XIP Example - Spansion S25FL128S Quad I/O Read Command Sequence (3-byte address, 0xeb [ExtAdd = 0], LC = 0b00) Seiko Epson Corporation 15-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 178: Initialization

- QSPI_nMOD.NOCLKDIV bit (Select master mode operating clock) - QSPI_nMOD.LSBFST bit (Select MSB first/LSB first) - QSPI_nMOD.CPHA bit (Select clock phase) - QSPI_nMOD.CPOL bit (Select clock polarity) - QSPI_nMOD.MST bit (Select master/slave mode) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-11 (Rev. 1.1) -

Page 179: Data Transmission In Master Mode

Even if the clock is being output from the QSPICLKn pin, the next transmit data can be written to the QSPI_ nTXD register after making sure the QSPI_nINTF.TBEIF bit is set to 1. Seiko Epson Corporation 15-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 180 DMA transfer in advance so that transmit data will be transferred to the QSPI_nTXD register. For more information on DMA, refer to the “DMA Controller” chapter. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-13 (Rev. 1.1)

-

Page 181: Data Reception In Register Access Master Mode

TMOD[1:0] bits is received when the QSPI_nINTF.RBFIF bit is set to 1, the QSPI_nRXD register is overwritten with the newly received data and the previously received data is lost. In this case, the QSPI_nINTF.OEIF bit is set. Seiko Epson Corporation 15-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 182 DMA controller and dummy data is transferred from the specified memory to the QSPI_ nTXD register via DMA Ch.x when the QSPI_nINTF.TBEIF bit is set to 1 (transmit buffer empty). Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-15 (Rev. 1.1)

- Page 183 DMA controller transfers data from the QSPI_nRXD register and then writes another dummy byte to the QSPI_nTXD register, allowing the QSPI to read the next data. 13. Wait for a DMA interrupt. Seiko Epson Corporation 15-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 184: Data Reception In Memory Mapped Access Mode

If the address in the memory mapped access area that is continuous to the previous read address is read when the FIFO contains the prefetched data (FIFO data ready status), the prefetched data is sent to the internal system bus with the HREADY signal held high (zero-wait read). Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-17 (Rev. 1.1) - Page 185 Data cycle 3 QSPI_nMOD register Dummy cycle Data cycle 1 (prefetching) (prefetching) CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.1 Data Receiving Operation in Memory Mapped Access Mode - First 32-bit Read Seiko Epson Corporation 15-18 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 186 HRDATA fifo_read_level Data cycle Data cycle QSPI_nMOD register (for n+8) (prefetching) CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.2 Data Receiving Operation in Memory Mapped Access Mode - 32-bit Sequential Read Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-19 (Rev. 1.1)

- Page 187 Dummy cycle (low-order 16 bits) (for n) (for n+8) QSPI_nMOD register #QSPISSn CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.3 Data Receiving Operation in Memory Mapped Access Mode - 32-bit Non-Sequential Read Seiko Epson Corporation 15-20 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 188 HADDR HTRANS HSIZE HREADY HRDATA QSPI_nMOD register Dummy cycle Data cycle CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.4 Data Receiving Operation in Memory Mapped Access Mode - First 8/16-bit Read Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-21 (Rev. 1.1)

- Page 189 HCLK HSEL HADDR HTRANS HSIZE HREADY HRDATA QSPI_nMOD register Data cycle CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.5 Data Receiving Operation in Memory Mapped Access Mode - 8/16-bit Sequential Read Seiko Epson Corporation 15-22 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 190 Address cycle Dummy cycle Data cycle (low-order 16 bits) QSPI_nMOD register #QSPISSn CPOL bit CPHA bit QSPICLKn QSDIOn[3:0] Figure 15.5.6.6 Data Receiving Operation in Memory Mapped Access Mode - 8/16-bit Non-Sequential Read Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-23 (Rev. 1.1)

- Page 191 The transfer source/destination and control data must be set for the DMA controller and the relevant DMA channel must be enabled to start a DMA transfer in advance. For more information on DMA, refer to the “DMA Controller” chapter. Seiko Epson Corporation 15-24 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 192: Terminating Memory Mapped Access Operations

1. Wait for an end-of-transmission interrupt (QSPI_nINTF.TENDIF bit = 1). 2. Set the QSPI_nCTL.MODEN bit to 0 to disable the QSPI Ch.n operations. 3. Stop the 16-bit timer to disable the clock supply to QSPI Ch.n. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-25 (Rev. 1.1) -

Page 193: Data Transfer In Slave Mode

Data (W) → QSPI_nTXD Software operations QSPI_nRXD → Data (R) QSPI_nRXD → Data (R) Figure 15.5.9.1 Example of Data Transfer Operations in Slave Mode (QSPI_nMOD.CHDL[3:0] bits = QSPI_nMOD.CHLN[3:0] bits = 0x3) Seiko Epson Corporation 15-26 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 194: Terminating Data Transfer In Slave Mode

The QSPI_nINTF register also contains the BSY and MMABSY bits that indicate the QSPI operating status in reg- ister access and memory mapped access modes, respectively. Figure 15.6.1 shows the QSPI_nINTF.BSY, QSPI_ nINTF.MMABSY and QSPI_nINTF.TENDIF bit set timings. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-27 (Rev. 1.1) -

Page 195: Dma Transfer Requests

When a 32-bit data is prefetched into the FIFO When the FIFO read access FIFO data FIFO data ready flag in memory mapped access mode level is cleared to 0 ready (internal signal) Seiko Epson Corporation 15-28 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 196: Control Registers

Note: When using the QSPI in slave mode, the QSPI_nMOD.CHDL[3:0] bits should be set to the same value as the QSPI_nMOD.CHLN[3:0] bits. Bits 11–8 CHLN[3:0] These bits set the number of clocks for data transfer. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-29 (Rev. 1.1) - Page 197 0 (R/W): MSB first Bit 2 CPHA Bit 1 CPOL These bits set the QSPI clock phase and polarity. For more information, refer to “QSPI Clock (QSPI- CLKn) Phase and Polarity.” Seiko Epson Corporation 15-30 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 198: Qspi Ch.n Control Register

Note: If the QSPI_nCTL.MODEN bit is altered from 1 to 0 while sending/receiving data, the data being sent/received cannot be guaranteed. When setting the QSPI_nCTL.MODEN bit to 1 again after that, be sure to write 1 to the QSPI_nCTL.SFTRST bit as well. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-31 (Rev. 1.1) -

Page 199: Qspi Ch.n Transmit Data Register

Transmit/receive busy 0 (R): Idle Bit 6 MMABSY This bit indicates the QSPI memory mapped access operating status. 1 (R): Memory mapped access state machine busy 0 (R): Idle Bits 5–4 Reserved Seiko Epson Corporation 15-32 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 200: Qspi Ch.n Interrupt Enable Register

Ch.15) when a transmit buffer empty state has occurred. 1 (R/W): Enable DMA transfer request 0 (R/W): Disable DMA transfer request Each bit corresponds to a DMA controller channel. The high-order bits for the unimplemented chan- nels are ineffective. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-33 (Rev. 1.1) -

Page 201: Qspi Ch.n Receive Buffer Full Dma Request Enable Register

11 clocks 10 clocks 9 clocks 8 clocks 7 clocks 6 clocks 5 clocks 4 clocks 3 clocks 2 clocks 1 clock Note: These bits specify a number of system clocks. Seiko Epson Corporation 15-34 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 202: Qspi Ch.n Remapping Start Address High Register

Flash memory in the memory mapped access mode. This setting is re- quired to output the XIP confirmation bit to Micron Flash memories or to output the mode byte to Spansion Flash memories. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-35 (Rev. 1.1) - Page 203 The QSDIOn[3:0] pins are used. Dual transfer mode The QSDIOn[1:0] pins are used. The QSDIOn[3:2] pins are not used. Single transfer mode The QSDIOn[1:0] pins are used. The QSDIOn[3:2] pins are not used. Seiko Epson Corporation 15-36 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 204: Qspi Ch.n Mode Byte Register

Note: In memory mapped access mode, the mode byte is always output from the LSB first. When us- ing a Flash memory that expects the mode byte to be output from the MSB first, write the mode byte to this register in reverse bit order. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 15-37 (Rev. 1.1) -

Page 205: C (I2C)

• The input filter for the SDA and SCL inputs does not comply with the standard for removing noise spikes less than 50 ns. Figure 16.1.1 shows the I2C configuration. Table 16.1.1 I2C Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 2 channels (Ch.0 and Ch.1) -

Page 206: Input/Output Pins And External Connections

• The internal pull-up resistors for the I/O ports cannot be used for pulling up SDA and SCL. • When the I2C is set into master mode, no other master device can be connected to the I bus. Seiko Epson Corporation 16-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 207: Clock Settings

16.3.3.1). Note: The I C bus transfer rate is limited to 100 kbit/s in standard mode or 400 kbit/s in fast mode. Do not set a transfer rate exceeding the limit. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-3 (Rev. 1.1) -

Page 208: Operations

- Set the I2C_nCTL.MST bit to 0. (Set slave mode) - Set the I2C_nCTL.SFTRST bit to 1. (Execute software reset) - Set the I2C_nCTL.MODEN bit to 1. (Enable I2C Ch.n operations) Seiko Epson Corporation 16-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 209: Data Transmission In Master Mode

I2C_nINTF.NACKIF bit = 1 (NACK received), the I2C Ch.n generates a repeated START condi- tion. When the repeated START condition has been generated, the I2C_nINTF.STARTIF and I2C_nINTF. TBEIF bits are both set to 1 same as when a START condition has been generated. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-5 (Rev. 1.1) - Page 210 Last data sent? Retry? Write 1 to the I2C_nCTL.TXSTOP bit Write data to the I2C_nTXD register Wait for an interrupt request (I2C_nINTF.STOPIF = 1) Figure 16.4.2.2 Master Mode Data Transmission Flowchart Seiko Epson Corporation 16-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 211: Data Reception In Master Mode

10. (When DMA is not used) Repeat Steps 6 to 8 until the end of data reception. 11. Wait for a STOP condition interrupt (I2C_nINTF.STOPIF bit = 1). Clear the I2C_nINTF.STOPIF bit by writing 1 after the interrupt has occurred. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-7 (Rev. 1.1) - Page 212 S: START condition, Sr: Repeated START condition, P: STOP condition, A: ACK, A: NACK, Saddr/R: Slave address + R(1), Data n: 8-bit data Figure 16.4.3.1 Example of Data Receiving Operations in Master Mode Seiko Epson Corporation 16-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 213 Transfer destination Memory address to which the last received data is stored Control data dst_inc 0x0 (+1) dst_size 0x0 (byte) src_inc 0x3 (no increment) src_size 0x0 (byte) R_power 0x0 (arbitrated for every transfer) n_minus_1 Number of receive data cycle_ctrl 0x1 (basic transfer) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-9 (Rev. 1.1)

-

Page 214: 10-Bit Addressing In Master Mode

Clear the I2C_nINTF.STARTIF bit by writing 1 after the interrupt has occurred. 9. Write the first address to the I2C_nTXD.TXD[7:1] bits and 1 that represents READ as the data transfer di- rection to the I2C_nTXD.TXD0 bit. 10. Perform data reception. Seiko Epson Corporation 16-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 215: Data Transmission In Slave Mode

Go to Step 6 when a STOP condition interrupt has occurred. ii. Go to Step 2 when a START condition interrupt has occurred. 6. Clear the I2C_nINTF.STOPIF bit and then terminate data sending operations. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-11 (Rev. 1.1) - Page 216 A: ACK, A: NACK, Saddr/R: Slave address + R(1), Saddr/W: Slave address + W(0), STARTIF = 1 Data n: 8-bit data Figure 16.4.5.1 Example of Data Sending Operations in Slave Mode Seiko Epson Corporation 16-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 217: Data Reception In Slave Mode

I2C Ch.n sends an ACK and pulls down SCL to low. The received data in the shift register is transferred to the receive data buffer and the I2C_nINTF.RBFIF and I2C_nINTF.BYTEENDIF bits are both set to 1. After that, the received data can be read out from the I2C_nRXD register. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-13 (Rev. 1.1) - Page 218 Wait for an interrupt request (I2C_nINTF.RBFIF = 1) Last data received next? Write 1 to the I2C_nCTL.TXNACK bit Read receive data from the I2C_nRXD register Last data received? Figure 16.4.6.2 Slave Mode Data Reception Flowchart Seiko Epson Corporation 16-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 219: Slave Operations In 10-Bit Address Mode

If SDA does not change from low when the I2C Ch.n outputs the ninth clock, it is regarded as an automatic bus clearing failure. In this case, the I2C Ch.n clears the I2C_nCTL.TXSTART bit to 0 and sets both the I2C_nINTF. ERRIF and I2C_nINTF.STARTIF bits to 1. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-15 (Rev. 1.1) -

Page 220: Error Detection

4 <Master mode only> When 1 is written to the I2C_nCTL. I2C_nINTF.ERRIF = 1 TXSTART bit while the I2C_nINTF.BSY bit = 0 (Refer to “Au- Automatic bus clearing I2C_nCTL.TXSTART = 0 tomatic Bus Clearing Operation.”) failure I2C_nINTF.STARTIF = 1 Seiko Epson Corporation 16-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 221: Interrupts

Master mode BRT + 3 CLK_I2Cn TXSTART = 1 TXSTART = 0 STARTIF = 1 Slave mode Address matching the I2C_nOADR register BSY = 1 TR = 0/1 STARTIF = 1 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-17 (Rev. 1.1) -

Page 222: Dma Transfer Requests

16.7 Control Registers I2C Ch.n Clock Control Register Register name Bit name Initial Reset Remarks I2C_nCLK 15–9 – 0x00 – – DBRUN 7–6 – – 5–4 CLKDIV[1:0] 3–2 – – 1–0 CLKSRC[1:0] Seiko Epson Corporation 16-18 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 223: I2C Ch.n Mode Register

Note: The I2C_nMOD register settings can be altered only when the I2C_nCTL.MODEN bit = 0. I2C Ch.n Baud-Rate Register Register name Bit name Initial Reset Remarks I2C_nBR 15–8 – 0x00 – – – – 6–0 BRT[6:0] 0x7f Bits 15–7 Reserved Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-19 (Rev. 1.1) -

Page 224: I2C Ch.n Own Address Register

STOP condition has been generated. This bit is automatically cleared when the bus free time (t defined in the I C Specifications) has elapsed after the STOP condition has been generated. Seiko Epson Corporation 16-20 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 225: I2C Ch.n Transmit Data Register

Register name Bit name Initial Reset Remarks I2C_nRXD 15–8 – 0x00 – – 7–0 RXD[7:0] 0x00 Bits 15–8 Reserved Bits 7–0 RXD[7:0] The receive data buffer can be read through these bits. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-21 (Rev. 1.1) -

Page 226: I2C Ch.n Status And Interrupt Flag Register

Bit 0 TBEIF These bits indicate the I2C interrupt cause occurrence status. 1 (R): Cause of interrupt occurred 0 (R): No cause of interrupt occurred 1 (W): Clear flag 0 (W): Ineffective Seiko Epson Corporation 16-22 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 227: I2C Ch.n Interrupt Enable Register

I2C_nINTE.NACKIE bit: NACK reception interrupt I2C_nINTE.STOPIE bit: STOP condition interrupt I2C_nINTE.STARTIE bit: START condition interrupt I2C_nINTE.ERRIE bit: Error detection interrupt I2C_nINTE.RBFIE bit: Receive buffer full interrupt I2C_nINTE.TBEIE bit: Transmit buffer empty interrupt Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 16-23 (Rev. 1.1) -

Page 228: I2C Ch.n Transmit Buffer Empty Dma Request Enable Register

(Ch.0–Ch.15) when a receive buffer full state has occurred. 1 (R/W): Enable DMA transfer request 0 (R/W): Disable DMA transfer request Each bit corresponds to a DMA controller channel. The high-order bits for the unimplemented chan- nels are ineffective. Seiko Epson Corporation 16-24 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 229: 16-Bit Pwm Timers (T16B)

- The capture circuit captures counter values using external/software trigger signals and generates interrupts or DMA requests. (Can be used to measure external event periods/cycles.) Figure 17.1.1 shows the T16B configuration. Table 17.1.1 T16B Channel Configuration of S1C31W74 Item S1C31W74 Number of channels 2 channels (Ch.0 and Ch.1) -

Page 230: Input/Output Pins

If the port is shared with the T16B pin and other functions, the T16B input/output function must be assigned to the port before activating T16B. For more information, refer to the “I/O Ports” chapter. Seiko Epson Corporation 17-2 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 231: Clock Settings

Figure 17.3.4.1 Count Timing (During Count Up Operation) Note: When running the counter using the event counter clock, two dummy clocks must be input be- fore the first counting up/down can be performed. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-3 (Rev. 1.1) -

Page 232: Operations

5. Set the following bits when using the interrupt: - Write 1 to the interrupt flags in the T16B_nINTF register. (Clear interrupt flags) - Set the interrupt enable bits in the T16B_nINTE register to 1. (Enable interrupts) Seiko Epson Corporation 17-4 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) -

Page 233: Counter Block Operations

T16Bn, one of the operations shown below is required to read correctly by the CPU. - Read the counter value twice or more and check to see if the same value is read. - Stop the timer and then read the counter value. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-5 (Rev. 1.1) - Page 234 0x0000 and continues counting down from the new MAX value after a counter under- flow occurs. In one-shot down count mode, the counter returns to the MAX value if a counter underflow occurs and stops automatically at that point. Seiko Epson Corporation 17-6 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 235 0x0000 and then starts counting up to the new MAX val- In one-shot up/down count mode, the counter stops automatically when it reaches 0x0000 during count down operation. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-7 (Rev. 1.1)

-

Page 236: Comparator/Capture Block Operations

When the counter reaches the MAX value in comparator mode, the T16B_nINTF.CNTMAXIF bit (counter MAX interrupt flag) is set to 1. When the counter reaches 0x0000, the T16B_nINTF.CNTZEROIF bit (counter zero interrupt flag) is set to 1. Seiko Epson Corporation 17-8 S1C31W74 TECHNICAL MANUAL (Rev. 1.1) - Page 237 Count cycle = — — — — — — — — [s] (Eq. 17.2) CLK_T16B CLK_T16B Where T16B_nCCRm register setting value (0 to 65,535) MAX: T16B_nMC register setting value (0 to 65,535) : Count clock frequency [Hz] CLK_T16B Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-9 (Rev. 1.1)

- Page 238 (T16B_nMC register) Compare period Compare buffer Counter value Time 0x0000 CNTMAXIF = 1 CNTMAXIF = 1 CNTMAXIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 Seiko Epson Corporation 17-10 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 239 Count cycle MAX value (T16B_nMC register) Compare period Compare buffer Counter value Time 0x0000 CNTMAXIF = 1 CNTMAXIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-11 (Rev. 1.1)

- Page 240 Compare buffer value Compare period Time 0x0000 CNTZEROIF = 1 CNTZEROIF = 1 CNTZEROIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 Seiko Epson Corporation 17-12 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 241 Time 0x0000 CNTMAXIF = 1 CNTZEROIF = 1 CNTMAXIF = 1 CNTZEROIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-13 (Rev. 1.1)

- Page 242 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 CMPCAPmIF = 1 (Note that the T16B_nINTF.CMPCAPmIF/CNTMAXIF/CNTZEROIF bit clearing operations via software are omitted from the figure.) Figure 17.4.3.2 Compare Buffer Operations Seiko Epson Corporation 17-14 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 243 If the captured data stored in the T16B_nCCRm register is overwritten by the next trigger when the T16B_ nINTF.CMPCAPmIF bit is still set, an overwrite error occurs (the T16B_nINTF.CAPOWmIF bit is set). Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-15 (Rev. 1.1)

- Page 244 Capture trigger signal T16B_nCCRm.CC[15:0] Capturing operation (2) Asynchronous capture mode (When T16B_nCCCTLm.CAPTRG[1:0] bits = 0x3) Count clock T16B_nTC.TC[15:0] Capture trigger signal T16B_nCCRm.CC[15:0] Capturing operation Figure 17.4.3.4 Synchronous Capture Mode/Asynchronous Capture Mode Seiko Epson Corporation 17-16 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

-

Page 245: Tout Output Control

Furthermore, when the T16B_nCCCTLm.TOUTMT bit is set to 1, the TOUT circuit uses the MATCH signal output from another system in the circuit pair (0 and 1, 2 and 3, 4 and 5). This makes it possible to change the signal twice within a counter cycle. Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-17 (Rev. 1.1) - Page 246 Software control mode (0x0) Set mode (0x1) Toggle/reset mode (0x2) Set/reset mode (0x3) Toggle mode(0x4) Reset mode (0x5) Toggle/set mode (0x6) Reset/set mode (0x7) ∗ ( ) indicates the T16B_nCCCTLm.TOUTMD[2:0] bit-setting value. Seiko Epson Corporation 17-18 S1C31W74 TECHNICAL MANUAL (Rev. 1.1)

- Page 247 Set/reset mode (0x3) Toggle mode(0x4) Reset mode (0x5) Toggle/set mode (0x6) Reset/set mode (0x7) ∗ ( ) indicates the T16B_nCCCTLm.TOUTMD[2:0] bit-setting value. Figure 17.4.4.2 TOUT Output Waveform (T16B_nCCCTLm.TOUTMT bit = 0) Seiko Epson Corporation S1C31W74 TECHNICAL MANUAL 17-19 (Rev. 1.1)