Table of Contents

Advertisement

Quick Links

To our customers,

st

On April 1

, 2010, NEC Electronics Corporation merged with Renesas Technology

Corporation, and Renesas Electronics Corporation took over all the business of both

companies. Therefore, although the old company name remains in this document, it is a valid

Renesas Electronics document. We appreciate your understanding.

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

Old Company Name in Catalogs and Other Documents

Renesas Electronics website: http://www.renesas.com

st

April 1

, 2010

Renesas Electronics Corporation

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Renesas PFESiP/V850EP1

- Page 1 On April 1 , 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

- Page 2 Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as “Specific”...

- Page 3 User's Manual PFESiP/V850EP1 ® 32-bit Microcontroller Dedicated to PFESiP EP-1 Product Data Document No. A19069EJ2V0UM00 (2nd Edition) Date published September 2009 NS 2008...

- Page 4 [MEMO] User's Manual A19069EJ2V0UM...

- Page 5 NOTES FOR CMOS DEVICES VOLTAGE APPLICATION WAVEFORM AT INPUT PIN Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between V (MAX) and V (MIN) due to noise, etc., the device may malfunction.

- Page 6 PFESiP is a registered trademark of NEC Electronics Corporation in Japan, Germany, and United Kingdom. All other trademarks or registered trademarks are the property of their respective owners. • The information in this document is current as of September, 2009. The information is subject to change without notice.

- Page 7 Major Revisions in This Edition Location Contents p.16 Modification of Table.1-8 Input Clock Timing p.17 Modification of 1.7.1 (2) Output Clock The mark <R> shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field. To obtain the latest documents when designing, contact an NEC sales office or a distributor.

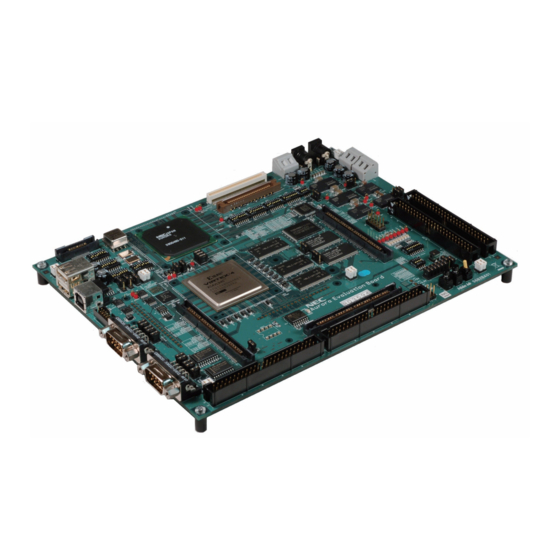

- Page 8 PREFACE Readers This manual is intended for users who understand the functions of the microcontroller function chip with an on-chip V850E2 CPU core (PFESiP/V850EP1) and wish to evaluate developing PFESiP EP-1 Series products using the chip. Purpose This manual is intended to give users an understanding of the electrical specifications of the PFESiP/V850EP1.

- Page 9 This manual PFESiP/V850EP1 Hardware (CPU Function) User’s Manual A19070E PFESiP/V850EP1 Hardware (USB Function) User’s Manual A19071E PFESiP/V850EP1 Hardware USB Function Sample Software Application Note A19349E Documents related to PFESiP EP-1 Evaluation Board Document Name Document No. PFESiP EP-1 Evaluation Board Technical Information User’s Manual A19350E PFESiP EP-1 Evaluation Board Lite Technical Information User’s Manual...

-

Page 10: Table Of Contents

CONTENTS CHAPTER 1 PRODUCT SPECIFCATIONS....................11 1.1 Terminology ..............................11 1.2 Absolute Maximum Rating Value .......................13 1.3 Recommended Operating Range.......................13 1.4 DC Characteristics ............................14 1.5 Pull-up/Pull-down Resistance ........................15 1.6 Power Supply Application/Interruption Procedure ..................15 1.7 AC Characteristics ............................16 1.7.1 Clock pins ............................16 1.7.2 Cautions on maximum operating frequency..................19 1.7.3 External memory interface pins .......................19 1.7.4 SiP internal-connection bus interface pins ..................32... - Page 11 LIST OF FIGURE Figure No. Title Page Output Clock Timing ............................17 Reset Timing ..............................18 Access Timing (SRAM, External ROM, External I/O) ..................20 Read Timing (SRAM, External ROM, External I/O) ..................21 Write Timing (SRAM, External ROM, External I/O)..................22 DMA Flyby Transfer Timing (SRAM → External I/O) ..................23 DMA Flyby Transfer Timing (External I/O →...

- Page 12 Pull-up/Pull-down Resistance (V Input Clock Timing ............................... 16 Output Clock Timing ............................17 1-10 Reset Timing................................ 18 1-11 PFESiP/V850EP1 Maximum Operating Frequency on Operating Conditions............19 1-12 Access Timing (SRAM, External ROM, External I/O)................... 19 1-13 SDRAM Access Timing............................26 1-14 Bus Hold Timing ..............................

-

Page 13: Chapter 1 Product Specifcations

= 0 V. High-level input voltage For voltage applied to the input of PFESiP/V850EP1, this value indicates the voltage of the high-level state in which the input buffer operates normally. ● If voltage greater than the MIN. value is applied, the input voltage is assured to be high level. - Page 14 CHAPTER 1 PRODUCT SPECIFCATIONS Table 1-3. Terminology for DC Characteristics Item Symbol Definition Static current consumption In the state where there is no voltage change in the input and output pins, indicates the current that flows in from the power supply pin at the specified power supply voltage. OFF state output current For a 3-state output, this value indicates the current that flows through the output pin at the specified voltage when the output is at high impedance.

-

Page 15: Absolute Maximum Rating Value

CHAPTER 1 PRODUCT SPECIFCATIONS 1.2 Absolute Maximum Rating Value Table 1-4. Absolute Maximum Rating Values Item Symbol Definition Item Unit −0.5 to +2.0 Power supply voltage 1.5 V system −0.5 to +4.6 3.3 V system Input/Output voltage 3.3 V buffer, V <... -

Page 16: Dc Characteristics

CHAPTER 1 PRODUCT SPECIFCATIONS 1.4 DC Characteristics = 3.3 ±0.3 V, T = 0 to +70 °C) Table 1-6. DC Characteristics (V Item Symbol Conditions MIN. TYP. MAX. Unit Supply current Normal (200 MHz operation) HALT IDLE Note 1 Output short-circuit current = GND −250 ±... -

Page 17: Pull-Up/Pull-Down Resistance

116.4 kΩ 1.6 Power Supply Application/Interruption Procedure The PFESiP/V850EP1 has two power supply pins: a power supply pin for internal units (IV ) and a power supply pin for external pins (EV ). The I/O status of an alternate-function I/O pin may be undefined outside the range in which the operation is guaranteed. -

Page 18: Ac Characteristics

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7 AC Characteristics 1.7.1 Clock pins (1) Input clock Table 1-8. Input Clock Timing Parameter Symbol Conditions MIN. MAX. Unit − X1 input cycle 20.83 SCLK PCLKIN input frequency SPCLK DCK input cycle − SDCK <R> UCLK input frequency 48 -1500 ppm 48+1500 ppm... - Page 19 CHAPTER 1 PRODUCT SPECIFCATIONS <R> (2) Output clock Table 1-9. Output Clock Timing Parameter Symbol Conditions MIN. MAX. Unit − BUSCLK output cycle Output load capacitance: 30 pF and less BCYC BUSCLK high-level width 0.5T−2.7 0.5T+2.7 WKH1 BUSCLK low-level width 0.5T−2.7 0.5T+2.7 WKL1...

-

Page 20: Reset Timing

CHAPTER 1 PRODUCT SPECIFCATIONS (3) Reset timing Table 1-10. Reset Timing Parameter Symbol Conditions MIN. MAX. Unit RESET pin low-level width WRSL Caution Sufficiently evaluate the oscillation stabilization time. Figure 1-2. Reset Timing < t > WRSL RESETZ (Input) User's Manual A19069EJ2V0UM... -

Page 21: Cautions On Maximum Operating Frequency

In an application design using the PFESiP/V850EP1, these load conditions may be exceeded, depending on the configuration of external circuits. In such a case, the electrical specifications will be inferior to those of the PFESiP/V850EP1 by itself. 1.7.3 External memory interface pins (1) Access Timing (SRAM, external ROM, external I/O) Table 1-12. - Page 22 CHAPTER 1 PRODUCT SPECIFCATIONS (a) Access timing (SRAM, external ROM, external I/O) Figure 1-3. Access Timing (SRAM, External ROM, External I/O) BUSCLK (output) < t > < t > A0-A25, CSZ0-CSZ7 (output) <t > <t > < t > DKBSL DKBSH DKBSL BCYSTZ (output)

-

Page 23: Read Timing (Sram, External Rom, External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (b) Read timing (SRAM, external ROM, external I/O) Figure 1-4. Read Timing (SRAM, External ROM, External I/O) TASW BUSCLK (output) < t > < t > A0-A25, CSZ0-CSZ7 Note (output) < t > DKWRH WRZ0-WRZ3, WRSTBZ (output) <... -

Page 24: Write Timing (Sram, External Rom, External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (c) Write timing (SRAM, external ROM, external I/O) Figure 1-5. Write Timing (SRAM, External ROM, External I/O) TASW BUSCLK (output) < t > < t > A0-A25, CSZ0-CSZ7 Note (output) < t > DKRDL < t >... -

Page 25: Dma Flyby Transfer Timing (Sram → External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (d) DMA flyby transfer timing (SRAM → external I/O) Figure 1-6. DMA Flyby Transfer Timing (SRAM → External I/O) TASW BUSCLK (output) < t > < t > A0-A25, CSZ0-CSZ7 Note (output) < t > < t >... -

Page 26: Dma Flyby Transfer Timing (External I/O → Sram Transfer)

CHAPTER 1 PRODUCT SPECIFCATIONS (e) DMA flyby transfer timing (external I/O→SRAM transfer) Figure 1-7. DMA Flyby Transfer Timing (External I/O → SRAM Transfer) TASW BUSCLK (output) < t > < t > A0-A25, CSZ0-CSZ7 Note (output) < t > < t >... -

Page 27: Page Rom Access Timing

CHAPTER 1 PRODUCT SPECIFCATIONS (f) Page ROM access timing Figure 1-8. Page ROM Access Timing TASW TPRW BUSCLK (output) < t > < t > CSZ0-CSZ7 (output) < t > < t > < t > A0-A25 (output) < t >... - Page 28 CHAPTER 1 PRODUCT SPECIFCATIONS (2) SDRAM access timing Table 1-13. SDRAM Access Timing Parameter Symbol MIN. MAX. Unit Address delay time (from BUSCLK↑) 11.0 BCYSTZ delay time (from BUSCLK↑) DKBC Note CSZn delay time (from BUSCLK↑) 11.0 DKCS SDRASZ delay time (from BUSCLK↑) 11.0 DKRAS SDCASZ delay time (from BUSCLK↑)

-

Page 29: Read Timing (Sdram Access)

CHAPTER 1 PRODUCT SPECIFCATIONS (a) Read timing (SDRAM access) Figure 1-9. Read Timing (SDRAM Access) TACT TBCW TREAD TLATE TLATE BUSCLK (output) < t > < t > < t > < t > D KA D KA A0-A25 (output) <... -

Page 30: Write Timing (Sdram Access)

CHAPTER 1 PRODUCT SPECIFCATIONS (b) Write timing (SDRAM access) Figure 1-10. Write Timing (SDRAM Access) TACT BUSCLK (output) < t > < t > < t > < t > < t > < t > < t > D KA A0-A25 (output) <... -

Page 31: Refresh Timing (Sdram Access)

CHAPTER 1 PRODUCT SPECIFCATIONS (c) Refresh Timing (SDRAM access) Figure 1-11. Refresh Timing (SDRAM Access) TRPW ALLPRE REFW REFW REFW TREF REFW TRPW TRPW TRPW BUSCLK (output) < t > < t > A0-A25 (output) < t > < t >... -

Page 32: Bus Hold Timing

CHAPTER 1 PRODUCT SPECIFCATIONS (3) Bus hold timing Table 1-14. Bus Hold Timing Parameter Symbol MIN. MAX. Unit HLDRQZ setup time (to BUSCLK ↑ ) − SHRK HLDRQZ hold time (from BUSCLK ↑ ) − HKHR Delay time from BUSCLK ↑ to HLDAKZ 11.0 DKHA HLDRQZ high-level width... - Page 33 CHAPTER 1 PRODUCT SPECIFCATIONS Figure 1-12. Bus Hold Timing BUSCLK (output) < t > HKHR < t > < t > HKH R SHRK < t > SHRK < t > < t > SHRK WHQH HLDRQZ (input) < t >...

-

Page 34: Sip Internal-Connection Bus Interface Pins

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.4 SiP internal-connection bus interface pins (1) Access timing (SRAM, external ROM, external I/O) Table 1-15. Access Timing (SRAM, External ROM, External I/O) Parameter Symbol MIN. MAX. Unit Address, SCSZ0-SCSZ3 output delay time (from SBUSCLK ↑ ) 11.0 SRDZ, SIORDZ ↓... -

Page 35: Base Access Timing (Sram, External Rom, External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (a) Base access timing (SRAM, external ROM, external I/O) Figure 1-13. Base Access Timing (SRAM, External ROM, External I/O) SBUSCLK (output) <t > < t > SA0-SA20, SCSZ0-SCSZ3 (output) <t > <t > < t > DKBSL D KBSH DKBSL... -

Page 36: Read Timing (Sram, External Rom, External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (b) Read timing (SRAM, external ROM, external I/O) Figure 1-14. Read Timing (SRAM, External ROM, External I/O) TASW SBUSCLK (output) < t > < t > SA0-SA20, SCSZ0-SCSZ3 Note (output) < t > DKWRH SWRZ0-SWRZ1, SWRSTBZ (output) <... -

Page 37: Write Timing (Sram, External Rom, External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (c) Write timing (SRAM, external ROM, external I/O) Figure 1-15. Write Timing (SRAM, External ROM, External I/O) TASW SBUSCLK (output) < t > < t > SA0-SA20, SCSZ0-SCSZ3 Note (output) < t > DKRDL < t >... -

Page 38: Dma Flyby Transfer Timing (Sram → External I/O)

CHAPTER 1 PRODUCT SPECIFCATIONS (d) DMA flyby transfer timing (SRAM → external I/O) Figure 1-16. DMA Flyby Transfer Timing (SRAM → External I/O) TASW SBUSCLK (output) < t > < t > SA0-SA20, SCSZ0-SCSZ1 Note (output) < t > < t >... -

Page 39: Dma Flyby Transfer Timing (External I/O → Sram Transfer)

CHAPTER 1 PRODUCT SPECIFCATIONS (e) DMA flyby transfer timing (external I/O → SRAM transfer) Figure 1-17. DMA Flyby Transfer Timing (External I/O → SRAM Transfer) TASW SBUSCLK (output) < t > < t > SA0-SA20, SCSZ0-SCSZ3 Note (output) < t >... -

Page 40: Page Rom Access Timing

CHAPTER 1 PRODUCT SPECIFCATIONS (f) Page ROM access timing Figure 1-18. Page ROM Access Timing TASW TPRW SBUSCLK (output) < t > < t > SCSZ0-SCSZ3 (output) < t > < t > < t > SA0-SA20 (output) < t >... -

Page 41: Bus Hold Timing

CHAPTER 1 PRODUCT SPECIFCATIONS (2) Bus hold timing Table 1-16. Bus Hold Timing Parameter Symbol MIN. MAX. Unit SHLDRQZ setup time (to SBUSCLK ↑ ) − SHRK SHLDRQZ hold time (from SBUSCLK ↑ ) − HKHR Delay time from SBUSCLK ↑ to SHLDAKZ 11.0 DKHA SHLDRQZ high-level width... - Page 42 CHAPTER 1 PRODUCT SPECIFCATIONS Figure 1-19. Bus Hold Timing SBUSCLK (output) < t > HKHR < t > < t > HKHR SH RK < t > SHRK < t > < t > SHRK WHQH SHLDRQZ (input) < t >...

-

Page 43: Dma Interface Pins

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.5 DMA interface pins (3) BUSCLK-synchronization signal The second DMA transfer request disable timing in single transfer is described below. Table 1-17. BUSCLK-synchronization Signal Parameter Symbol MIN. MAX. Unit DMARQZ0-DMARQZ3 setup time(from BUSCLK ↑ ) − SDRK To DMAAKZ ↓... -

Page 44: Sip Internal-Connection Dma Interface Pins

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.6 SiP internal-connection DMA interface pins (1) SBUSCLK-synchronization signal The second DMA transfer request disable timing in single transfer is described below. Table 1-18. SBUSCLK-synchronization Signal Parameter Symbol MIN. MAX. Unit SDMARQZ0-SDMARQZ3 setup time (from SBUSCLK ↑ ) −... -

Page 45: Bus Reset Output Puns

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.7 Bus reset output puns (1) External Memory interface pins The access timing of the external bus reset output pun is described below. Table 1-19. External Bus Reset Output Pin Parameter Symbol MIN. MAX. Unit VBRESTOZ output delay time (from VBCLKOUT ↓ ) 10.0 DVBRESZ Figure 1-22. -

Page 46: Csi Interface Pins

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.8 CSI interface pins The access timing of CSI (Clock-synchronized Serial Interface) is shown below. CSI has a master mode and a slave mode, and they show their respective timings. The operating timing varies depending on CKP and DAP settings. Table 1-21. - Page 47 CHAPTER 1 PRODUCT SPECIFCATIONS Figure 1-24. CSI Access Timing (CKP, DAP = 00) < t > CSICYC Note SCKn (output) < t > < t > No te (input) < t > < t > Note (output) n = 0, 1 Note Remark Broken lines indicate high impedance.

- Page 48 CHAPTER 1 PRODUCT SPECIFCATIONS Figure 1-26. CSI Access Timing (CKP, DAP = 10) < t > CSICYC Note SCKn (output) < t > < t > Not e (input) < t > < t > Note (output) n = 0, 1 Note Remark Broken lines indicate high impedance.

-

Page 49: N-Wire Interface Pins

CHAPTER 1 PRODUCT SPECIFCATIONS 1.7.9 N-Wire interface pins (1) Trace interface The access timing of the trace interface is shown below. Table 1-23. Trace Interface Parameter Symbol MIN. MAX. Unit Note TRCDATA output delay time (from TRCCLK ↑ ) × 0.5 + 3.5 DTRCDATA CCLK Note... -

Page 50: Debug Serial Interface

CHAPTER 1 PRODUCT SPECIFCATIONS (2) Debug serial interface The access timing of the debug serial interface is shown below. Table 1-24. Debug Serial Interface Parameter Symbol MIN. MAX. Unit DMS input setup time (to DCK ↑ ) 10.0 − SDMS DMS input hold time (from DCK ↑... -

Page 51: A/D Converter Characteristics

CHAPTER 1 PRODUCT SPECIFCATIONS 1.8 A/D Converter Characteristics Table 1-25. A/D Converter Characteristics (EV = AV = AV = 3.0 to 3.6 V, EV = AV = AV = 0 V) REFP REFM Parameter Symbol Conditions MIN. TYP. MAX. Unit −... -

Page 52: Power Supply Application/Interruption Procedure

CHAPTER 1 PRODUCT SPECIFCATIONS 1.9 Power Supply Application/Interruption Procedure Pin capacitance is the sum of the interface block capacitance and the package characteristic capacitance. Table 1-27 and 1-28 show the capacitance (C ) of the interface blocks. The pin capacitance is calculated by the following formula: Pin capacitance (C ) = interface block capacitance (C ) + capacitance (C... -

Page 53: Chapter 2 Internal Sscg-Pll Characteristics

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS The SSCG-PLL incorporated in PFESiP/V850EP1 is a spread spectrum clock generator used to suppress noise, and is effective in reducing the peak value of electromagnetic interference (EMI) noise. 2.1 Block Diagram Figure 2-1. SSCG-PLL Block Diagram... -

Page 54: Electrical Specifications

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS 2.2 Electrical Specifications 2.2.1 Recommended operating range Parameter Symbol Conditions MIN. MAX. Unit − Oscillation Block Input Frequency 50.0 Input Frequency − 200.0 PFD Input Frequency − Input Duty duty MULT = n / m / p −... -

Page 55: Setting Sscg-Pll Operation Mode With Pins

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS 2.3 Setting SSCG-PLL Operation Mode with Pins To set SSCG-PLL Operation mode, PFESiP/V850EP1 has the following pins. Set the following pins to satisfy the specified operating conditions before turning on power. Pin Name Internal Signal... -

Page 56: Pllm0-Pllm6, Plln0-Plln2, Pllp0-Pllp1 (Pllm, N, P-Counter Select)

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS 2.3.1 PLLM0-PLLM6, PLLN0-PLLN2, PLLP0-PLLP1 (PLLM, N, P-counter select) These pins set the multiplication factor of an internal PLL. PLLM0 to PLLM6, and PLLP0 and PLLP1 are directly connected to AAPLSCGH of the internal PLL. PLLN0 to PLLN2 are connected to AAPLSCGH, while 92 is added to them, because the input range of AAPLSCGH is 92 to 99 in decimal form. -

Page 57: Ssmdl0 To Ssmdl1 (Modulation Frequency Range) (Input)

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS 2.3.2 SSMDL0 to SSMDL1 (modulation frequency range) (input) Set SSCG-output modulation period. These pins are directly connected to MDL0 and MDL1 of AAPLSCGH. Table 2-2. Setting SSCG-output Modulation Period by SSMDL0 to SSMDL1 PLL13 PLL12 Modulation Period [kHz] SSMDL1 SSMDL0... -

Page 58: Plls0 To Plls1 (S-Selector) (Input)

CHAPTER 2 INTERNAL SSCG-PLL CHARACTERISTICS 2.3.4 PLLS0 to PLLS1 (S-selector) (input) Set the S-selector as below, according to the value of the PFD input frequency (fpfd) specified in Table 2-1 when these pins are used in frequency diffusion mode. Table 2-4. Setting the S-selector PLL18 PLL17 PFD Input Frequency [MHz]... -

Page 59: Chapter 3 Development Tools And Middleware

CHAPTER 3 DEVELOPMENT TOOLS AND MIDDLEWARE The following development tools and middleware are provided for developing systems using the PFESiP/V850EP1. 3.1 Development Tools Real-time OS Compiler Debugger Server In-circuit emulator Remark Note 1 RX850pro CCV850 MULTI rteserve RTE-2000-TP ( Midas lab Inc. ) No. - Page 60 [MEMO] User's Manual A19069EJ2V0UM...

- Page 61 For further information, please contact: NEC Electronics Corporation 1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/ [Asia & Oceania] [America] [Europe] NEC Electronics (China) Co., Ltd NEC Electronics America, Inc. NEC Electronics (Europe) GmbH 7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian 2880 Scott Blvd.

Need help?

Do you have a question about the PFESiP/V850EP1 and is the answer not in the manual?

Questions and answers