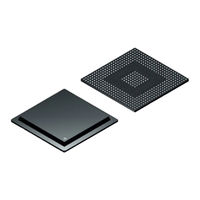

User Manuals: Renesas SuperH SH-4A Microcontroller

Manuals and User Guides for Renesas SuperH SH-4A Microcontroller. We have 2 Renesas SuperH SH-4A Microcontroller manuals available for free PDF download: Software Manual, User Manual

Renesas SuperH SH-4A Software Manual (472 pages)

32-Bit RISC Microcomputer

Brand: Renesas

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

-

Preface6

-

Features21

-

Appendix

35-

Usage Notes42

-

-

-

-

Usage Notes114

-

Features117

-

-

Data Formats118

-

-

-

Rounding128

-

Overview of MMU133

-

-

TLB Functions151

-

MMU Functions156

-

MMU Exceptions160

-

-

PMB Function174

-

Section 8 Caches179

-

Features179

-

-

Read Operation193

-

IC Two-Way Mode194

-

-

Store Queues202

-

-

Features207

-

-

Operation217

-

Usage Notes220

-

Page Conflict220

-

Sleep Mode220

-

-

CPU Instruction222

-

-

-

FPU Instruction374

-

Appendix

451 -

Section 8 Caches

460 -

-

Index465

-

Advertisement

Renesas SuperH SH-4A User Manual (416 pages)

Microcomputer Development Environment System

Brand: Renesas

|

Category: Computer Hardware

|

Size: 4 MB

Table of Contents

-

Components29

-

Overview44

-

Online Help78

-

CD-R82

-

System Check119

-

Debug Sessions141

-

General] Page156

-

Main Board] Page159

-

Bus Board] Page161

-

PC Breakpoints192

-

Eventpoints192

-

List] Sheet284

-

Tree] Sheet285

-

Notes290

-

Introduction319

-

Viewing Memory334

-

Break Function345

-

Trace Functions359

-

MMU Support380

-

What Next391

-

Maintenance395

-

Guarantee395

-

Appendix A Menus399