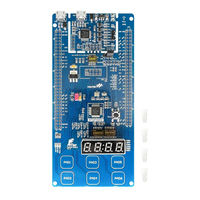

Holtek HT32F54253 Manuals

Manuals and User Guides for Holtek HT32F54253. We have 1 Holtek HT32F54253 manual available for free PDF download: User Manual

Holtek HT32F54253 User Manual (576 pages)

Brand: Holtek

|

Category: Microcontrollers

|

Size: 6 MB

Table of Contents

-

Introduction25

-

Overview25

-

Features25

-

Memory Map37

-

Introduction43

-

Features43

-

Page Erase46

-

Mass Erase48

-

Register Map53

-

Introduction69

-

Features70

-

Register Map74

-

Introduction80

-

Features82

-

Register Map89

-

Introduction115

-

Power-On Reset115

-

System Reset116

-

Register Map116

-

Introduction123

-

Features124

-

Register Map126

-

Introduction168

-

Features169

-

Lock Mechanism170

-

Register Map170

-

Introduction175

-

Features176

-

Register Map177

-

Introduction178

-

Features178

-

Register Map181

-

Introduction188

-

Features189

-

ADC Clock Setup190

-

Conversion Mode190

-

Data Format194

-

Analog Watchdog194

-

Interrupts195

-

Register Map196

-

Introduction214

-

Features214

-

Register Map217

-

Introduction223

-

Features224

-

Counter Mode224

-

Clock Controller226

-

Slave Controller229

-

Input Stage234

-

Output Stage237

-

Register Map248

-

Introduction285

-

Features286

-

Counter Mode287

-

Clock Controller291

-

Slave Controller293

-

Input Stage299

-

Output Stage301

-

Lock Level Table321

-

Register Map323

-

Introduction366

-

Features367

-

Counter Mode367

-

Clock Controller368

-

Slave Controller370

-

Input Stage374

-

Output Stage375

-

Register Map378

-

Introduction394

-

Features394

-

Repetitive Mode395

-

One Shot Mode396

-

Register Map397

-

Introduction400

-

Features400

-

Register Map404

-

Introduction410

-

Features411

-

Register Map413

-

Introduction419

-

Features420

-

Data Validity421

-

Arbitration424

-

Bus Error424

-

Address Snoop425

-

Operation Mode425

-

Register Map431

-

Introduction445

-

Features446

-

Master Mode446

-

Slave Mode446

-

SPI Dual Mode451

-

Status Flags453

-

Register Map456

-

Introduction468

-

Features469

-

Irda473

-

RS485 Mode475

-

Register Map479

-

Introduction494

-

Features495

-

Register Map498

-

Introduction506

-

Features506

-

AHB Master507

-

PDMA Channel507

-

Channel Transfer508

-

Channel Priority508

-

Transfer Request509

-

Address Mode509

-

Auto-Reload510

-

Register Map511

-

Divider (DIV)522

-

Introduction522

-

Features522

-

Register Map523

-

Introduction526

-

Features526

-

CRC Computation527

-

CRC with PDMA528

-

Register Map528

-

Introduction531

-

Features532

-

Register Map539

-

Touch Key547

-

Introduction547

-

Features547

-

Manual Mode548

-

Auto Scan Mode549

-

Register Map554

Advertisement