Xilinx Spartan-6 FPGA Series Manuals

Manuals and User Guides for Xilinx Spartan-6 FPGA Series. We have 7 Xilinx Spartan-6 FPGA Series manuals available for free PDF download: Design And Pin Planning Manual, User Manual, Getting Started

Xilinx Spartan-6 FPGA Series Design And Pin Planning Manual (72 pages)

Printed circuit boards

Brand: Xilinx

|

Category: Motherboard

|

Size: 10 MB

Table of Contents

Advertisement

Xilinx Spartan-6 FPGA Series User Manual (67 pages)

Brand: Xilinx

|

Category: Motherboard

|

Size: 2 MB

Table of Contents

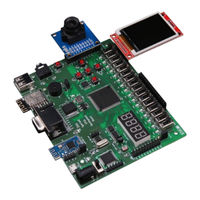

Xilinx Spartan-6 FPGA Series User Manual (40 pages)

Brand: Xilinx

|

Category: Control Unit

|

Size: 1 MB

Table of Contents

Advertisement

Xilinx Spartan-6 FPGA Series User Manual (55 pages)

Brand: Xilinx

|

Category: Motherboard

|

Size: 1 MB

Table of Contents

Xilinx Spartan-6 FPGA Series Getting Started (37 pages)

Brand: Xilinx

|

Category: Motherboard

|

Size: 4 MB

Table of Contents

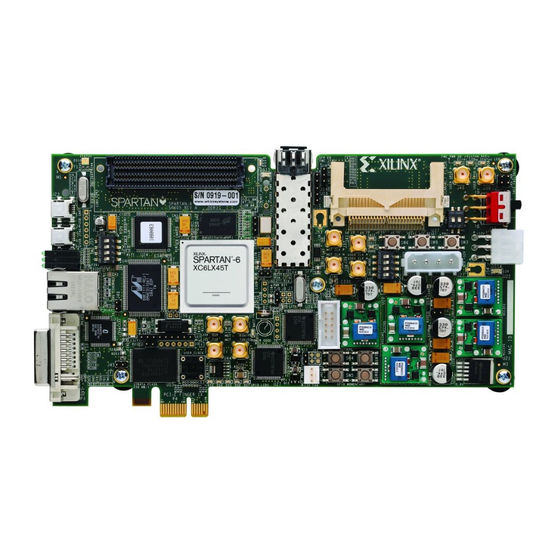

Xilinx Spartan-6 FPGA Series Getting Started (32 pages)

Evaluation Kit

Brand: Xilinx

|

Category: Motherboard

|

Size: 26 MB

Table of Contents

Xilinx Spartan-6 FPGA Series User Manual (40 pages)

FPGA GTP Transceiver Signal Integrity Simulation Kit

Brand: Xilinx

|

Category: Transceiver

|

Size: 4 MB