Advertisement

Quick Links

Advertisement

Subscribe to Our Youtube Channel

Summary of Contents for Analog Devices MAX96752

- Page 1 MAX96752 User Guide UG-2231 Revision 0 Rev 0; 5/24...

-

Page 2: Table Of Contents

TABLE OF CONTENTS About the User Guide ....................................2 Device Overview......................................2 Start-up and Programming Sequence ..............................2 Register Configuration Sequencing – MAX96752 ..........................2 Dual-View ........................................3 Pixel-Interleaved Dual-View Mode ............................... 4 Side-by-Side Dual-View Mode ................................5 Line Interleaved Dual-View Mode ................................ 6 Color Lookup Table (LUT) .................................. - Page 3 GPIO Pull-up and Pull-Down Resistor Setup ............................. 32 GPIO Output Driver Setup ................................... 33 Configuring GPIO Forwarding ................................33 GPIO Broadcasting ....................................33 GPIO Delay Compensation ................................. 34 Toggling GPIO Manually with Registers ............................. 34 www.analog.com Analog Devices | 3...

- Page 4 Monitoring Details .................................. 44 DDIO Error Reporting and Status ................................. 45 ERRB Configuration ..................................45 Latching Status Bits and Clearing Errors ............................45 Bandwidth Efficiency Optimization ................................ 45 Overview ......................................45 Calculating Bandwidth ..................................45 www.analog.com Analog Devices | 4...

- Page 5 Device Error Flags ....................................47 Complete Use Case Programming Examples ............................48 Use Case Example 1 .................................... 48 Use Case Example 1 Script ................................48 Use Case Example 2 .................................... 49 Use Case Example 2 Script ................................49 www.analog.com Analog Devices | 5...

-

Page 6: About The User Guide

Examples shown in this guide do not consider errata fixes that may be necessary to ensure reliable operation in production. To obtain errata documents, on the Analog Devices website, search for a specific part, and review the Documentation section. Make sure to include any relevant errata writes in the final production software. In addition to the errata, it is also important to have the latest revision of the GMSL device for testing. -

Page 7: Dual-View

VIDEO LOCK if there is video throughput. Video Lock indicates there is video output from the deserializer *These are the minimum configurations that need to be done to achieve video throughput through the MAX96752 deserializer. Dual-View Dual-view is a configurable feature that enables a single serializer to support two different video streams. A serializer with dual-view enabled can receive a video stream comprising two videos combined into a single frame. -

Page 8: Pixel-Interleaved Dual-View Mode

Pixel-Interleaved Dual-View Mode Pixel-interleaved mode (also known as Column-interleaved mode) separates the video stream by assigning every odd pixel to one stream and every even pixel to another stream (Figure 3). This includes the horizontal blanking, www.analog.com Analog Devices | 4... -

Page 9: Side-By-Side Dual-View Mode

The odd pixels are sent to one video stream and even are sent to another stream. Horizontal blanking is split symmetrically between streams, and vertical timing is maintained from superframe to the two subframe video streams. The PCLK is divided by two for each subframe. www.analog.com Analog Devices | 5... -

Page 10: Line Interleaved Dual-View Mode

LINE 1: VIDEO A LINE 1 LINE 2: VIDEO B LINE 1 LINE 3: VIDEO A LINE 2 VIDEO A PIXELS LINE 4: VIDEO B LINE 2 VIDEO B PIXELS TOTAL Figure 5. Line-Interleaved Dual-View Mode www.analog.com Analog Devices | 6... -

Page 11: Color Lookup Table (Lut)

Figure 6. RGB Pixel Data Translation using Color Lookup Tables (LUT) Configuration At power-up, the LUTs are assigned random values but are not enabled. The LUTs should first be configured via the appropriate register space(s) before setting the register enable bit. www.analog.com Analog Devices | 7... -

Page 12: Oldi Deserializers

0: Disabled (BLUE) translation Readback Restriction The following sequence is common in typical use cases: • Program the LUT translation values. • Readback the LUT translation values (to ensure proper programming). • Enable the LUT. www.analog.com Analog Devices | 8... -

Page 13: Enabling Luts

ID (Ex. Pipe X = 0b00, Pipe Y = 0b01, Pipe Z = 0b10, and Pipe U = 0b11). GMSL display deserializers have usually one video pipe which is also annotated as 2 bits representing the stream ID. By default, the MAX96752 serializer video pipes are turned on and stream ID 0b00 is selected. Table 4. MAX96752 Video Pipe Routing Registers... -

Page 14: Operation

The GMSL2 oLDI deserializer generates the oLDI clock output from the tracked and measured clock frequency of the video input at the connected serializer. Figure 7 shows the LVDS pulse positions with the oLDI clock. www.analog.com Analog Devices | 10... -

Page 15: Lvds Data Mapping

LVDS Data Mapping The following sections provide the LVDS data mapping for single- and dual-port oLDI output. Single Pixel per Clock Output TxOUT0 TxOUT1 TxOUT2 TxOUT3 Figure 8. Single oLDI Port Mapping (oLDI/Format 1) www.analog.com Analog Devices | 11... -

Page 16: Dual Pixel Per Clock Output

Figure 9. Single oLDI Port Mapping (VESA/Format 2) Dual Pixel per Clock Output The first pixel is mapped to TxOUTA. PREVIOUS CYCLE CURRENT CYCLE TxOUT0_A TxOUT1_A TxOUT2_A TxOUT3_A TxOUT0_B TxOUT1_B TxOUT2_B TxOUT3_B Figure 10. Dual oLDI Port Mapping (oLDI/Format 1) www.analog.com Analog Devices | 12... -

Page 17: Output Programming

40kHz triangular modulation frequency. It is possible to program the spread-spectrum percentage up to 4% with the config_spread_bit_ratio bitfield (register DPLL_3). Note: oLDI SSC mode programming is independent of the GMSL high-speed clock SSC mode. www.analog.com Analog Devices | 13... -

Page 18: Odd/Even Pixel Interleaving In Dual Oldi Mode

Figure 12. Serializer Single Link Mode with oLDI Deserializer Single or Dual Mode Figure 13, the serializer in pixel-interleaved dual-view mode receives a superframe from the video source. The dual-view block splits the superframe and transmits the pixel-interleaved data on the serial link. The oLDI www.analog.com Analog Devices | 14... - Page 19 The serializer in Figure 15 transmits a replicated video stream in GMSL2 dual link mode to two connected oLDI deserializers. Each oLDI deserializer outputs to one connected display in either single or dual oLDI mode. www.analog.com Analog Devices | 15...

- Page 20 HDMI Serializer OLDI Deserializer GMSL (Link A) 1x4 OLDI Display 1 OLDI TMDS Video HDMI Memory 1x4 OLDI Display 2 OLDI Figure 16. Single Video Stream with oLDI Deserializer Replication www.analog.com Analog Devices | 16...

-

Page 21: Configuration

Table 7 contains registers used to output polarity inversion and output pin mapping. Polarity is inverted on a lane- by-lane basis. The pin mapping registers enable programming the pin assignments for the oLDI output ports and www.analog.com Analog Devices | 17... - Page 22 0b000: Output from A0 0b001: Output from A1 0b010: Output from A2 Selects oLDI Port A Lane 1 output 0b011: Output from A3 0x1D1 LANE_SEL_A1[2:0] pins 0b100: Output from ACLK 0b101: Reserved 0b110: Reserved 0b111: Reserved www.analog.com Analog Devices | 18...

-

Page 23: Programming Examples

OLDI_FORMAT = Select the mapping format (oLDI or VESA) for the LVDS port OLDI_4TH_LANE = Select 24- or 18-bit output (i.e., 4- or 3-lane output port) OLDI_DUP = Select if the same video should be duplicated on both LVDS ports www.analog.com Analog Devices | 19... -

Page 24: Stream At Dual Oldi Output

Error Flags section for additional information. The following video receiver status registers and interrupts may also be used: • Line CRC interrupt (LCRC_ERR_FLAG). • Video block length error interrupt (VID_BLK_LEN_ERR). • Video sequence number error (VID_SEQ_ERR). www.analog.com Analog Devices | 20... -

Page 25: Debug Procedure

10µs delay from the write acknowledgement (ACK) to the next transaction is required. Port Access and Routing The MFPs shown in the table below are used for the I2C primary and pass-through channels. • MAX96752 Pins for I Default Function C Function Notes... -

Page 26: I 2 C Registers

When enabling a I C pass-through channel, other MFP functions must be disabled first. With MAX96752 the user can bring out the first pass-through I C channel (SDA1_RX1/SCL1_TX1) on pin 40/pin 42. The second pass-through I2C channel (SDA2_RX2/SCL2_TX2) can also be programmed on pin 27/ pin 29. Pass- through channels are enabled by setting the fields IIC_1_EN and IIC_2_EN in register 0x1. -

Page 27: Uart Control Channel

This mode prevents inadvertent programming of the serializer/deserializer registers and can be switched in and out of during normal operation. Port Access and Routing The MFPs shown in the table below are used for the UART primary and pass-through channels. Table 12. MAX96752 MFP pins for UART Default Function UART Function #1 Notes GPIO03... -

Page 28: Uart Registers

UART Registers Table 13. MAX96752 UART Registers Register Bits Decode Address 0x02 DIS_LOCAL_CC, Bit [5]: Disable primary UART Control Channel connection to RX and TX pins 0x02 DIS_REM_CC, Bit [4]: Disable access to remote device control-channel over GMSL link 0x03... -

Page 29: Mfp/Cfg Pin Setup For Spi

The table below shows some of the important setup registers for enabling SPI interface. Register block in the data sheet will have additional details for configuring the SPI main, subordinate, SCLK timings, etc.). See the programming script in the section below as an example. Table 14. MAX96752 SPI Register Settings Register Bitfield Name Bits... -

Page 30: Spi Initialization

SPI Example with Register Writes Below is the SPI setup example script for MAX96751 with its accompanying device MAX96752 (0x80 is the serializer address, 0x90 is the deserializer address), assuming micro-controller or external SPI main is on the serializer side*. - Page 31 *Note: If micro-controller or external SPI main is on the deserializer side, swap the Ser and Des register writes in the script. Figure 18 Figure 19 show MFP pins being used for SPI after running the above script. Figure 18. SPI MFP Pin Settings for MAX95751 www.analog.com Analog Devices | 27...

-

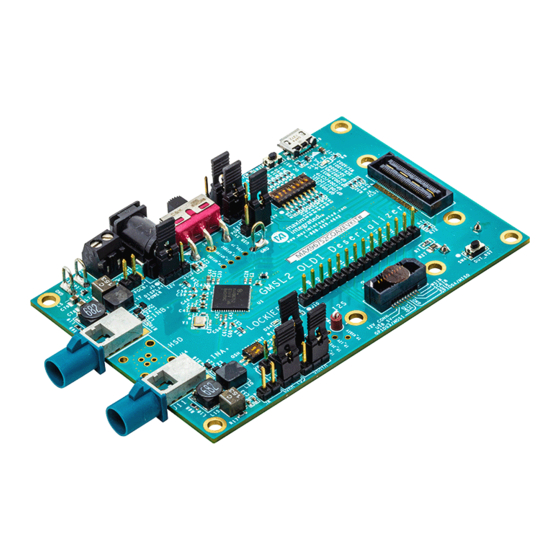

Page 32: Spi Example Using Gmsl Gui And Evaluation Boards

Figure 19. SPI MFP Pin Settings for MAX96752 SPI Example using GMSL GUI and Evaluation Boards • It is recommended to set the SCLK output rate equal or more than the SCLK input rate to avoid buffer overflow in the SER or DES. The SCLK rate can be set using register writes. -

Page 33: Data Integrity And Avoiding Buffer Overflow

After a SPI data byte is sent across the GMSL link, the GMSL device on the remote side will send the data out on the MFP pins. It will also send the data back across the link so that the external SPI main device can read back the data. www.analog.com Analog Devices | 29... - Page 34 SPI subordinate are available to be read.). Figure 22. SPI Transmission Example Each Rx and Tx SPI buffer has overflow detection logic with status bits that can be monitored by registers SPI_TX_OVRFLW and SPI_RX_OVRFLW. www.analog.com Analog Devices | 30...

-

Page 35: General-Purpose Input And Output (Gpio)

C, LOCK, ERRB, etc.). Refer to the data sheets for additional details on GPIO capabilities and default states after power-up. The MAX96752 family has 15 multifunction pins (MFPs), refer to datasheet for full details. Operation GPIO pin mapping is coordinated across the serial link through GPIO “pin ID” assignments. Each GPIO input is assigned a pin ID that is included in the packet sent across the serial link and corresponds with a GPIO output. -

Page 36: Gpio, Gpi, Gpo And Odo

GPI-TO-GPO DELAY Figure 24. GPIO Forwarding Timing Diagram GPIO, GPI, GPO and ODO The MAX96752 has 15 GPIOs; 11 of these MFPs are GPIO (general-purpose input or output), 4 are GPO (general- purpose-output). Table 15 shows the GPIO capabilities of each GPIO pin. -

Page 37: Gpio Output Driver Setup

GPIO pins. Figure 25 is an example of this configuration. MFP0 MFP0 RX_ID = 0 TX_ID = 0 (GPIO0) (GPIO0) GMSL LINK SERIALIZER DESERIALIZER MFP3 RX_ID = 0 (GPIO3) Figure 25. GPIO Broadcasting www.analog.com Analog Devices | 33... -

Page 38: Gpio Delay Compensation

= 0 to disable the GPIO receive block for the GPIO pin. This sets the GPIO to receive its value from the bitfield GPIO_OUT instead of from the value being transmitted across the GMSL2 link. • Set GPIO_OUT to the desired value. Table 17. MAX96752 GPIO Registers Register Bits Default Value Decode 0x203 0x83... -

Page 39: Gpio Programming Example

GPIO pins or forward a GPIO on the local side to the remote side, depending on the desired application. An important note is to set up the GPIO Rx side before setting up the GPIO Tx side to prevent asynchronous states. www.analog.com Analog Devices | 35... -

Page 40: Mfp Slew Rate

High MFP slew rates, especially combined with high toggle frequencies, near the GMSL or high-speed video pins may adversely affect performance of the data path, including CRC errors, 9b10b code or disparity errors, reduction of link margin, and/or loss of link lock. www.analog.com Analog Devices | 36... -

Page 41: Configuration

Refer to the corresponding device’s data sheet “Control- and Side-Channel Typical Rise and Fall Times” section for timing details. The table below represents slew rate registers and the typical rise and fall times. DDIO Table 18. MAX96752 MFP Slew Rate Registers Register Bitfield Name Bits... -

Page 42: Pin Access And Routing

GMSL2 PROCESS) AUDIO SOURCE Figure 27. Audio Architecture Example Pin Access and Routing Table 19. MAX96752 Pins for Audio Default Function Audio Function #1 Notes Word Select Word-Select input with internal 1MΩ pull- down to ground. Supports forward audio from serializer to deserializer... -

Page 43: Power Manager And Sleep Mode

In all power modes, the power manager monitors power supplies for under- and over-voltage conditions. In Sleep mode, the power manager minimizes current consumption and can quickly restore device configurations after waking up. • MAX96752 Power Manager and Sleep Mode Availability Part Number Power Manager Sleep Mode... -

Page 44: Power Supplies

Run mode and draws minimal current. Retention memories are also powered by the V domain so that device DD18 configuration and register settings can be saved and restored. Figure 28 shows the state diagram for the power manager. www.analog.com Analog Devices | 40... -

Page 45: Reset (Power Down/Sleep)

DD18 supply must be continuously maintained to ensure that previous configurations and settings are preserved. It is recommended that all other supplies be maintained during Sleep mode to simplify the sleep and wakeup sequences. BOOT www.analog.com Analog Devices | 41... -

Page 46: Run

RESET_ALL resets the device and erroneously loads the contents of the retention memory that had been stored when the most recent SLEEP command was executed. As a result, the www.analog.com Analog Devices | 42... -

Page 47: Not All Registers Are Saved

DD33 family-specific power supplies are not typically monitored. The following table details the power supplies for which voltage monitoring is available. Table 21. Power Supply Monitoring Functions Available for MAX96752 Supply Name Description Monitor Functions Available Internal 1V digital core supply Undervoltage, Overvoltage GMSL 1.8V supply... -

Page 48: Undervoltage Monitoring Of V

In the case of an undervoltage condition, the status register bit CMP_STATUS[1] is latched low. The error can be flagged using the VDDCMP_INT_FLAG, which can be configured to drive the fault condition to the ERRB pin. The error status is cleared by first reading CMP_STATUS[1] and then reading VDDCMP_INT_FLAG. www.analog.com Analog Devices | 44... -

Page 49: Error Reporting And Status

Before implementing a new design, it is critical to do bandwidth (BW) calculations to verify that the right devices and settings are used. If this is not done, it is possible that data will be lost or corrupted. Although the MAX96752 family can transmit at 6Gbps/187.5Mbps depending on part number and configuration, the maximum allowable... -

Page 50: Error Flags

The error bar (ERRB) pin is an MFP pin that logically NORs many of the errors. Whether an error is included in the ERRB output depends on if its output-enable (OEN) bitfield is set high. Most OENs are high by default. www.analog.com Analog Devices | 46... -

Page 51: Device Error Flags

Figure 29. ERRB Reporting Flow Device Error Flags MAX96752 ERRB pin (active low) is available on pin 14 and is enabled by default. In addition, register bitfield ERROR (register 0x13 bit 2) goes HIGH when device has an error. Table 25 lists all of the error flags in this device. -

Page 52: Complete Use Case Programming Examples

MAX96751 serializer and MAX96752 deserializer. The format of the programming examples throughout this section will follow the format allowable by the GMSL GUI for .csv files, so that users may copy them for use immediately. -

Page 53: Use Case Example 2

Use Case Example 2 This example has the following characteristics: • One MAX96751 connected to one MAX96752 using GMSL Links A and B • Initial I2C address of serializer is 0x80 • Initial I2C address of deserializers is 0x90 •... - Page 54 Analog Devices | 50...

Need help?

Do you have a question about the MAX96752 and is the answer not in the manual?

Questions and answers