Subscribe to Our Youtube Channel

Summary of Contents for ADLINK Technology intel COM Express Express-TL

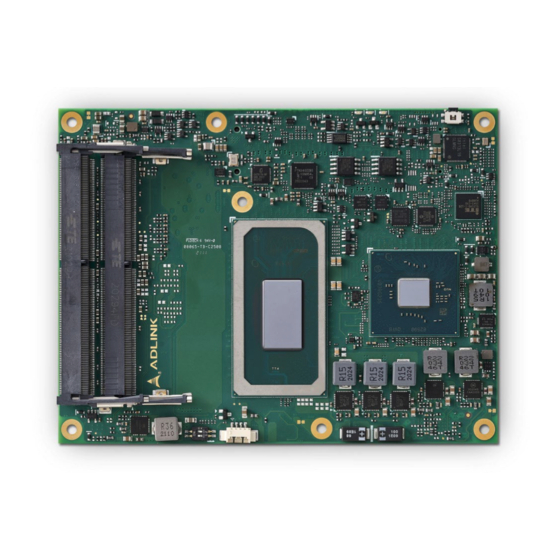

- Page 1 Express-TL User’s Guide PICMG COM.0 R3.0 Express-TL User’s Guide Revision: Rev. 1.1 Date: 2022-03-16 Part Number: 50M-00058-1010 Page 1 Copyright © 2022 ADLINK Technology, Inc.

-

Page 2: Revision History

Express-TL User’s Guide PICMG COM.0 R3.0 Revision History Revision Description Date Author Initial release 2021-12-16 Update pin definitions; update I/O and LED specifications 2022-03-16 Page 2 Copyright © 2022 ADLINK Technology, Inc. -

Page 3: Preface

Product names mentioned herein are used for identification purposes only and may be trademarks / registered trademarks of respective companies. Copyright © 2021 ADLINK Technology Incorporated This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer. - Page 4 Only install/attach and operate equipment on stable surfaces and/or recommended mountings; • If the equipment will not be used for long periods of time, turn off the power source and unplug the equipment. • Page 4 Copyright © 2022 ADLINK Technology, Inc.

- Page 5 Caution: This information indicates the possibility of minor physical injury, component damage, data loss, and/or program corruption. Warning: This information warns of possible serious physical injury, component damage, data loss, and/or program corruption. Page 5 Copyright © 2022 ADLINK Technology, Inc.

- Page 6 ADLINK Technology GmbH Hans-Thoma-Strasse 11, D-68163 Mannheim, Germany Tel: +49-621-43214-0 Fax: +49-621 43214-30 Email: emea@adlinktech.com Please visit the Contact page at www.adlinktech.com for information on how to contact the ADLINK regional office nearest you. Page 6 Copyright © 2022 ADLINK Technology, Inc.

-

Page 7: Table Of Contents

SATA ..................................................................31 4.3.6 PCI Express ................................................................. 32 4.3.7 LPC Bus ................................................................34 4.3.8 USB ..................................................................35 4.3.9 SPI Bus (BIOS only) ............................................................36 4.3.10 Miscellaneous ..............................................................37 4.3.11 SMBus .................................................................. 38 Page 7 Copyright © 2022 ADLINK Technology, Inc. - Page 8 8.1. Module Dimensions ..............................................................69 8.2. Thermal Solutions ................................................................ 70 8.2.1 Heatspreader: HTS ............................................................70 8.2.2 Heatsink: THS ..............................................................71 8.2.3 Heatsink High Profile: THSH ........................................................72 8.2.4 Heatsink with Fan: THSF ..........................................................73 Page 8 Copyright © 2022 ADLINK Technology, Inc.

-

Page 9: List Of Figures

Figure 7 – Heatspreader: HTS ........................................................70 Figure 8 – Heatsink: THS ..........................................................71 Figure 9 – Heatsink High Profile: THSH ....................................................72 Figure 10 – Heatsink with Fan: THSF ....................................................... 73 Page 9 Copyright © 2022 ADLINK Technology, Inc. -

Page 10: Introduction

SATA 6 Gb/s ports. Optional onboard PCIe Gen3 NVMe SSD is offered by project basis. Support is provided for SMBus and I C. The module is equipped with SPI AMI EFI BIOS with CMOS backup, supporting embedded features such as remote console, hardware monitor, and watchdog timer. Page 10 Copyright © 2022 ADLINK Technology, Inc. -

Page 11: Specifications

Xeon® processors paired with RM590E Chipset can support both of ECC and non-ECC memory. Other processor/chipset combinations support non- ECC memory. Fourth SODIMM on bottom side is supported by build option. Note: Top SODIMM sockets must be populated first. Page 11 Copyright © 2022 ADLINK Technology, Inc. -

Page 12: Video

HEVC/H.265, H.264, JPEG, VP9 HW encode • Advanced Scheduler 2.0, 1.0, XPDM support • DirectX up to 12 • OpenGL up to 4.5 and ES 2.0 support • OpenCL up to 2.1 support • Page 12 Copyright © 2022 ADLINK Technology, Inc. -

Page 13: Display Interface Support

8 PCI Express x1 Gen3: Lanes 0-3 (configurable to 4 x1, 2 x2, 1 x4, 1 x2 + 2 x1) and Lanes 4-7 (configurable to 4 x1, 2 x2, 1 x4, 1 x2 + 2 x1) Other: SMBus (system), I C (user), LPC bus (via eSPI to LPC bridge IC) Page 13 Copyright © 2022 ADLINK Technology, Inc. -

Page 14: Ethernet

4x SATA 6Gb/s (SATA 0,1,2,3) Note: For SATA 6Gb/s compatibility, it is strongly recommended to use a SATA redriver on the carrier board GPIO or SD 4 GPO and 4 GPI (GPI with interrupt) Page 14 Copyright © 2022 ADLINK Technology, Inc. -

Page 15: Trusted Platform Module (Tpm)

Supports: Voltage/current monitoring, power sequence debug support, AT/ATX mode control, logistics and forensic information, flat panel control, general purpose I C, failsafe BIOS (dual BIOS, opt. support), watchdog timer and fan control Page 15 Copyright © 2022 ADLINK Technology, Inc. -

Page 16: Debug

Storage: -20°C to +80°C Extreme Rugged -40°C to +85°C (Standard Voltage Input) Storage: -40°C to +85°C (selected SoC SKUs) Humidity 5-90% RH operating, non-condensing, 5-95% RH storage (and operating with conformal coating) Page 16 Copyright © 2022 ADLINK Technology, Inc. - Page 17 Shock and Vibration IEC 60068-2-64 and IEC-60068-2-27 MIL-STD-202F, Method 213B, Table 213-I, Condition A and Method 214A, Table 214-I, Condition D HALT tested Thermal Stress, Vibration Stress, Thermal Shock and Combined Test Page 17 Copyright © 2022 ADLINK Technology, Inc.

-

Page 18: Block Diagram

1 PCIe Gen4 x4 TPM 2.0 2 MIPI-CSI SMBus DB30 x86 Connector HSUART eSPI eSPI eSPI to LPC 8xGPIO/SDIO Connector Embedded 2xUART/CAN Controller LM73 (board) LPC/eSPI Figure 1 – Module function diagram Page 18 Copyright © 2022 ADLINK Technology, Inc. -

Page 19: Pinout And Signal Descriptions

COM.0 R3.0 specification. Signals described in the specification but not supported on the Express-TL are marked with strike-through. socket depends on SKUs NVMe SSD optional A110 Figure 2 - Module rear side row and pin numbering Page 19 Copyright © 2022 ADLINK Technology, Inc. - Page 20 AC/HDA_SYNC AC/HDA_SDIN1 DDI1_PAIR5+ DDI1_PAIR1+ AC/HDA_RST# AC/HDA_SDIN0 DDI1_PAIR5- DDI1_PAIR1- GND (FIXED) GND (FIXED) GND (FIXED) GND (FIXED) AC/HDA_BITCLK SPKR DDI2_CTRLCLK_AUX+ DDI1_PAIR2+ AC/HDA_SDOUT I2C_CK DDI2_CTRLDATA_AUX- DDI1_PAIR2- BIOS_DIS0#/ESPI_SAFS I2C_DAT DDI2_DDC_AUX_SEL DDI1_DDC_AUX_SEL THRMTRIP# THRM# RSVD RSVD Page 20 Copyright © 2022 ADLINK Technology, Inc.

- Page 21 RSVD RSVD PCIE_TX1+ PCIE_RX1+ RSVD RSVD PCIE_TX1- PCIE_RX1- PEG_RX4+ PEG_TX4+ WAKE0# PEG_RX4- PEG_TX4- GPI2 WAKE1# RAPID_SHUTDOWN PCIE_TX0+ PCIE_RX0+ PEG_RX5+ PEG_TX5+ PCIE_TX0- PCIE_RX0- PEG_RX5- PEG_TX5- GND (FIXED) GND (FIXED) GND (FIXED) GND (FIXED) Page 21 Copyright © 2022 ADLINK Technology, Inc.

- Page 22 D101 PEG_TX15+ A102 SER1_RX/CAN_RX B102 FAN_TACHIN C102 PEG_RX15- D102 PEG_TX15- A103 LID# B103 SLEEP# C103 D103 A104 VCC_12V B104 VCC_12V C104 VCC_12V D104 VCC_12V A105 VCC_12V B105 VCC_12V C105 VCC_12V D105 VCC_12V Page 22 Copyright © 2022 ADLINK Technology, Inc.

- Page 23 (see 4.3.4 Gigabit Ethernet on page 30). Maximum 2x USB4 is a build option in place of DDI 1, DDI 2 channels by project basis. Please contact your local representative for details. Page 23 Copyright © 2022 ADLINK Technology, Inc.

-

Page 24: Signal Terminology Descriptions

Pull-down strap. A Module output pin that is either tied to GND or is not connected. Used to signal Module capabilities to the Carrier Board. PU (pull-up) resistor on module PD (pull-down) resistor on module Page 24 Copyright © 2022 ADLINK Technology, Inc. -

Page 25: Ab Connector Signal Descriptions

Serial TDM data output to the CODEC. PCH internal PD 20Kohm HDA_SDOUT 3.3VSB AC_SDIN[2:0] / Serial TDM data inputs from up to 3 CODECs. PCH internal PD 20Kohm HDA_SDIN[2:0] 3.3VSB AC_SDNI2/HDA_SDIN2 not supported Page 25 Copyright © 2022 ADLINK Technology, Inc. -

Page 26: Analog Vga

I/O OD 3.3V PU 2k2 3.3V monitor capabilities) VGA_I2C_DAT DDC data line. I/O OD 3.3V PU 2k2 3.3V Note: VGA is BOM option support (in place of DDI 3) by project basis Page 26 Copyright © 2022 ADLINK Technology, Inc. -

Page 27: Lvds Or Edp

LVDS_B0- LVDS_B1+ LVDS_B1- LVDS_B2+ LVDS_B2- LVDS_B3+ LVDS_B3- LVDS_B_CK+ LVDS_B_CK- LVDS_VDD_EN eDP_VDD_EN LVDS_BKLT_EN eDP_BKLT_EN LVDS_BKLT_CTRL eDP_BKLT_CTRL LVDS_I2C_CK eDP_AUX+ LVDS_I2C_DAT eDP_AUX- eDP_HPD Note: LVDS is the default mode and eDP is a BOM option Page 27 Copyright © 2022 ADLINK Technology, Inc. - Page 28 PD 100K LVDS_I2C_CK DDC lines used for flat panel detection and control. O 3.3V PU 2k2 3.3V LVDS_I2C_DAT DDC lines used for flat panel detection and control. I/O 3.3V PU 2k2 3.3V Page 28 Copyright © 2022 ADLINK Technology, Inc.

- Page 29 I/O PCIE AC coupled off module eDP_HPD Detection of Hot Plug / Unplug and notification of the I 3.3V PD 100K PD 100K on this pin when eDP is supported link layer Page 29 Copyright © 2022 ADLINK Technology, Inc.

-

Page 30: Gigabit Ethernet

GBE0_LINK100# will be active for 1GbE speed indication or lower. GBE0_ACT# and GBE0_LINK# share the same source from the LAN controller. For 100Mbit/sec and 10Mbit/sec speed, the LAN LED will be OFF. Page 30 Copyright © 2022 ADLINK Technology, Inc. -

Page 31: Sata

ATA (parallel and serial) or SAS activity indicator, active low. O 3.3V PU 10K 3.3V 4.3.5.1. PCH HSIO Lane Assignments Name HSIO name on SOC Comment SATA0 HSIO 26 SATA1 HSIO 27 SATA2 HSIO 28 SATA3 HSIO 29 Page 31 Copyright © 2022 ADLINK Technology, Inc. -

Page 32: Pci Express

PCI Express channel 5, Receive Input differential pair. I PCIE AC coupled off Module PCIE_RX5- PCIE_CLK_REF+ PCI Express Reference Clock output for all PCI Express and PCI O PCIE PCIE_CLK_REF- Express Graphics Lanes. Page 32 Copyright © 2022 ADLINK Technology, Inc. - Page 33 PCH HSIO Lane Assignments Name HSIO name on SOC Comment PCIE0 HSIO 22 PCIE1 HSIO 23 PCIE2 HSIO 24 PCIE3 HSIO 25 PCIE4 HSIO 30 PCIE5 HSIO 31 PCIE6 HSIO 32 PCIE7 HSIO 33 Page 33 Copyright © 2022 ADLINK Technology, Inc.

-

Page 34: Lpc Bus

I/O 3.3VSB PU 8.2K 3.3VSB LPC_CLK LPC clock output –33MHz nominal O 3.3VSB The LPC_CLK frequency is 24MHz on this platform Note: LPC Bus is supported by an eSPI to LPC bridge IC Page 34 Copyright © 2022 ADLINK Technology, Inc. -

Page 35: Usb

USB0. A high value indicates that a host is present. *Note: A pull-up for this line shall be present on the module. An open drain driver from a USB current monitor on the carrier board may drive this line low. Page 35 Copyright © 2022 ADLINK Technology, Inc. -

Page 36: Spi Bus (Bios Only)

PU 10K Carrier shall pull to GND or leave not- connected. 3.3VSB BIOS_DIS1# Selection strap to determine the BIOS boot device. PU 10K Carrier shall pull to GND or leave not- connected 3.3VSB Page 36 Copyright © 2022 ADLINK Technology, Inc. -

Page 37: Miscellaneous

PD only when TPM on module. Active high. TPM chip has an internal pull down. This Modules implementing a TPM shall pull down signal is used to indicate Physical Presence to the TPM. Page 37 Copyright © 2022 ADLINK Technology, Inc. -

Page 38: Smbus

Source SEMA BMC as default (chipset by BOM 3.3VSB 3.3VSB option) I2C_DAT General purpose I²C port data I/O line I/O OD PU 2.2K Source SEMA BMC as default (chipset by BOM 3.3VSB 3.3VSB option) Page 38 Copyright © 2022 ADLINK Technology, Inc. -

Page 39: General Purpose I/O (Gpio)

O CMOS Power rail tolerance 5V, 12V 3.3V There shall be PD on carrier board SER1_RX A102 General purpose serial port receiver I CMOS PU 10K 3.3V Power rail tolerance 5V, 12V 3.3V Page 39 Copyright © 2022 ADLINK Technology, Inc. -

Page 40: Power And System Management

Trigger for Rapid Shutdown. Must be driven to 5V though a <=50-ohm source RAPID_ I CMOS Not supported impedance for ≥ 20 μs. SHUTDOWN 5VSB Page 40 Copyright © 2022 ADLINK Technology, Inc. -

Page 41: Power And Ground

A1, A11, A21, A31, A41, A51, Ground - DC power and signal and AC signal return A57, A60, A66, A70, A80, A90, path. A100, A110, B1, B11, B21, B31, B41, B51, B60, B70, B80, B90, B100, B110 Page 41 Copyright © 2022 ADLINK Technology, Inc. -

Page 42: Cd Connector Signal Descriptions

Additional Transmit signal differential pairs for the SuperSpeed O PCIE AC coupled on module USB_SSTX3+ USB data path on USB3 4.4.1.1. USB Root Segmentation All USB interfaces are derived from the xHCI controller. Page 42 Copyright © 2022 ADLINK Technology, Inc. -

Page 43: Pci Express

PCIE_RX7+ PCI Express channel 7, Receive Input differential pair. I PCIE AC coupled off Module PCIE_RX7- 4.4.2.1. PCH HSIO Lane Assignments Refer to Section 4.3.6.1 PCH HSIO Lane Assignments on page 33. Page 43 Copyright © 2022 ADLINK Technology, Inc. -

Page 44: Ddi1 Port

DP_AUX+ /- pair must be AC coupled. A set of FET switches is usually used to sort this out. The FET gates can be controlled by the AUX_SEL pin function. Page 44 Copyright © 2022 ADLINK Technology, Inc. - Page 45 AC coupled on Module Management and Device Control DDI1_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M DP mode enabled 1M pull-down to logic ground enables HDMI Floating enables DisplayPort mode Page 45 Copyright © 2022 ADLINK Technology, Inc.

- Page 46 AC couple on Module DDI1_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M HDMI mode enabled 1M pull-down to logic ground enables HDMI Leve this signal floating enables DisplayPort mode Page 46 Copyright © 2022 ADLINK Technology, Inc.

-

Page 47: Ddi2 Port

DP_AUX+ /- pair must be AC coupled. A set of FET switches is usually used to sort this out. The FET gates can be controlled by the AUX_SEL pin function. Page 47 Copyright © 2022 ADLINK Technology, Inc. - Page 48 AC coupled on Module Management and Device Control DDI2_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M DP mode enabled 1M pull-down to logic ground enables HDMI Floating enables DisplayPort mode Page 48 Copyright © 2022 ADLINK Technology, Inc.

- Page 49 AC couple on Module DDI2_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M HDMI mode enabled 1M pull-down to logic ground enables HDMI Leve this signal floating enables DisplayPort mode Page 49 Copyright © 2022 ADLINK Technology, Inc.

-

Page 50: Ddi3 Port

DP_AUX+ /- pair must be AC coupled. A set of FET switches is usually used to sort this out. The FET gates can be controlled by the AUX_SEL pin function. Page 50 Copyright © 2022 ADLINK Technology, Inc. - Page 51 AC coupled on Module Management and Device Control DDI3_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M DP mode enabled 1M pull-down to logic ground enables HDMI Floating enables DisplayPort mode Page 51 Copyright © 2022 ADLINK Technology, Inc.

- Page 52 AC couple on Module DDI3_DDC_AUX_SEL Strapping Signal to select HDMI or DP output I 3.3V PD 1M HDMI mode enabled 1M pull-down to logic ground enables HDMI Leve this signal floating enables DisplayPort mode Page 52 Copyright © 2022 ADLINK Technology, Inc.

-

Page 53: Pcie Graphics Port (Peg)

Type 6 PEG_TX5+ PCI Express Graphics transmit differential pairs. O PCIE AC coupled on Module PEG_TX5- These are the same lines as PCIE_TX[16:31]+ and – in Module pin- out Type 6 Page 53 Copyright © 2022 ADLINK Technology, Inc. - Page 54 Type 6 PEG_RX10+ PCI Express Graphics receive differential pairs. I PCIE AC coupled off Module PEG_RX10- These are the same lines as PCIE_TX[16:31]+ and – in Module pin- out Type 6 Page 54 Copyright © 2022 ADLINK Technology, Inc.

- Page 55 These are the same lines as PCIE_TX[16:31]+ and – in Module pin- out Type 6 PEG_LANE_RV# PCI Express Graphics lane reversal input strap. Pull low on the I 3.3V Carrier Board to reverse lane order. Page 55 Copyright © 2022 ADLINK Technology, Inc.

-

Page 56: Module Type Definition

Carrier Board logic may also implement a fault indicator such as an LED. TYPE10# In case of a type 10 module this pin signal is tied to GND through a 47K resistor No PD on the module. Page 56 Copyright © 2022 ADLINK Technology, Inc. -

Page 57: Power And Ground

C76, C80, C84, C87, C90, C93, C96, C100, C103, C110, D1, D2, D5, D8, D11, D14, D21, D31, D41, D51, D60, D67, D70, D73, D76, D80, D84, D87, D90, D93, D96, D100, D103, D110 Page 57 Copyright © 2022 ADLINK Technology, Inc. -

Page 58: Additional Features

This chapter describes connectors, LEDs, switches and additional items located on the module and not necessarily included in the PICMG standard spec- ification. The locations of these items are as below: Status BIOS Default LEDs 5.1. Module Feature Locations Reset Button BIOS Boot Select Figure 3 – Module feature locations (top side) Page 58 Copyright © 2022 ADLINK Technology, Inc. -

Page 59: Figure 4 - Module Feature Locations (Bottom Side)

Express-TL User’s Guide PICMG COM.0 R3.0 30-pin Debug Connector PCI Express Configuration Switch Figure 4 – Module feature locations (bottom side) Page 59 Copyright © 2022 ADLINK Technology, Inc. -

Page 60: Debug Connector

• SPI BIOS programming interface • Embedded Controller programming interface • 30-pin Debug Connector located on bottom side 30-pin Debug Connector located on bottom side Figure 5 – Express-TL and Debug Module Page 60 Copyright © 2022 ADLINK Technology, Inc. -

Page 61: Status Leds

Rebooted after PWRBTN WD LED = LED OFF Rebooted after RESET BTN WD LED = LED OFF Note: only a RESET not initiated by the BMC can clear the WD LED (user action) Page 61 Copyright © 2022 ADLINK Technology, Inc. -

Page 62: Exception Codes

Express-TL User’s Guide PICMG COM.0 R3.0 5.4. Exception Codes Exception Code Error Message NOERROR NO_SLP_S5 NO_SLP_S4 NO_SLP_S3 BIOS_FAIL RESET_FAIL NO_CB_PWROK CRITICAL_TEMP POWER_FAIL VOLTAGE_FAIL RSMRST_FAIL NO_VDDQ_PG NO_VCORE_PG NO_SYS_GD NO_V3P3A NO_PWRSRC_GD Page 62 Copyright © 2022 ADLINK Technology, Inc. -

Page 63: Fan Connector

Express-TL User’s Guide PICMG COM.0 R3.0 5.5. Fan Connector Connector type: JVE 24W1125A-04M00 4 3 2 1 Name Description FAN_PWMOUT FAN_TACHIN Page 63 Copyright © 2022 ADLINK Technology, Inc. -

Page 64: Bios Default Reset Button

2. Keep the BIOS Setup Defaults Reset Button pressed and boot up the system. You can release the button when the BIOS prompt screen appears 3. The BIOS prompt screen will display a confirmation that BIOS defaults have been reset and request that you reboot the system. Page 64 Copyright © 2022 ADLINK Technology, Inc. -

Page 65: Pci Express Configuration Switch

The PCI Express Configuration Switch allows you to configure the PCI Express x16 lanes from the CPU as 1 PCIe x16, 2 PCIe x8, or 1 PCIe x8 + 2 PCIe x4. Mode Pin 1 Pin 2 1 PCIe x16 (default) 2 PCIe x8 1 PCIe x8 + 2 PCIe x4 Reserved Page 65 Copyright © 2022 ADLINK Technology, Inc. -

Page 66: Bios Boot Select

In either mode, BIOS Select and Mode Configuration Switch Pin 1 is used to select whether to boot from SPI0 or SPI1. Mode Pin 1 Pin 2 Boot from SPI0 (default) Boot from SPI1 Set BIOS to PICMG mode (default) Set BIOS to Failsafe BIOS mode Page 66 Copyright © 2022 ADLINK Technology, Inc. -

Page 67: Bios Checkpoints, Beep Codes

These PCI add-on cards show the value of I/O port 80h on an LED display. Aptio V Checkpoint and Beep Codes Download the Aptio V Checkpoint and Beep Codes from the AMI website at: www.ami.com/download/aptio-v-checkpoint-and-beep-codes Page 67 Copyright © 2022 ADLINK Technology, Inc. -

Page 68: Software Support

Express-TL User’s Guide PICMG COM.0 R3.0 7. Software Support 7.1. Windows 10 IoT Enterprise 64-bit 7.2. Yocto Linux 64-bit https://github.com/ADLINK/meta-adlink-x86-64bit (TBC) 7.3. Ubuntu Under planning, TBC 7.4. VxWorks 64-bit Under planning, TBC Page 68 Copyright © 2022 ADLINK Technology, Inc. -

Page 69: Mechanical And Thermal

± 0.25mm, unless otherwise noted. The tolerances on the module connector locating peg holes (dimensions [16.50, 6.00]&[16.50,18.00]) should be ± 0.10mm. Front View Dimensions: mm Figure 6 – Module mechanical dimensions Page 69 Copyright © 2022 ADLINK Technology, Inc. -

Page 70: Thermal Solutions

Express-TL User’s Guide PICMG COM.0 R3.0 8.2. Thermal Solutions 8.2.1 Heatspreader: HTS Dimensions: mm M2.5*2pcs M2.5*4pcs Figure 7 – Heatspreader: HTS Page 70 Copyright © 2022 ADLINK Technology, Inc. -

Page 71: Heatsink: Ths

Express-TL User’s Guide PICMG COM.0 R3.0 8.2.2 Heatsink: THS Dimensions: mm M2.5*2pcs M2.5*4pcs 16.4 Figure 8 – Heatsink: THS Page 71 Copyright © 2022 ADLINK Technology, Inc. -

Page 72: Heatsink High Profile: Thsh

Express-TL User’s Guide PICMG COM.0 R3.0 8.2.3 Heatsink High Profile: THSH Dimensions: mm M2.5*2pcs M2.5*4pcs 25.1 Figure 9 – Heatsink High Profile: THSH Page 72 Copyright © 2022 ADLINK Technology, Inc. -

Page 73: Heatsink With Fan: Thsf

Express-TL User’s Guide PICMG COM.0 R3.0 8.2.4 Heatsink with Fan: THSF Dimensions: mm M2.5*2pcs M2.5*x4pcs 39.4 Figure 10 – Heatsink with Fan: THSF Page 73 Copyright © 2022 ADLINK Technology, Inc.

Need help?

Do you have a question about the intel COM Express Express-TL and is the answer not in the manual?

Questions and answers