Summary of Contents for ADLINK Technology Com Express nanoX-BT

- Page 1 nanoX-BT User’s Manual Manual Revision: 1.03 Revision Date: March 17, 2016 Part Number: 50-1J053-1030...

-

Page 2: Revision History

Revision History Revision Description Date 1.00 Initial release 2014-07-24 1.01 Add BIOS Checkpoints, Beep Codes; correct SD signal support; add SEMA CPU temperature 2014-09-24 limitation 1.02 Correct specifications (CPU, memory, serial port, GPIO, eMMC, OS); add SW1 BIOS settings 2015-09-07 description 1.03 Add clarification of single channel 24-bit EDID LVDS panel support by BOM option;... -

Page 3: Preface

Preface Copyright 2014-16 ADLINK Technology, Inc. This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer. -

Page 4: Table Of Contents

Table of Contents Revision History ......................2 Preface..........................3 Introduction ......................8 Specifications....................... 9 2.1. Core System..........................9 2.2. Expansion Busses........................9 2.3. SEMA Board Controller......................9 2.4. Debug Headers .........................9 2.5. Video............................10 2.6. Audio............................10 2.7. LAN ............................10 2.8. Multi I/O and Storage ......................10 2.9. - Page 5 3.3.12. SPI (BIOS only) ..........................22 3.3.13. Miscellaneous..........................23 3.3.14. SMBus............................23 3.3.15. I2C Bus............................23 3.3.16. General Purpose I/O (GPIO) ......................23 3.3.17. Serial Interface Signals ........................24 3.3.18. Power And System Management....................24 3.3.19. Power and Ground ........................25 Module interfaces ..................... 26 4.1. Connector, Switch and LED Locations ................... 26 4.1.1.

- Page 6 7.2.1. System Information........................40 7.2.2. Processor Information.........................40 7.2.3. VGA Firmware Version ........................40 7.2.4. Memory Information........................40 7.2.5. SOC Information..........................40 7.2.6. System Management ........................41 7.2.7. System Date and Time.........................43 7.3. Advanced ..........................44 7.3.1. CPU..............................44 7.3.2. Memory............................45 7.3.3. Graphics ............................45 7.3.4. SATA ............................46 7.3.5.

- Page 7 9.1. Board-to-Board Connectors ....................66 9.2. Thermal Solution ........................67 9.2.1. Heat Spreaders..........................67 9.2.2. Heat Sinks............................67 9.2.3. Installation...........................67 9.3. Mounting Methods........................ 69 9.4. Standoff Types ........................70 Safety Instructions ...................... 71 Getting Service ......................72 nanoX-BT Page 7...

-

Page 8: Introduction

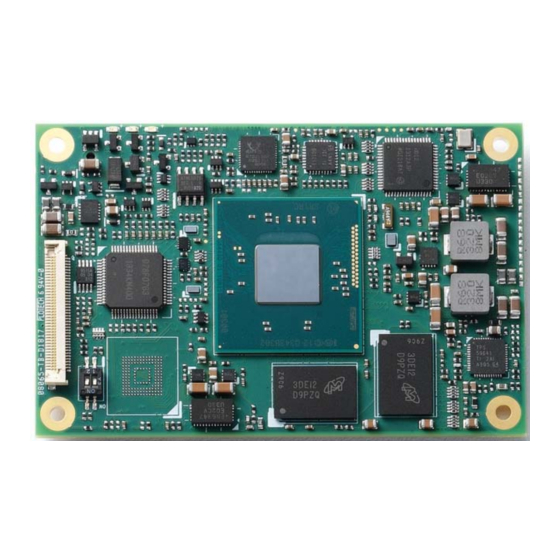

1. Introduction The nanoX-BT is a COM Express® COM.0 R2.1 Type 10 module supporting Intel® Atom™ processor E3800 Series and Intel® Celeron® processor system-on-chip (SoC). The nanoX-BT is specifically designed for customers who need high-level processing and graphics performance with low power consumption in a long product life solution. The nanoX-BT features Intel®... -

Page 9: Specifications

2. Specifications 2.1. Core System CPU: Single, dual or quad-core Intel® Atom™ or Celeron® Processor • Atom™ E3845 1.91 GHz 542/792 (Turbo) 10W (4C/1333) • Atom™ E3827 1.75 GHz 542/792 (Turbo) 8W (2C/1333) • Atom™ E3826 1.46 GHz 533/667 (Turbo) 7W (2C/1066) •... -

Page 10: Video

2.5. Video GPU Feature Support: 7th generation graphics Intel core architecture with four execution units supporting two independent displays • 3D graphics hardware acceleration • Support for DirectX11, OCL 1.1, OGL ES Halt/2.0/1.1, OGL 3.2 • Video decode hardware acceleration including support for H.264, MPEG2, VC-1, WMV and VP8 formats •... -

Page 11: Power Specifications

2.9. Power Specifications Power Modes: AT and ATX mode (AT mode start controlled by SEMA) Standard Voltage Input: ATX = 12V±5%, 5Vsb ±5% or AT = 12V ±5% Wide Voltage Input: ATX = 5~14 V, 5Vsb ±5% or AT = 5 ~14V Power Management: ACPI 4.0 compliant, Smart Battery support Power States:... -

Page 12: Functional Diagram

2.14. Functional Diagram eDP (optional) LVDS DDI1 eDP to LVDS Soldered eDP 1 lane RTL2132 Intel® Atom™ 2~4 GB DDR3L non ECC (only) E3845 DDI2 E3827 4 lanes E3826 E3825 E3815 1x USB 1.1/2.0/3.0 (port 0) E3805 (No GFX) 3x USB 1.1/2.0 (port 1~3) 1x USB 1.1/2.0 client (port 7) Intel®... -

Page 13: Mechanical Dimensions

2.15. Mechanical Dimensions connector on bottom side Top View Side View Units: mm nanoX-BT Page 13... -

Page 14: Pinouts And Signal Descriptions

3. Pinouts and Signal Descriptions 3.1. AB Pin Definitions The nanoX-BT is a Type 10 module supporting USB3.0 and DDI channel on the AB connector In below table all standard pins of the COM Express specification are described, also those not supported on the nanoX-BT ! Note: Signals not supported on the nanoX-BT module are crossed out Type 10 COM.0 Rev. - Page 15 Row A Row B Name Name THRMTRIP# THRM# USB6- USB7- USB6+ USB7+ USB_6_7_OC# USB_4_5_OC# USB4- USB5- USB4+ USB5+ GND(FIXED) GND(FIXED) USB2- USB3- USB2+ USB3+ USB_2_3_OC# USB_0_1_OC# USB0- USB1- USB0+ USB1+ VCC_RTC EXCD1_PERST# EXCD0_PERST# EXCD1_CPPE# EXCD0_CPPE# SYS_RESET# LPC_SERIRQ CB_RESET# GND(FIXED) GND(FIXED) RSVD RSVD RSVD...

- Page 16 Row A Row B Name Name GND(FIXED) GND(FIXED) LVDS_A_CK+ / eDP_TX3+ DDI0_PAIR3+ LVDS_A_CK- / eDP_TX3- DDI0_PAIR3- LVDS_I2C_CK / eDP_AUX+ LVDS_/eDP_BKLT_CTRL LVDS_I2C_DAT / eDP_AUX- VCC_5V_SBY GPI3 VCC_5V_SBY RSVD VCC_5V_SBY eDP_HPD VCC_5V_SBY PCIE_CLK_REF+ BIOS_DIS1# PCIE_CLK_REF- DD0_HPD GND(FIXED) GND(FIXED) SPI_POWER DDI0_PAIR5+ SPI_MISO DDI0_PAIR5- GPO0 DDI0_PAIR6+ SPI_CLK...

-

Page 17: Signal Description Terminology

3.2. Signal Description Terminology The following terms are used in the COM Express AB/CD Signal Descriptions below. Input to the Module Output from the Module Bi-directional input / output signal Open drain output I 3.3V Input 3.3V tolerant I 5V Input 5V tolerant O 3.3V Output 3.3V signal level... -

Page 18: Ab Signal Description

3.3. AB Signal Description 3.3.1. Audio Signals Signal Pin # Description PU/PD Comment AC_RST# Reset output to CODEC, active low. O 3.3VSB HDA_RST# AC_SYNC / Sample-synchronization signal to the CODEC(s). O 3.3V HDA_SYNC AC_BITCLK / Serial data clock generated by the external CODEC(s). I/O 3.3V HDA_BITCLK AC _SDOUT / Serial TDM data output to the CODEC. -

Page 19: Ddi0 Channel

3.3.3. DDI0 Channel Signal Pin # Description PU/PD Comment DDI0_PAIR0+ Digital Display Interface differential pairs O PCIE Pair 4 to Pair 6 DDI0_PAIR0- are not DDI0_PAIR1+ supported DDI0_PAIR1- DDI0_PAIR2+ DDI0_PAIR2- DDI0_PAIR3+ DDI0_PAIR3- DDI0_PAIR4+ DDI0_PAIR4- DDI0_PAIR5+ DDI0_PAIR5- DDI0_PAIR6+ DDI0_PAIR6- DDI0_HPD Digital Display Interface Hot-Plug Detect I 3.3V 100k DDI0_CTRLCLK_AUX+... -

Page 20: Sata

3.3.5. SATA Signal Pin # Description PU/PD Comment SATA0_TX+ Serial ATA channel 0, Transmit Output differential pair. O SATA AC coupled on Module SATA0_TX- SATA0_RX+ Serial ATA channel 0, Receive Input differential pair. I SATA AC coupled on Module SATA0_RX- SATA1_TX+ Serial ATA channel 1, Transmit Output differential pair. -

Page 21: Lpc Bus

3.3.8. LPC Bus Signal Pin # Description PU/PD Comment LPC_AD[0:3] B4-B7 LPC multiplexed address, command and data I/O 3.3V LPC_FRAME# LPC frame indicates the start of an LPC cycle O 3.3V LPC_DRQ0# LPC serial DMA request I 3.3V LPC_DRQ1# LPC_SERIRQ LPC serial interrupt I/O OD 3.3V PU 8k2 3.3V... -

Page 22: Usb 3.0 Extension

3.3.10. USB 3.0 Extension Signal Description PU/PD Comment USB_SSRX0- Additional Receive signal differential pairs for the SuperSpeed I PCIE USB_SSRX0+ USB data path on USB0 USB_SSTX0- Additional Transmit signal differential pairs for the SuperSpeed O PCIE AC coupled on Module USB_SSTX0+ USB data path on USB0 USB_SSRX1-... -

Page 23: Miscellaneous

3.3.13. Miscellaneous Signal Pin # Description PU/PD Comment SPKR Output for audio enunciator, the “speaker” in PC-AT systems O 3.3V Output indicating that a watchdog time-out event has occurred. O 3.3V THRM# Input from off-module temp sensor indicating an over-temp situation. I 3.3V THERMTRIP# Active low output indicating that the CPU has entered thermal shutdown. -

Page 24: Serial Interface Signals

3.3.17. Serial Interface Signals Signal Pin # Description PU/PD Comment SER0_TX A98 General purpose serial port transmitter (TTL level output) O CMOS Power rail tolerance 5V / 12V SER0_RX A99 General purpose serial port receiver (TTL level input) I CMOS Power rail tolerance 5V / 12V SER1_TX A101 General purpose serial port transmitter (TTL level output) O CMOS... -

Page 25: Power And Ground

3.3.19. Power and Ground Signal Pin # Description I/O PU/PD Comment VCC_12V A104-A109 Primary power input: +12V nominal 5~14 V See section 7 “Electrical Specifications“ for allowable input range. All B104-B109 available VCC_12V pins on the connector(s) shall be used. VCC_5V_SBY B84-B87 Standby power input: +5.0V nominal. -

Page 26: Module Interfaces

4. Module interfaces This chapter describes connectors and pinouts, LEDs and switches that are used on the module but are not included in the PICMG standard specification 4.1. Connector, Switch and LED Locations Debug Header Note: The optional XDP is located on breakout PCB. 4.1.1. -

Page 27: 40-Pin Multipurpose Connector

4.2. 40-pin Multipurpose Connector FPC Connector Type: FCI 59GF Flex 10042867 Pin Orientation Pin Definitions (on COMe module) Interface Signal Remark Interface Signal Remark VCC_SPI_IN SPI Power Input from flash tool to BMC Program TXD6 Program module. HW need add MOS FET interface interface to switch SPI power for SPI ROM... -

Page 28: Status Leds

4.3. Status LEDs To facilitate easier maintenance, status LED’s are mounted on the board. LED1 LED2 LED3 LED Descriptions Name Color Connection Function LED1 Blue BMC output Power Sequence Status Code (BMC) Power Changes, RESET (see 5.1.4 Exception Codes below) LED2 Green Power Source 3Vcc... -

Page 29: Xdp Debug Header

4.4. XDP Debug Header Optionally available on breakout PCB. The debug port is a connection into a target-system environment that provides access to JTAG, run control, system control, and observation resources. The XDP target system connector is a Samtec 60-pin BSH-030-01 series connector. Specific plating types, locking clips, and alignment pin details of this connector can be obtained from Samtec. -

Page 30: Nanox-Bt Switch Settings

4.5. Switch Settings 4.5.1. Switch Locations 4.5.2. SW1: BIOS Select and Mode Configuration Switch Module has two BIOS chips and BIOS operation can be configured to "PICMG" and "Failsafe" modes using SW1, Pin 2. Setting the module to PICMG mode will configure the BIOS chips on the module as SPI0 and SPI1. In PICMG mode, a BIOS chip CANNOT be placed in SPI0 on the carrier. -

Page 31: Smart Embedded Management Agent (Sema)

5. Smart Embedded Management Agent (SEMA) The onboard microcontroller (BMC) implements power sequencing and Smart Embedded Management Agent (SEMA) functionality. The microcontroller communicates via the System Management Bus with the CPU/chipset. The following functions are implemented Total operating hours counter. Counts the number of hours the module has been run in minutes. On-time minutes counter. -

Page 32: Board Specific Sema Functions

5.1. Board Specific SEMA Functions 5.1.1. Voltages The BMC of the nanoX-BT implements a voltage monitor and samples several onboard voltages. The voltages can be read by calling the SEMA function “Get Voltages”. The function returns a 16-bit value divided into high-byte (MSB) and low-byte (LSB). ADC Channel Voltage Name Voltage Formula [V]... -

Page 33: Exception Codes

5.1.4. Exception Codes In case of an error, the BMC drives a blinking code on the blue Status LED (LED1). The same error code is also reported by the BMC Flags register. The Exception Code is not stored in the Flash Storage and is cleared when the power is removed. Therefore, a “Clear Exception Code”... -

Page 34: System Resources

6. System Resources 6.1. System Memory Map Address Range (decimal) Address Range (hex) Size Description Start 128KB below 1MB 000E0000h-000FFFFFh Low Bios Starts 20MB below 4GB FEC00000h-FEC0040h IO APIC Start 19MB below 4GB FED00000h-FED003FFh HPET Start 64 KB below 4GB FFFF0000h-FFFFFFFFh High Bios 0K –1MB... -

Page 35: Interrupt Request (Irq) Lines

6.3. Interrupt Request (IRQ) Lines 6.3.1. PIC Mode IRQ# Typical Intterupt Resource Connected to Pin Available Counter 0 Keyboard controller IRQ1 via SERIRQ / PIRQ Cascade interrupt from slave PIC Generic IRQ3 via SERIRQ / PIRQ Note (1) PCU Serial Port (COM1) IRQ4 via SERIRQ / PIRQ Note (1) Generic... - Page 36 IRQ# Typical Intterupt Resource Connected to Pin Available IRQ12 via SERIRQ / PIRQ Note (1) Note (1) Note (1) Note (1) PCIE Port 1/2/3/4, eMMC, IGD Note (1) PCIE Port 1/2/3/4 Note (1) PCIE Port 1/2/3/4, SD Device, HSUART Note (1) PCIE Port 1/2/3/4, AHCI controller Note (1) Gbe controller, xHCI controller...

-

Page 37: Pci Configuration Space Map

6.4. PCI Configuration Space Map Bus Number Device Number Function Number Routing Description Soc Transaction Router Internal Graphics & Display Internal Storage Control Cluster (SD Port) Internal SATA Internal xHCI USB Internal Storage Control Cluster (MMC Port) Internal Trusted Execution Engine Internal HD Audio Internal... -

Page 38: Pci Interrupt Routing Map

6.5. PCI Interrupt Routing Map INT Line Intel IGD PCIE Root PCIE Root PCIE Root PCIE Root SD Host # 0 SD Host# 2 Port#1 Port#2 Port#3 Port#4 eMMC SD Card Int0 INTA:16 INTA:16 INTA:16 INTC:18 Int1 INTB:17 Int2 INTC:18 Int3 INTD:19 INT Line SATA... -

Page 39: Bios Setup

7. BIOS Setup 7.1. Menu Structure This section presents the six primary menus of the BIOS Setup Utility. Use the following table as a quick reference for the contents of the BIOS Setup Utility. The subsections in this section describe the submenus and setting options for each menu item. The default setting options are presented in bold, and the function of each setting is described in the right hand column of the respective table. -

Page 40: Main

7.2. Main The Main Menu provides read-only information about your system and also allows you to set the System Date and Time. Refer to the tables below for details of the submenus and settings. 7.2.1. System Information Feature Options Description BIOS Version Info only ADLINK BIOS version... -

Page 41: System Management

7.2.6. System Management 7.2.6.1. System Management > Board Information Board Information Info only SMC Firmware Read only Display SMC firmware Build Date Read only Display SMC firmware build date SMC Boot loader Read only Display SMC boot loader Build Date Read only Display SMC boot loader build date Hardware Version... - Page 42 Feature Options Description V3.30 Read only Display actual V3.30 voltage Read only Display actual VIN voltage AIN7 Read only Display actual AIN7 voltage 7.2.6.4. System Management > Runtime Statistics Feature Options Description Runtime Statistics Info only Total Runtime Read only The returned value specifies the total time in minutes the system is running in S0 state.

-

Page 43: System Date And Time

7.2.6.7. System Management > LVDS Backlight Feature Options Description LVDS Backlight Info only LVDS Backlight Bright The value range starts at 0 and ends at 255. 7.2.6.8. System Management > Smart Fan Feature Options Description Smart Fan Info only CPU Smart FanTemperature Source CPU Sensor Select CPU smart fan source System Sensor... -

Page 44: Advanced

7.3. Advanced This menu contains the settings for most of the user interfaces in the system. 7.3.1. Feature Options Description Infor only CPU Brand Name Info only Display CPU brand name CPU Signature Info only Display CPU signature Processor Family Info only Display processor family Microcode Patch... -

Page 45: Memory

7.3.2. Memory Feature Options Description Memory Info only Total Memory Info only Display total memory DIMM#0/1 Info only Display DIMM#0/1 SPD Write Protect Enabled Enabled: Writes to SMBus slave addresses A0h – Aeh are disabled Disabled Max TOLUD Dynamic Maximum value of TOLUD 7.3.3. -

Page 46: Sata

7.3.3.1. AMI Graphics Output Protocol Policy Feature Options Description Intel(R) Valley View Graphics Controller Info only Intel(R) GOP Driver Info only Output Select Output Interface. [List connect device] Brightness Setting Set GOP Brightness value [LFP device connect only] BIST Enable Enabled Starts or stops the built-in self-test (BIST) on the integrated display Disabled... -

Page 47: Network

Feature Options Description EHCI Hand-off Enabled This is a workaround for OSes without EHCI hand-off support. The Disabled EHCI ownership change should be claimed by the EHCI OS driver. USB Mass Storage Driver Support Enabled Enable/Disable USB mass storage driver support. Disabled Chipset USB Configuration Submenu... -

Page 48: Pci And Pcie

7.3.7. PCI and PCIe Feature Options Description PCI and PCIe Info only PCI Common Settings Info only PCI Latency 32 PCI Bus Clocks Value to be programmed into PCI latency timer register. 64 PCI Bus Clocks 96 PCI Bus Clocks 128 PCI Bus Clocks 160 PCI Bus Clocks 192 PCI Bus Clocks... - Page 49 Feature Options Description Unpopulated Links Keep Link ON In order to save power, software will disable unpopulated PCI Disabled Express links if this option set to Disabled. Restore PCIE Registers Enabled On non-PCI Express aware OSes (pre Windows Vista) some Disabled devices may not be correctly reinitialized after S3.

-

Page 50: Super Io

7.3.8. Super IO Feature Options Description Super IO Chip Info only W83627DHG Super IO Configuration Info only Serial Port 1 Configuration Serial Port Enabled Enable/Disable Serial Port 1 (COM0). Disabled Device Settings IO=3F8h; IRQ=4 Fixed configuration of serial port. Change Settings Auto Select an optimal setting for Super IO device. -

Page 51: Sound

7.3.10. Sound Feature Options Description Sound Info only Azalia Disabled Control detection of the Azalia device. Enabled Disabled = Azalia will be unconditionally disabled. Enabled = Azalia will be unconditionally enabled. Auto = Azalia will be enabled if present, disabled otherwise. Azalia Docking Support Disabled Enable/Disable Azalia docking support of audio controller. -

Page 52: Thermal

7.3.11.1. Serial Port Console > Console Redirection Settings Feature Options Description COM0/COM1 Console Redirection Settings Info only Terminal Type VT100 VT100: ASCII char set. VT100+ VT100+: Extends VT100 to support color, function keys, etc. VT-UTF8 VT-UTF8: Uses UTF8 encoding to map Unicode chars onto 1 or ANSI more bytes. -

Page 53: Miscellaneous

Feature Options Description Passive Trip Point Disabled This value controls the temperature of the ACPI Passive Trip Point - 90 C the point at which the OS will begin throtting the processor. 80 C Passive TC1 Value This value sets the TC1 value for the ACPI Passive Cooling Formula. -

Page 54: Boot

7.3.13.2. Miscellaneous > BIOS Security Configuration Feature Options Description BIOS Security Configuration Info only Global SMI Lock Enabled Enable or disable SMI lock. Disabled 7.3.13.3. Miscellaneous > Trusted Computing Feature Options Description Coniguration Info only Security Device Support Enabled Enables or disables BIOS support for security device. OS will Disabled not show security device. -

Page 55: Security

Feature Options Description CSM16 Module Version Info only GataA20 Active Upon Request Upon Request – GA20 can be disabled using BIOS services. Always Always – do not allow disabling of GA20; this option is useful when any RT code is executed above 1MB. Option ROM Messages Force BIOS Set display mode for Option ROM. -

Page 56: Save & Exit

7.6. Save & Exit Feature Options Description Save Changes and Exit Yes No Exit system setup after saving the changes. Discard Changes and Exit Yes No Exit system setup without saving any changes. Save Changes and Reset Yes No Reset the system after saving the changes. Discard Changes and Reset Yes No Reset system setup without saving any changes. -

Page 57: Bios Checkpoints, Beep Codes

8. BIOS Checkpoints, Beep Codes This section of this document lists checkpoints and beep codes generated by AMI Aptio BIOS. The checkpoints defined in this document are inherent to the AMIBIOS generic core, and do not include any chipset or board specific checkpoint definitions. Checkpoints and Beep Codes Definition A checkpoint is either a byte or word value output to I/O port 80h. -

Page 58: Checkpoint Ranges

8.1. Checkpoint Ranges Status Code Description Range 0x01 – 0x0B SEC execution 0x0C – 0x0F SEC errors 0x10 – 0x2F PEI execution up to and including memory detection 0x30 – 0x4F PEI execution after memory detection 0x50 – 0x5F PEI errors 0x60 –... -

Page 59: Sec Beep Codes

SEC Error Codes 0x0C – 0x0D Reserved for future AMI SEC error codes 0x0E Microcode not found 0x0F Microcode not loaded 8.2.2. SEC Beep Codes None 8.2.3. PEI Phase Status Code Description Progress Codes 0x10 PEI Core is started 0x11 Pre-memory CPU initialization is started 0x12 Pre-memory CPU initialization (CPU module specific) - Page 60 Status Code Description 0x35 CPU post-memory initialization. Boot Strap Processor (BSP) selection 0x36 CPU post-memory initialization. System Management Mode (SMM) initialization 0x37 Post-Memory North Bridge initialization is started 0x38 Post-Memory North Bridge initialization (North Bridge module specific) 0x39 Post-Memory North Bridge initialization (North Bridge module specific) 0x3A Post-Memory North Bridge initialization (North Bridge module specific) 0x3B...

-

Page 61: Pei Beep Codes

Status Code Description 0xEA S3 Resume Boot Script Error 0xEB S3 OS Wake Error 0xEC-0xEF Reserved for future AMI error codes Recovery Progress Codes 0xF0 Recovery condition triggered by firmware (Auto recovery) 0xF1 Recovery condition triggered by user (Forced recovery) 0xF2 Recovery process started 0xF3... - Page 62 Status Code Description 0x65 CPU DXE initialization (CPU module specific) 0x66 CPU DXE initialization (CPU module specific) 0x67 CPU DXE initialization (CPU module specific) 0x68 PCI host bridge initialization 0x69 North Bridge DXE initialization is started 0x6A North Bridge DXE SMM initialization is started 0x6B North Bridge DXE initialization (North Bridge module specific) 0x6C...

- Page 63 Status Code Description 0x9C USB Detect 0x9D USB Enable 0x9E – 0x9F Reserved for future AMI codes 0xA0 IDE initialization is started 0xA1 IDE Reset 0xA2 IDE Detect 0xA3 IDE Enable 0xA4 SCSI initialization is started 0xA5 SCSI Reset 0xA6 SCSI Detect 0xA7 SCSI Enable...

-

Page 64: Dxe Beep Codes

Status Code Description 0xD5 No Space for Legacy Option ROM 0xD6 No Console Output Devices are found 0xD7 No Console Input Devices are found 0xD8 Invalid password 0xD9 Error loading Boot Option (LoadImage returned error) 0xDA Boot Option is failed (StartImage returned error) 0xDB Flash update is failed 0xDC... -

Page 65: Oem-Reserved Checkpoint Ranges

8.3. OEM-Reserved Checkpoint Ranges Status Code Description 0x05 OEM SEC initialization before microcode loading 0x0A OEM SEC initialization after microcode loading 0x1D – 0x2A OEM pre-memory initialization codes 0x3F – 0x4E OEM PEI post memory initialization codes 0x80 – 0x8F OEM DXE initialization codes 0xC0 –... -

Page 66: Mechanical Information

9. Mechanical Information 9.1. Board-to-Board Connectors To allow for different stacking heights, the receptacles for COM Express carrier boards are available in two heights: 5 mm and 8 mm. When 5 mm receptacles are chosen, the carrier board should be free of components. Tyco 3-1827253-6 Foxconn QT002206-2131-3H •... -

Page 67: Thermal Solution

9.2. Thermal Solution 9.2.1. Heat Spreaders The function of the heat spreader is to ensure an identical mechanical profile for all COM Express modules. By using a heat spreader, the thermal solution that is built on top of the module is compatible with all COM Express modules. 9.2.2. - Page 68 Step 3: Put heatsink on the COM Express module and assemble the heatsink onto the COM Express module. Use the four M2.5, L=6mm screws provided to fasten the heatsink to the module. Page 68 nanoX-BT...

-

Page 69: Mounting Methods

9.3. Mounting Methods There are several standard ways to mount the COM Express module with a thermal solution onto a carrier board. In addition to the choice of 5 mm or 8mm board-to-board connectors, there is the choice of Top and Bottom mounting. In Top mounting, the threaded standoffs are on the carrier board and the thermal solution is equipped with through-hole standoffs. -

Page 70: Standoff Types

9.4. Standoff Types The standoffs available for Top and Bottom mounting methods are shown below. Note that threaded standoffs are DIP type and through- hole standoffs are SMT type. Other types not listed are available upon request. 5mm through-hole standoff (SMT type) 5mm threaded standoff (DIP type) P/N: 33-72000-0050 P/N: 33-72016-0050... -

Page 71: Safety Instructions

Safety Instructions Read and follow all instructions marked on the product and in the documentation before you operate your system. Retain all safety and operating instructions for future use. • Please read these safety instructions carefully. • Please keep this User‘s Manual for later reference. •... -

Page 72: Getting Service

5215 Hellyer Avenue, #110, San Jose, CA 95138, USA Tel: +1-408-360-0200 Toll Free: +1-800-966-5200 (USA only) Fax: +1-408-360-0222 Email: info@adlinktech.com ADLINK Technology (China) Co., Ltd. Address: 300 Fang Chun Rd., Zhangjiang Hi-Tech Park, Pudong New Area Shanghai, 201203 China Tel: +86-21-5132-8988 Fax: +86-21-5132-3588 Email: market@adlinktech.com... - Page 73 84 Genting Lane #07-02A, Cityneon Design Centre Singapore 349584 Tel: +65-6844-2261 Fax: +65-6844-2263 Email: singapore@adlinktech.com ADLINK Technology Singapore Pte. Ltd. (Indian Liaison Office) Address: #50-56, First Floor, Spearhead Towers Margosa Main Road (between 16th/17th Cross), Malleswaram Bangalore - 560 055, India Tel: +91-80-65605817, +91-80-42246107 Fax:...

Need help?

Do you have a question about the Com Express nanoX-BT and is the answer not in the manual?

Questions and answers