Table of Contents

Advertisement

Quick Links

Download this manual

See also:

User Manual

Advertisement

Table of Contents

Summary of Contents for Intel Quark D2000

- Page 1 Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

- Page 2 You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

-

Page 3: Table Of Contents

Features ................................31 Clocking ..............................33 Features ................................34 General Purpose I/O (GPIO) ........................35 Signal Descriptions ............................35 Features ................................36 10.0 JTAG ................................38 11.0 Analog-to-Digital Converter (ADC) .......................39 Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... - Page 4 Figure 26. Analog Shielding Requirements ......................39 Figure 27. Active Pull – Down circuit implementation ..................41 Tables Table 1. Terminology ................................. 8 Table 2. Reference Documents ............................. 8 Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

- Page 5 Table 12. RTC Signals................................ 34 Table 13. GPIO Pin Routing Guidelines ........................36 Table 14. Generic Routing Requirements......................... 38 Table 15. Active Pull – Down circuit BOM ........................ 42 Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN...

- Page 6 Revision History Date Revision Description November 2016 Memory specification updated. Power Delivery chapter added. December 2015 Initial release. § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

-

Page 7: Introduction

This design guide has been developed to ensure maximum flexibility for board designers while reducing the risk of board-related issues. Design recommendations are based on Intel's simulations and lab experience and are strongly recommended, if not necessary, to meet the timing and signal quality specifications. Design recommendations are based on the reference platforms designed by Intel. -

Page 8: Terminology

System on Chip Serial Peripheral Interface UART Universal Asynchronous Receiver Transmitter XTAL Crystal Reference Documents Table 2. Reference Documents Document Document No. 333577 Intel® Quark™ Microcontroller D2000 Datasheet § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 9: System Assumptions

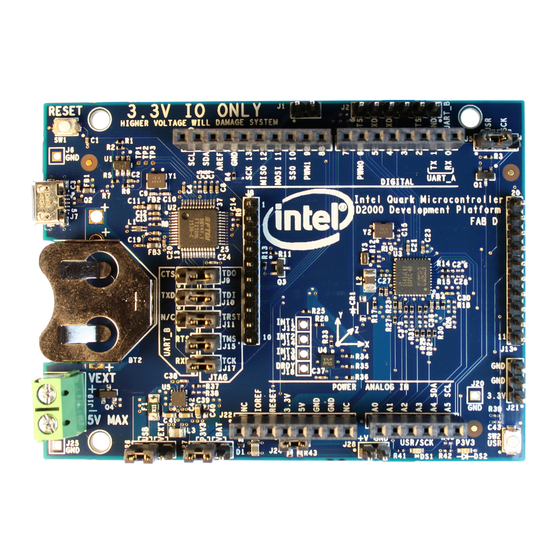

This section covers general Intel® Quark™ Microcontroller D2000 and Intel® Quark™ Microcontroller D2000 Customer Reference Board (CRB) system topology and interface connectivity assumptions. The Intel® Quark™ Microcontroller D2000 CRB is used as a baseline reference example for guidelines. Figure 1. Block Diagram Intel®... -

Page 10: Figure 2. Pcb Floor Plan

System Assumptions Figure 2. PCB Floor Plan Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 11: Pcb Technology And Stackup

The typical values, including the design and material tolerances, are centered on a nominal single line impedance specification of 50�� ± 15% for microstrip. Many interfaces specify a different nominal single-ended impedance. For more details on the Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide... -

Page 12: Figure 4. Single-Ended Microstrip Diagram

1 oz.; however, the trace thickness range defined allows for significant process variance around this nominal. Based on the Intel® Quark™ Microcontroller D2000 layout layers, 3/4 dual stripline is assumed to be built from 1 oz. copper. ... -

Page 13: Figure 5. Differential Microstrip Diagram

Soldermask 0.50 Hoz+Plating 1.80 3.94 4.2/8 Prepreg 2.70 1080 1.20 Core 50mil core 1.20 Prepreg 2.70 1080 Bottom Hoz+Plating 1.80 3.94 4.2/8 Soldermask 0.50 Finished 62.40 Thickness (mils) Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 14: Backward And Forward Coupling Coefficient Calculation

Kf is typically a very small value in most practical designs. Therefore, Intel has not included the Kf values in the design guide. However, if the value is desired, the equation for calculating Kf is provided in Figure Figure 6. -

Page 15: Feature Set

A wearable can contain any feature set and capabilities supported on Intel® Quark™ Microcontroller D2000. The following is an example feature set of a typical wearable and used in the Intel® Quark™ Microcontroller D2000 form factor. Refer to the SoC Datasheet for the latest features supported on the platform. - Page 16 2x PWM signals 25 GPIOs Real-time clock Watchdog timer Intel® Quark™ Microcontroller D2000 main expansion options: “Arduino Uno” compatible SIL sockets (3.3V I/O only) Intel® Quark™ Microcontroller D2000 on-board components: Accelerometer/Magnetometer sensor UART/JTAG to USB convert for USB debug port Other Intel®...

-

Page 17: Crb Pin Mapping

System Assumptions CRB Pin Mapping Figure 10 shows the CRB interfaces and mapping. Figure 10. CRB Pin Mapping Diagram § Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 18: Subsystem Details

Design Recommendations The Intel® Quark™ Microcontroller D2000 SoC is an ultra-low-power Intel® architecture SoC that integrates an Intel® Quark™ Microcontroller D2000 processor core, memory subsystem with on-die volatile and non-volatile storage and I/O interfaces into a single system-on-chip solution. -

Page 19: General Design Guideline Assumptions

For technical specifications (such as speeds, supported resolutions, and data rates), refer to the Intel® Quark™ Microcontroller D2000 Datasheet. 1. Follow the general guidelines in this section, if a specific interface design guide is Note: not available. -

Page 20: I²C Interface

Fast mode (≤ 400Kbps) Fast mode plus (≤ 1Mbps) 7-bit or 10-bit addressing Support for clock stretching by slave devices Multi-master arbitration Spike suppression Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 21: Interface Routing Guidelines

Length matching between Data and Clk is 540 mils Load = routing length capacitance + MCP = device pin capacitance MCP + device pin capacitance = 10 µF Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 22: General Design Considerations

The maximum bus capacitive load for each I²C bus is 400 pF. The pull-up resistor cannot be made so large that the bus time constant (Resistance X Capacitance) does not meet the I²C rise and fall time specification. § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 23: Pulse Width Modulation (Pwm)

Interrupt generation only on both edges of the PWM Output Interrupt mask capability Timer Mode 32-bit timer operating at 32MHz Timer periods from 1 32MHz clock period (31.25ns) to 2^32-1 Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 24: Pwm Signaling

In PWM Mode, the high and low times can be configured as follows. This assumes a nominal system clock frequency of 32MHz. The values, in nanoseconds, will differ if the system clock frequency is changed. Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016... -

Page 25: Table 6. Pwm Timing

0 to 134.22 s Timer Mode supports the following maskable interrupt source: Timer expiry Interrupts are cleared by reading the Timer N End of Interrupt register. § Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 26: Uart

Support for HW DMA with configurable FIFO thresholds Support for 9-bit operation mode Support for RS485 and RS232 Support for DTR/DCD/DSR/RI Modem Control Pins through GPIO pins controlled by software Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 27: Signal Descriptions

RS485 in the platform/board. Polarity is configurable. This is multiplexed onto the UART_B_CTS pin depending on RS485 or RS232 mode of operation. Figure 18. UART 2-Via Point-to-Point Topology Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 28: Features

Operation compliant with the 16550 Standard Start bit 5 to 9 bits of data Optional Parity bit (Odd or Even) 1, 1.5 or 2 Stop bits Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... - Page 29 Exception: 2.07% error for 1.391 Mbaud, 2.12% for 1.882 Mbaud and 2Mbaud, 2.53% error for 1.684 Mbaud. 9-bit data transfer mode to support a multi-drop system where one master is connected to multiple slaves in a system. § Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN...

-

Page 30: Spi

Up to 4 Slave Select pins per master interface FIFO mode support (16B TX and RX FIFOs) Support for HW DMA with configurable FIFO thresholds Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 31: Features

Control of up to 4 Slave Selects Frame formats: Motorola* SPI Texas Instruments* SSP National Semiconductor Microwire* Transfer modes: Transmit & Receive Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... - Page 32 Configurable Clock Polarity and Clock Phase Hardware Handshake Interface to support DMA capability Interrupt Control FIFO mode support with 16B deep TX and RX FIFOs § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

-

Page 33: Clocking

The RTC operates in all SoC power states. The RTC is powered from the same battery supply as the rest of the SoC and does not have its own dedicated supply. Figure 21. RTC Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide... -

Page 34: Features

Comparator for Interrupt/Wake Event generation based on the programmed Match Value Support for Interrupt/Wake Event generation when only the Counter Clock is running (Fabric Clock is off) § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 35: General Purpose I/O (Gpio)

All GPIOs support Debounce logic for interrupt sources. All 26 GPIOs are Always-on interrupt and wake capable. Signal Descriptions All GPIO pins are described in the SoC Datasheet. Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... -

Page 36: Features

The following is a list of the GPIO controller features: 26 independently configurable GPIOs Separate data register bit and data direction control bit for each GPIO Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... - Page 37 Interrupt mode supported for all GPIOs, configurable as follows: Active High Level Active Low Level Rising Edge Falling Edge Both Edge Debounce logic for interrupt sources § Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN...

-

Page 38: Jtag

JTAG 10.0 JTAG This section provides JTAG information. Figure 25. JTAG Connectivity Table 14. Generic Routing Requirements § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN... -

Page 39: Analog-To-Digital Converter (Adc)

Offset Error = +/- 2 LSB (calibration enabled), +/- 64 LSB (calibration disabled) Latencies: Power-up time of <= 10 us 1 conversion cycle = (resolution bits + 2) cycles Intel® Quark™ Microcontroller D2000 November 2016 Platform Design Guide Document Number: 333580-002EN... - Page 40 Current consumption: ~18 uA at 10 kSPS ~240 uA at 1 MSPS ~1.1 mA at 5 MSPS ~15 uA standby ~2 uA powerdown § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

-

Page 41: Power Delivery

Power Delivery 12.0 Power Delivery This chapter provides the recommendations on how to deliver the power into the Intel® Quark™ Microcontroller D2000 SoC to assure the system stability and to avoid unexpected behavior of the system, during power ON sequence especially. -

Page 42: Table 15. Active Pull - Down Circuit Bom

ON sequence, especially during hard reset. If a faulty power sequence occurs, the device may enter a high current state and become unresponsive. This high current state can lead to device heating. § Intel® Quark™ Microcontroller D2000 Platform Design Guide November 2016 Document Number: 333580-002EN...

Need help?

Do you have a question about the Quark D2000 and is the answer not in the manual?

Questions and answers