Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Alinx ACU3EG

- Page 1 ZYNQ UltraScale+ FPGA Development Board ACU3EG System on Module...

-

Page 2: Version Record

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Version Record Version Date Release By Description Rev 1.0 2021-04-23 Rachel Zhou First Release Amazon Store: https://www.amazon.com/alinx 2 / 33... -

Page 3: Table Of Contents

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Table of Contents Version Record.......................2 Part 1: ACU3EG Core Board Introduction............4 Part 2: ZYNQ Chip....................6 Part 3: DDR4 DRAM..................... 8 Part 4: QSPI Flash....................15 Part 5: eMMC Flash.................... 17 Part 6: Clock Configuration................19 Part 7: LED...................... -

Page 4: Part 1: Acu3Eg Core Board Introduction

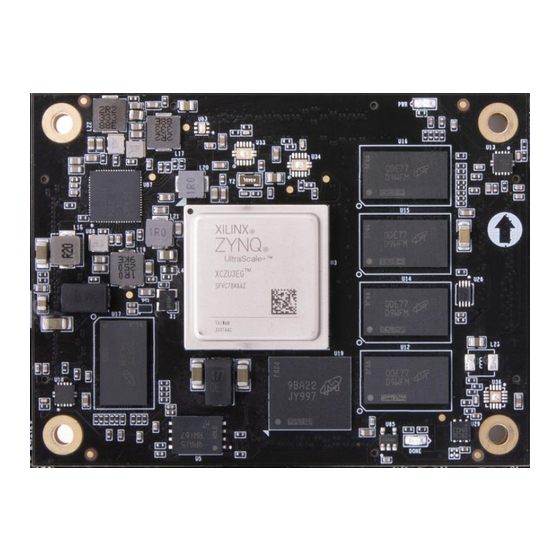

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 1: ACU3EG core board Introduction ACU3EG (core board model, the same below) FPGA core board, ZYNQ chip is based on XCZU3EG-1SFVC784I of XILINX company Zynq UltraScale+ MPSoCs EG series. This core board uses 5 Micron DDR4 chips MT40A512M16GE, of which 4 DDR4 chips are mounted on the PS side to form a 64-bit data bus bandwidth and 4GB capacity. - Page 5 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Figure 1-1: ACU3EG Core Board (Front View) Amazon Store: https://www.amazon.com/alinx 5 / 33...

-

Page 6: Part 2: Zynq Chip

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 2: ZYNQ Chip The FPGA core board ACU3Eg uses Xilinx's Zynq UltraScale+ MPSoCs EG series chip, module XCZU3EG-1SFVC784I. The PS system of the ZU3EG chip integrates 4 ARM Cortex™-A53 processors with a speed of up to 1.2Ghz and supports Level 2 Cache;... - Page 7 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual The main parameters of the PS system part are as follows: ARM quad-core Cortex ™ -A53 processor, speed up to 1.2GHz, each CPU 32KB level 1 instruction and data cache, 1MB level 2 cache, shared by 2 CPUs ...

-

Page 8: Part 3: Ddr4 Dram

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 3: DDR4 DRAM The ACU3EG core board is equipped with 5 Micron (Micron) 1GB DDR4 chips, model MT40A512M16LY-062E, of which 4 DDR4 chips are mounted on the PS side to form a 64-bit data bus bandwidth and 4GB capacity. One DDR4 chip is mounted on the PL end, which is a 16-bit data bus width and a capacity of 1GB. - Page 9 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Figure 3-1: DDR3 DRAM schematic diagram The hardware connection of DDR4 SDRAM on the Pl Side is shown in Figure 3-2: Figure 3-2: DDR3 DRAM schematic diagram Amazon Store: https://www.amazon.com/alinx 9 / 33...

- Page 10 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PS Side DDR4 DRAM pin assignment: Signal Name Pin Name Pin Number PS_DDR4_DQS0_P PS_DDR_DQS_P0_504 AF21 PS_DDR4_DQS0_N PS_DDR_DQS_N0_504 AG21 PS_DDR4_DQS1_P PS_DDR_DQS_P1_504 AF23 PS_DDR4_DQS1_N PS_DDR_DQS_N1_504 AG23 PS_DDR4_DQS2_P PS_DDR_DQS_P2_504 AF25 PS_DDR4_DQS2_N PS_DDR_DQS_N2_504 AF26 PS_DDR4_DQS3_P PS_DDR_DQS_P3_504...

- Page 11 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PS_DDR4_DQ18 PS_DDR_DQ18_504 AD25 PS_DDR4_DQ19 PS_DDR_DQ19_504 AD24 PS_DDR4_DQ20 PS_DDR_DQ20_504 AG26 PS_DDR4_DQ21 PS_DDR_DQ21_504 AH25 PS_DDR4_DQ22 PS_DDR_DQ22_504 AH26 PS_DDR4_DQ23 PS_DDR_DQ23_504 AG25 PS_DDR4_DQ24 PS_DDR_DQ24_504 AH27 PS_DDR4_DQ25 PS_DDR_DQ25_504 AH28 PS_DDR4_DQ26 PS_DDR_DQ26_504 AF28 PS_DDR4_DQ27 PS_DDR_DQ27_504 AG28 PS_DDR4_DQ28 PS_DDR_DQ28_504...

- Page 12 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PS_DDR4_DQ54 PS_DDR_DQ54_504 PS_DDR4_DQ55 PS_DDR_DQ55_504 PS_DDR4_DQ56 PS_DDR_DQ56_504 PS_DDR4_DQ57 PS_DDR_DQ57_504 PS_DDR4_DQ58 PS_DDR_DQ58_504 PS_DDR4_DQ59 PS_DDR_DQ59_504 PS_DDR4_DQ60 PS_DDR_DQ60_504 PS_DDR4_DQ61 PS_DDR_DQ61_504 PS_DDR4_DQ62 PS_DDR_DQ62_504 PS_DDR4_DQ63 PS_DDR_DQ63_504 PS_DDR4_DM0 PS_DDR_DM0_504 AG20 PS_DDR4_DM1 PS_DDR_DM1_504 AE23 PS_DDR4_DM2 PS_DDR_DM2_504 AE25 PS_DDR4_DM3 PS_DDR_DM3_504 AE28...

- Page 13 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PS_DDR4_ALERT_B PS_DDR_ALERT_N_504 PS_DDR4_BA0 PS_DDR_BA0_504 PS_DDR4_BA1 PS_DDR_BA1_504 PS_DDR4_BG0 PS_DDR_BG0_504 PS_DDR4_CS0_B PS_DDR_CS_N0_504 PS_DDR4_ODT0 PS_DDR_ODT0_504 PS_DDR4_PARITY PS_DDR_PARITY_504 PS_DDR4_RESET_B PS_DDR_RST_N_504 PS_DDR4_CLK0_P PS_DDR_CK0_P_504 PS_DDR4_CLK0_N PS_DDR_CK0_N_504 PS_DDR4_CKE0 PS_DDR_CKE0_504 PL Side DDR4 DRAM pin assignment: Signal Name Pin Name...

- Page 14 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PL_DDR4_DM1 IO_L13P_T2L_N0_GC_QBC_64 PL_DDR4_A0 IO_L8N_T1L_N3_AD5N_64 PL_DDR4_A1 IO_L3P_T0L_N4_AD15P_64 PL_DDR4_A2 IO_L8P_T1L_N2_AD5P_64 PL_DDR4_A3 IO_L3N_T0L_N5_AD15N_64 PL_DDR4_A4 IO_L11P_T1U_N8_GC_64 PL_DDR4_A5 IO_L4P_T0U_N6_DBC_AD7P_64 PL_DDR4_A6 IO_L9N_T1L_N5_AD12N_64 PL_DDR4_A7 IO_L2P_T0L_N2_64 PL_DDR4_A8 IO_L9P_T1L_N4_AD12P_64 PL_DDR4_A9 IO_L1P_T0L_N0_DBC_64 PL_DDR4_A10 IO_L4N_T0U_N7_DBC_AD7N_64 PL_DDR4_A11 IO_L7N_T1L_N1_QBC_AD13N_64 PL_DDR4_A12 IO_L6N_T0U_N11_AD6N_64 PL_DDR4_A13 IO_L1N_T0L_N1_DBC_64 PL_DDR4_BA0 IO_T1U_N12_64...

-

Page 15: Part 4: Qspi Flash

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 4: QSPI Flash The FPGA core board ACU3EG is equipped with one 256MBit Quad-SPI FLASH chip to form an 8-bit bandwidth data bus, the flash model is MT25QU256ABA1EW9, which uses the 1.8V CMOS voltage standard. Due to the non-volatile nature of QSPI FLASH, it can be used as a boot device for the system to store the boot image of the system. - Page 16 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Configure chip pin assignments: Signal Name Pin Name Pin Number MIO0_QSPI0_SCLK PS_MIO0_500 AG15 MIO1_QSPI0_IO1 PS_MIO1_500 AG16 MIO2_QSPI0_IO2 PS_MIO2_500 AF15 MIO3_QSPI0_IO3 PS_MIO3_500 AH15 MIO4_QSPI0_IO0 PS_MIO4_500 AH16 MIO5_QSPI0_SS_B PS_MIO5_500 AD16 Amazon Store: https://www.amazon.com/alinx 16 / 33...

-

Page 17: Part 5: Emmc Flash

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 5: eMMC Flash The ACU3EG core board is equipped with a large-capacity 8GB eMMC FLASH chip, the model is MTFC8GAKAJCN-4M, it supports the HS-MMC interface of the JEDEC e-MMC V5.0 standard, and the level supports 1.8V or 3.3V. - Page 18 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Configuration Chip pin assignment: Signal Name Pin Name Pin Number MMC_DAT0 PS_MIO13_500 AH18 MMC_DAT1 PS_MIO14_500 AG18 MMC_DAT2 PS_MIO15_500 AE18 MMC_DAT3 PS_MIO16_500 AF18 MMC_DAT4 PS_MIO17_500 AC18 MMC_DAT5 PS_MIO18_500 AC19 MMC_DAT6 PS_MIO19_500 AE19 MMC_DAT7...

-

Page 19: Part 6: Clock Configuration

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 6: Clock Configuration The core board provides reference clock and RTC real-time clock for PS system and PL logic respectively, so that PS system and PL logic can work independently. The schematic diagram of the clock circuit design is shown in... - Page 20 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Clock pin assignment: Signal Name PS_PADI_503 PS_PADO_503 PS System Clock Source The X1 crystal on the core board provides a 33.333MHz clock input for the PS part. The clock input is connected to the PS_REF_CLK_503 pin of BANK503 of the ZYNQ chip.

- Page 21 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Figure 6-4: PL system clock source Clock pin assignment: Signal Name PL_CLK0_P PL_CLK0_N Amazon Store: https://www.amazon.com/alinx 21 / 33...

-

Page 22: Part 7: Led

Part 7: LED There is a red power indicator (PWR) and a configuration LED (DONE) on the ACU3EG core board. When the core board is powered on, the power indicator will light up; after the FPGA configuration program, the configuration LED light will light up. -

Page 23: Part 8: Power Supply

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 8: Power Supply The power supply voltage of the ACU3EG core board is DC12V, which is supplied by connecting the carrier board. The core board uses a PMIC chip TPS6508641 to generate all the power required by the XCZU3EG chip. For the TPS6508641 power supply design, please refer to the power supply chip manual. - Page 24 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual In addition, the VCCIO power supply of BANK65 and BANK66 of XCZU3EG chip is provided by the carrier board, which is convenient for users to modify, but the maximum power supply cannot exceed 1.8V.

-

Page 25: Part 9: Acu3Eg Core Board Size Dimension

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part 9: ACU3EG Core Board Size Dimension Figure 9-1: ACU3EG Core Board Size Dimension Amazon Store: https://www.amazon.com/alinx 25 / 33... -

Page 26: Part 10: Board To Board Connectors Pin Assignment

ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Part Board Board Connectors assignment The core board has a total of four high-speed expansion ports. It uses four 120-pin inter-board connectors (J29/J30/J31/J32) to connect to the carrier board. The connectors used is Panasonic AXK5A2137YG, and the corresponding connector model in the carrier board is Panasonic AXK6A2337YG. - Page 27 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual B65_L15_P B65_L9_P B65_L15_N B65_L9_N B65_L16_P B65_L3_N B65_L16_N B65_L3_P B65_L14_P B65_L19_P B65_L14_N B65_L19_N B65_L5_N B65_L18_P B65_L5_P B65_L18_N B65_L11_N B65_L8_P B65_L11_P B65_L8_N B65_L10_N B65_L24_N B65_L10_P B65_L24_P B66_L3_P B65_L12_P B66_L3_N B65_L12_N B66_L1_P B65_L13_N B66_L1_N B65_L13_P...

- Page 28 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual B66_L11_P B66_L20_P B66_L11_N B66_L20_N B66_L12_P B66_L7_P B66_L12_N B66_L7_N B66_L13_N B66_L10_P B66_L13_P B66_L10_N B66_L8_N B66_L9_P B66_L8_P B66_L9_N Pin assignment of board to board connector J30 J30 Pin Signal Name J30 Pin Signal Name...

- Page 29 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual B66_L18_N B25_L12_P B66_L18_P B25_L12_N B25_L4_N B25_L11_P B25_L4_P B25_L11_N B26_L11_P B25_L6_N B26_L11_N B25_L6_P B26_L10_N B26_L6_N B26_L10_P B26_L6_P B26_L7_N B26_L3_N B26_L7_P B26_L3_P B26_L9_N B26_L2_N B26_L9_P B26_L2_P B26_L5_N B26_L4_N B26_L5_P B26_L4_P B26_L1_P B26_L12_P B26_L1_N B26_L12_N...

- Page 30 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual 505_TX2_P 505_RX1_P 505_TX2_N 505_RX1_N 505_RX2_P 505_RX0_P 505_RX2_N 505_RX0_N Pin assignment of board to board connector J31 J31 Pin Signal Name J31 Pin Signal Name Pin Number Number B24_L10_P B24_L7_P AA13 B24_L10_N B24_L7_N...

- Page 31 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual B24_L11_P B44_L1_P AG10 B24_L9_N B24_L4_P AE13 B24_L9_P B24_L4_N AF13 B24_L8_P AB15 B44_L5_P AE12 B24_L8_N AB14 B44_L5_N AF12 B44_L2_N AG11 B44_L4_N AF10 B44_L2_P AF11 B44_L4_P AE10 VBAT_IN B44_L11_P B44_L11_N PS_POR_B 224_CLK0_P 224_CLK1_P 224_CLK0_N...

- Page 32 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual Pin assignment of board to board connector J32 J32 Pin Signal Name Pin Number J32 Pin Signal Name Pin Number PS_MIO35 PS_MIO30 PS_MIO29 PS_MIO31 PS_MIO58 PS_MIO53 PS_MODE0 PS_MIO52 PS_MODE1 PS_MIO55 PS_MODE2 PS_MIO56...

- Page 33 ZYNQ Ultrascale + FPGA Board ACU3EG User Manual PS_MIO48 PS_MIO69 PS_MIO41 PS_MIO74 PS_MIO32 PS_MIO73 PS_MIO46 PS_MIO72 PS_MIO50 PS_MIO71 PS_MIO49 PS_MIO75 PS_MIO34 PS_MIO70 PS_MIO26 PS_MIO43 PS_MIO24 AB19 PS_MIO51 PS_MIO25 AB21 PS_MIO42 PS_MIO33 VCCO_65 VCCO_66 VCCO_65 VCCO_66 VCCO_65 VCCO_66 +12V +12V +12V...

Need help?

Do you have a question about the ACU3EG and is the answer not in the manual?

Questions and answers