Subscribe to Our Youtube Channel

Summary of Contents for SMART Embedded Computing MVME7100

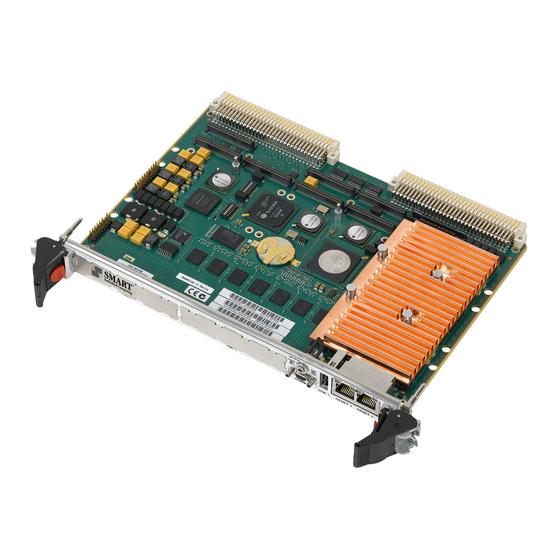

- Page 1 MVME7100 Single Board Computer Programmer’s Reference P/N: 6806800E82C September 2019...

- Page 2 Computing” and the SMART Embedded Computing logo are trademarks of SMART Modular Technologies, Inc. All other names and logos referred to are trade names, trademarks, or registered trademarks of their respective owners. These materials are provided by SMART Embedded Computing as a service to its customers and may be used for informational purposes only. Disclaimer* SMART Embedded Computing (SMART EC) assumes no responsibility for errors or omissions in these materials.

-

Page 3: Table Of Contents

3.1.16 Watch Dog Timer Load Register ........35 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 4 4.13.3 Local Bus Controller Clock Divisor........58 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 5 Related Documentation ............85 B.1 SMART Embedded Computing Documentation ....... . . 85 B.2 Manufacturers’...

- Page 6 Table of Contents MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 7 Boot Flash Bank ..........28 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 8 List of Figures MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 9 I2C Bus Device Addressing ..........50 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 10 Related Specifications ..........87 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 11: About This Manual

This manual is divided into the following chapters and appendices: Chapter 1, Introduction, provides a brief product description and a block diagram showing the architecture of the MVME7100 Single Board Computer. Chapter 2, Memory Maps, provides information on the board’s memory maps. -

Page 12: Table 1 Conventions Table

Ranges, for example: 0..4 means one of the integers 0,1,2,3, and 4 (used in registers) Logical OR Indicates a hazardous situation which, if not avoided, could result in death or serious injury MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 13 Summary of Changes This is the first edition of this manual.. Part Number Publication Date Description 6806800E82C September 2019 SMART Embedded Computing rebranding 6806800E82B June 2014 Rebranded to Artesyn template 6806800E82A January 2009 First release MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 14 About this Manual About this Manual MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 15: Introduction

Appendix B, Related Documentation, for more detail and programming information. Ordering and Support Information Refer to the data sheets for the MVME7100 SBC for a complete list of available variants and accessories. Refer to Appendix B, Related Documentation on page 85... -

Page 16: Table 1-1 Features List

One 16550-compatible, 9.6 to 115.2 Kbaud, MC864xD, asynchronous serial channel: one channel for front panel I/O One quad UART (QUART) controller to provide four 16550-compatible, 9.6 to 115.2 Kbaud, asynchronous serial channels: four channels for rear P2 I/O MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 17 Board fail User S/W controlled LED Planar status indicators One standard 16-pin JTAG/COP header Boundary scan support Switches for VME geographical addressing in a three-row backplane Software Support VxWorks OS support Linux OS support MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 18: Block Diagram

Introduction Introduction Block Diagram The following figure is a block diagram of the MVME7100 architecture. Figure 1-1 Block Diagram MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 19: Functional Description

I/O with access to the rear I/O via the MVME7216E transition module. The MVME7100 provides front panel access to one serial port with a mini DB-9 connector, two 10/100/1000 Ethernet ports with two RJ-45 connectors, and one USB port with one type A connector. - Page 20 Introduction Introduction MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 21: Memory Maps

Chapter 2 Memory Maps Overview The following sections describe the memory maps for the MVME7100. Refer to the MC864 D Reference Manual for additional details and/or programming information. 2.1.1 Default Processor Memory Map The following table describes a default memory map from the point of view of the processor after a processor reset. -

Page 22: Pci Memory Map

- 1 dram_size (on-board DRAM) 2.1.4 VME Memory Map The MVME7100 is fully capable of supporting both the PReP and the CHRP VME Memory Map examples with RAM size limited to 2GB. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 23: Register Descriptions

Overview System resources including system control and status registers, external timers, and the QUART are mapped into a 16MB address range accessible from the MVME7100 local bus via the MC864 D LBC. The memory map is defined in the following table including the LBC bank chip select used to decode the register. -

Page 24: Table 3-16 Nand Flash Chip 2 Status Register

COM 2 (QUART channel 1) F201 1FFF F201 2000 - COM 3 (QUART channel 2) F201 2FFF F201 3000 - COM 4 (QUART channel 3) F201 3FFF F201 4000 - COM 5 (QUART channel 4) F201 4FFF MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 25 External PLD Tick Timer 4 Counter Register F202 004C - Reserved F2FF FFFF F203 0000 NAND Chip 1 Data Register F203 0001 - Reserved F203 0FFF F203 1000 NAND Chip 2 Data Register F203 1001 - Reserved F203 FFFF MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 26: System Status Register

2. 32-bit write only. 3. Byte read/write capable. 3.1.1 System Status Register The MVME7100 has a System Status Register that is a read only register used to provide general board status information. Table 3-2 System Status Register System Status Register - 0xF200 0000... -

Page 27: System Control Register

A set condition indicates the switch is on. 3.1.2 System Control Register The MVME7100 has a System Control Register that provides general board control bits. Table 3-3 System Control Register System Control Register - 0xF200 0001... -

Page 28: Status Indicator Register

3.1.3 Status Indicator Register The MVME7100 provides a Status Indicator Register that may be read by the system software to determine the state of the on-board status indicator LEDs or written to by system software to illuminate the corresponding on-board LED. - Page 29 Memory Map Select. When this bit is cleared, the flash memory map is controlled by the Flash Boot Block Select switch (see the MVME7100 Installation and Use manual for switch settings). When the Map Select bit is set, boot block A is selected and mapped to the...

-

Page 30: Interrupt Register 1

Figure 3-1 Boot Flash Bank 3.1.5 Interrupt Register 1 The MVME7100 provides an Interrupt Register that may be read by the system software to determine which of the Ethernet PHYs originated their combined (OR'd) interrupt. Table 3-6 Interrupt Register 1... -

Page 31: Interrupt Register 2

3.1.6 Interrupt Register 2 The RTC, TEMP sensor and Abort switch interrupts are OR'd together. The MVME7100 provides an Interrupt Register that may be read by the system software to determine which device originated the interrupt. This register also includes bits that allow the interrupt sources to be mask. -

Page 32: Presence Detect Register

Register Descriptions Register Descriptions 3.1.7 Presence Detect Register The MVME7100 provides a Presence Detect Register that may be read by the system software to determine the presence of optional devices. Table 3-8 Presence Detect Register Presence Detect Register - 0xF200 0006... -

Page 33: Nand Flash Chip 1 Select Register

RSVD Reserved for future implementation. 3.1.9 NAND Flash Chip 1 Select Register The MVME7100 provides a Select Register for the NAND flash device. Table 3-10 NAND Flash Chip 1 Select Register NAND Flash Chip 1 Select Register - 0xF200 0011... -

Page 34: Nand Flash Chip 1 Presence Register

Register Descriptions Register Descriptions 3.1.10 NAND Flash Chip 1 Presence Register The MVME7100 provides a Presence Register for the NAND flash device. Table 3-11 NAND Flash Chip 1 Presence Register NAND Flash Chip 1 Presence Register - 0xF200 0014 Field... -

Page 35: Nand Flash Chip 2 Control Register

Register Descriptions 3.1.12 NAND Flash Chip 2 Control Register The MVME7100 provides a Control Register for the NAND flash device. Table 3-13 NAND Flash Chip 2 Control Register NAND Flash Chip 2 Control Register - 0xF200 0018 Field RSVD RSVD... -

Page 36: Nand Flash Chip 2 Presence Register

RSVD Reserved for future implementation. 3.1.14 NAND Flash Chip 2 Presence Register The MVME7100 provides a Presence Register for the NAND flash device. Table 3-15 NAND Flash Chip 2 Presence Register NAND Flash Chip 2 Presence Register - 0xF200 001C... -

Page 37: 3.1.16 Watch Dog Timer Load Register

System Reset. If cleared a board-level reset is generated when a time-out occurs. If set, a VMEbus SYSRST is generated when a time-out occurs. If MVME7100 is SYSCON then a local reset will also result in a VMEbus SYSRST. Enable. If cleared the watch dog timer is disabled. If set the watch dog timer is enabled. -

Page 38: 3.1.18 Watch Dog Timer Resolution Register

Register Descriptions Register Descriptions 3.1.18 Watch Dog Timer Resolution Register The MVME7100 provides a watch dog timer resolution register. Table 3-19 Watch Dog Timer count Register Watch Dog Timer Resolution Register - 0xF200 0025 Field RSVD RSVD RSVD RSVD OPER RESET Resolution. -

Page 39: 3.1.19 Watch Dog Timer Count Register

If the counter reaches zero a system or board-level reset will be generated. 3.1.20 PLD Revision Register The MVME7100 provides a PLD revision register that can be read by the system software to determine the current revision of the timers/registers PLD. Table 3-21 PLD Revision Register... -

Page 40: Pld Date Code Register

Register Descriptions Register Descriptions 3.1.21 PLD Date Code Register The MVME7100 PLD provides a 32-bit register which contains the build date code of the inters/registers PLD. Table 3-22 PLD Date Code Register Test Register 1 - 0xF200 0034 31:24 23:16... -

Page 41: Test Register 2

Register Descriptions 3.1.23 Test Register 2 The MVME7100 provides a second 32-bit test register that reads back the complement of the data in Test Register 1. Table 3-24 Test Register 2 Test Register 2 - 0xF200 003C 31:0 Field TEST2... -

Page 42: 3.1.24.2 Control Registers

ENINT Enable Interrupt. When the bit is set the interrupt is enabled. When the bit is cleared the interrupt is not enabled. CINT Clear Interrupt. INTS Interrupt Status. RSVD Reserved for future implementation. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 43: 3.1.24.3 Compare Register

Tick Timer 2 Counter Register - 0xF202 0028 (32 bits) Tick Timer 3 Counter Register - 0xF202 0038 (32 bits) Tick Timer 4 Counter Register - 0xF202 0048 (32 bits) … Field Tick Timer Counter Value OPER RESET MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 44: Geographical Address Register

The VMEbus Status Register in the Tsi148 provides the VMEbus geographical address of the MVME7100. This register reflects the inverted states of the geographical address pins at the 5-row, 160-pin P1 connector. Applications not using the 5-row backplane can use the planar switch described in the MVME7100 Installation and Use manual to assign a geographical address. -

Page 45: Programming Details

Clock Distribution on page 57 MC864xD Reset Configuration The MVME7100 supports the power-on reset (POR) pin sampling method for processor reset configuration. The states of the various configuration pins on the processor are sampled when reset is deasserted to determine the desired operating modes. -

Page 46: Table 4-1 Mc864Xd Por Configuration Settings

1_0000 LDP[0:3], (e600 Core: Resistors 0_1000 for LA[27] MPX Clock) 1_1100 3.5:1 1.067GHz 1_0100 processor 0_1110 4.5:1 Core 1 disabled TSEC3_TX Core 1 (no option Resistor D[2] Enable Core 1 enabled disabled) MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 47 Local Bus GPCM -32 -bit ROM 1 (no PCI-E 1 outbound ATMU window Alternate option pull- 1 is enabled TSEC1_TX Resistor Boot Vector down) D[0] Location Boot vector fetched from default boot ROM location MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 48 1010 SerDes2: x4 Serial RapidIO SerDes1: disabled 1011 SerDes2: x4 Serial RapidIO SerDes1: disabled 1110 SerDes2: x1/x2/x4/x8 PCIE SerDes1: x1/x2/x4/x8 PCI-E, 100 MHz ref clk 1111 SerDes2: x1/x2/x4/x8 PCI-E, 100 MHz ref clk MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 49 Normal I2C addressing Boot LGPL3, Testpoints Sequencer Extended I2C addressing LGPL5 Configuration Boot sequencer is disabled TSEC2_TX DDR1 D[4] DDR SDRAM Connects Type TSEC2_TX (default) DDR2 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 50 DDR debug information is driven on the ECC pins instead of the D1_MSRCI DDR Debug normal ECC I/O. (processor D[1] Connect Configuration default) DDR debug information is not driven on the ECC pins. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 51: Mc864Xd Interrupt Controller

Programming Details MC864xD Interrupt Controller The MVME7100 uses the MC864xD integrated programmable interrupt controller (PIC) to manage locally generated interrupts. Currently defined external interrupting devices and interrupt assignments, along with corresponding edge/levels and polarities, are shown in the following table. -

Page 52: Local Bus Controller Chip Select Assignments

C controller is used by the system software to read the contents of the various I C devices located on the MVME7100. The following table contains the I C devices used for the MVME7100 and their assigned device addresses. Table 4-4 I2C Bus Device Addressing Device Address... -

Page 53: User Configuration Eeprom

Documentation, for additional details. VPD EEPROM The MVME7100 board provides an 8 KB dual address serial EEPROM containing Vital Product Data (VPD) configuration information specific to the MVME7100. Typical information that may be present in the EEPROM may include: manufacturer, board revision, build version, date of assembly, memory present, options present, L2 cache information, etc. -

Page 54: Rtm Vpd Eeprom

RTM VPD EEPROM The MVME7100 RTM provides an 8 KB dual address serial EEPROM containing VPD configuration information specific to the MVME7100 RTM. Typical information that may be present in the EEPROM may include: manufacturer, board revision, build version, date of assembly, options present, etc. -

Page 55: Flash Memory

512 megabit AMD-0001h 7E23h A hardware flash bank write-protect switch is provided on the MVME7100 to enable write protection of the NOR flash. Regardless of the state of the software flash write-protect bit in the NOR Flash Control/Status register, write protection is enabled when this switch is ON. -

Page 56: Pci/Pci-X Configuration

0b0_0010 Tsi148 VME (PEX8114) IRQ3 IRQ0 IRQ1 IRQ2 PCI4 INTC INTA INTB uPD720101 0b0_0010 (PEX8112) IRQ3 IRQ0 IRQ1 IRQ2 Refer to the MC864xD reference manual for additional details about the MC864xD PIC operation. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 57: Pci Arbitration Assignments

The integrated PCI/X arbiters internal to the PEX8112 and the PEX8114 provide PCI arbitration for the MVME7100. The arbitration assignments on the MVME7100 are shown in the next table so that software may set arbiter priority assignments if necessary. Table 4-10... -

Page 58: Other Software Considerations

LBC Timing Parameters NAND MRAM UART Timers Flash Flash Flash BCTLD CSNT XACS SETA TRLX EHTR 4.12.2 USB Oscillator Configuration Software must configure the USB chip for the correct clock input of 48MHz. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 59: Clock Distribution

PCI/PCI-X bus clocks are generated by the bridge chips from the PCI-E clock. Additional clocks required by individual devices are generated near the devices using individual oscillators. The following table lists the clocks required on the MVME7100 along with their frequency and source. -

Page 60: System Clock

This provides a fixed clock reference for the MC864xD PIC timers which software can use as a known timing reference. 4.13.3 Local Bus Controller Clock Divisor The Local Bus Controller (LBC) clock output is connected to the PLD but is not used by the internal logic. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 61: Programmable Configuration Data

Programmable Configuration Data Overview This appendix provides data and specifications pertaining to programmable parts used on the MVME7100. The board is shipped after the programmable parts have been programmed through ATE or boundary scan according to the in-circuit test specifications. Table A-1... -

Page 62: Vital Product Data (Vpd) Introduction

If the VPD information becomes corrupted, the following occurs: A warning message is displayed in the startup banner. The firmware ignores the VPD contents and attempts to acquire information from other sources. Some device drivers will not work. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 63: How To Fix Corrupted Vpd Information

If you suspect that your board has problems as a result of wrong VPD information, select SAFE mode by setting S1:1 ON and reboot the MVME7100. At this point, the firmware will ignore all SROM contents. Use SROM or the IBM command to change the VPD to the correct parameters. - Page 64 (dataBitValue = 0; dataBitValue < 8; dataBitValue++) msbDataBitValue = (crcValue >> 31) & 1; crcValue <<= 1; if (msbDataBitValue ^ (dataByte & 1)) crcValue ^= 0x04c11db6; crcValue |= 1; dataByte >>= 1; MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 65: Serial Presence Detect Checksum Calculation

Serial PD Convert to Decimal 00 (0x00) 0010 0100 > 01 (0x01) 1111 1110 > + 254 02 (0x02) 0000 0000 > 03 (0x03) 0000 0000 > > > 60 (0x3C) 0000 0000 > MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 66: A.10 Vpd Contents For Mvme7100 Boards

Size of VPD area in bytes. The size is viewed as logical; it is not the size of the EEPROM. 512 bytes in this VPD architecture BINARY VPD Revision Packet BINARY # of Bytes MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) -

Page 67: Table A-4 Static Vpd Contents

Board Type: Processor Board BINARY Architecture Revision BINARY Board Build Revision BINARY Revision Reason Flags BINARY Product Identifier Packet Refer to Notes 1 and BINARY # of bytes ASCII Product Identifier. Table A-5 Refer to MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 68 **Serial number to be filled in. Refer to Notes BINARY # of bytes ASCII Most significant serial number character Least significant serial number character BINARY External Processor Clock Frequency Packet BINARY # of bytes MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 69 Ethernet Controller 0 BINARY Ethernet MAC Address Packet BINARY # of bytes BINARY Six bytes containing the next Ethernet address. BINARY Ethernet Controller 1 BINARY Ethernet MAC Address Packet BINARY # of bytes MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 70 Ethernet MAC Address Packet BINARY # of bytes BINARY Six bytes containing the highest Ethernet address. BINARY Ethernet Controller 3 BINARY Processor Identifier Packet BINARY # of bytes ASCII Processor type Table A-5 Refer to MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 71 Flash bank number BINARY Flash access speed in nanoseconds: 0x6E = 110 ns BINARY Total bank size [(1<<n)*256K bytes]: 0x09 = 128 MB BINARY Bank 2 Flash Memory Configuration Packet BINARY # of bytes MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 72 For this reason, these packets shall have fixed sizes and shall immediately follow the header. 3. This data is not static. Each board's Serial Number packet must be unique. The board's serial number is obtained from the onboard serial number label. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 73: Table A-5 Variable Vpd Contents

0x32 represents the assembly revision letter (A=41, B=42, etc.). Table A-5 Variable VPD Contents Offset MVME7100-161 MVME7100-163 MVME7100-171 MVME7100-173 (Hex) 0106839D01* 0106839D02* 0106839D03* 0106839D04* Product Identifier (ASCII) Factory Assembly Number (ASCII) MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 74 Programmable Configuration Data Programmable Configuration Data Table A-5 Variable VPD Contents (continued) Offset MVME7100-161 MVME7100-163 MVME7100-171 MVME7100-173 (Hex) 0106839D01* 0106839D02* 0106839D03* 0106839D04* Processor Type NAND Flash Size MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 75: A.11 Spd Contents For Mvme7100 Boards

Primary SDRAM Width: 0x08 = 8 bits 14 (0x0E) Error Checking SDRAM Width: 0x08 = 8 bits 15 (0x0F) Reserved 16 (0x10) SDRAM Device Attributes - Burst Lengths Supported: 0x0C = 4, and 8 burst lengths MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 76 Minimum RAS to CAS delay (t RCD): 0x3C = 15ns. Refer to Note 30 (0x1E) Minimum RAS Pulse width (t RAS): 0x2D = 45ns. Refer to Note 31 (0x1F) Module Bank Density: 0x80 = 512 MB MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 77 Tcasemax: 0x50 = 95 degree max case temperature 48 (0x30) Not Used 49 (0x31) 0x03 = Double refresh mode bit and High temperature self-refresh 50 (0x32) Not Used 51 (0x33) Not Used 52 (0x34) Not Used MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 78 65 (0x41) 66 (0x42) 67 (0x43) 68 (0x44) 69 (0x45) 70 (0x46) 71 (0x47) 72 (0x48) Module Manufacturing location. Refer to Note 73 (0x49) Module Part Number. Refer to Note 74 (0x4A) 75 (0x4B) MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 79 91 (0x5B) Module Revision Code. Refer to Note 92 (0x5C) 93 (0x5D) Module Manufacturing Date. Refer to Note 94 (0x5E) 95 (0x5F) Module Serial Number. Refer to Note 96 (0x60) 97 (0x61) 98 (0x62) MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 80: Table A-7 Variable Spd Contents

Number of DIMM Banks: 0x00 = one bank 06 (0x06) Data Width of this assembly: 0x48 = 72 bits 07 (0x07) Reserved 08 (0x08) Voltage Interface Level of this assembly: 0x05 = SSTL 1.8 V MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 81 Refer to Note 23 (0x17) Minimum Clock Cycle at CLX-1: 0x3D = 3.75ns. Refer to Note 24 (0x18) Maximum Data Access Time (t AC) from Clock at CLX-1: 0x50 = 0.50ns. Refer to Note MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 82 Internal Read to Precharge Command Delay (t RTP): 0x1E = 7.5ns 39 (0x27) Reserved 40 (0x28) Extension of Byte 41 and 42 41 (0x29) Minimum Active to Active/Auto Refresh Time (t RC) 0x3C = 60ns MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 83 61 (0x3D) Not Used 62 (0x3E) SPD Revision 0x12 = revision level 1.2 63 (0x3F) Checksum for bytes 0 - 62. Refer to Section 0 64 (0x40) Manufactures JEDEC ID Code. Refer to Note MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 84 Refer to Note 74 (0x4A) 75 (0x4B) 76 (0x4C) 77 (0x4D) 78 (0x4E) 79 (0x4F) 80 (0x50) 81 (0x51) 82 (0x52) 83 (0x53) 84 (0x54) 85 (0x55) 86 (0x56) 87 (0x57) 88 (0x58) 89 (0x59) MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 85 1. This will typically be programmed as 128 bytes. 2. his will typically be programmed as 256 bytes. 3. From data sheet. 4. High order bit is self-refresh flag. If set to 1, the assembly supports self refresh. 5. Reserved. MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 86 Programmable Configuration Data Programmable Configuration Data MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 87: Related Documentation

The documentation listed is referenced in this manual. Technical documentation can be found by using the Documentation Search at https://www.smartembedded.com/ec/support/ or you can obtain electronic copies of SMART Embedded Computing documentation by contacting your local sales representative. Table B-1 SMART EC Documentation... - Page 88 ESD-Protected, 1µA, 3.0V to 5.5V, 250kbps, Rev 5 RS-232 Transceivers with AutoShutdown 10/03 MAX811/MAX812 19-0411 4-Pin µP Voltage Monitors Rev 3 With Manual Reset Input 3/99 MAX6649 Digital Temperature Sensor 19-2450 Rev 3 05/07 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

-

Page 89: Related Specifications

Table B-3 Related Specifications Organization and Document Document Number Vita Standards Organization VME64 ANSI/VITA 1-1994 VME64 Extensions ANSI/VITA 1.1-1997 2eSST Source Synchronous Transfer ANSI/VITA 1.5-2003 MVME7100 Single Board Computer Programmer’s Reference (6806800E82C) - Page 90 Institute for Electrical and Electronics Engineers, Inc. Draft Standard for a Common Mezzanine Card Family: CMC P1386 - 2001 Draft Standard Physical and Environmental Layer for PCI Mezzanine P1386 - 2001 Cards: PMC MVME7100 Single Board Computer Programmer’s Reference (6806800E82C)

- Page 92 © 2019 SMART Embedded Computing™, Inc. All rights reserved. The stylized “S” and “SMART” is a registered trademark of SMART Modular Technologies, Inc. and “SMART Embedded Computing” and the SMART Embedded Computing logo are trademarks of SMART Modular Technologies, Inc. All other names and logos...

Need help?

Do you have a question about the MVME7100 and is the answer not in the manual?

Questions and answers