Xilinx Virtex-7 FPGA VC7222 Getting Started Manual

Characterization kit ibert

Hide thumbs

Also See for Virtex-7 FPGA VC7222:

- Getting started manual (68 pages) ,

- User manual (65 pages) ,

- Getting started manual (44 pages)

Summary of Contents for Xilinx Virtex-7 FPGA VC7222

- Page 1 Virtex-7 FPGA VC7222 Characterization Kit IBERT Getting Started Guide UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 2: Revision History

Revision History The following table shows the revision history for this document. Date Version Revision Initial Xilinx release. 09/20/2013 09/24/2013 1.0.1 Updated the Notice of Disclaimer, page 2.. 11/07/2013 Updated for Vivado® Design Suite 2013.3. Updated most figures in Chapter 1, VC7222 IBERT Getting Started Guide. - Page 3 Figure 1-29, Figure 1-31, Figure 1-32, Figure 2-1, Figure 2-4, Figure 2-8, Figure 3-1, and Figure 3-5. Version changed to match the software release. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 4: Table Of Contents

Xilinx Resources ........ -

Page 5: Overview

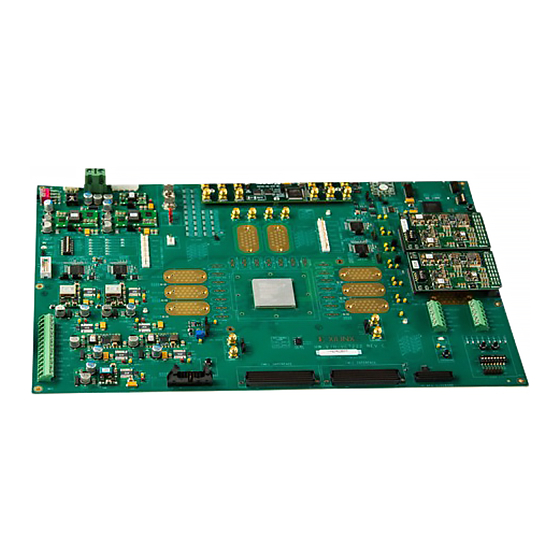

Virtex-7 FPGA VC7222 Characterization Kit documentation website. The VC7222 board is described in detail in Virtex-7 FPGA VC7222 GTH and GTZ Transceiver Characterization Board User Guide (UG965) [Ref The IBERT GTH demonstration operates one GTH Quad at a time. The procedure consists of:... -

Page 6: Requirements

Requirements The hardware and software required to run the GTH and GTZ IBERT demonstration are listed here: • Virtex-7 FPGA VC7222 GTH and GTZ Transceiver Characterization Board. The kit includes: One SD card containing the IBERT demonstration designs ° One Samtec BullsEye™ cable °... -

Page 7: Setting Up The Vc7222 Board For Gth And Gtz Ibert Testing

IBERT demonstrations. 1. Move all jumpers and switches to their default positions. The default jumper and switch positions are listed in Virtex-7 FPGA VC7222 GTH and GTZ Transceiver Characterization Board User Guide (UG965) [Ref 2. - Page 8 SuperClock-2 module (described in Starting the SuperClock-2 Module, page 20 in the GTH section and Starting the SuperClock-2 Module, page 36 in the GTZ section). VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 9: Running The Gth Ibert Demonstration

GTH transceiver Quads on the Rev. 1 VC7222 board. X-Ref Target - Figure 1-1 Figure 1-1: GTH Quad Location VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015... - Page 10 Figure 1-2 B shows the connector pinout. X-Ref Target - Figure 1-2 Figure 1-2: A – GTH Connector Pad. B – GTH Connector Pinout VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 11 For the GTH IBERT demonstration, the output clock frequencies are preset to 325.00 MHz. For more information regarding the SuperClock-2 module, see the HW-CLK-101-SCLK2 SuperClock-2 Module User Guide (UG770) [Ref VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 12 Note: X-Ref Target - Figure 1-4 Figure 1-4: BullsEye Connector with Elastomer Seal VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 13 Any one of the five differential outputs from the SuperClock-2 module can be used to source Note: the GTH reference clock. CLKOUT1_P and CLKOUT1_N are used here as an example. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 14 SMAs. X-Ref Target - Figure 1-6 Figure 1-6: SMA F-F Adapter X-Ref Target - Figure 1-7 Figure 1-7: TX-To-RX Loopback Connection Example VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 15 The FPGA can also be configured through Vivado Design Suite using the .bit files available on the SD card, or online (as collection rdf0297-vc7222-ibert-2015-1.zip) at the Virtex-7 FPGA VC7222 Characterization Kit documentation website. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 16 GTH Quad 213 GTH Quad 214 GTH Quad 215 GTZ Quad 300A and 300B USB/UART 5. Place the main power switch SW1 to the ON position. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 17 1. Start Vivado Design Suite on the host computer and click Flow > Open Hardware Manager (highlighted in Figure 1-10). X-Ref Target - Figure 1-10 Figure 1-10: Vivado Design Suite, Open Hardware Manager VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 18 3. An Open Hardware Target wizard starts. Click Next to run the wizard. 4. In the Hardware Server Settings window, select Local server (target is on local machine). Click Next to open the server and connect to the Xilinx TCF JTAG cable. VC7222 IBERT Getting Started Guide www.xilinx.com...

- Page 19 Figure 1-12: Select Hardware Target 6. In the Open Hardware Target Summary window, click Finish. The wizard closes and the Vivado Design Suite opens the hardware target. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 20 Hardware Device Properties window, enter the file path to the Q115 Probes file (vc7222_ibert_q115_debug_nets.ltx) in the extracted IBERT files from the SD card (Figure 1-13). X-Ref Target - Figure 1-13 Figure 1-13: Adding the Probes File VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 21 If the FPGA was not programmed using the SD card, provide both the programming and Note: Program Device the probes files, and then select X-Ref Target - Figure 1-14 Figure 1-14: Program/Refresh Device VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 22 1-15). In the Run Script window, navigate to the setup_scm2_325_00.tcl script in the extracted files and click OK. X-Ref Target - Figure 1-15 Figure 1-15: Run TCL Script VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 23 SuperClock-2 frequencies and their associated ROM addresses is provided in Table 1-2. X-Ref Target - Figure 1-16 Figure 1-16: SuperClock-2 Module VIO Core VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 24 Create Links, or by clicking the Create Links button (Figure 1-17). X-Ref Target - Figure 1-17 Figure 1-17: Serial I/O Analyzer—Create Links VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 25 (Figure 1-18): MGT_X1Y8/TX to MGT_X1Y8/RX MGT_X1Y9/TX to MGT_X1Y9/RX MGT_X1Y10/TX to MGT_X1Y10/RX MGT_X1Y11/TX to MGT_X1Y11/RX X-Ref Target - Figure 1-18 Figure 1-18: Create Links Window VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 26 The line rate for all four GTH transceivers is 13.0 Gb/s (see the Status column in Figure 1-19). • Verify that there are no bit errors. X-Ref Target - Figure 1-19 Figure 1-19: Serial I/O Analyzer Links VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 27 To stop the IBERT demonstration: 1. Close the Vivado Design Suite application by selecting File > Exit. 2. Place the main power switch SW1 in the off position. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 28: Running The Gtz Ibert Demonstration

GTZ transceiver Quads (GTZ Quads Q300A and Q300B) on the Rev. B VC7222 board. X-Ref Target - Figure 1-20 Figure 1-20: GTZ Quad Location VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015... - Page 29 IBERT demonstration. For the GTZ IBERT demonstration, the output clock frequency is preset to 255.00 MHz. See the description for connecting the SuperClock-2 module, page 10, for more details. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 30 BullsEye cable is available, make sure to power down the board before moving the BullsEye cable to the second half of the GTZ lanes X-Ref Target - Figure 1-22 Figure 1-22: BullsEye Connector Attached to GTZ Quads Q300A and Q300B VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 31 GTZ reference clock CLK1 (J46 and J47) can be left disconnected. Note: X-Ref Target - Figure 1-23 Figure 1-23: GTZ CLK0 and CLK1 Connection VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 32 TX7_N → SMA F-F Adapter → RX7_N To ensure good connectivity, it is recommended that the adapters be secured with a wrench, Note: however do not over-tighten the SMA connectors. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 33 This section describes how to configure the FPGA using the SD card included with the Virtex-7 FPGA VC7222 GTH and GTZ Transceiver Characterization Board. The FPGA can also be configured through Vivado Design Suite using the .bit files available on the SD card, or online (as collection rdf0297-vc7222-ibert-2015-1.zip) at the...

- Page 34 Figure 1-25: Configuration Address DIP Switch (SW8) 5. Place the main power switch SW1 to the ON position. Table 1-1 for more details on the System ACE configuration. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 35 10 MHz or lower for reliable JTAG communication during the GTZ demonstration (Figure 1-26). X-Ref Target - Figure 1-26 Figure 1-26: Select Hardware Target VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 36 Hardware Device Properties window, enter the file path to the Q300 Probes file (vc7222_ibert_q300_debug_nets.ltx) in the extracted IBERT files from the SD card (Figure 1-27). X-Ref Target - Figure 1-27 Figure 1-27: Adding the Probes File VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 37 If the FPGA was not programmed using the SD card, provide both the programming and Note: Program Device the probes files, and then select X-Ref Target - Figure 1-28 Figure 1-28: Program/Refresh Device VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 38 1-29). In the Run Script window, navigate to the setup_scm2_255_00.tcl script in the extracted files and click OK. X-Ref Target - Figure 1-29 Figure 1-29: Run TCL Script VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 39 SuperClock-2 frequencies and their associated ROM addresses is provided in Table 1-2. X-Ref Target - Figure 1-30 Figure 1-30: SuperClock-2 Module VIO Core VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 40 Create Links, or by clicking the Create Links button (Figure 1-31). X-Ref Target - Figure 1-31 Figure 1-31: Serial I/O Analyzer - Create Links VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 41 Lane4/TX to Lane4/RX ° Lane5/TX to Lane5/RX ° Lane6/TX to Lane6/RX ° Lane7/TX to Lane7/RX ° X-Ref Target - Figure 1-32 Figure 1-32: Create Links Window VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 42 Q300B, all Q300A lanes must be set in loopback mode. If the BullsEye cable is connected to Q300B, all Q300A lanes must be set in loopback mode. X-Ref Target - Figure 1-33 Figure 1-33: Serial I/O Analyzer Links VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 43: Superclock-2 Frequency Table

666.514 Generic CPRI 491.52 OTU-1 666.75 Generic 666.667 Display Port 67.5 OTU-2 167.33 Generic Display Port OTU-2 669.31 Generic Display Port OTU-3 168.05 Generic VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015... - Page 44 Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic Generic VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 45: Chapter 2: Creating The Gth Ibert Core

2. In the Vivado window, click the Manage IP icon highlighted in Figure 2-1, then select New IP Location. X-Ref Target - Figure 2-1 Figure 2-1: Initial Window, Vivado Design Suite VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015... - Page 46 Part field. A Select Device window pops up. Use the drop-down menu items to narrow the choices. Select the xc7vh580thcg1155-2G device (Figure 2-2). Click OK. X-Ref Target - Figure 2-2 Figure 2-2: Select Device VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 47 (Figure 2-3). Click Finish. Make sure the directory name does not include spaces. Note: X-Ref Target - Figure 2-3 Figure 2-3: Manage IP Settings VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 48 6. In the IP Catalog window, open the Debug & Verification folder, then open the Debug folder, and double-click IBERT 7 Series GTH (Figure 2-4). X-Ref Target - Figure 2-4 Figure 2-4: IP Catalog VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 49 LineRate(Gbps) to 13.0. Use the drop-down menu to change the Refclk(MHz) to 325.00. Do not change other defaults (Figure 2-5). X-Ref Target - Figure 2-5 Figure 2-5: Customize IP - Protocol Definition VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 50 8. In the Protocol Selection tab, use the Protocol Selected drop-down menu next to QUAD_115 to select Custom 1/13.0 Gbps (Figure 2-6). X-Ref Target - Figure 2-6 Figure 2-6: Customize IP - Protocol Selection VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 51 2-7). Click OK. Click Generate in the next window to generate the output products. X-Ref Target - Figure 2-7 Figure 2-7: Customize IP - Clock Settings VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 52 2-8). Specify a location to save the design, press OK, and the design opens in a new Vivado window. X-Ref Target - Figure 2-8 Figure 2-8: Open IP Example Design VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 53 OK. The SuperClock-2 Module Design Sources and Constraints are automatically added to the example design (Figure 2-9). X-Ref Target - Figure 2-9 Figure 2-9: Sources after Running add_scm2.tcl VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 54 (Figure 2-10). Click File > Save File. X-Ref Target - Figure 2-10 Figure 2-10: SuperClock-2 in the Example IBERT Wrapper VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 55 13. In the Sources window, Design Sources should now reflect that the SuperClock-2 module is part of the example IBERT design (Figure 2-11). X-Ref Target - Figure 2-11 Figure 2-11: Design Sources File Hierarchy VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 56 15. When synthesis is done, a Synthesis Complete window pops up. Select Open Synthesized Design and click OK (Figure 2-13). X-Ref Target - Figure 2-13 Figure 2-13: Synthesis Completed VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 57 2-15). A window pops up asking if it is ok to launch implementation. Click Yes. X-Ref Target - Figure 2-15 Figure 2-15: Generate Bitstream VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 58 (Figure 2-16). X-Ref Target - Figure 2-16 Figure 2-16: Bitstream Generation Completed 19. The generated bitstream is located in the following directory: ..\ibert_7series_gtz_0\ibert_7series_gtz_0_example\ibert_7series _gtz_0_example.runs\impl_1 VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 59: Chapter 3: Creating The Gtz Ibert Core

Programming and Debugging (UG908) [Ref See steps 1–5 in Chapter 2, Creating the GTH IBERT Core to learn how to create a new IP core. Note: VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015... - Page 60 Debug folder. Double-click or right-click the IBERT 7 Series GTZ to run the GTZ configuration wizard (Figure 3-1). X-Ref Target - Figure 3-1 Figure 3-1: IP Catalog VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 61 200 MHz, the input Standard to LVDS, the P and N Pin location to AL24 and AL25, respectively (Figure 3-2). X-Ref Target - Figure 3-2 Figure 3-2: Customize IP - Design Options VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 62 The same frequency should be set in the setup_scm2_freq_00_xx.tcl script by modifying the set frequency statement. X-Ref Target - Figure 3-3 Figure 3-3: Customize IP - Protocol Selection VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 63 Generate Output Products window opens. Leave the defaults unchanged, and press Generate. X-Ref Target - Figure 3-4 Figure 3-4: Customize IP - GTZ Lane Selection VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 64 3-5). Specify a location to save the design, press OK, and the design opens in a new Vivado window. X-Ref Target - Figure 3-5 Figure 3-5: Open IP Example Design VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 65 Add the top level ports from top_scm2.v to the module declaration and instantiate the top_scm2 module in the example IBERT wrapper (Figure 3-7). Click File > Save File. VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 66 Chapter 3: Creating the GTZ IBERT Core X-Ref Target - Figure 3-7 Figure 3-7: SuperClock-2 in the Example IBERT Wrapper VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 67 7. In the Sources window, Design Sources should now reflect that the SuperClock-2 module is part of the example IBERT design (Figure 3-8). X-Ref Target - Figure 3-8 Figure 3-8: Design Sources File Hierarchy VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 68 9. When synthesis is done, a Synthesis Complete window pops up. Select Open Synthesized Design and click OK (Figure 3-10). X-Ref Target - Figure 3-10 Figure 3-10: Synthesis Completed VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 69 11. In the Project Manager window, under Program and Debug, click Generate Bitstream. Confirm the launching of implementation (Figure 3-12). X-Ref Target - Figure 3-12 Figure 3-12: Generate Bitstream VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

- Page 70 (Figure 3-13). X-Ref Target - Figure 3-13 Figure 3-13: Bitstream Generation Completed 13. The generated bitstream is located in the following directory: ..\ibert_7series_gtz_0\ibert_7series_gtz_0_example\ibert_7series _gtz_0_example.runs\impl_1 VC7222 IBERT Getting Started Guide www.xilinx.com Send Feedback UG971 (Vivado Design Suite v2015.1) April 27, 2015...

-

Page 71: Appendix A: Additional Resources And Legal Notices

Virtex-7 FPGA VC7222 Characterization Kit Master Answer Record (AR 54015) These Xilinx documents provide supplemental material useful with this guide: 1. Virtex-7 FPGA VC7222 GTH and GTZ Transceiver Characterization Board User Guide (UG965) 2. HW-CLK-101-SCLK2 SuperClock-2 Module User Guide (UG770) 3. -

Page 72: Please Read: Important Legal Notices

Xilinx’s Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance;... - Page 73 Customer. For any breach by Xilinx of this limited warranty, the exclusive remedy of Customer and the sole liability of Xilinx shall be, at the option of Xilinx, to replace or repair the affected products, or to refund to Customer the price of the affected products.

- Page 74 X-ON Electronics Largest Supplier of Electrical and Electronic Components Click to view similar products for manufacturer: Xilinx Other Similar products are found below : XC3SD3400A-4CSG484LI XC6SLX100-3FGG676I XC6SLX45-2CSG324C DK-K7-CONN-G XC7Z030-1FFG676I XC7V2000T- 1FLG1925CES9937 XC6SLX16-3FTG256I XC5VFX30T-1FFG665C XC4VLX40-10FFG668I XC3S50A-4FTG256C XC3S1200E- 4FG400C XC2C256-7PQG208C XC2C256-7TQ144I XC2S200-6PQG208C XC2S30-5TQG144I XC3S4000-4FGG900I XC4VFX20-...

Need help?

Do you have a question about the Virtex-7 FPGA VC7222 and is the answer not in the manual?

Questions and answers