Table of Contents

Advertisement

Quick Links

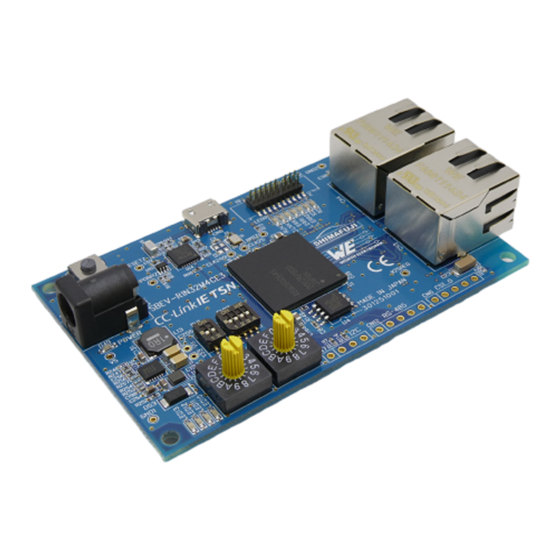

R-IN32M4-CL3

R9A06G064MGBG

R9A06G064SGBG

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Electronics Corp. without notice. Please review the latest information published by

Renesas Electronics Corp. through various means, including the Renesas Electronics Corp.

website (http://www.renesas.com).

Document number: R18UZ0074EJ0100

Issue date: Dec 24, 2019

Renesas Electronics

www.renesas.com

User's Manual: Board design edition

Advertisement

Table of Contents

Summary of Contents for Renesas R-IN32M4-CL3

- Page 1 All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp.

- Page 2 Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user’s manual or other Renesas Electronics document.

- Page 3 Products The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- Page 4 This manual is intended for users who wish to understand the functions of industrial Ethernet communications ASSP (Application Specific Standard Product) “R-IN32M4-CL3” (R9A06G064MGBG, R9A06G064SGBG) and design application systems using it. It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- Page 5 2. Notation of Numbers and Symbols Weight in data notation: Left is high-order column, right is low-order column Active low notation: xxxZ (capital letter Z after pin name or signal name) or xxx_N (capital letter _N after pin name or signal name) or xxnx (pin name or signal name contains small letter n) Note: Explanation of (Note) in the text...

-

Page 6: Table Of Contents

Contents Overview ................................ 1 Definition of Pin Handling and Symbols in This Manual ................... 1 Power/Reset Pins ............................2 Power-On/Off Sequence ............................. 2 2.1.1 Power-On/Off Sequence without 2.5-V built-in Regulator ............... 3 2.1.2 Power-On/Off Sequence with 2.5-V built-in Regulator ................4 Power Supply Pins .............................. - Page 7 2.5-V built-in Regulator Peripheral Circuit Configuration ................21 Peripheral Connection Configuration with 2.5-V built-in Regulator ..............21 Peripheral Connection Configuration without 2.5-V built-in Regulator ............21 Recommended Components of Inductor and Capacitors .................. 22 Recommended Component of Schottky barrier diode ..................22 Example of PCB Layout Image (23 mm Square BGA Package) ..............

- Page 8 10. Serial Flash ROM Connection Pins ......................45 11. Asynchronous Serial Interface J Connection Pins ..................46 12. I C Connection Pins ............................ 47 13. CAN Pins ..............................48 14. CSIH Pins ..............................49 14.1 One Master and One Slave ..........................49 14.2 One Master and Two Slaves ..........................

- Page 9 Figure 2.2 Power Supply Channel to R-IN32M4-CL3 (without 2.5-V built-in Regulator).......... 3 Figure 2.3 Power-On/Off Sequence (with 2.5-V built-in Regulator) ................4 Figure 2.4 Power Supply Channel to R-IN32M4-CL3 (with 2.5-V built-in Regulator) ..........4 Figure 3.1 Example of GND Pattern for the Components for External Constants ............8 Figure 3.2 Configuration Example of the Oscillation Circuit ..................

- Page 10 Figure 18.1 Mount Pad Sizes (23 mm Square BGA Package) ................... 57 Figure 18.2 Mount Pad Sizes (17 mm Square BGA Package) ................... 57 Figure 21.1 R-IN32M4-CL3 Marking Information (23 mm Square BGA Package) ..........60 Figure 21.2 R-IN32M4-CL3 Marking Information (17 mm Square BGA Package) ..........60...

- Page 11 List of Tables Table 1.1 Definition of Pin Handling ........................... 1 Table 2.1 External Power Supply ..........................2 Table 6.1 Example of Recommended Components of Ceramic Capacitors ............... 14 Table 6.2 Example of Recommended Components of Ferrite Beads ................. 14 Table 7.1 Example of Recommended Component of Inductor ..................

-

Page 12: Overview

This manual is intended for being used by engineers that work on a circuit and PCB design that is equipped with an Ethernet communication LSI from the R-IN32M4-CL3 made by Renesas Electronics. The target device is the R-IN32M4-CL3. It is recommended to study this manual carefully and to follow the recommendations during the circuit and board design. -

Page 13: Power/Reset Pins

Power/Reset Pins Power-On/Off Sequence Table 2.1 lists external power supplies to R-IN32M4-CL3. In addition, Figure 2.1 and Figure 2.3 show the power-on/off sequence. There is no particular rule for the power-on sequence. We recommend supplying external power voltage VDD11 first and then supplying external power voltage VDD33. -

Page 14: Power-On/Off Sequence Without 2.5-V Built-In Regulator

Figure 2.1 Power-On/Off Sequence (without 2.5-V built-in Regulator) 3.3 ± 0.165 V 2.5 ± 0.125 V 1.15 ± 0.06 V Gigabit Regulator Ethernet R-IN32M4-CL3 Figure 2.2 Power Supply Channel to R-IN32M4-CL3 (without 2.5-V built-in Regulator) R18UZ0074EJ0100 Page 3 of 61 Dec 24, 2019... -

Page 15: Power-On/Off Sequence With 2.5-V Built-In Regulator

Figure 2.3 Power-On/Off Sequence (with 2.5-V built-in Regulator) 3.3 ± 0.165 V 1.15 ± 0.06 V 2.5 ± 0.125 V Gigabit Regulator Ethernet R-IN32M4-CL3 Figure 2.4 Power Supply Channel to R-IN32M4-CL3 (with 2.5-V built-in Regulator) R18UZ0074EJ0100 Page 4 of 61 Dec 24, 2019... -

Page 16: Power Supply Pins

R-IN32M4-CL3 User's Manual: Board design edition 2. Power/Reset Pins Power Supply Pins This is a list of power supply pins of R-IN32M4-CL3. When designing with these pins, refer to the connection example as follows. Pin Name Function Reference for Connection Example PLL_VDD PLL power supply (1.15 V) -

Page 17: Reset Pins

2. Power/Reset Pins Reset Pins This is a list of reset pins of R-IN32M4-CL3. As a width at low level of at least 1 s is required for the reset input signals, secure this by applying the low level of the reset signal over the oscillation stabilization time of the external oscillator (25 MHz). -

Page 18: Clock Input Pins

R-IN32M4-CL3 User's Manual: Board design edition 3. Clock Input Pins Clock Input Pins Pin Functions This is a list of pin functions of clock input pins. Pin Name Attribute Function Connects an external oscillator. When OSCTH = 0, this pin functions as an output pin. -

Page 19: Notes On Configuring The Oscillation Circuit

Make the ground connections of the capacitors to the GND pins of R-IN32M4-CL3 as short and thick as possible. Make the lead wires between the resonator and capacitors as short as possible. -

Page 20: Configuration Example Of Oscillation Circuits

Figure 3.2 Configuration Example of the Oscillation Circuit Caution: The input of the R-IN32M4-CL3 is fixed to 25 MHz. When a resonator is to be used, contact the resonator manufacturer and ask for a corresponding part number and external constants. -

Page 21: Pll Power Supply Pins

Reference ferrite beads: TDK MPZ2012S601A, MPZ1608S601A Figure 4.1 Recommended Configuration of Filter Caution: Place C1 immediately close to R-IN32M4-CL3. If C2 is not placed immediately close to R-IN32M4-CL3, this will not cause any problems. R18UZ0074EJ0100 Page 10 of 61 Dec 24, 2019... -

Page 22: Notes On Placement Of Peripheral Components

4. PLL Power Supply Pins Notes on Placement of Peripheral Components The 0.1-F ceramic capacitor (C1) should be placed immediately close to R-IN32M4-CL3 (in the immediate vicinity of the pin). Figure 4.2 is a schematic view from below the board. -

Page 23: Gpio Port Pins

5. GPIO Port Pins GPIO Port Pins GPIO is a general-purpose I/O port. As for the internal configuration, see the section in the following document. Section 27 “Port Functions” in the “R-IN32M4-CL3 User’s Manual: Hardware edition” R18UZ0074EJ0100 Page 12 of 61... -

Page 24: Gigabit Ethernet Phy Pins

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins Gigabit Ethernet PHY Pins Since the Gigabit Ethernet PHY interface handles high-speed transfer, designing the board pattern for it and other components requires full consideration on numerous points. Design it in accord with the advice in this section. -

Page 25: Recommended Components

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins 6.1.2 Recommended Components Ceramic capacitors We recommend using components that satisfy the following conditions. Capacitors: 47 F, 10 F, and 0.1 F Thermal characteristic: X5R or X7R ESR: No more than 0.1 Ω (from 100 kHz to 100 MHz) Table 6.1 Example of Recommended Components of Ceramic Capacitors... -

Page 26: Peripheral Circuit Of Pulse Transformer

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins Peripheral Circuit of Pulse Transformer An example of the circuit configuration for the Gigabit Ethernet PHY, pulse transformers, and RJ-45 connector, and recommended pulse transformer products are shown below. -

Page 27: Recommended Components

We recommend using pulse transformer that satisfy the following conditions. We also recommend the constitution illustrated in Transformer of Figure 6.3. Common-mode chokes are not required on the R-IN32M4-CL3 (PHY side) and is mounted on the connector. Winding ratio: 1:1 (2% or less, or 3%) recommended Return loss (see Figure 6.4): -18dB or less (from 1.0 MHz to 40 MHz) -

Page 28: Ref_Rext And Ref_Filt Pins

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins REF_REXT and REF_FILT Pins The method of handling the REF_REXT and REF_FILT pins and recommended values for the connected components are shown below. 6.3.1 Example of Circuit Configuration Place the wiring separately from that for other high-frequency signals, but place the components close to the pins. -

Page 29: Notes On Board Wiring

Bends in lines should be at angles of at least 135 degrees. (Figure 6.7) Differential signal traces between the R-IN32M4-CL3, pulse transformer, and RJ-45 connector should be designed with a differential impedance of 100 10% and with an impedance of 50 relating to GND. -

Page 30: Figure 6.7 Example Of Wiring For Differential Signals (2)

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins Figure 6.7 Example of Wiring for Differential Signals (2) Figure 6.8 Example of Wiring for Differential Signals (3) R18UZ0074EJ0100 Page 19 of 61 Dec 24, 2019... -

Page 31: Unused Gbe-Phy

R-IN32M4-CL3 User's Manual: Board design edition 6. Gigabit Ethernet PHY Pins void void Figure 6.9 Example of Wiring for Differential Signals (4) Unused GbE-PHY Comply with the following requirements even when GbE-PHY is not in use. Always power supply to the VDD25A and VDD11A pins. -

Page 32: 5-V Built-In Regulator Peripheral Circuit Configuration

7. 2.5-V built-in Regulator Peripheral Circuit Configuration 2.5-V built-in Regulator Peripheral Circuit Configuration This section describes the peripheral circuit configuration of the 2.5-V built-in regulator installed in R-IN32M4-CL3. Peripheral Connection Configuration with 2.5-V built-in Regulator This figure shows a peripheral connection configuration with the 2.5-V built-in regulator. -

Page 33: Recommended Components Of Inductor And Capacitors

R-IN32M4-CL3 User's Manual: Board design edition 7. 2.5-V built-in Regulator Peripheral Circuit Configuration Recommended Components of Inductor and Capacitors The inductor and ceramic capacitors recommended for L and C , and C are shown. BYPASS Inductor (L) Inductance: 4.7 μH ± 30% ... -

Page 34: Example Of Pcb Layout Image (23 Mm Square Bga Package)

7. 2.5-V built-in Regulator Peripheral Circuit Configuration Example of PCB Layout Image (23 mm Square BGA Package) This section describes the peripheral circuit configuration of the 2.5-V built-in regulator installed in the R-IN32M4-CL3 in a 23 mm square BGA package. -

Page 35: Example Of Pcb Layout Image (17 Mm Square Bga Package)

7. 2.5-V built-in Regulator Peripheral Circuit Configuration Example of PCB Layout Image (17 mm Square BGA Package) This section describes the peripheral circuit configuration of the 2.5-V built-in regulator installed in the R-IN32M4-CL3 in a 17 mm square BGA package. -

Page 36: Requirements For Parasitic Resistances And Parasitic Inductances In Pcb

R-IN32M4-CL3 User's Manual: Board design edition 7. 2.5-V built-in Regulator Peripheral Circuit Configuration Requirements for Parasitic Resistances and Parasitic Inductances in PCB In this PCB layout, draw patterns so that the parasitic resistances and the parasitic inductances satisfy the followings. -

Page 37: Thermal Design

Deciding on whether Particular Measures for Heat Dissipation are Required 8.1.1 Estimating Tj Take Tj ≤ 125°C as the criterion for Tj of the R-IN32M4-CL3. Estimate Tj from the following formulae. Tj = Tt + Ψjt x power or Tj = Ta + θja x power Junction temperature [°C] Package surface temperature [°C]... -

Page 38: Examples Of Measures For Heat Dissipation

R-IN32M4-CL3 User's Manual: Board design edition 8. Thermal Design Examples of Measures for Heat Dissipation We classify measures for heat dissipation into two types. For details, see the following pages. (1) Measures for heat release in designing the board Take these types of measures into consideration when designing the board. -

Page 39: Measures For Heat Release In Designing The Board

R-IN32M4-CL3 User's Manual: Board design edition 8. Thermal Design 8.2.1 Measures for Heat Release in Designing the Board Thermal Vias Placing as many vias to the power supply and GND areas as possible below the center of the package increases the number of paths for the flow of heat in the z direction. - Page 40 R-IN32M4-CL3 User's Manual: Board design edition 8. Thermal Design Residual Copper Ratio of Cu Layers Increasing the residual copper ratio in all layers of the board layers increases the breadth of the paths for heat transfer. Cu Thickness Designing all Cu layers of the board to be thick increases the volume of paths for heat dissipation. Since thinner Cu layers reduce the effectiveness of heat dissipation, care is required on this point.

-

Page 41: Heat Dissipation From The Periphery (Including The Casing)

R-IN32M4-CL3 User's Manual: Board design edition 8. Thermal Design 8.2.2 Heat Dissipation from the Periphery (Including the Casing) Incorporating a Heat Sink Incorporating a heat sink increases the area for heat dissipation, making heat dissipation from the surface of the device more efficient. -

Page 42: Caution

R-IN32M4-CL3 User's Manual: Board design edition 8. Thermal Design Caution 8.3.1 Handling of Unused Pins If an unused pin is clamped to the GND or a power supply on the board, the corresponding pin must have the input attribute as a fixed setting. If it is set as an output, and the level at the point to which it is clamped is opposite that of the pin, a large steady-state current will continuously flow through the output buffer. -

Page 43: External Mcu/Memory Interface Pins

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins External MCU/Memory Interface Pins This LSI is able to connect an external MCU or memory. The connection mode is decided by the signal level of the MEMIFSEL, MEMCSEL, HIFSYNC, and ADMUXMODE pins as shown in Table 9.1. -

Page 44: External Mcu Interface

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins External MCU Interface The external MCU interface is multiplexed with the external memory interface. When the MEMIFSEL pin is set to the high level, it functions as the external MCU interface. -

Page 45: Asynchronous-Sram Supporting Mcu Connection Mode

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.1.1 Asynchronous-SRAM Supporting MCU Connection Mode The following figure shows a general connection example in asynchronous-SRAM supporting MCU interface mode, when this LSI chip is connected as a slave device to an external MCU. -

Page 46: Synchronous-Sram Supporting Mcu Connection Mode

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.1.2 Synchronous-SRAM Supporting MCU Connection Mode The following figure shows a general connection example in synchronous-SRAM supporting MCU interface mode, when this LSI chip is connected as a slave device to an external MCU. -

Page 47: Synchronous-Burst-Transfer Supporting Mcu Connection Mode

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.1.3 Synchronous-Burst-Transfer Supporting MCU Connection Mode The following figure shows a general connection example in synchronous-burst-transfer supporting MCU connection mode, when this LSI chip is connected as a slave device to an external MCU. - Page 48 R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins Notes 1. In this mode, drive the HWRZSEL pin low. 2. Connecting the HERROUTZ signal is not indispensable. Connect it to an interrupt or general-purpose port input of the MCU to be connected, if required.

-

Page 49: Figure 9.7 Connection Example Of 32-Bit External Mcu Interface

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.1.3.2 Address/Data Separated Mode (ADMUXMODE = L) R-IN32M4-CL3 External MCU HBUSCLK BUSCLK Note3 Note4 HA1-HA19 A2-A20 HD0-HD31 D0-D31 HCSZ PGCSZ HPGCSZ BCYSTZ / ADV HBCYSTZ HRDZ HWRSTBZ WRSTBZ HWRZ0 / HBENZ0... -

Page 50: External Memory Interface

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins External Memory Interface This section describes the connection as a master device to an external memory. The operating connection mode of the external memory interface depends on the level of the signal on the MEMCSEL pin (see Table 9.1, Mode Selection of External MCU/Memory Connection). -

Page 51: Figure 9.9 Connection Example With 32-Bit Sram (Asynchronous Sram Memc)

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.2.1.1 Connection Example with SRAM The following figure shows an example when this LSI chip is connected to SRAM. R-IN32M4-CL3 A2-A19 A0-A17 D16-D31 I/O1-I/O16 CSZn SRAM (256 Kwords × 16 bits) -

Page 52: Figure 9.11 Connection Example With 32-Bit Paged Rom (Asynchronous Sram Memc)

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.2.1.2 Connection Example with Paged ROM The following figure shows an example when this LSI chip is connected to paged ROM. R-IN32M4-CL3 A2-A21 A0-A19 D16-D31 O0-O15 Paged ROM CSZ0 (1 Mword ×... -

Page 53: Synchronous Burst Access Memc

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.2.2 Synchronous Burst Access MEMC The synchronous burst access MEMC is externally connectable to paged ROM, ROM, SRAM, PSRAM, NOR-flash memory, or peripheral devices with an interface similar to the SRAM interface via a 16- or 32-bit bus. -

Page 54: Figure 9.13 Connection Example With 32-Bit Sram (Synchronous Burst Access Memc)

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.2.2.1 Connection Example with SRAM The following figure shows an example when this LSI chip is connected to SRAM. R-IN32M4-CL3 BUSCLK BUSCLK Note Note A2-A19 A0-A17 D16-D31 I/O1-I/O16 SRAM CSZn (256 Kwords ×... -

Page 55: Figure 9.15 Connection Example With 32-Bit Paged Rom (Synchronous Burst Access Memc)

R-IN32M4-CL3 User's Manual: Board design edition 9. External MCU/Memory Interface Pins 9.2.2.2 Connection Example with Paged ROM The following figure shows an example when this LSI chip is connected to paged ROM. R-IN32M4-CL3 BUSCLK BUSCLK Note Note A2-A21 A0-A19 D16-D31... -

Page 56: Serial Flash Rom Connection Pins

R-IN32M4-CL3 User's Manual: Board design edition 10. Serial Flash ROM Connection Pins Serial Flash ROM Connection Pins This LSI chip has a memory controller to connect the serial flash ROM that supports the SPI compatible interface. R-IN32M4-CL3 SMCSZ (P17) /S (/CS) -

Page 57: Asynchronous Serial Interface J Connection Pins

R-IN32M4-CL3 User's Manual: Board design edition 11. Asynchronous Serial Interface J Connection Pins Asynchronous Serial Interface J Connection Pins The following figure shows a connection example between the R-IN32M4-CL3 and the asynchronous serial interface J (UARTJ) device. R-IN32M4-CL3 UART device... -

Page 58: I 2 C Connection Pins

12. I2C Connection Pins C Connection Pins Figure 12.1 shows a connection example between the R-IN32M4-CL3 and the I C slave device. Since the serial clock line and serial data line are N-channel open drain outputs, an external pull-up resistor is required. -

Page 59: Can Pins

R-IN32M4-CL3 User's Manual: Board design edition 13. CAN Pins CAN Pins The following figure shows a connection example between the R-IN32M4-CL3 and the CAN transceiver. The CAN transceiver is used to connect the CAN bus. CAN bus R-IN32M4-CL3 CAN transceiver... -

Page 60: Csih Pins

The following figure illustrates the connections between an R-IN32M4-CL3 as a master and two slaves. In this example, the R-IN32M4-CL3 supplies one chip select (CS) signal to each of the slaves. This signal is connected to the slave select input (SSI) of the slave. -

Page 61: Jtag/Trace Pins

R-IN32M4-CL3 User's Manual: Board design edition 15. JTAG/Trace Pins JTAG/Trace Pins The following figures show examples when this LSI chip is connected to the ICE (in-circuit emulator). As long as nRESET is input to RESETZ, nRESET is not required to input to HOTRESETZ. -

Page 62: Figure 15.2 Connection Example Of Jtag Interface (20-Pin Half-Pitch With Trace)

R-IN32M4-CL3 User's Manual: Board design edition 15. JTAG/Trace Pins VDD33 (3.3 V) Reset circuit About 4.7 kΩ to R-IN32M4-CL3 ICE connecter (20-pin half-pitch) 10 kΩ RESETZ nRESET HOTRESETZ Wired OR connection with open drain TRSTZ Not connected TRACECLK TRACECLK TRACEDATA0... -

Page 63: Figure 15.3 Connection Example Of Swd Interface (20-Pin Half-Pitch Without Trace)

R-IN32M4-CL3 User's Manual: Board design edition 15. JTAG/Trace Pins VDD33 (3.3 V) Reset About 4.7 kΩ to circuit R-IN32M4-CL3 ICE connecter (20-pin half-pitch) 10 kΩ RESETZ nRESET HOTRESETZ Wired OR connection with open drain TRSTZ Not connected TCK (SWCLK) TCK (SWCLK) -

Page 64: Figure 15.4 Connection Example Of Jtag Interface (20-Pin Full-Pitch)

R-IN32M4-CL3 User's Manual: Board design edition 15. JTAG/Trace Pins VDD33 (3.3 V) Reset About 4.7 kΩ to circuit R-IN32M4-CL3 ICE connecter (20-pin full-pitch) 10 kΩ RESETZ nSRST HOTRESETZ Wired OR connection with open drain TRSTZ nTRST JTAGSEL Figure 15.4 Connection Example of JTAG Interface (20-Pin Full-Pitch) -

Page 65: Implementation Conditions

R-IN32M4-CL3 User's Manual: Board design edition 16. Implementation Conditions Implementation Conditions The following figures show implementation conditions of the R-IN32M4-CL3. Open the aluminum dry pack Storage period is Baking within 7 days* (125°C, 24 to 72h) *Storage conditions: 5 to 30°C temperature,... -

Page 66: Package Information

R-IN32M4-CL3 User's Manual: Board design edition 17. Package Information Package Information The following figures show the package information of R-IN32M4-CL3. Figure 17.1 Package Information (23 mm Square BGA Package) R18UZ0074EJ0100 Page 55 of 61 Dec 24, 2019... -

Page 67: Figure 17.2 Package Information (17 Mm Square Bga Package)

R-IN32M4-CL3 User's Manual: Board design edition 17. Package Information Figure 17.2 Package Information (17 mm Square BGA Package) R18UZ0074EJ0100 Page 56 of 61 Dec 24, 2019... -

Page 68: Mount Pad Information

R-IN32M4-CL3 User's Manual: Board design edition 18. Mount Pad Information Mount Pad Information The following figures show the mount pad information of the R-IN32M4-CL3. 0.50 to 0.70 1.00 mm 0.43 to 0.53 mm 1.00 mm 0.43 to 0.53 mm Figure 18.1 Mount Pad Sizes (23 mm Square BGA Package) 0.45 to 0.55 mm... -

Page 69: Bscan Information

XT1, XT2, PONRZ, JTAGSEL, CTRSTBYB, TMODE0–TMODE2, TMS, TDI, TDO, TRSTZ, TCK, P[0:1]_D[3:0]P/N, REF_FILT, REF_REXT, TANA_[1:0], REG_FB, REG_OUT 19.5 How to Get BSDL With regard to obtain the BSDL file, please contact a Renesas Sales Representative or Distributor in your area. R18UZ0074EJ0100 Page 58 of 61 Dec 24, 2019... -

Page 70: Ibis Information

R-IN32M4-CL3 User's Manual: Board design edition 20. IBIS Information IBIS Information For IBIS information, please contact a Renesas Sales Representative or Distributor in your area. R18UZ0074EJ0100 Page 59 of 61 Dec 24, 2019... -

Page 71: Marking Information

R-IN32M4-CL3 User's Manual: Board design edition 21. Marking Information Marking Information The following figures show the marking information of R-IN32M4-CL3. Figure 21.1 R-IN32M4-CL3 Marking Information (23 mm Square BGA Package) Figure 21.2 R-IN32M4-CL3 Marking Information (17 mm Square BGA Package) R18UZ0074EJ0100 Page 60 of 61... -

Page 72: Countermeasure For Noise

22.1 Stopping Clock Output If the BUSCLK pin is not in use, output on the pin from the R-IN32M4-CL3 can be stopped. See Section 4.2.2 “Clock Control Registers (CLKGTD0, CLKGTD1, CLKGTD2)” in the “R-IN32M4-CL3 User’s Manual: Hardware edition” regarding control of the GCBCLK bit in the CLKGTD1 register, which enables or disables output from the BUSCLK pin. - Page 73 R-IN32M4-CL3 User’s Manual: Board design edition REVISION HISTORY REVISION HISTORY R-IN32M4-CL3 User’s Manual: Board design edition Description Rev. Date Page Summary — 1.00 Dec 24, 2019 First edition issued...

- Page 74 R-IN32M4-CL3 User’s Manual: Board design edition REVISION HISTORY [MEMO]...

- Page 75 R-IN32M4-CL3 User’s Manual: Board design edition Publication Date: Rev.1.00 Dec 24, 2019 Published by: Renesas Electronics Corporation...

- Page 76 R-IN32M4-CL3 User’s Manual: Board design edition R18UZ0074EJ0100...

Need help?

Do you have a question about the R-IN32M4-CL3 and is the answer not in the manual?

Questions and answers