Table of Contents

Advertisement

Quick Links

FEATURES

Low power: 1.0 W @ 1 GSPS, 600 mW @ 500 MSPS,

full operating conditions

Single carrier W-CDMA ACLR = 7 dBc @ 80 MHz IF

Analog output: adjustable 8.7 mA to 31.7 mA,

R

= 25 Ω to 50 Ω

L

Novel 2×, 4×, and 8× interpolator/coarse complex modulator

allows carrier placement anywhere in DAC bandwidth

Auxiliary DACs allow control of external VGA and offset control

Multiple chip synchronization interface

High performance, low noise PLL clock multiplier

Digital inverse sinc filter

100-lead, exposed paddle TQFP

APPLICATIONS

Wireless infrastructure

W-CDMA, CDMA2000, TD-SCDMA, WiMax, GSM

Digital high or low IF synthesis

Internal digital upconversion capability

Transmit diversity

Wideband communications: LMDS/MMDS, point-to-point

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Downloaded from

Elcodis.com

electronic components distributor

TYPICAL SIGNAL CHAIN

COMPLEX I AND Q

DC

DIGITAL INTERPOLATION FILTERS

FPGA/ASIC/DSP

AD9776A/AD9778A/AD9779A

Dual 12-/14-/16-Bit,1 GSPS,

Digital-to-Analog Converters

AD9776A/AD9778A/AD9779A

GENERAL DESCRIPTION

The AD9776A/AD9778A/AD9779A are dual, 12-/14-/16-bit,

high dynamic range, digital-to-analog converters (DACs) that

provide a sample rate of 1 GSPS, permitting a multicarrier

generation up to the Nyquist frequency. They include features

optimized for direct conversion transmit applications, including

complex digital modulation, and gain and offset compensation.

The DAC outputs are optimized to interface seamlessly with

analog quadrature modulators such as the ADL537x FMOD

series from Analog Devices, Inc. A serial peripheral interface

(SPI) provides for programming/readback of many internal

parameters. Full-scale output current can be programmed over

a range of 10 mA to 30 mA. The devices are manufactured on

an advanced 0.18 μm CMOS process and operate on 1.8 V and

3.3 V supplies for a total power consumption of 1.0 W. They are

enclosed in a 100-lead TQFP.

PRODUCT HIGHLIGHTS

1.

Ultralow noise and intermodulation distortion (IMD)

enable high quality synthesis of wideband signals from

baseband to high intermediate frequencies.

2.

A proprietary DAC output switching technique enhances

dynamic performance.

3.

The current outputs are easily configured for various

single-ended or differential circuit topologies.

4.

CMOS data input interface with adjustable setup and hold.

5.

Novel 2×, 4×, and 8× interpolator/coarse complex

modulator allows carrier placement anywhere in DAC

bandwidth.

QUADRATURE

MODULATOR/

MIXER/

AMPLIFIER

DC

I DAC

ANALOG FILTER

Q DAC

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113

LO

POST DAC

A

www.analog.com

©2007–2008 Analog Devices, Inc. All rights reserved.

Advertisement

Table of Contents

Summary of Contents for Analog Devices AD9776A

-

Page 1: Features

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. -

Page 2: Table Of Contents

Theory of Operation ..............23 Synchronization Logic Overview ..........45 Differences Between AD9776/AD9778/ AD9779 and Synchronizing Devices to a System Clock ......46 AD9776A/AD9778A/AD9779A..........23 Interrupt Request Operation ............ 46 Serial Peripheral Interface ............. 24 ... -

Page 3: Functional Block Diagram

AD9776A/AD9778A/AD9779A FUNCTIONAL BLOCK DIAGRAM DELAY SYNC_O LINE SYNC_I CLOCK GENERATION/DISTRIBUTION CLOCK REFCLK+ DELAY MULTIPLIER DATACLK LINE 2×/4×/8× REFCLK– DATA ASSEMBLER SYNC OUT1_P 16-BIT I DAC OUT1_N P1D<15:0> LATCH 2× 2× 2× n × n = 0, 1, 2 ... 7... -

Page 4: Specifications

AD9776A/AD9778A/AD9779A SPECIFICATIONS DC SPECIFICATIONS to T , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, I = 20 mA, maximum sample rate, unless OUTFs otherwise noted. Table 1. AD9776A AD9778A AD9779A Parameter... -

Page 5: Digital Specifications

AD9776A/AD9778A/AD9779A DIGITAL SPECIFICATIONS to T , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V, I = 20 mA, maximum sample rate, unless OUTFs otherwise noted. LVDS driver and receiver are compliant to the IEEE-1596 reduced range link, unless otherwise noted. -

Page 6: Digital Input Data Timing Specifications

AD9776A/AD9778A/AD9779A DIGITAL INPUT DATA TIMING SPECIFICATIONS All modes, −40°C to +85°C. Table 3. Parameter Conditions Unit Input Data Setup Time Input data to DATACLK Hold Time Input data to DATACLK Setup Time Input data to REFCLK −0.8 Hold Time Input data to REFCLK Latency 1×... -

Page 7: Absolute Maximum Ratings

AD9776A/AD9778A/AD9779A ABSOLUTE MAXIMUM RATINGS Table 5. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress Parameter With Respect To Rating rating only; functional operation of the device at these or any... -

Page 8: Pin Configurations And Function Descriptions

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 NC = NO CONNECT Figure 3. AD9776A Pin Configuration Table 7. AD9776A Pin Function Descriptions Mnemonic Description... -

Page 9: Changes To Pin 39 Description, Table 7

AD9776A/AD9778A/AD9779A Mnemonic Description Mnemonic Description TXENABLE AGND Analog Ground. Transmit Enable. In single port mode, this pin also functions as IQSELECT. IPTAT Factory Test Pin. Output current is P2D<11> Port 2, Data Input D11 (MSB). proportional to absolute temperature, approximately 14 μA at 25°C with P2D<10>... -

Page 10: Changes To Pin 39 Description, Table 8

AD9776A/AD9778A/AD9779A 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 CVDD18 I120 PIN 1 CVDD18 VREF CGND IPTAT ANALOG DOMAIN CGND AGND REFCLK+ REFCLK–... - Page 11 AD9776A/AD9778A/AD9779A Mnemonic Description Mnemonic Description P2D<11> Port 2, Data Input D11. IPTAT Factory Test Pin. Output current is proportional to absolute temperature, DVDD18 1.8 V Digital Supply. approximately 14 μA at 25°C with DGND Digital Ground. approximately 20 nA/°C slope. This pin P2D<10>...

-

Page 12: Changes To Pin 39 Description, Table 9

AD9776A/AD9778A/AD9779A 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 CVDD18 I120 PIN 1 CVDD18 VREF CGND IPTAT ANALOG DOMAIN CGND AGND REFCLK+ REFCLK–... - Page 13 AD9776A/AD9778A/AD9779A Mnemonic Description Mnemonic Description P2D<13> Port 2, Data Input D13. IPTAT Factory Test Pin. Output current is proportional to absolute temperature, DVDD18 1.8 V Digital Supply. approximately 14 μA at 25°C with DGND Digital Ground. approximately 20 nA/°C slope. This pin P2D<12>...

-

Page 14: Typical Performance Characteristics

AD9776A/AD9778A/AD9779A TYPICAL PERFORMANCE CHARACTERISTICS = 160MSPS DATA = 200MSPS DATA –1 –2 = 250MSPS DATA –3 –4 –5 –6 CODE (MHz) Figure 9. AD9779A In-Band SFDR vs. f Figure 6. AD9779A Typical INL 2× Interpolation = 100MSPS = 200MSPS DATA... - Page 15 AD9776A/AD9778A/AD9779A PLL OFF = 160MSPS DATA PLL ON = 200MSPS DATA = 250MSPS DATA (MHz) (MHz) Figure 12. AD9779A Out-of-Band SFDR vs. f Figure 15. AD9779A In-Band SFDR, 4× Interpolation, 2× Interpolation = 100 MSPS, PLL On/Off DATA 0dBFS –3dBFS –6dBFS...

- Page 16 AD9776A/AD9778A/AD9779A = 160MSPS DATA = 200MSPS DATA = 250MSPS DATA = 75MSPS DATA = 100MSPS DATA = 50MSPS DATA = 125MSPS DATA (MHz) (MHz) Figure 18. AD9779A Third-Order IMD vs. f Figure 21. AD9779A Third-Order IMD vs. f 1× Interpolation 8×...

- Page 17 AD9776A/AD9778A/AD9779A REF 0dBm *ATTEN 20dB *PEAK 10dB EXT REF DC-COUPLED 0dBFS –3dBFS –6dBFS LGAV £(f): FTUN START 1.0MHz STOP 400.0MHz VBW 20kHz (MHz) *RES BW 20kHz SWEEP 1.203s (601 pts) Figure 24. AD9779A IMD Performance vs. Digital Full-Scale Input over Figure 27.

- Page 18 AD9776A/AD9778A/AD9779A –150 –55 –60 –154 –65 0dBFS, PLL ENABLED = 200MSPS –158 –70 = 400MSPS –6dBFS, PLL DISABLED –75 –162 = 800MSPS –80 –166 –85 0dBFS, PLL DISABLED –3dBFS, PLL DISABLED –170 –90 (MHz) (MHz) Figure 30. AD9779A Noise Spectral Density vs. f over Output Frequency Figure 33.

- Page 19 AD9776A/AD9778A/AD9779A = 200MSPS DATA = 160MSPS DATA = 250MSPS DATA –0.5 –1.0 –1.5 (MHz) CODE Figure 36. AD9778A Typical INL Figure 39. AD9778A In-Band SFDR vs. f , 2× Interpolation –60 –70 1ST ADJ CHAN –0.2 3RD ADJ CHAN –0.4 –80...

- Page 20 –0.2 –0.3 –0.4 1024 1536 2048 2560 3072 3584 4096 (MHz) CODE Figure 44. AD9776A Typical INL Figure 47. AD9776A In-Band SFDR vs. f , 2× Interpolation Rev. A | Page 20 of 60 Downloaded from Elcodis.com electronic components distributor...

- Page 21 –85 –90 –170 (MHz) (MHz) Figure 48. AD9776A ACLR, f = 122.88 MSPS, 4× Interpolation, Figure 50. AD9776A Noise Spectral Density vs. f , Eight-Tone Input DATA /4 Modulation with 500 kHz Spacing, f = 200 MSPS DATA REF –25.29dBm...

-

Page 22: Terminology

AD9776A/AD9778A/AD9779A TERMINOLOGY Integral Nonlinearity (INL) In-Band Spurious Free Dynamic Range (SFDR) INL is defined as the maximum deviation of the actual analog In-band SFDR is the difference, in decibels, between the peak output from the ideal output, determined by a straight line amplitude of the output signal and the peak spurious signal drawn from zero scale to full scale. -

Page 23: Theory Of Operation

The optimal settings for the AD9776/AD9778/AD9779 differ carriers to be synthesized than in previously available DACs. from the AD9776A/AD9778A/AD9779A. Refer to the PLL Bias The digital engine uses an innovative filter architecture that Settings section for complete details. -

Page 24: Serial Peripheral Interface

There are two phases to a communication cycle with the address. The remaining register addresses are generated by the AD9776A/AD9778A/AD9779A. Phase 1 is the instruction cycle device based on the LSB First bit (Register 0x00, Bit 6). (the writing of an instruction byte into the device), coinciding with the first eight SCLK rising edges. -

Page 25: Serial Interface Port Pin Descriptions

AD9776A/AD9778A/AD9779A SERIAL INTERFACE PORT PIN DESCRIPTIONS The serial port controller data address decrements from the data address written toward 0x00 for multibyte I/O operations if the Serial Clock (SCLK) MSB first mode is active. The serial port controller address incre-... -

Page 26: Spi Register Map

AD9776A/AD9778A/AD9779A SPI REGISTER MAP Note that all unused register bits should be kept at the device default values. Table 13. Address Register Decimal Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Def. -

Page 27: Changes To Table 14

AD9776A/AD9778A/AD9779A Table 14. SPI Register Description Register Register Name Address Bits Parameter Function Default Comm 0x00 SDIO Bidirectional 0: use SDIO pin as input data only 1: use SDIO as both input and output data 0x00 LSB/MSB First 0: first bit of serial data is MSB of data byte... - Page 28 AD9776A/AD9778A/AD9779A Register Register Name Address Bits Parameter Function Default Sync Control 0x03 DATACLK Delay Mode 0: manual data timing error correct mode 1: automatic data timing error correct mode 0x03 Reserved Should always be set to 1. 0x03 DATACLK Divide<1:0>...

- Page 29 AD9776A/AD9778A/AD9779A Register Register Name Address Bits Parameter Function Default PLL Control 0x08 PLL Band Select<5:0> This sets the operating frequency range of the 111001 VCO. For details, see Table 21. 0x08 PLL VCO Drive<1:0> Controls the signal strength of the VCO output. Set to 11 for optimal performance.

- Page 30 AD9776A/AD9778A/AD9779A Register Register Name Address Bits Parameter Function Default AUX DAC2 Control 0x12 Auxiliary DAC2 Data<9:8> AUX DAC2 10-bit output current control word. Magnitude of the AUX DAC current increases with 0x11 Auxiliary DAC2 Data<7:0> 00000000 increasing value. Bit 9 is the MSB and Bit 0 is the LSB.

-

Page 31: Interpolation Filter Architecture

AD9776A/AD9778A/AD9779A INTERPOLATION FILTER ARCHITECTURE The AD9776A/AD9778A/AD9779A can provide up to 8× inter- Table 16. Low-Pass Filter 2 polation, or the interpolation filters can be entirely disabled. It Lower Coefficient Upper Coefficient Integer Value is important to note that the input signal should be backed off... - Page 32 AD9776A/AD9778A/AD9779A –10 –10 –20 –20 –30 –30 –40 –40 –50 –50 –60 –60 –70 –70 –80 –80 –90 –90 –100 –100 –4 –3 –2 –1 –4 –3 –2 –1 (× Input Data Rate) (× Input Data Rate) Figure 58. 4× Interpolation, Low-Pass Response to ±4× Input Data Rate Figure 61.

-

Page 33: Changes To Interpolation Filter Architecture Section

–70 the DAC Nyquist bandwidth. –80 The AD9776A/AD9778A/AD9779A are dual DACs with –90 internal complex modulators built into the interpolating filter –100 response. In dual channel mode, the devices expect the real and –4... - Page 34 AD9776A/AD9778A/AD9779A Table 19. Interpolation Filter Modes, (Register 0x01, Bits<5:2>) Frequency Normalized to f Interpolation Nyquist Zone Factor<7:6> Filter Mode<5:2> Modulation Pass Band Center High Comments 0x00 −0.05 +0.05 In 8× interpolation; BW (min) = 0.0375 × f 0x01 DC shifted +0.0125...

-

Page 35: Interpolation Filter Bandwidth Limits

AD9776A/AD9778A/AD9779A INTERPOLATION FILTER BANDWIDTH LIMITS The AD9776A/AD9778A/AD9779A use a novel interpolation filter architecture that allows DAC IF frequencies to be gener- –10 ated anywhere in the spectrum. Figure 68 shows the traditional –20 choice of DAC IF output bandwidth placement. Note that there –30... -

Page 36: Sourcing The Dac Sample Clock

AD9776A/AD9778A/AD9779A SOURCING THE DAC SAMPLE CLOCK × × The AD9776A/AD9778A/AD9779A offer two modes of sourcing REFCLK the DAC sample clock (DACCLK). The first mode employs an The DAC sample clock frequency, f , is equal to DACCLK on-chip clock multiplier that accepts a reference clock operating ×... - Page 37 AD9776A/AD9778A/AD9779A Table 21. Typical VCO Frequency Range vs. PLL Band Select Value PLL Lock Ranges over Temperature, −40°C to +85°C PLL Lock Ranges over Temperature, −40°C to +85°C VCO Frequency Range in MHz VCO Frequency Range in MHz PLL Band Select...

-

Page 38: Driving The Refclk Input

CVDD18 system, there may be a screened device option that can satisfy 1kΩ the system requirements. Analog Devices offers a pair of screened devices that are guaranteed to maintain PLL lock over the entire 0.1µF 287Ω... -

Page 39: Full-Scale Current Generation

AD9776A/AD9778A/AD9779A FULL-SCALE CURRENT GENERATION INTERNAL REFERENCE AD9776A/AD9778A/AD9779A I DAC GAIN Full-scale current on the I DAC and Q DAC can be set from I DAC 1.2V BAND GAP 8.66 mA to 31.66 mA. Initially, the 1.2 V band gap reference is... -

Page 40: Transmit Path Gain And Offset Correction

Figure 78 can be removed. A low-pass or band-pass passive filter is recommended when spurious signals Two auxiliary DACs are provided on the AD9776A/AD9778A/ from the DAC (distortion and DAC images) at the quadrature AD9779A. The full-scale output current on these DACs is derived modulator inputs can affect the system performance. -

Page 41: Lo Feedthrough Compensation

–10 to one or the other of the quadrature modulator signal inputs. –20 This can be seen in the schematics for the AD9776A/AD9778A/ –30 AD9779A evaluation board (see Figure 106). –40 To achieve LO feedthrough compensation, the user should start –50... -

Page 42: Input Data Ports

TXENABLE input is used to power down the digital data path. The simplest method of interfacing to the AD9776A/AD9778A/ AD9779A is when the input data is referenced to the DATACLK In dual port mode, the data must be delivered at the input data output. -

Page 43: Input Data Referenced To Refclk

AD9776A/AD9778A/AD9779A The DATACLKDIV only affects the DATACLK output frequency SYNC_I and not the frequency of the data sampling clock. To maintain an f frequency that samples the input data that remains H_SYNC DATACLK consistent with the expected data rate, DATACLKDIV should... -

Page 44: Optimizing The Data Input Timing

Figure 87 shows a timing diagram of the data interface and the status of the Data Timing The AD9776A/AD9778A/AD9779A have on-chip circuitry that Error Type bit. enables the user to optimize the input data timing by adjusting... -

Page 45: Device Synchronization

AD9776A/AD9778A/AD9779A DEVICE SYNCHRONIZATION System demands can impose two different requirements for pulse generation circuit on a multiple of 32 DACCLK periods. synchronization. Some systems require multiple DACs to be In any case, the maximum frequency of SYNC_I must be less synchronized to each other. -

Page 46: Synchronizing Devices To A System Clock

Figure 90 shows the timing of the SYNC_I input with respect to the REFCLK input. Note that although the timing is relative to The AD9776A/AD9778A/AD9779A offer a pulse mode synchro- the REFCLK signal, SYNC_I is sampled at the DACCLK rate. -

Page 47: Power Dissipation

AD9776A/AD9778A/AD9779A POWER DISSIPATION Figure 91 to Figure 99 show the power dissipation of the 1.8 V mode is 102 mW/31 mA. In dual DAC mode, this is 182 mW/ and 3.3 V digital and clock supplies in single DAC and dual DAC 55 mA. -

Page 48: Power-Down And Sleep Modes

AD9776A/AD9778A/AD9779A 0.125 POWER-DOWN AND SLEEP MODES 8× INTERPOLATION, f The AD9776A/AD9778A/AD9779A have a variety of power- NO MODULATION 0.100 4× INTERPOLATION down modes; thus, the digital engine, main TxDACs, or auxiliary DACs can be powered down individually or together. Via the SPI port, the main TxDACs can be placed in sleep or power-down 0.075... -

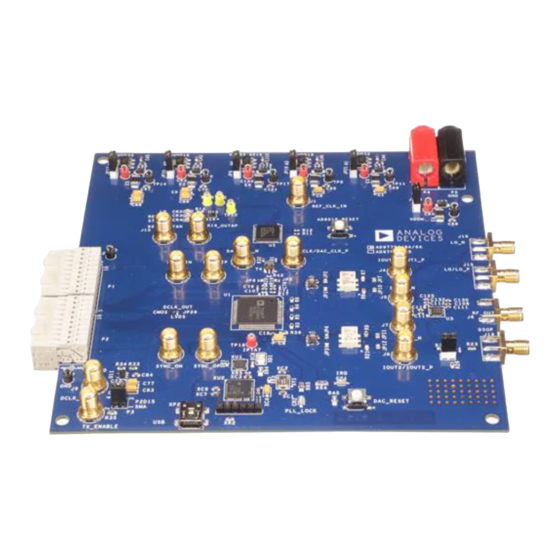

Page 49: Evaluation Board Operation

AD9779A ADL537x JP16 S6 OUTPUT 2 JP17 LOCAL OSC INPUT S7 DCLKOUT ANALOG DEVICES AD9776A/ AD9788A/ SPI PORT AD9779A Figure 102. AD9776A/AD9778A/AD9779A Evaluation Board Showing All Connections Rev. A | Page 49 of 60 Downloaded from Elcodis.com electronic components distributor... - Page 50 AD9776A/AD9778A/AD9779A 1. SET INTERPOLATION RATE 2. SET INTERPOLATION FILTER MODE 3. SET INPUT DATA FORMAT 4. SET DATACLK POLARITY TO MATCH INPUT TIMING Figure 103. SPI Port Software Window The evaluation board comes with software that allows the user the evaluation board, these transformers are designated T1A, to program the SPI port.

-

Page 51: Using The Adl5372 Quadrature Modulator

USING THE ADL5372 QUADRATURE MODULATOR To evaluate the ADL5372 on this board, these same jumper positions should be reversed so that they are in the following The evaluation board contains an Analog Devices ADL5372 positions: quadrature modulator. The AD9776A/AD9778A/AD9779A •... -

Page 52: Evaluation Board Schematics

AD9776A/AD9778A/AD9779A EVALUATION BOARD SCHEMATICS Figure 105. Evaluation Board, Rev. A, Power Supply and Decoupling Rev. A | Page 52 of 60 Downloaded from Elcodis.com electronic components distributor... - Page 53 AD9776A/AD9778A/AD9779A ACASE RC 0 60 3 RC 0 60 3 VOLT VOLT Figure 106. Evaluation Board, Rev. A, Analog and Digital Interfaces to TxDAC Rev. A | Page 53 of 60 Downloaded from Elcodis.com electronic components distributor...

- Page 54 AD9776A/AD9778A/AD9779A ETC1-1-13 Figure 107. Evaluation Board, Rev. A, ADL5372 (FMOD2) Quadrature Modulator Rev. A | Page 54 of 60 Downloaded from Elcodis.com electronic components distributor...

- Page 55 AD9776A/AD9778A/AD9779A Figure 108. Evaluation Board, Rev. A, Tx DAC Clock Interface Rev. A | Page 55 of 60 Downloaded from Elcodis.com electronic components distributor...

- Page 56 AD9776A/AD9778A/AD9779A Figure 109. Evaluation Board, Rev. A, Digital Input Data Lines Rev. A | Page 56 of 60 Downloaded from Elcodis.com electronic components distributor...

- Page 57 AD9776A/AD9778A/AD9779A Figure 110. Evaluation Board, Rev. A, On-Board Power Supply Rev. A | Page 57 of 60 Downloaded from Elcodis.com electronic components distributor...

-

Page 58: Deleted Figure 112 To Figure 117

AD9776A/AD9778A/AD9779A Figure 111. Evaluation Board, Rev A, Top Side Silk Screen Rev. A | Page 58 of 60 Downloaded from Elcodis.com electronic components distributor... - Page 59 AD9776A/AD9778A/AD9779A Figure 112. Evaluation Board, Rev. A, Bottom Side Silk Screen Rev. A | Page 59 of 60 Downloaded from Elcodis.com electronic components distributor...

-

Page 60: Outline Dimensions

AD9778A-EBZ Evaluation Board AD9779A-EBZ Evaluation Board Z = RoHS Compliant Part. ©2007–2008 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D06452-0-3/08(A) Rev. A | Page 60 of 60 Downloaded from Elcodis.com...

Need help?

Do you have a question about the AD9776A and is the answer not in the manual?

Questions and answers