Table of Contents

Advertisement

Quick Links

One Technology Way · P.O. Box 9106 · Norwood, MA 02062-9106 · Tel: 781.329.4700 · Fax: 781.461.3113 ·

www.analog.com

EVALUATING THE AD9257/AD9637

ANALOG-TO-DIGITAL CONVERTERS

Preface

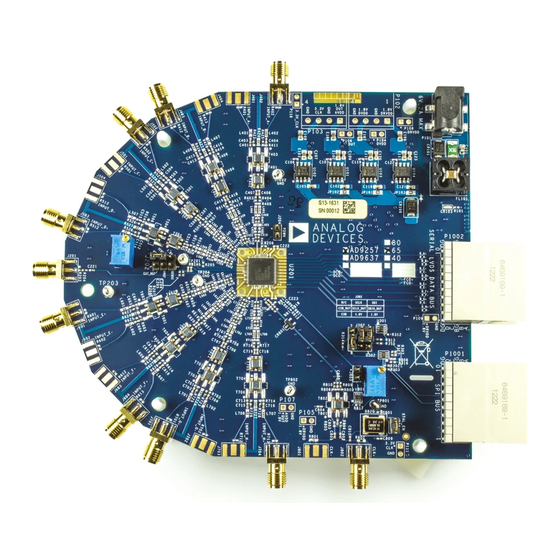

This user guide describes the

AD9257

and

AD9637

evaluation boards,

AD9257-65EBZ

and

AD9637-80EBZ, which provide the support circuitry required to operate these parts in their various

modes and configurations. The application software used to interface with the devices is also

described.

Though the information on this page applies generally to the currently released version of the

AD9257-65EBZ and AD9637-80EBZ, the specifics (i.e. photos, jumper labels, etc.) are for the

soon-to-be-released version. Information specifically for the released version can be found here

quickstartguide_ad9257_ad9637_prb.pdf.

The

AD9257

and

AD9637

data sheets provide additional information and should be consulted when

using the evaluation board. All documents and software tools are available at

www.analog.com/hsadcevalboard. For additional information or questions, send an email to

highspeed.converters@analog.com.

Typical Measurement Setup

Rev 13 Nov 2013 00:23 | Page 1

Advertisement

Table of Contents

Summary of Contents for Analog Devices AD9257

- Page 1 Though the information on this page applies generally to the currently released version of the AD9257-65EBZ and AD9637-80EBZ, the specifics (i.e. photos, jumper labels, etc.) are for the soon-to-be-released version. Information specifically for the released version can be found here quickstartguide_ad9257_ad9637_prb.pdf.

-

Page 2: Helpful Documents

Figure 1. Evaluation Board Connection—AD9257-65EBZ AD9637-80EBZ (on Left) and HSC-ADC-EVALCZ (on Right) Features Full featured evaluation board for the AD9257/AD9637 SPI interface for setup and control External, on-board oscillator, or AD9517 clocking option Balun/transformer or amplifier input drive option On-board LDO regulator or switching regulator, needing a single external 6V, 2A dc supply VisualAnalog®... -

Page 3: Design And Integration Files

Use a shielded, RG-58, 50Ω coaxial cable (optimally 1 m or shorter) to connect the signal generator. For best results, use a narrow-band, band-pass filter with 50Ω terminations and an appropriate center frequency. (Analog Devices, Inc. uses TTE, Allen Avionics, and K&L band-pass filters.) -

Page 4: Power Supplies

(see the Specifications section in the data sheet of the respective part). When connecting the analog input source, use of a multipole, narrow-band band-pass filter with 50Ω terminations is recommended. Analog Devices uses band-pass filters from TTE and K&L Microwave, Inc. Connect the filters directly to the evaluation board. -

Page 5: Output Signals

Output Signals The default setup uses the Analog Devices high speed converter evaluation platform ( HSC-ADC-EVALCZ) for data capture. The serial LVDS outputs from the ADC are routed to Connector P1302 using 100Ω differential traces. For more information on the data capture board and its optional settings, visit www.analog.com/hsadcevalboard. -

Page 6: Evaluation Board Circuitry

Figure 2. Default Jumper Connections for AD9257-65EBZ/AD9637-80EBZ Board Evaluation Board Circuitry This section explains the default and optional ADC settings or modes allowed on the AD9257-65EBZ and the AD9637-80EBZ boards. Power Connect the switching power supply that is supplied in the evaluation kit between a rated 100V ac to 240V ac, 47Hz to 63Hz wall outlet and P101. -

Page 7: Modes Of Operation

The clock input is 50 Ω terminated and ac-coupled to handle single-ended sinusoidal inputs. The transformer converts the single-ended input to a differential signal that is clipped by CR1101 before entering the ADC clock inputs. The AD9257 AD9637 ADCs are equipped with an internal 8:1 clock divider to facilitate usage with higher frequency clocks. -

Page 8: Default Mode

1.8V_DUT_AVDD (jumper J301 Pin 5 to Pin 6) 10 0000 0000 0000 Note that the above settings only apply when CSB is tied high (J301 Pin 8 “floating”) at power up. Additional information on the Standalone (PIN) Mode is provided in the AD9257 AD9637 data sheets. - Page 9 Figure 3. VisualAnalog, New Canvas Window After the template is selected, a message might appear asking if the default configuration can be used to program the FPGA (see Figure 4). If this message appears, click Yes, and the window closes. Figure 4.

-

Page 10: Evaluation And Test

Figure 6. VisualAnalog, Main Window Expanded Display Evaluation And Test Setting up the SPI Controller Software After the ADC data capture board setup is complete, set up the SPI controller software using the following procedure: Open the SPI controller software by going to the Start menu or by double-clicking the SPIController software desktop icon. - Page 11 Figure 7. SPI Controller, CHIP ID(1) Box Click the New DUT button in the SPIController window (see Figure 8) Figure 8. SPI Controller, New DUT Button Rev 13 Nov 2013 00:23 | Page 11...

- Page 12 In the ADCBase 0 tab of the SPIController window, find the CLOCK DIVIDE(B) box (see Figure 9), and the MODES(8) box (see Figure 10). If using the clock divider, use the drop-down box to select the correct clock divide ratio, if necessary. If there is any interruption of the ADC clock during power-up or during operation, a Digital Reset may be needed to re-initialize the ADC (Figure 10).

-

Page 13: Adjusting The Amplitude Of The Input Signal

The next step is to adjust the amplitude of the input signal for each channel as follows: Adjust the amplitude of the input signal so that the fundamental is at the desired level. Examine the Fund Power reading in the left panel of the VisualAnalog Graph - AD9257 FFT window (see Figure 13). -

Page 14: Troubleshooting Tips

13. Graph Window of VisualAnalog Repeat this procedure for the other channels, if desired Click the floppy-disk icon within the VisualAnalog Graph - AD9257 FFT window to save the performance data as a .csv formatted file for plotting or analysis. - Page 15 Probe the DCO signal at P802 (Pin A10 and/or Pin B10) on the evaluation board, and confirm that a clock signal is present at the ADC sampling rate. © Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

Need help?

Do you have a question about the AD9257 and is the answer not in the manual?

Questions and answers