Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Xilinx AV6045

- Page 1 FPGA Video Processing Development Platform AV6045 User Manual...

-

Page 2: Version Record

FPGA Video Processing Development Platform AV6045 User Manual Version Record Version Date Release By Description Rev 1.0 2019-05-01 Rachel Zhou First Release 2 / 54 Contact Email: rachel.zhou@alinx.com.cn... -

Page 3: Table Of Contents

FPGA Video Processing Development Platform AV6045 User Manual Table of Contents Version Record ..................2 Part 1: FPGA Development Board Introduction ......... 6 Part 2: Function realization ................ 8 Part 2.1: Video Input ................8 Part 2.2: Video Output ............... 11 Part 3: AC6045 core board .............. - Page 4 FPGA Video Processing Development Platform AV6045 User Manual Part 4.11: Buttons ................51 Part 4.12: Power Supply ..............52 4 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 5 FPGA Video Processing Development Platform AV6045 User Manual This XILINX FPGA Video Processing development platform (module: AV6045) adopts the core board + carrier board mode, which is convenient for users to use the core board for secondary development. This FPGA video image processing development platform is derived from the improvement of our company's ALTERA video development board.

-

Page 6: Part 1: Fpga Development Board Introduction

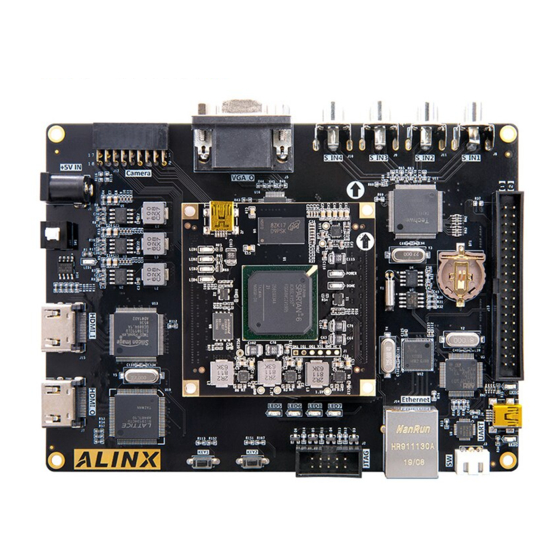

FPGA Video Processing Development Platform AV6045 User Manual Part 1: FPGA Development Board Introduction The entire structure of the AV6045 FPGA development board is inherited from our consistent core board + carrier board mode. A high-speed inter-board connector is used between the core board and the carrier board. - Page 7 FPGA Video Processing Development Platform AV6045 User Manual 视频 视频 视频 视频 HDMI输出 HDMI输入 VGA输出 输入 输入 输入 输入 接口 接口 接口 接口 ADV7123 SiI9134 TW2867 SiI9013 XILINX XC6SLX45 CP2102 RTL8211E 以太网网 CMOS接口 USB UART SD Card 口 Figure 1-1-1: The Schematic Diagram of the AV6045...

-

Page 8: Part 2: Function Realization

FPGA Video Processing Development Platform AV6045 User Manual output 1-channel HDMI Output Select Silion Image SIL9134 HDMI encoding chip, support up to 1080P@60Hz output, support 3D output. 1-channel HDMI Input Select Silion Image SIL9013 HDMI decoder chip, support up to 1080P@60Hz input, support different formats of data output ... - Page 9 FPGA Video Processing Development Platform AV6045 User Manual video sources available for development boards, such as: 1) Surveillance cameras Through the FPGA development board, it is possible to realize four-channel surveillance camera through the display (VGA/DVI/HDMI interface, which can realize 1080p) for split-screen display. Our development board is equivalent to the digital video host in the Figure below.

- Page 10 FPGA Video Processing Development Platform AV6045 User Manual Figure 2-1-2: Set top box 3) Camera Module CMOS camera interface, plug in ALINX 30 megapixel camera module or 5 megapixel camera module, real-time display 1080P video image on VGA display or HDMI display.

-

Page 11: Part 2.2: Video Output

FPGA Video Processing Development Platform AV6045 User Manual Part 2.2: Video Output There are two kinds of video output on the FPGA development board: you can connect a VGA monitor to display VGA images; you can also connect HMDI monitors or TV to display HDMI video signals. The video display for VGA and HDMI output is up to 1080P@60Hz. -

Page 12: Part 3: Ac6045 Core Board

FPGA Video Processing Development Platform AV6045 User Manual Part 3: AC6045 core board 12 / 54 Contact Email: rachel.zhou@alinx.com.cn... -

Page 13: Part 3.1: Ac6045 Core Board Introduction

FPGA Video Processing Development Platform AV6045 User Manual Part 3.1: AC6045 Core Board Introduction FPGA+ DDR3 core board is based on XILINX's SPARTAN6 series XC6SLX45-2FG484I. This chip develops a high-performance core board with high speed, high bandwidth and high capacity. It is suitable for video image processing and high-speed data acquisition. - Page 14 FPGA Video Processing Development Platform AV6045 User Manual In addition, the normal operation of DDR3 requires DDR3 address line and control line to provide termination voltage VTT and DDR3 chip reference voltage VREF, VTT and VREF voltage are both 1.5V, the following Figure 3-2-1 is the power part schematic.

-

Page 15: Part 3.3: Spi Flash

FPGA Video Processing Development Platform AV6045 User Manual DDR3 is connected to the BANK3 of the FPGA. DDR3 Pin Assignment Pin Name FPGA Pin Pin Name FPGA Pin DDR3_A[0] DDR3_A[11] DDR3_A[1] DDR3_A[12] DDR3_A[2] DDR3_A[13] DDR3_A[3] DDR3_A[14] DDR3_A[4] DDR3_BA[0] DDR3_A[5] DDR3_BA[1]... - Page 16 FPGA Video Processing Development Platform AV6045 User Manual Due to the non-volatile nature of SPI FLASH, it can be used as a boot device for the system to store the boot image of the system. These images mainly include FPGA bit files, core application code and other user data files. The specific models and related parameters of SPI FLASH are shown in Table 3-3-1.

-

Page 17: Part 3.4: Av6045 Power Supply

FPGA Video Processing Development Platform AV6045 User Manual SPI Flash pin assignments: Pin Name FPGA Pin SPI_CLK SPI_CSn AB20 SPI_DIN AA20 SPI_DOUT Part 3.4: AV6045 Power Supply In order for FGPA to work properly, it is necessary to provide three power supplies for P3V3, P1V2 and VCCIO for the FPGA. - Page 18 FPGA Video Processing Development Platform AV6045 User Manual Figure 3-4-1:Power Supply on core board schematic 18 / 54 Contact Email: rachel.zhou@alinx.com.cn...

-

Page 19: Part 3.5: Expansion Ports

FPGA Video Processing Development Platform AV6045 User Manual Figure 3-4-2: Power Supply Circuit on the AC6045 FPGA Core Board Part 3.5: Expansion Ports The core board has a total of two high-speed expansion ports, which is connected with the FPGA carrier board by two 100-pin inter-board connectors. - Page 20 FPGA Video Processing Development Platform AV6045 User Manual Figure 3-5-1: Expansion Ports P1 20 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 21 FPGA Video Processing Development Platform AV6045 User Manual Figure 3-5-2: Expansion Ports P2 21 / 54 Contact Email: rachel.zhou@alinx.com.cn...

-

Page 22: Part 3.6: Powe Interface On Core Board

FPGA Video Processing Development Platform AV6045 User Manual Figure 3-5-3: Expansion Ports P1&P2 on the Core Board Part 3.6: Powe interface on Core Board In order to make the core board work normally, the FPGA expansion baord needs to provide a +5V power supply to the core board through the expansion ports. -

Page 23: Part 3.7: Crystal Oscillator On Core Board

FPGA Video Processing Development Platform AV6045 User Manual Figure 3-6-1: Power input pin If you need to debug the core board separately, power the core board through the Mini USB port (J2) of the core board, the Mini USB cable is connected to the USB port of the computer. - Page 24 FPGA Video Processing Development Platform AV6045 User Manual and the 27MHz clock is connected to the B10 pin of the FPGA. Figure 3-7-1: Crystal oscillator Schematic Figure 3-7-2: Crystal oscillator on the Core Board Crystal oscillator Pin Assignment Input Clock...

-

Page 25: Part 3.8: Led Light On Core Board

FPGA Video Processing Development Platform AV6045 User Manual Part 3.8: LED Light on Core Board There are 6 red LED lights on the AC6045 FPGA core board, one of which is the power indicator light (PWR), one is the configuration LED light (DONE), and four are the user LED light. - Page 26 FPGA Video Processing Development Platform AV6045 User Manual The schematic diagram of the four user LED sections is shown below. In Figure 3-8-3, When the FPGA pin output is logic 0, the LED will be lit. Figure 3-8-3: User LED Schemaitc...

-

Page 27: Part 3.9: Structure Diagram

FPGA Video Processing Development Platform AV6045 User Manual Part 3.9: Structure Diagram Figure 3-9-1: AC6045 FPGA Core board (Top view) Figure 3-9-2: AC6045 FPGA Core board (Top view) 27 / 54 Contact Email: rachel.zhou@alinx.com.cn... -

Page 28: Part 4: Carrier Board

FPGA Video Processing Development Platform AV6045 User Manual Part 4: Carrier board Part 4.1: Carrier board Introduction Through the previous function introduction, you can understand the function of the carrier board part 4-channel Video Input TW2867 1-channel HDMI Input SiI9013 ... -

Page 29: Part 4.2: Vga Display Interface

FPGA Video Processing Development Platform AV6045 User Manual Basic experiment 1) DDR3 test experiment 2) VGA output color bar experiment 3) HDMI output color bar experiment 4) TW2867 input to VGA display experiment 5) I2C communication experiment 6) RGB to Ycbcr experiment... - Page 30 RGB digital signals to output VGA video signals, up to 1080p@60Hz output. In the AV6045 FPGA development board, the RGB digital signal output by the FPGA is 24-bit color, of which 8 colors are red, green and blue. In the schematic design, the 8-bit data of the red, green and blue output of the FPGA is connected to the 3-way DA of the ADV7123.

-

Page 31: Part 4.3: Hdmi Output Interface

FPGA Video Processing Development Platform AV6045 User Manual VGA Signal Pin Assignment Pin Name FPGA Pin VGA_CLK VGA_EN VGA_HS VGA_VS VGA_R7 VGA_R6 VGA_R5 VGA_R4 VGA_R3 VGA_R2 VGA_R1 VGA_R0 VGA_G7 VGA_G6 VGA_G5 VGA_G4 VGA_G3 VGA_G2 VGA_G1 VGA_G0 VGA_B7 VGA_B6 VGA_B5 VGA_B4... - Page 32 FPGA Video Processing Development Platform AV6045 User Manual of Silion Image , which supports up to 1080P@60Hz output and supports 3D output. Among them, IIC interface of SIL9134 is connected with STM32F103, SIL9134 is initialized and controlled by STM32F103, and other pins of SIL9134 are connected to FPGA.

- Page 33 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-3-2: HDMI Output interafce on the carrier board HDMI Output Interface Pin Assignment Pin Name FPGA Pin 9134_CLK 9134_HS 9134_VS 9134_DE 9134_D[0] 9134_D[1] 9134_D[2] 9134_D[3] AB18 9134_D[4] AA18 9134_D[5] AB17 9134_D[6]...

-

Page 34: Part 4.4: Hdmi Input Interface

FPGA Video Processing Development Platform AV6045 User Manual AB19 9134_D[13] 9134_D[14] 9134_D[15] 9134_D[16] 9134_D[17] 9134_D[18] 9134_D[19] 9134_D[20] 9134_D[21] 9134_D[22] 9134_D[23] Part 4.4: HDMI Input Interface The HDMI input interface, used the SIL9013 HDMI decoder chip of Silion Image , which supports up to 1080P@60Hz input and Support data output in different formats. - Page 35 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-4-2: HDMI Input Interface on the FPGA Board HDMI Input Interface Pin Assignment Pin Name FPGA Pin AA12 9013_CLK 9013_HS 9013_VS 9013_DE 9013_D[0] 9013_D[1] 9013_D[2] 9013_D[3] 9013_D[4] 9013_D[5] 9013_D[6] 9013_D[7] 9013_D[8]...

-

Page 36: Part 4.5: Video Input Interface

FPGA Video Processing Development Platform AV6045 User Manual AB15 9013_D[14] 9013_D[15] AA16 9013_D[16] 9013_D[17] 9013_D[18] 9013_D[19] 9013_D[20] 9013_D[21] 9013_D[22] AB16 9013_D[23] Part 4.5: Video input interface Select Techwell TW2867, input composite video signals, PAL/NTSC/SECAM automatic identification, output BT656, multiplexable bus,... - Page 37 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-5-1: Video Input Interface Schematic Figure 4-5-2: Video Input Interface on the carrier board 37 / 54 Contact Email: rachel.zhou@alinx.com.cn...

-

Page 38: Part 4.6: Gigabit Ethernet Interface

FPGA Video Processing Development Platform AV6045 User Manual Video Input Interface Pin Assignment Pin Name FPGA Pin 2867_CLKP 2867_CLKN 2867_D[0] 2867_D[1] 2867_D[2] 2867_D[3] 2867_D[4] 2867_D[5] 2867_D[6] 2867_D[7] Part 4.6: Gigabit Ethernet Interface FPGA development board provides users with network communication services through the Realtek RTL8211EG Ethernet PHY chip. - Page 39 FPGA Video Processing Development Platform AV6045 User Manual When the network is connected to Gigabit Ethernet, the data transmission of FPGA and PHY chip RTL8211EG is communicated through the RGMII bus, the transmission clock is 125Mhz. The receive clock E_RXC is provided by the PHY chip, the transmit clock E_GTXC is provided by the FPGA, and the data is sampled on the rising edge of the clock.

- Page 40 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-6-2: Gigabit Ethernet interface on the Carrier board Gigabit Ethernet pin assignments: Pin Name FPGA Pin Description RGMII transmit clock E_GCLK Transmit Data bit0 E_TXD0 Transmit Data bit1 E_TXD1 Transmit Data bit2...

-

Page 41: Part 4.7: Arm Controller

FPGA Video Processing Development Platform AV6045 User Manual MIMO Management Data E_MDIO Part 4.7: ARM Controller An ARM chip (STM32F103) is mounted on the carrier board, and each interface chip is reset through the IO port, and the registers of each interface chip and the data communication with the FPGA are configured through I2C. - Page 42 FPGA Video Processing Development Platform AV6045 User Manual At the same time, the ARM chip also brings out real-time clock, EEPROM, 4 LEDs, and serial ports. Part 4.7.1: Real Time Clock Figure 4-7-3: RTC Schematic Figure 4-7-4: RTC on the carrier board 42 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 43 FPGA Video Processing Development Platform AV6045 User Manual ARM corresponding pin: Pin Name ARM Pin RTC_SCLK RTC_IO RTC_RESET Part 4.7.2: EEPROM Figure 4-7-5: EEPROM Schematic Figure 4-7-6: EEPROM on the carrier board ARM corresponding pin: Pin Name ARM Pin 24LC04_SDA...

- Page 44 FPGA Video Processing Development Platform AV6045 User Manual Part 4.7.3: LED Figure 4-7-7: LED Schematic Figure 4-7-8: LED on the carrier board ARM corresponding pin: Pin Name ARM Pin LED0 LED1 LED2 LED3 44 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 45 FPGA Video Processing Development Platform AV6045 User Manual Part 4.7.4: USB to Serial Port Figure 4-7-9: USB to Serial Port Schematic Figure 4-7-10: USB to Serial Port on the expansion port ARM corresponding pin: Pin Name ARM Pin RXD1 TXD1 45 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 46 FPGA Video Processing Development Platform AV6045 User Manual Part 4.7.5: SD Card Slot ARM communicates with the Micro SD card through the SPI interface for reading and storing SD card data. Figure 4-7-11: Mini SD Schematic Figure 4-7-12: SD Card Slot on the carrier board...

-

Page 47: Part 4.8: Camera Module Interface

FPGA Video Processing Development Platform AV6045 User Manual Part 4.8: Camera Module Interface Figure 4-8-1: CMOS camera interface Schematic The development board includes an 18-pin CMOS camera interface that can be connected to the OV7670 camera module and the OV5640 camera module for video capture. -

Page 48: Part 4.9: Expansion Header

FPGA Video Processing Development Platform AV6045 User Manual The following table shows the FPGA pin assignments for connecting 5 million CMOS cameras (AN5640 modules): Pin Name FPGA Pin CMOS_SCLK CMOS_SDAT CMOS_VSYNC CMOS_HREF CMOS_PCLK CMOS_XCLK CMOS_D[7] CMOS_D[6] CMOS_D[5] CMOS_D[4] CMOS_D[3] AB11... - Page 49 FPGA Video Processing Development Platform AV6045 User Manual circuit of the expansion port (J13) is shown in Figure 3-9-1. Figure 4-9-1: Expansion header J13 schematic Figure 4-9-2: Expansion header J13 on the Carrier board J13 Expansion Header Pin Assignment Pin Number...

-

Page 50: Part 4.10: Jtag Interface

FPGA Video Processing Development Platform AV6045 User Manual D3V3 D3V3 Part 4.10: JTAG Interface A JTAG interface is reserved on the FPGA carrier board for downloading FPGA programs or firmware to FLASH. In order to prevent damage to the FPGA chip caused by hot plugging, a protection diode is added to the JTAG signal to ensure that the voltage of the signal is within the range accepted by the FPGA to avoid damage of the FPGA chip. - Page 51 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-10-1: JTAG Interface Schematic Figure 4-10-2: JTAG Interface on the carrier board Be careful not to hot swap when JTAG cable is plugged and unplugged. Part 4.11: Buttons The FPGA carrier board contains two user buttons KEY1~KEY2. All buttons are connected to the normal IO of the FPGA.

- Page 52 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-11-1: Button Schematic Figure 4-11-2: User Buttons on the Carrier board Buttons Pin Assignment Net Name FPGA PIN KEY1 KEY2 Part 4.12: Power Supply The power input voltage of the FPGA development board is DC5V. It is converted into D3V3, D1V2, D1V8 three-way power supply through three-way DC/DC power chip MP1482.

- Page 53 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-12-1 Power Design Schematic on the carrier board 53 / 54 Contact Email: rachel.zhou@alinx.com.cn...

- Page 54 FPGA Video Processing Development Platform AV6045 User Manual Figure 4-12-2: Power Supply circuit on the carrier board 54 / 54 Contact Email: rachel.zhou@alinx.com.cn...

Need help?

Do you have a question about the AV6045 and is the answer not in the manual?

Questions and answers